Rev PrA, 24-Jan-08 Advanced Product Information – All Information Subject to Change

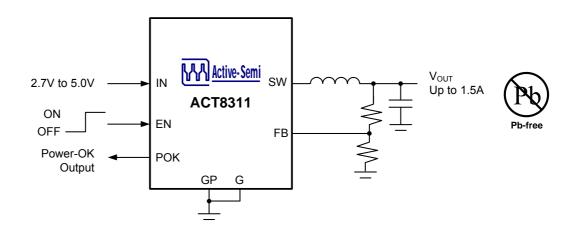

# 1.5A, PWM Step-Down DC/DCs in TDFN

#### **FEATURES**

- Multiple Patents Pending

- Up to 95% High Efficiency

- Up to 1.5A Guaranteed Output Current (ACT8311)

- 1.35MHz Constant Frequency Operation

- Internal Synchronous Rectifier Eliminates Schottky Diode

- ACT8309: Up to 900mA

ACT8310: Up to 1.2A

ACT8311: Up to 1.5A

- 100% Duty Cycle Low-Dropout Operation

- 0.1µA Shutdown Current

- Small TDFN33-8 Package

- RoHS-Compliant

- Independent Enable/Disable Control

- Minimal External Components

#### **APPLICATIONS**

- Wireless Handhelds

- Portable Devices

- GPS/PND equipment

#### **GENERAL DESCRIPTION**

The patent-pending ACT8309/ACT8310/ACT8311 are current-mode, fixed-frequency PWM, synchronous step-down DC/DC converters that are capable of delivering 1.5A with efficiency of up to 95%. These devices operate with a fixed frequency of 1.35MHz, minimizing noise in sensitive equipment as well as optimizing both efficiency and component size and cost.

These devices feature very low-resistance power MOSFET and 100% duty cycle operation, making them ideal choices for portable applications requiring a 3.0V or 3.3V rail to be generated from a Li+battery.

The ACT8311 is capable of supplying up to 1.5A of output current, while the ACT8309 and ACT8310 are capable of supplying up to 900mA and 1.2A, respectively. All three devices have adjustable output voltages that are programmable down to 1.2V. Contact Active-Semi for custom fixed output voltage availability.

www.DataSheet4U.com

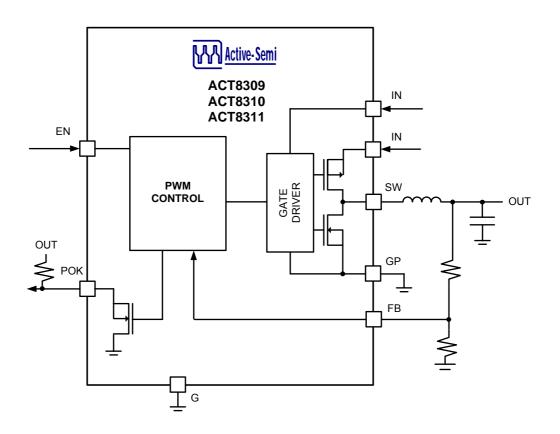

## SYSTEM BLOCK DIAGRAM

Rev PrA, 24-Jan-08

# **ORDERING INFORMATION**

| PART<br>NUMBER | OUTPUT<br>CURRENT | OUTPUT<br>VOLTAGE                                  | PACKAGE  | PINS | TEMPERATURE<br>RANGE |  |

|----------------|-------------------|----------------------------------------------------|----------|------|----------------------|--|

| ACT8309NHADJ-T | 0.9A              | Adjustable                                         | TDFN33-8 | 8    | -40°C to +85°C       |  |

| ACT8309NHxyz-T | 0.9A              | 1.2V, 1.5V, 1.8V,<br>2.5V, 3.0V, 3.3V <sup>®</sup> | TDFN33-8 | 8    | -40°C to +85°C       |  |

| ACT8310NHADJ-T | 1.2A              | Adjustable                                         | TDFN33-8 | 8    | -40°C to +85°C       |  |

| ACT8310NHxyz-T | 1.2A              | 1.2V, 1.5V, 1.8V,<br>2.5V, 3.0V, 3.3V <sup>®</sup> | TDFN33-8 | 8    | -40°C to +85°C       |  |

| ACT8311NHADJ-T | 1.5A              | Adjustable                                         | TDFN33-8 | 8    | -40°C to +85°C       |  |

| ACT8311NHxyz-T | 1.5A              | 1.2V, 1.5V, 1.8V,<br>2.5V, 3.0V, 3.3V <sup>©</sup> | TDFN33-8 | 8    | -40°C to +85°C       |  |

①: Fixed output voltage options are available for production subject to minimum order quantities. Contact Active-Semi for more information regarding fixed output voltage options.

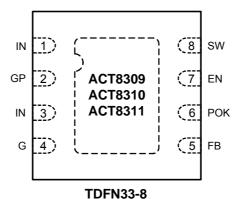

## **PIN CONFIGURATION**

www.DataSheet4U.com

## **PIN DESCRIPTIONS**

| PIN  | NAME | DESCRIPTION                                                                                                                                                                                                                                                                |  |  |  |

|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1, 3 | IN   | Power Input. Bypass to GP close to IC with a high quality ceramic capacitor.                                                                                                                                                                                               |  |  |  |

| 2    | GP   | Power Ground. Connect to G with a short trace.                                                                                                                                                                                                                             |  |  |  |

| 4    | G    | Analog Ground. Connect to GP with a short trace.                                                                                                                                                                                                                           |  |  |  |

| 5    | FB   | Feedback Node. For fixed output voltage versions, connect this pin directly to the output. For the adjustable output versions the voltage at this pin is regulated to 0.8V, connect to this pin to the center of the output feedback resistor divider for voltage setting. |  |  |  |

| 6    | POK  | Open-Drain Power-OK Status Output. POK is an open-drain output which sinks current when the output voltage is less than 95% of the normal value. When the IC is disabled, POK is high impedance.                                                                           |  |  |  |

| 7    | EN   | Enable Input. When higher than 1.4V, this pin turns the IC on. When lower than 0.4V, this pin turn the IC off.                                                                                                                                                             |  |  |  |

| 8    | SW   | Switch Output. Connect this pin to the switching end of the inductor.                                                                                                                                                                                                      |  |  |  |

Rev PrA, 24-Jan-08

# **ABSOLUTE MAXIMUM RATINGS®**

| PARAMETER                                                               | VALUE                         | UNIT |

|-------------------------------------------------------------------------|-------------------------------|------|

| IN, SW to GP                                                            | -0.3 to +5.5                  | V    |

| FB, EN, POK to G                                                        | -0.3 to +5.5                  | V    |

| FB, EN, SW Voltage                                                      | -0.3 to V <sub>IN</sub> + 0.3 | V    |

| GP to G                                                                 | -0.3 to +0.3                  | V    |

| Continuous SW Current                                                   | Internally limited            | Α    |

| Junction to Ambient Thermal Resistance (θ <sub>JA</sub> )               | 61                            | °C/W |

| Maximum Power Dissipation (derate 5.3mW/°C above T <sub>A</sub> = 50°C) | 1.63                          | W    |

| Operating Junction Temperature                                          | -40 to 150                    | °C   |

| Storage Temperature                                                     | -55 to 150                    | °C   |

| Lead Temperature (Soldering, 10 sec)                                    | 300                           | °C   |

①: Do not exceed these limits to prevent damage to the device. Exposure to absolute maximum rating conditions for long periods may affect device reliability.

www.DataSheet4U.com

Rev PrA, 24-Jan-08

## **ELECTRICAL CHARACTERISTICS**

( $V_{IN}$  =  $V_{EN}$  = 3.6V,  $T_A$  = 25°C, unless otherwise specified.)

| PARAMETER                       | SYMBOL            | TEST CONDITIONS                                | MIN   | TYP       | MAX   | UNIT |  |

|---------------------------------|-------------------|------------------------------------------------|-------|-----------|-------|------|--|

| Input Voltage Range             | V <sub>IN</sub>   |                                                | 2.7   |           | 5.0   | V    |  |

| Under Voltage Lockout Threshold | $V_{\text{UVLO}}$ | V <sub>IN</sub> rising, hysteresis = 80mV      | 2.35  | 2.5       | 2.6   | V    |  |

| Standby Supply Current          |                   | $V_{FB} = 103\%V_{FB,TYP}, I_{OUT} = 0$        |       | 150       | 310   | μΑ   |  |

| Shutdown Supply Current         |                   | EN = G, V <sub>IN</sub> = 4.2V                 |       | 0.1       | 1     | μΑ   |  |

| 50.V.#                          | $V_{FB}$          | T <sub>A</sub> = 25°C                          | 0.786 | 0.80      | 0.814 | V    |  |

| FB Voltage                      |                   | -40°C < T <sub>A</sub> < 85°C                  | 0.776 | 0.80      | 0.824 |      |  |

| Output Valtage Assurage         |                   | T <sub>A</sub> = 25°C                          | -2%   | $V_{NOM}$ | +2%   |      |  |

| Output Voltage Accuracy         |                   | -40°C < T <sub>A</sub> < 85°C                  | -3%   | $V_{NOM}$ | +3%   | - V  |  |

| Output Voltage Line Regulation  |                   |                                                |       | 0.06      | 0.4   | %/V  |  |

| Output Voltage Load Regulation  |                   |                                                |       | 0.6       |       | %    |  |

|                                 |                   | ACT8309NH                                      | 1.1   | 1.3       | 1.8   |      |  |

| Current Limit                   |                   | ACT8310NH                                      | 1.4   | 1.7       | 2.2   | Α    |  |

|                                 |                   | ACT8311NH                                      | 1.75  | 2.1       | 2.8   | 1    |  |

|                                 |                   | ACT8309NH                                      |       |           | 0.9   |      |  |

| Max Output Current              |                   | ACT8310NH                                      |       |           | 1.2   | Α    |  |

|                                 |                   | ACT8311NH                                      |       |           | 1.5   |      |  |

| Ossillatas Francisco            |                   | V <sub>OUT</sub> = 80% of V <sub>OUT,NOM</sub> | 1.05  | 1.35      | 1.6   | MHz  |  |

| Oscillator Frequency            | f <sub>SW</sub>   | V <sub>FB</sub> = 0.1V                         |       | 450       |       | kHz  |  |

|                                 | R <sub>ONP</sub>  | ACT8309, I <sub>SW</sub> = -100mA              |       | 0.15      | 0.234 |      |  |

| PMOS On-Resistance              |                   | ACT8310, I <sub>SW</sub> = -100mA              |       | 0.12      | 0.192 | Ω    |  |

| tachect+0.com                   |                   | ACT8311, I <sub>SW</sub> = -100mA              |       | 0.10      | 0.165 |      |  |

| NMOS On-Resistance              | R <sub>ONN</sub>  | I <sub>SW</sub> = 100mA                        |       | 0.15      | 0.26  | Ω    |  |

| EN Logic High Threshold         | V <sub>IH</sub>   | V <sub>IN</sub> = 2.7V to 5.0V                 | 1.4   |           |       | V    |  |

| EN Logic Low Threshold          | V <sub>IL</sub>   | V <sub>IN</sub> = 2.7V to 5.0V                 |       |           | 0.4   | V    |  |

| EN Input Bias Current           | I <sub>EN</sub>   | V <sub>IN</sub> = 5.0V, EN = G or IN           |       | 0.01      | 0.1   | μΑ   |  |

| POK Threshold                   |                   | % of V <sub>OUT,NOM</sub>                      |       | 95        |       | %    |  |

| POK Output Low Voltage          | V <sub>OL</sub>   | Ι <sub>ΡΟΚ</sub> = 100μΑ                       |       | 0.008     | 0.012 | V    |  |

| POK Leakage Current             | I <sub>POK</sub>  | V <sub>POK</sub> = 5.0V                        |       | 0.01      | 0.1   | μA   |  |

Rev PrA, 24-Jan-08

Figure1: Functional Block Diagram

Figure 2:

www.DataSheet4U Complication Circuit

Rev PrA, 24-Jan-08

#### **FUNCTIONAL DESCRIPTION**

The patent-pending ACT8309/ACT8310/ACT8311 are current-mode, fixed-frequency PWM, synchronous step-down DC/DC converters that are capable of delivering up to 1.5A (ACT8311) with efficiency of up to 95%. These devices feature very low-resistance power MOSFETs and 100% duty cycle operation, making them ideal choices for portable applications requiring a 3.0V or 3.3V rail to be generated form a Li+ battery. These device operate with a fixed frequency of 1.35MHz, minimizing noise in sensitive equipment as well as optimizing both efficiency and component size and cost.

## 100% Duty Cycle Operation

These devices are capable of operating at up to 100% duty cycle operation. During 100% duty cycle operation, the high-side power MOSFET is held on continuously, providing a direct connection from the input to the output (through the inductor), ensuring the lowest possible dropout voltage in battery-powered applications.

## **Synchronous Rectification**

The ACT8309/ACT8310/ACT8311 each feature integrated n-channel synchronous rectifiers, maximizing efficiency and minimizing the total solution size and cost by eliminating the need for external rectifiers.

#### Soft-Start

The ACT8309/ACT8310/ACT8311 each include www.Databased Soft-start circuitry. When enabled, the output voltage track an internal 200µs soft-start ramp so that the output power up in a controlled, monotonic manner that is independent of loading.

## Compensation

The ACT8309/ACT8310/ACT8311 each utilize current-mode control and a proprietary internal compensation scheme to simultaneously simplify external component selection and optimize transient performance over their full operating range. No compensation design is required, simply follow a few simple guidelines described below when choosing external components.

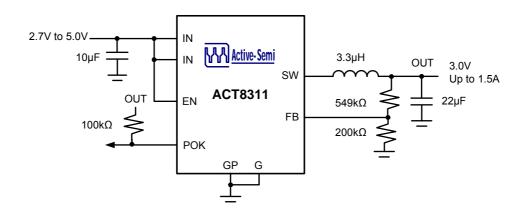

#### Capacitor Selection

The input capacitor reduces peak currents and noise induced upon the voltage source. A  $10\mu F$  ceramic capacitor is recommended for most applications.

For most applications, a 22µF ceramic output capacitor is recommended. Although the these regulators were designed to take advantage of the benefits of ceramic capacitors, namely small size and very-low ESR, low-ESR tantalum capacitors can provide acceptable results as well.

#### **Inductor Selection**

These devices were optimized for operation with  $3.3\mu H$  inductors, although inductors in the  $1.5\mu H$  to  $4.7\mu H$  range may be used. Choose an inductors with a low DC-resistance, and avoid inductor saturation by choosing inductors with DC ratings that exceed the maximum output current of the application by at least 30%.

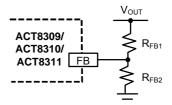

## **Output Voltage Setting**

Figure 3 shows the feedback network necessary to set the output voltage when using adjustable output voltage options. Output voltage options. Select components as follows: Set  $R_{FB2}$  = 200k $\Omega$ , calculate  $R_{FB1}$  using the following equation:

$$R_{FB1} = R_{FB2} \left( \frac{V_{OUT}}{V_{FB}} - 1 \right)$$

Where  $V_{FB}$  is 0.8V.

# Figure 3: Output Voltage Setting

## **Enable/Disable Control**

These devices may be enabled and disabled using the EN input. Drive EN to a logic-high to enable the regulator, drive EN to a logic-low to disable the regulator. When disabled, each regulator's quiescent supply current drops to less than 1µA.

#### Power-OK Output (POK)

These devices feature an open-drain "Power-OK" indicator output. This output sinks current whenever the output voltage is (typically) 5% below the regulation voltage, and goes high-impedance when the output voltage is above this threshold. To generate

Rev PrA, 24-Jan-08

a logic-level "Power-OK" signal, simply connect a pullup resistor from POK to an appropriate output voltage.

## **PCB Layout Considerations**

High switching frequencies and large peak current make PC board layout an important part of stepdown DC/DC converter design. A good design minimizes excessive EMI on the feedback paths and voltage gradients in the ground plane, both of which can result in instability or regulation errors. Step-down DC/DCs exhibit discontinuous input current, so the input capacitors should be placed as close as possible to the IC, and avoiding the use of vias if possible. The inductor, input filter capacitor, and output filter capacitor should be connected as close together as possible, with short, direct, and wide traces. The ground nodes for each regulator's power loop should be connected at a single point in a star-ground configuration, and this point should be connected to the backside ground plane with multiple vias. For fixed output voltage options the output node for each regulator should be connected to its corresponding FB pin through the shortest possible route, while keeping sufficient distance from switching nodes to prevent noise injection. Adjustable output versions should follow the same guidelines, but additionally connect the feedback resistors to the FB pin as close to the IC as possible to minimize noise injection.

www.DataSheet4U.com

Efficiency (%)

30

20 10

0

# ACT8309/8310/8311

Rev PrA, 24-Jan-08

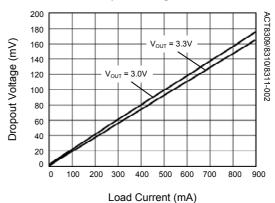

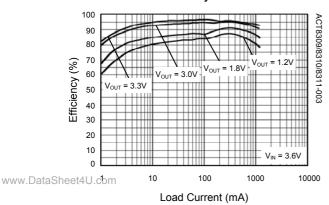

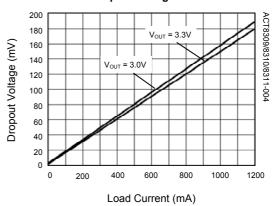

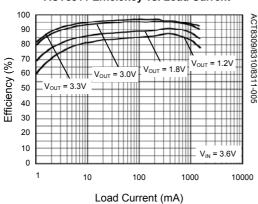

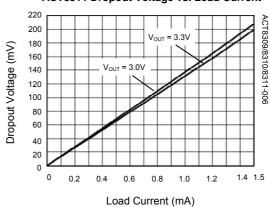

## TYPICAL PERFORMANCE CHARACTERISTICS

$(V_{IN} = V_{EN} = 3.6V, T_A = 25^{\circ}C, unless otherwise specified.)$

##

**ACT8309 Efficiency vs. Load Current**

100 1 Load Current (mA)

#### ACT8309 Dropout Voltage vs. Load Current

#### **ACT8310 Efficiency vs. Load Current**

#### ACT8310 Dropout Voltage vs. Load Current

#### ACT8311 Efficiency vs. Load Current

#### **ACT8311 Dropout Voltage vs. Load Current**

Rev PrA, 24-Jan-08

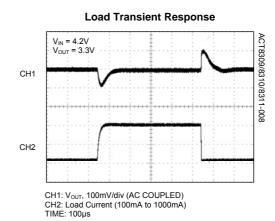

# TYPICAL PERFORMANCE CHARACTERISTICS

$(V_{IN} = V_{EN} = 3.6V, T_A = 25^{\circ}C, unless otherwise specified.)$

# Startup Waveform V<sub>IN</sub> = 4.2V V<sub>OUT</sub> = 3.3V I<sub>OUT</sub> = 1A CH1 CH2 CH1: V<sub>OUT</sub>, 1.0V/div CH2: POK, 2.0V/div TIME: 100µs

www.DataSheet4U.com

Rev PrA, 24-Jan-08

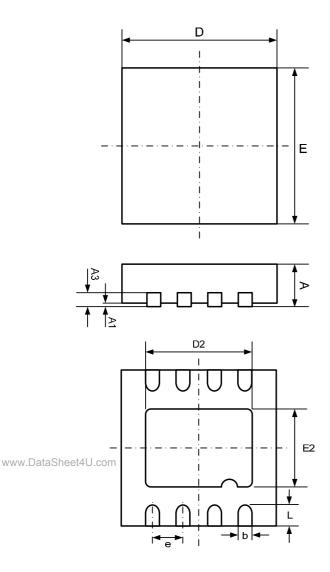

## PACKAGE OUTLINE

#### **TDFN33-8 PACKAGE OUTLINE AND DIMENSIONS**

| SYMBOL |       | SION IN<br>IETERS | DIMENSION IN INCHES |       |  |

|--------|-------|-------------------|---------------------|-------|--|

|        | MIN   | MAX               | MIN                 | MAX   |  |

| А      | 0.700 | 0.800             | 0.028               | 0.031 |  |

| A1     | 0.000 | 0.050             | 0.000               | 0.002 |  |

| A3     | 0.153 | 0.253             | 0.006               | 0.010 |  |

| D      | 2.900 | 3.100             | 0.114               | 0.122 |  |

| Е      | 2.900 | 3.100             | 0.114               | 0.122 |  |

| D2     | 2.200 | 2.400             | 0.087               | 0.094 |  |

| E2     | 1.400 | 1.600             | 0.055               | 0.063 |  |

| b      | 0.200 | 0.320             | 0.008               | 0.013 |  |

| е      | 0.650 | ) TYP             | 0.026 TYP           |       |  |

| L      | 0.375 | 0.575             | 0.015               | 0.023 |  |

Active-Semi, Inc. reserves the right to modify the circuitry or specifications without notice. Users should evaluate each product to make sure that it is suitable for their applications. Active-Semi products are not intended or authorized for use as critical components in life-support devices or systems. Active-Semi, Inc. does not assume any liability arising out of the use of any product or circuit described in this datasheet, nor does it convey any patent license.

Active-Semi and its logo are trademarks of Active-Semi, Inc. For more information on this and other products, contact <u>sales@active-semi.com</u> or visit <u>http://www.active-semi.com</u>. For other inquiries, please send to:

1270 Oakmead Parkway, Suite 310, Sunnyvale, California 94085-4044, USA