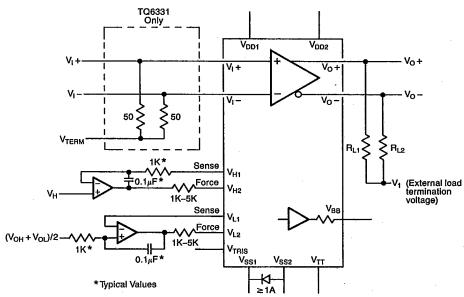

#### TO6331 Only Pin Driver/ $V_{DD1}$ $V_{DD2}$ Line Receiver

#### Features:

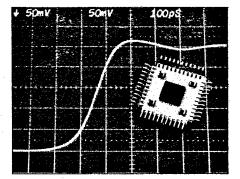

- 100ps Rise and Fall Times, typical

- 3.0 Gbits/sec Data Rate, typical

- Controllable Output Voltage Levels

- Tri-State Outputs (50 Ohms to -2V)

- **■** ECL-Compatible Inputs

- Inputs and Outputs can be Differential or Single-Ended

## Applications:

- **■** High-Speed Test Systems

- Clock Driver/Buffer

- Fiber Optic Laser Drivers

- High-Speed Pulse Generators

- High-Speed Line Receivers

- High-Speed Modulators

- Signal Conditioning for High-**Speed Counters**

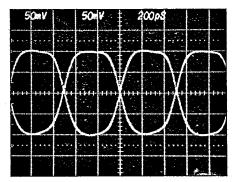

100ps risetime, 0.5V/div, differential output

## Block Diagram:

### Functional Description:

The TQ6330 is a pin or line driver whose output voltage levels can be adjusted between +3.0 Volts and -3.0 Volts when driving 50-Ohm load resistors. The output voltage levels are controlled by driving the level-control inputs. Sense outputs are provided so that the user may provide a level control input to achieve the desired output, either as a calibration procedure or in a feedback control loop. Each output is designed to produce a swing of up to 3 Volts (4V typical) into 50 Ohms with typical rise and fall times of 100ps (1V swing).

The outputs can typically switch from 5 Volts to 0 Volts when driving a high impedance load, making the TQ6330 suitable for driving CMOS or TTL. The inputs and outputs can be differential or single-ended. The inputs are compatible with standard ECL voltage levels.

The outputs can be switched to a "Tri-State" mode where they become 50-Ohm resistors connected to -2 Volts. The "Tri-State" condition of the outputs is controlled by an input which is ECL-compatible.

The TQ6331 line receiver is identical to the TQ6330 pin driver with the addition of 50-Ohm input termination resistors from V<sub>I</sub> + and V<sub>I</sub> - to the common termination voltage pin, V<sub>TERM</sub>.

The TQ6330 and TQ6331 are also available in die form, designated as TQ6330D and TQ6331D.

# **Electrical Specifications**

| $V_{DD1} = V_{DD2} = +6V$                  | $V_{SS1} = -6V$            | V <sub>SS2</sub> = -8V | DC Specifications (typical) |

|--------------------------------------------|----------------------------|------------------------|-----------------------------|

| V <sub>IH</sub> = -1.1V                    | V <sub>IL</sub> = 1.5V     |                        | (4)                         |

| $V_{OH}^{(3)} = 3.0V^{(1)}, 5.0V^{(2)}$    | $V_{OL}^{(3)} = -3.0V$     |                        |                             |

| $V_{OH} - V_{OL}^{(3)} = 0$ to $+4V^{(1)}$ | or 0 to +8V <sup>(2)</sup> |                        |                             |

Power dissipation = 2W

$T_C = 27^{\circ}C$

| <b>Data Rate</b> | NRZ: |

|------------------|------|

|------------------|------|

3.0 Gbits/sec

... AC Specifications (typical, V<sub>OH</sub> - V<sub>OL</sub> = 1V)

Rise Time: (20% to 80%)

100ps

Note 1: R<sub>LOAD</sub> = 50 Ohms. Note 2: 1 TTL or CMOS load. Note 3: User adjustable.

tife-support devices and/or systems.

The information provided herein is believed to be reliable; however, TriQuint assumes no responsibility for inaccuracies or omissions. TriQuint assumes no responsibility for the use of this information, and all such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. TriQuint does not authorize or warrant any TriQuint product for use in

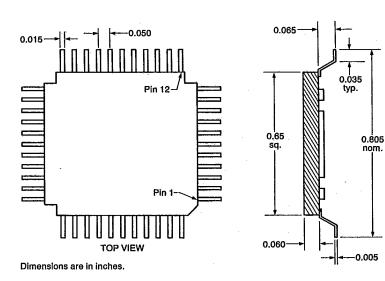

| Pin | Name             | Pin  | Name              |

|-----|------------------|------|-------------------|

| 1   | GND              | 23   | GND               |

| 2   | n.c.             | 24   | V <sub>I</sub> –  |

| 3   | $V_{DD1}$        | 25   | V <sub>TERM</sub> |

| 4   | GND              | 26   | GND               |

| 5   | $V_{DD1}$        | 27   | V <sub>I</sub> +  |

| 6   | Vo-              | 28   | V <sub>BB</sub>   |

| 7   | GND              | 29   | GND               |

| 8   | $V_{L1}$         | . 30 | $V_{DD1}$         |

| 9   | Vo+              | 31   | V <sub>SS2</sub>  |

| 10  | GND              | 32   | GND               |

| 11  | V <sub>SS1</sub> | 33   | V <sub>SS1</sub>  |

| 12  | GND              | 34   | GND               |

| 13  | VH1              | 35   | VTRIS             |

| 14  | $V_{DD2}$        | 36   | VL2               |

| 15  | GND              | 37   | GND               |

| 16  | $V_{DD2}$        | 38   | $V_{H2}$          |

| 17  | VSS2             | 39   | VTT               |

| 18  | GND              | 40   | GND               |

| 19  | VSS1             | 41   | V <sub>SS1</sub>  |

| 20  | n.c.             | 42   | V <sub>SS1</sub>  |

| 21  | GND              | 43   | GND               |

| 22  | V <sub>SS2</sub> | 44   | $V_{SS2}$         |

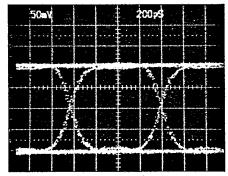

2 Gbits/sec, 0.5V/div, 50  $\Omega$  load

Pseudo random data eye pattern 1.2 Gbits/sec NRZ data, 0.5V/div, 50  $\Omega$  load

For further information, please contact: Sales Department

TriQuint Semiconductor, Inc. Group 700, P.O. Box 4935 Beaverton, OR 97076 (503) 644-3535

FAX: (503) 644-3198