#### Advance Information

This document contains information on a product under development. The parametric information contains target parameters that are subject to change.

## Bt829B/827B

#### VideoStreamII Decoders

## **Bt829B**– Video Capture Processor and Scaler for TV/VCR Analog Input

#### Bt827B- Composite Video and S-Video Decoder

The Bt829B and Bt827B VideoStream™ Decoders are a family of single-chip, pinand register-compatible, composite NTSC/PAL/SECAM video and S-Video decoders. They are also pin and register backward compatible with the Bt829A/827A family of products. Low operating power consumption and power-down capability make them ideal low-cost solutions for PC video capture applications on both desktop and portable system platforms with a 3.3 V digital I/O interface. They support square pixel and CCIR601 resolutions for NTSC, PAL, and SECAM video. They have a flexible pixel port which supports a variety of system interface configurations, and they are offered in a 100-pin Plastic Quad Flat Pack (PQFP).

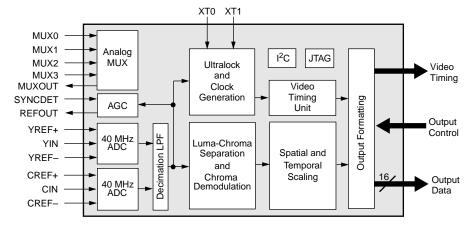

#### **Functional Block Diagram**

#### **Distinguishing Features**

- Single-chip composite/S-Video NTSC/PAL/ SECAM to YCrCb digitizer

- On-chip Ultralock™

- Square Pixel and CCIR601 Resolution for:

- NTSC (M)

- NTSC (M) without 7.5IRE pedestal

- PAL (B, D, G, H, I, M, N, N combination)

- SECAM

- · Chroma comb filter

- Arbitrary horizontal and 5-tap vertical filtered scaling

- · Hardware closed-caption decoder

- Vertical Blanking Interval (VBI) data pass-through

- Arbitrary temporal decimation for a reduced frame-rate video sequence

- Programmable hue, brightness, saturation, and contrast

- User-programmable cropping of the video window

- 2x oversampling to simplify external analog filtering

- Two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus interface

- 8- or 16-bit pixel interface

- YCrCb (4:2:2) output format

- Software selectable four-input analog MUX

- · 4 fully programmable GPIO bits

- Auto NTSC/PAL format detect

- Automatic Gain Control (AGC)

- 3.3 V I/O

- Typical power consumption 0.85 W

- IEEE 1149.1 Joint Test Action Group (JTAG) interface

- 100-pin PQFP

#### **Related Products**

Bt829A, Bt856/857, Bt864A/865A, Bt864/ 865, Bt852

#### **Applications**

- · Multimedia

- Image processing

- · Desktop video

- · Video phone

- Teleconferencing

- Interactive video

#### **Ordering Information**

| Model Number | Package                               | Ambient Temperature Range |

|--------------|---------------------------------------|---------------------------|

| Bt829BKRF    | 100-Pin Plastic Quad Flat Pack (PQFP) | 0°C to +70°C              |

| Bt827BKRF    | 100-Pin Plastic Quad Flat Pack (PQFP) | 0°C to +70°C              |

Copyright © 1998 Rockwell Semiconductor Systems, Inc. All rights reserved.

Print date: March 1998

Rockwell Semiconductor Systems, Inc. reserves the right to make changes to its products or specifications to improve performance, reliability, or manufacturability. Information furnished is believed to be accurate and reliable. However, no responsibility is assumed for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by its implication or otherwise under any patent or intellectual property rights of Rockwell Semiconductor Systems, Inc.

Rockwell Semiconductor Systems, Inc. products are not designed or intended for use in life support appliances, devices, or systems where malfunction of a Rockwell Semiconductor Systems, Inc. product can reasonably be expected to result in personal injury or death. Rockwell Semiconductor Systems, Inc. customers using or selling Rockwell Semiconductor Systems, Inc. products for use in such applications do so at their own risk and agree to fully indemnify Rockwell Semiconductor Systems, Inc. for any damages resulting from such improper use or sale.

Bt is a registered trademark of Rockwell Semiconductor Systems, Inc. SLC<sup>®</sup> is a registered trademark of AT&T Technologies, Inc. Product names or services listed in this publication are for identification purposes only, and may be trademarks or registered trademarks of their respective companies. All other marks mentioned herein are the property of their respective holders.

Specifications are subject to change without notice.

PRINTED IN THE UNITED STATES OF AMERICA

## **Table of Contents**

| ist of Figures                                               | Vİİ |

|--------------------------------------------------------------|-----|

| ist of Tables                                                | ix  |

| .0 Functional Description                                    | 1   |

| 1.1 Functional Overview                                      | 1   |

| 1.1.1 Bt829B Video Capture Processor for TV/VCR Analog Input | 3   |

| 1.1.2 Bt827B Composite/S-Video Decoder                       | 3   |

| 1.1.3 Bt829B Architecture and Partitioning                   | 4   |

| 1.1.4 UltraLock                                              | 4   |

| 1.1.5 Scaling and Cropping                                   |     |

| 1.1.6 Input Interface                                        |     |

| 1.1.7 Output Interface                                       |     |

| 1.1.8 VBI Data Pass-Through                                  |     |

| 1.1.9 Closed Caption Decoding                                |     |

| 1.1.10 I <sup>2</sup> C Interface                            |     |

| 1.2 Pin Descriptions                                         | 7   |

| 1.3 Differences Between Bt829A/827A and Bt829B/827B          | 12  |

| 1.4 UltraLock                                                | 14  |

| 1.4.1 The Challenge                                          | 14  |

| 1.4.2 Operation Principles of UltraLock                      | 14  |

| 1.5 Composite Video Input Formats                            | 16  |

| 1.6 Y/C Separation and Chroma Demodulation                   | 18  |

| 1.7 Video Scaling, Cropping, and Temporal Decimation         | 20  |

| 1.7.1 Horizontal and Vertical Scaling                        | 20  |

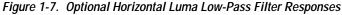

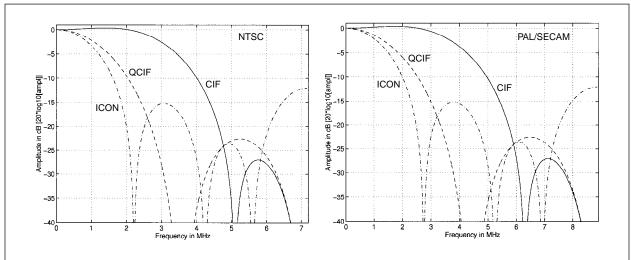

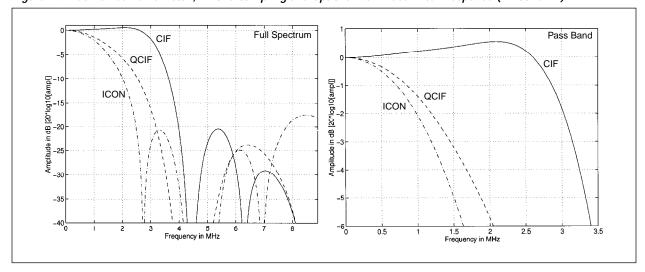

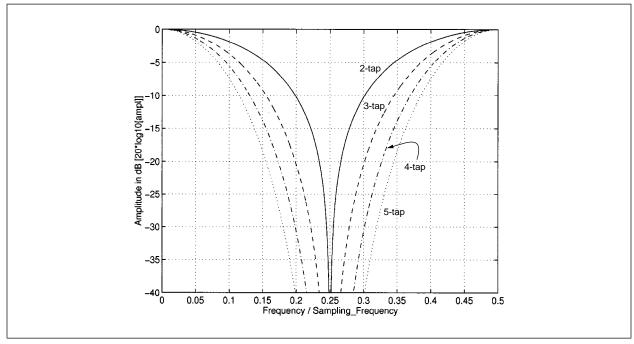

| 1.7.2 Luminance Scaling                                      | 20  |

| 1.7.3 Peaking                                                | 23  |

| 1.7.4 Chrominance Scaling                                    |     |

| 1.7.5 Scaling Registers                                      | 25  |

| 1.7.6 Image Cropping                                         |     |

| 1.7.7 Cropping Registers                                     |     |

| 1.7.8 Temporal Decimation                                    | 32  |

| 1.8 Video Adjustments                                                                                           | <br>33 |

|-----------------------------------------------------------------------------------------------------------------|--------|

| 1.8.1 The Hue Adjust Register (HUE)                                                                             | <br>33 |

| 1.8.2 The Contrast Adjust Register (CONTRAST)                                                                   | <br>33 |

| 1.8.3 The Saturation Adjust Registers (SAT_U, SAT_V)                                                            | <br>33 |

| 1.8.4 The Brightness Register (BRIGHT)                                                                          | <br>33 |

| 1.9 Bt829B VBI Data Output Interface                                                                            | <br>34 |

| 1.9.1 Introduction                                                                                              | <br>34 |

| 1.9.2 Overview                                                                                                  | <br>34 |

| 1.9.3 Functional Description                                                                                    | <br>36 |

| 1.9.4 VBI Line Output Mode                                                                                      | <br>36 |

| 1.9.5 VBI Frame Output Mode                                                                                     | <br>40 |

| 1.10 Closed Captioning and Extended Data Services Decoding                                                      | <br>41 |

| 1.10.1 Automatic Chrominance Gain Control                                                                       | <br>43 |

| 1.10.2 Low Color Detection and Removal                                                                          | <br>43 |

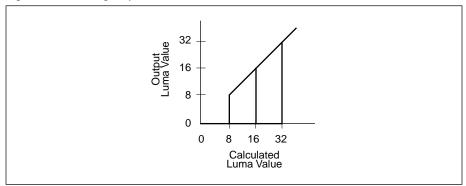

| 1.10.3 Coring                                                                                                   | <br>44 |

| 2.0 Electrical Interfaces                                                                                       | 15     |

|                                                                                                                 |        |

| 2.1 Input Interface                                                                                             |        |

| 2.1.1 Analog Signal Selection                                                                                   |        |

| 2.1.2 Multiplexer Considerations                                                                                |        |

| 2.1.3 Autodetection of NTSC or PAL/SECAM Video                                                                  |        |

| 2.1.4 Flash A/D Converters                                                                                      |        |

| 2.1.5 A/D Clamping                                                                                              |        |

| 2.1.6 Power-Up Operation                                                                                        |        |

| 2.1.7 Automatic Gain Controls (AGC)                                                                             |        |

| 2.1.8 Crystal Inputs and Clock Generation                                                                       |        |

| 2.1.9 2X Oversampling and Input Filtering                                                                       |        |

| 2.2 Output Interface                                                                                            |        |

| 2.2.1 Output Interfaces                                                                                         |        |

| 2.2.2 YCrCb Pixel Stream Format, SPI Mode, 8- and 16-Bit Formats 2.2.3 Synchronous Pixel Interface (SPI Mode 1) |        |

| ` , , ,                                                                                                         |        |

| 2.2.4 Synchronous Pixel Interface (SPI Mode 2, ByteStream)                                                      |        |

| · · · · · · · · · · · · · · · · · · ·                                                                           |        |

| 2.3 I <sup>2</sup> C Interface                                                                                  |        |

| 2.3.1 Starting and Stopping                                                                                     |        |

| 2.3.3 Reading and Writing                                                                                       |        |

| 2.3.4 Software Reset                                                                                            |        |

|                                                                                                                 |        |

| 2.4 JTAG Interface                                                                                              |        |

| 2.4.1 Need for Functional Verification                                                                          |        |

| 2.4.2 JTAG Approach to Testability                                                                              |        |

| 2.4.3 Optional Device ID Register                                                                               |        |

| 2.4.4 Verification with the Tap Controller                                                                      | <br>69 |

| 7 4 3 LAGUIUE DAIA LINUU                                                                                        | 117    |

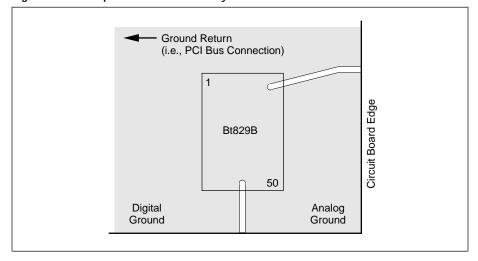

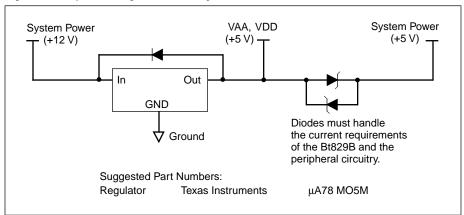

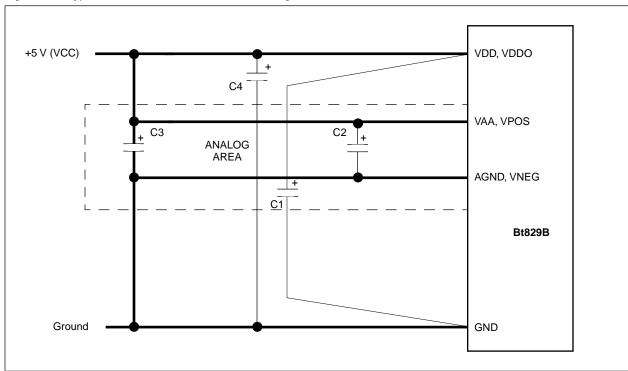

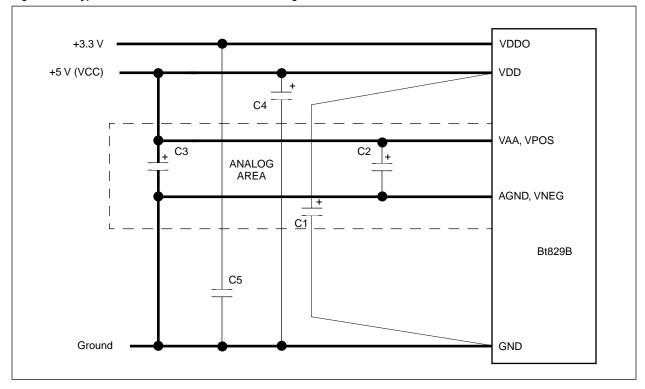

| 3.0 PC Board  | Layout Considerations                                                 | . 73 |

|---------------|-----------------------------------------------------------------------|------|

| 3.1 Gro       | ound Planes                                                           | . 73 |

|               | 3.1.1 Power Planes                                                    | . 74 |

|               | 3.1.2 Supply Decoupling                                               | . 75 |

|               | 3.1.3 Digital Signal Interconnect                                     |      |

|               | 3.1.4 Analog Signal Interconnect                                      |      |

|               | 3.1.5 Latch-up Avoidance                                              | . 77 |

| 4.0 Control R | Register Definitions                                                  | . 79 |

|               | 0x00—Device Status Register (STATUS)                                  | . 81 |

|               | 0x01—Input Format Register (IFORM)                                    | . 82 |

|               | 0x02—Temporal Decimation Register (TDEC)                              | . 83 |

|               | 0x03—MSB Cropping Register (CROP)                                     |      |

|               | 0x04—Vertical Delay Register, Lower Byte (VDELAY_LO)                  |      |

|               | 0x05—Vertical Active Register, Lower Byte (VACTIVE_LO)                |      |

|               | 0x06—Horizontal Delay Register, Lower Byte (HDELAY_LO)                | . 84 |

|               | 0x07—Horizontal Active Register, Lower Byte (HACTIVE_LO)              | . 85 |

|               | 0x08—Horizontal Scaling Register, Upper Byte (HSCALE_HI)              | . 85 |

|               | 0x09—Horizontal Scaling Register, Lower Byte (HSCALE_LO)              | . 85 |

|               | 0x0A—Brightness Control Register (BRIGHT)                             | . 86 |

|               | 0x0B—Miscellaneous Control Register (CONTROL)                         | . 87 |

|               | 0x0C—Luma Gain Register, Lower Byte (CONTRAST_LO)                     | . 88 |

|               | 0x0D—Chroma (U) Gain Register, Lower Byte (SAT_U_LO)                  | . 89 |

|               | 0x0E—Chroma (V) Gain Register, Lower Byte (SAT_V_LO)                  | . 90 |

|               | 0x0F—Hue Control Register (HUE)                                       | . 91 |

|               | 0x10—SC Loop Control (SCLOOP)                                         | . 92 |

|               | 0x11—White Crush Up Count Register (WC_UP)                            | . 93 |

|               | 0x12—Output Format Register (OFORM)                                   | . 94 |

|               | 0x13—Vertical Scaling Register, Upper Byte (VSCALE_HI)                | . 95 |

|               | 0x14—Vertical Scaling Register, Lower Byte (VSCALE_LO)                | . 96 |

|               | 0x15—Test Control Register (TEST)                                     | . 96 |

|               | 0x16—Video Timing Polarity Register (VPOLE)                           | . 97 |

|               | 0x17—ID Code Register (IDCODE)                                        | . 98 |

|               | 0x18—AGC Delay Register (ADELAY)                                      | . 98 |

|               | 0x19—Burst Delay Register (BDELAY)                                    | . 99 |

|               | 0x1A—ADC Interface Register (ADC)                                     | 100  |

|               | 0x1B—Video Timing Control (VTC)                                       | 101  |

|               | 0x1C—Extended Data Service/Closed Caption Status Register (CC_STATUS) | 103  |

|               | 0x1D—Extended Data Service/Closed Caption Data Register (CC_DATA)     | 104  |

|               | 0x1E—White Crush Down Count Register (WC_DN)                          | 104  |

|               | 0x1F—Software Reset Register (SRESET)                                 | 105  |

|               | 0x3F—Programmable I/O Register (P_IO)                                 | 105  |

Table of Contents Bt829B/827B

| 5.0 Pa | rametric Information            | 107 |

|--------|---------------------------------|-----|

|        | 5.1 DC Electrical Parameters    | 107 |

|        | 5.2 AC Electrical Parameters    | 110 |

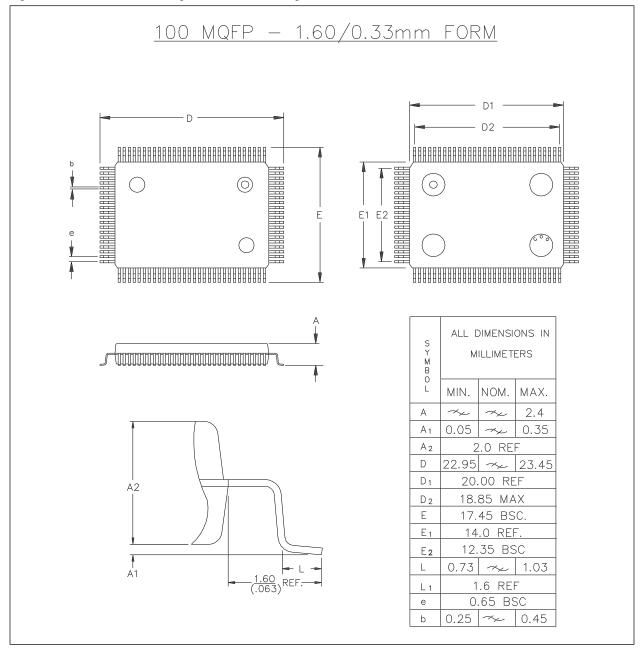

|        | 5.3 Package Mechanical Drawings | 114 |

|        | 5 4 Revision History            | 115 |

## **List of Figures**

| Figure 1-1.  | Bt829B/827B Detailed Block Diagram                                                     | 2  |

|--------------|----------------------------------------------------------------------------------------|----|

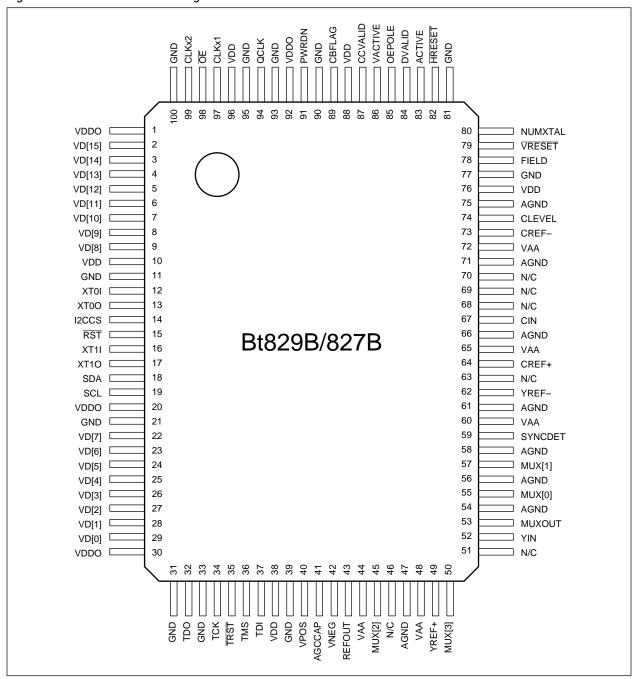

| Figure 1-2.  | Bt829B/827B Pinout Diagram                                                             | 7  |

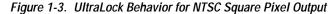

| Figure 1-3.  | UltraLock Behavior for NTSC Square Pixel Output                                        | 15 |

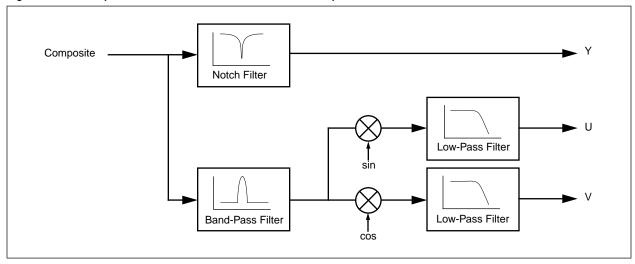

| Figure 1-4.  | Y/C Separation and Chroma Demodulation for Composite Video                             | 18 |

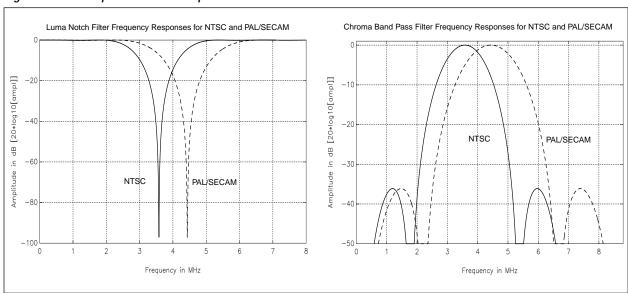

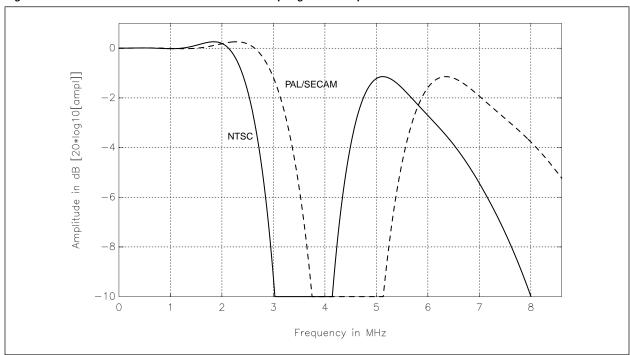

| Figure 1-5.  | Y/C Separation Filter Responses                                                        | 18 |

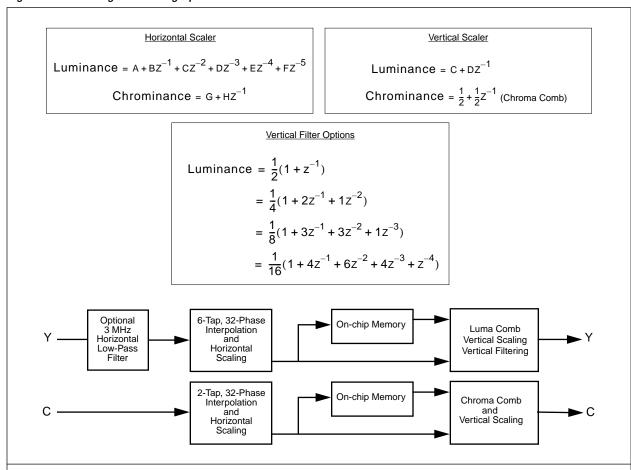

| Figure 1-6.  | Filtering and Scaling Operations                                                       | 19 |

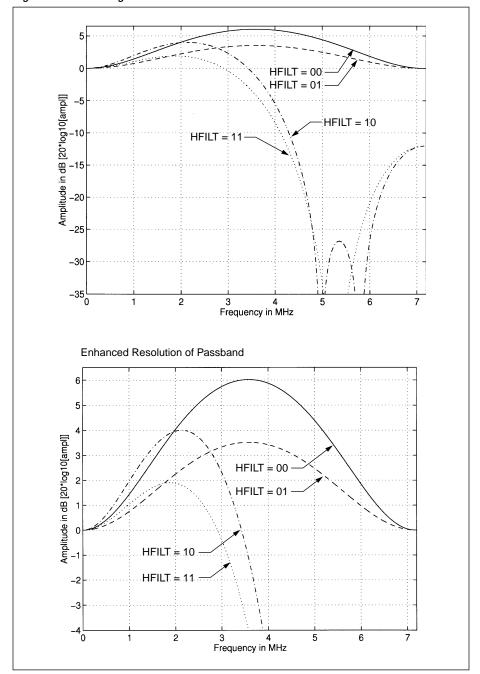

| Figure 1-7.  | Optional Horizontal Luma Low-Pass Filter Responses                                     | 20 |

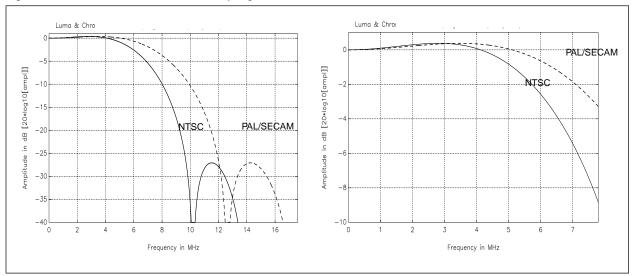

| Figure 1-8.  | Combined Luma Notch, 2x Oversampling and Optional Low-Pass Filter Response (NTSC)      | 21 |

| Figure 1-9.  | Combined Luma Notch, 2x Oversampling and Optional Low-Pass Filter Response (PAL/SECAM) | 21 |

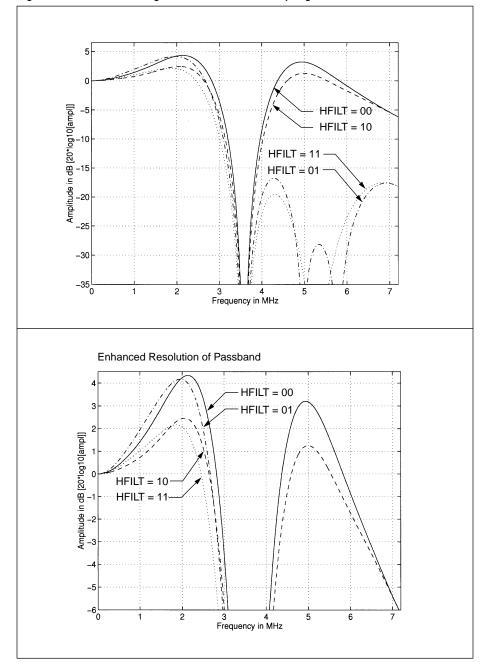

| Figure 1-10. | Frequency Responses for the Four Optional Vertical Luma Low-Pass Filters               | 22 |

| Figure 1-11. | Combined Luma Notch and 2x Oversampling Filter Response                                | 22 |

| Figure 1-12. | Peaking Filters                                                                        | 23 |

| Figure 1-13. | Luma Peaking Filters with 2x Oversampling Filter and Luma Notch                        | 24 |

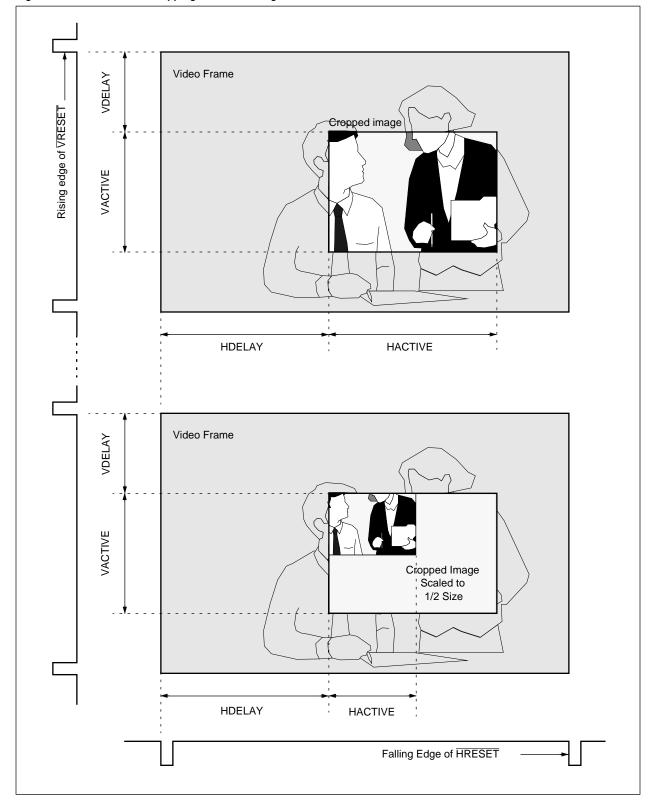

| Figure 1-14. | Effect of the Cropping and Active Registers                                            | 29 |

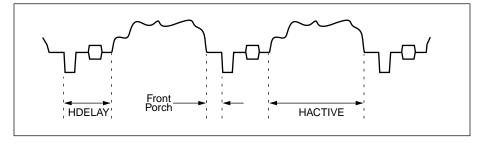

| Figure 1-15. | Regions of the Video Signal                                                            | 30 |

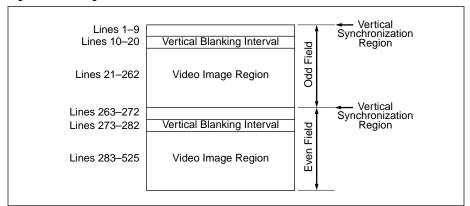

| Figure 1-16. | Regions of the Video Frame                                                             | 34 |

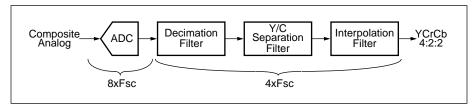

| Figure 1-17. | Bt829B YCrCb 4:2:2 Data Path                                                           | 34 |

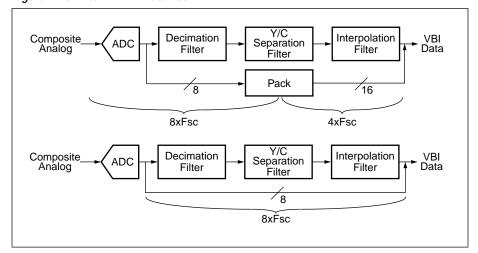

| Figure 1-18. | Bt829B VBI Data Path                                                                   | 35 |

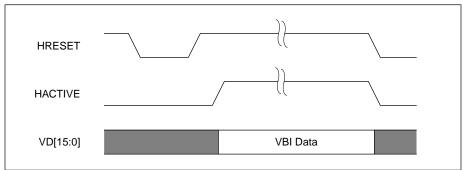

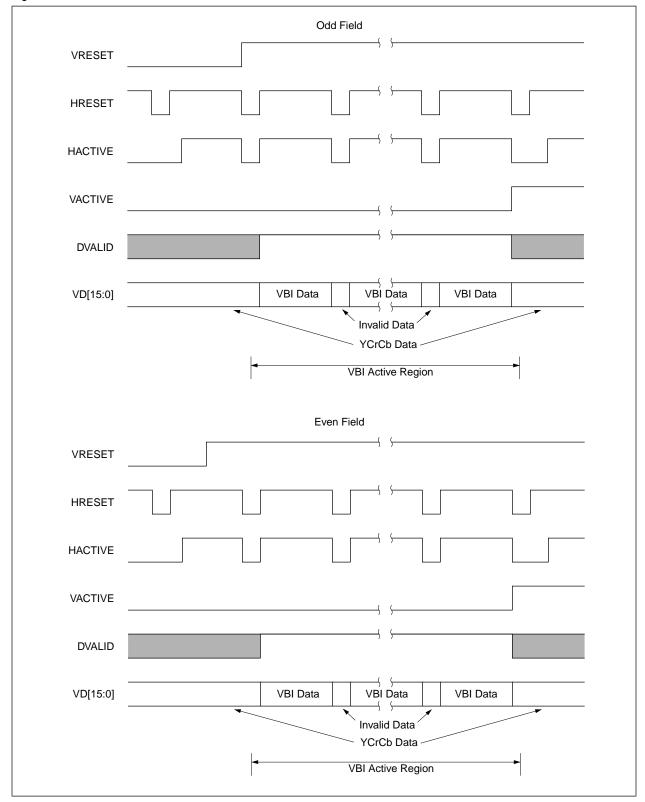

| Figure 1-19. | VBI Line Output Mode Timing                                                            | 36 |

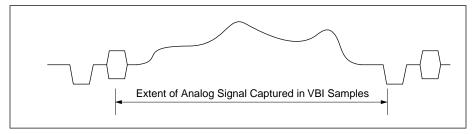

| Figure 1-20. | VBI Sample Region                                                                      | 37 |

| Figure 1-21. | Location of VBI Data                                                                   | 38 |

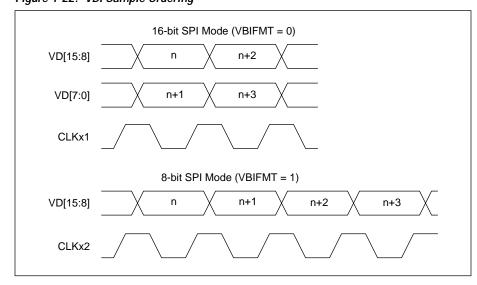

| Figure 1-22. | VBI Sample Ordering                                                                    | 39 |

| Figure 1-23. | CC/EDS Data Processing Path                                                            | 41 |

| Figure 1-24. | CC/EDS Incoming Signal                                                                 | 41 |

| Figure 1-25. | Closed Captioning/Extended Data Services FIFO                                          | 42 |

| Figure 1-26. | Coring Map                                                                             | 44 |

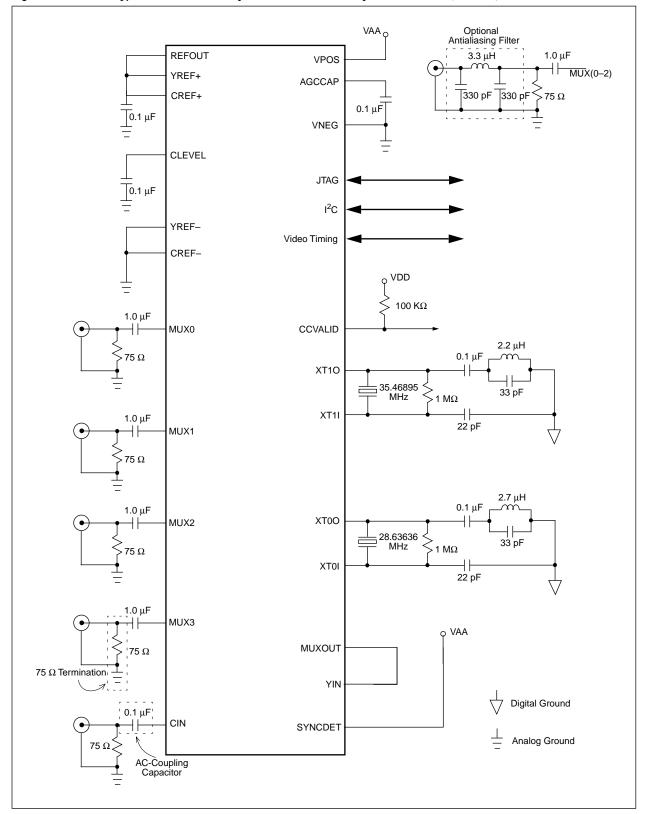

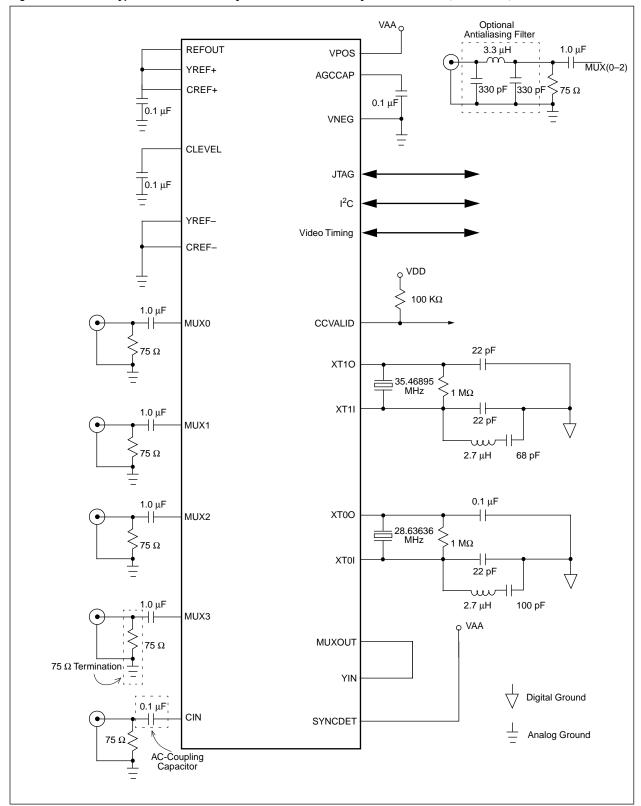

| Figure 2-1.  | Bt829B Typical External Circuitry with Third Overtone Crystal Oscillators (5 V VDD)    | 48 |

| Figure 2-2.  | Bt829B Typical External Circuitry with Third Overtone Crystal Oscillators (3.3V VDDO)  | 49 |

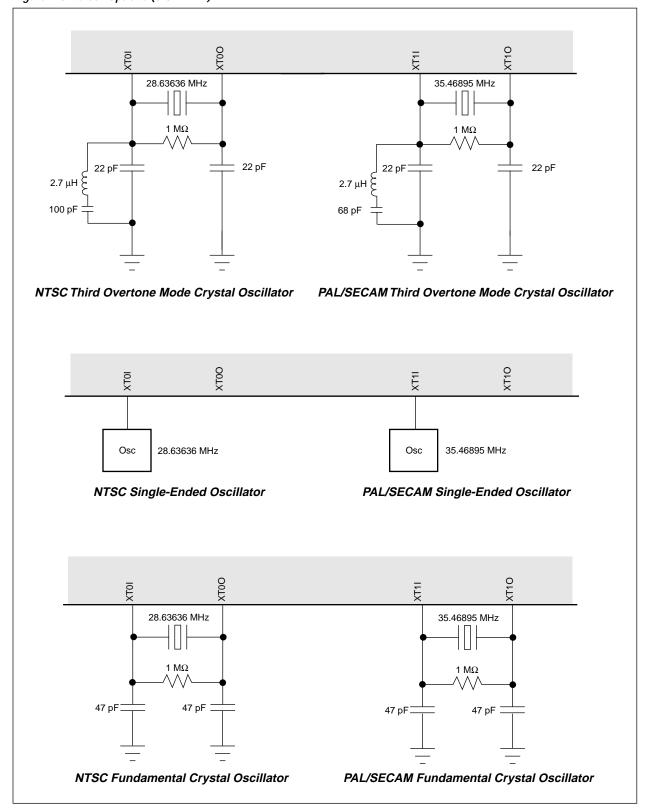

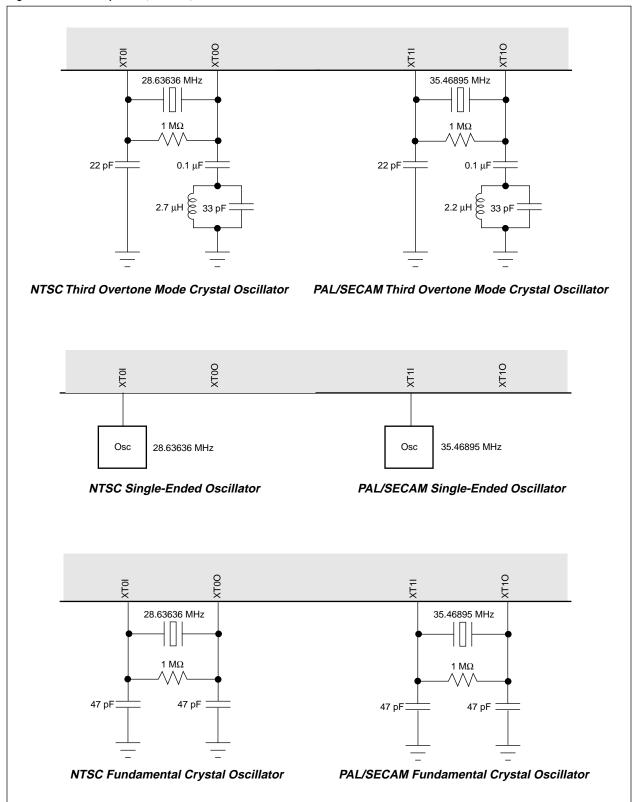

| Figure 2-3.  | Clock Options (3.3 V VDD)                                                              | 52 |

| Figure 2-4.  | Clock Options (5 V VDD)                                                                | 53 |

| Figure 2-5.  | Luma and Chroma 2x Oversampling Filter                                                 | 54 |

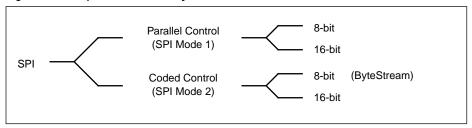

| Figure 2-6.  | Output Mode Summary                                                                    | 55 |

|              |                                                                                        |    |

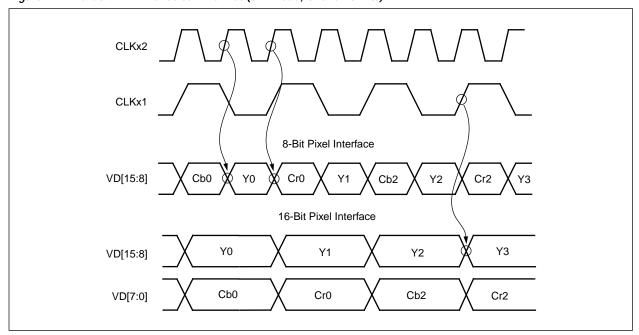

| Figure 2-7.  | YCrCb 4:2:2 Pixel Stream Format (SPI Mode, 8- and 16-Bits)                    | 56  |

|--------------|-------------------------------------------------------------------------------|-----|

| Figure 2-8.  | Bt829B/827B Synchronous Pixel Interface, Mode 1 (SPI-1)                       | 57  |

| Figure 2-9.  | Basic Timing Relationships for SPI Mode 1                                     | 57  |

| Figure 2-10. | Data Output in SPI Mode 2 (ByteStream)                                        | 59  |

| Figure 2-11. | Video Timing in SPI Modes 1 and 2                                             | 60  |

| Figure 2-12. | Horizontal Timing Signals in the SPI Modes                                    | 61  |

| Figure 2-13. | The Relationship between SCL and SDA                                          | 62  |

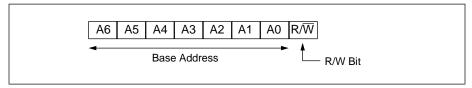

| Figure 2-14. | I2C Slave Address Configuration                                               | 63  |

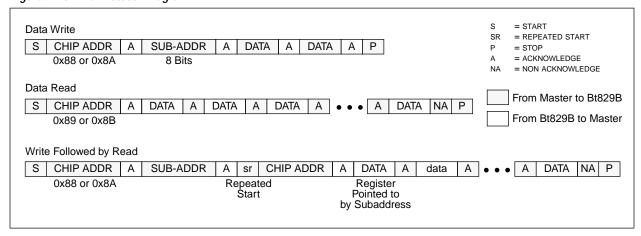

| Figure 2-15. | I2C Protocol Diagram                                                          | 66  |

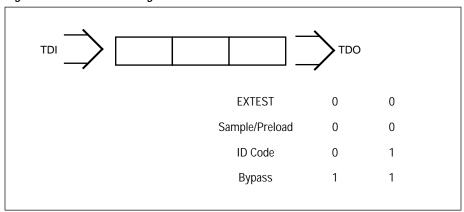

| Figure 2-16. | Instruction Register                                                          | 68  |

| Figure 3-1.  | Example of Ground Plane Layout                                                | 73  |

| Figure 3-2.  | Optional Regulator Circuitry                                                  | 74  |

| Figure 3-3.  | Typical Power and Ground                                                      |     |

|              | Connection Diagram and Parts List for 5 V I/O Mode                            | .75 |

| Figure 3-4.  | Typical Power and Ground Connection Diagram and Parts List for 3.3 V I/O Mode | .76 |

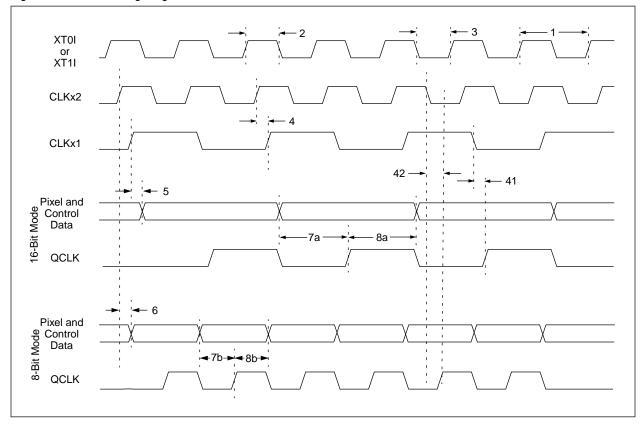

| Figure 5-1.  | Clock Timing Diagram                                                          | 112 |

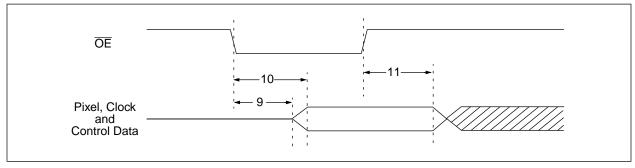

| Figure 5-2.  | Output Enable Timing Diagram                                                  | 113 |

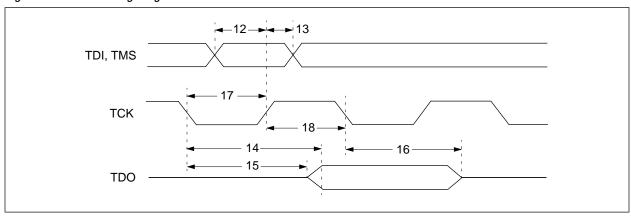

| Figure 5-3.  | JTAG Timing Diagram                                                           | 113 |

| Figure 5-4.  | 100-Pin PQFP Package Mechanical Drawing                                       | 114 |

## **List of Tables**

| Table 1-1.  | VideoStream II Features Options                           | . 3 |

|-------------|-----------------------------------------------------------|-----|

| Table 1-2.  | Pin Descriptions Grouped By Pin Function                  | . 8 |

| Table 1-3.  | Pin Function Differences                                  | 12  |

| Table 1-4.  | 3.3 V Pin Output                                          | 12  |

| Table 1-5.  | 3.3 V Pin Input                                           | 13  |

| Table 1-6.  | Video Input Formats Supported by the Bt829B               | 16  |

| Table 1-7.  | Register Values for Video Input Formats                   | 17  |

| Table 1-8.  | Scaling Ratios for Popular Formats Using Frequency Values | 26  |

| Table 2-1.  | Pixel/Pin Map                                             | 56  |

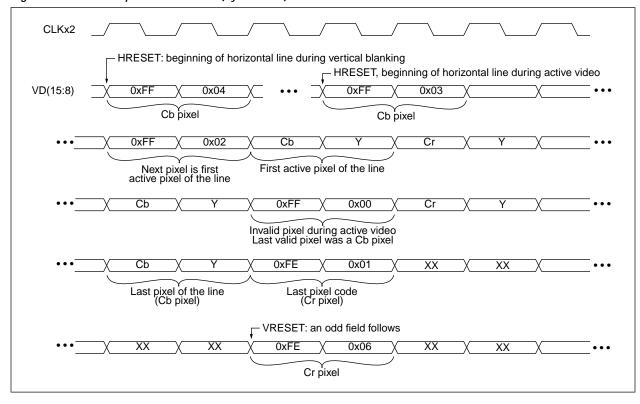

| Table 2-2.  | Description of the Control Codes in the Pixel Stream      | 58  |

| Table 2-3.  | Data Output Ranges                                        | 61  |

| Table 2-4.  | Bt829B Address Matrix                                     | 63  |

| Table 2-5.  | Example I2C Data Transactions                             | 64  |

| Table 2-6.  | Device Identification Register                            | 68  |

| Table 4-1.  | Register Map                                              | 79  |

| Table 5-1.  | Recommended Operating Conditions                          | 107 |

| Table 5-2.  | Absolute Maximum Ratings                                  | 108 |

| Table 5-3.  | DC Characteristics (3.3 V digital I/O operation)          | 108 |

| Table 5-4.  | DC Characteristics (5 V only operation)                   | 109 |

| Table 5-5.  | Clock Timing Parameters                                   | 110 |

| Table 5-6.  | Power Supply Current Parameters                           | 112 |

| Table 5-7.  | Output Enable Timing Parameters                           | 112 |

| Table 5-8.  | JTAG Timing Parameters                                    | 113 |

| Table 5-9.  | Decoder Performance Parameters                            | 113 |

| Table 5-10. | Bt829B Datasheet Revision History                         | 115 |

List of Tables Bt829B/827B

## 1.0 Functional Description

#### 1.1 Functional Overview

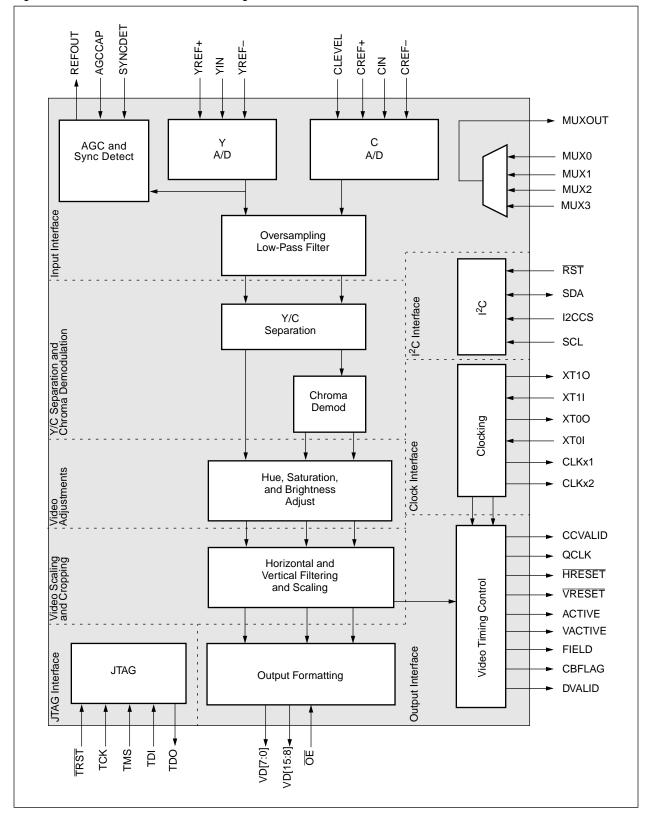

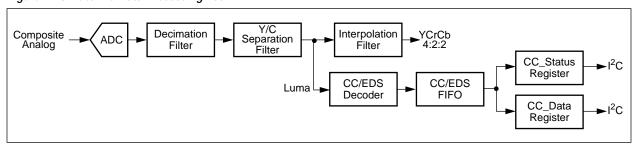

Rockwell's VideoStream II products are a family of single-chip, pin-and register-compatible solutions for processing analog NTSC/PAL/SECAM video into digital 4:2:2 YCrCb video. They provide a comprehensive choice of capabilities to enable the feature set and cost to be tailored to different system hardware configurations. All solutions are housed in a 100-pin PQFP package. A detailed block diagram is shown in Figure 1-1.

1.1 Functional Overview VideoStream II Decoders

Figure 1-1. Bt829B/827B Detailed Block Diagram

1.1 Functional Overview

#### 1.1.1 Bt829B Video Capture Processor for TV/VCR Analog Input

The Bt829B Video Capture Processor is a fully integrated single-chip decoding and scaling solution for analog NTSC/PAL/SECAM input signals from TV tuners, VCRs, cameras, and other sources of composite or Y/C video. It is the second generation front-end input solution for low-cost PC video/graphics systems that deliver complete integration and high-performance video synchronization, Y/C separation, and filtered scaling. The Bt829B has all the mixed signal and DSP circuitry required to convert an analog composite waveform into a scaled digital video stream, supporting a variety of video formats, resolutions, and frame rates.

### 1.1.2 Bt827B Composite/S-Video Decoder

The Bt827B provides full composite and S-Video capability along with horizontal scaling. Vertical scaling can only be implemented by line-dropping.

The Synchronous Pixel Interface (SPI) is common to both pin-compatible devices, which enables implementation of a single system hardware design. Similarly, a common I<sup>2</sup>C register set allows a single piece of driver code to be written for software control of both options. Table 1-1 compares Bt829B and Bt827B features.

Table 1-1. VideoStream II Features Options

| Feature Options                | Bt829B | Bt827B |

|--------------------------------|--------|--------|

| Composite Video Decoding       | Х      | X      |

| S-Video Decoding               | X      | X      |

| SECAM Video                    | X      | X      |

| Hardware Closed Caption Decode | X      | X      |

| 3.3 V Digital I/O              | X      | X      |

| Filtered Vertical Scaling      | X      |        |

1.1 Functional Overview VideoStream II Decoders

#### 1.1.3 Bt829B Architecture and Partitioning

The Bt829B has been developed to provide the most cost-effective, high-quality video input solution. It is used for low-cost multimedia subsystems that integrate both graphics display and video capabilities. The feature set of the Bt829B supports a video/graphics system partitioning which optimizes the total cost of a system configured both with and without video capture capabilities. This enables system vendors to easily offer products with various levels of video support using a single base-system design.

As graphics chip vendors move from graphics-only to video/graphics coprocessors, and eventually to single-chip video/graphics processor implementations, the ability to efficiently use silicon and package pins to support both graphics acceleration, video playback acceleration, and video capture becomes critical. This problem becomes more acute as the race towards higher performance graphics requires more and more package pins to be consumed for wide 64-bit memory interfaces and glueless local bus interfaces.

The Bt829B minimizes the cost of video capture function integration in two ways. First, recognizing that YCrCb to RGB color space conversion is a required feature of multimedia controllers for acceleration of digital video playback, the Bt829B avoids redundant functionality and allows the downstream controller to perform this task. Second, the Bt829B can minimize the number of interface pins required by a downstream multimedia controller in order to keep package costs to a minimum. The Bt829B can also output all timing and data signals at 3.3 V levels.

Controller systems designed to take advantage of these features allow video capture capability to be added to the base system in a modular fashion using only a single Integrated Circuit (IC).

The Bt827B is targeted at system configurations using video processors which typically integrate the scaling function.

#### 1.1.4 UltraLock

The Bt829B and Bt827B employ a proprietary technique known as UltraLock to lock to the incoming analog video signal. It will always generate the required number of pixels per line from an analog source in which the line length can vary by as much as a few microseconds. UltraLock's digital locking circuitry enables the VideoStream decoders to quickly and accurately lock on to video signals, regardless of their source. Since the technique is completely digital, UltraLock can recognize unstable signals caused by VCR headswitches or any other deviation and adapt the locking mechanism to accommodate the source. UltraLock uses nonlinear techniques which are difficult, if not impossible, to implement in genlock systems. And unlike linear techniques, it adapts the locking mechanism automatically.

1.1 Functional Overview

#### 1.1.5 Scaling and Cropping

The Bt829B can reduce the video image size in both horizontal and vertical directions independently using arbitrarily selected scaling ratios. The X and Y dimensions can be scaled down to one-sixteenth of the full resolution. Horizontal scaling is implemented with a 6-tap interpolation filter, while up to 5-tap interpolation is used for vertical scaling with a line store. The Bt827B supports vertical scaling by line-dropping.

The video image can be arbitrarily cropped by programming the ACTIVE flag to reduce the number of active scan lines and active horizontal pixels per line.

The Bt829B and Bt827B also support a temporal decimation feature that reduces video bandwidth by allowing frames or fields to be dropped from a video sequence at regular but arbitrarily selected intervals.

#### 1.1.6 Input Interface

Analog video signals are input to the Bt829B/827B via a four-input multiplexer that can select between four composite source inputs or between three composite and a single S-Video input source. When an S-Video source is input to the Bt829B, the luma component is fed through the input analog multiplexer, and the chroma component is fed directly into the C-input pin. An AGC circuit enables the Bt829B/827B to compensate for reduced amplitude in the analog signal input.

The clock signal interface consists of two pairs of pins for crystal connection and two clock output pins. One pair of crystal pins is for connection to a 28.64 MHz (8\*NTSC Fsc) crystal which is selected for NTSC operation. The other is for PAL operation with a 35.47 MHz (8\*PAL Fsc) crystal. Either of the two crystal frequencies can be selected to generate CLKx1 and CLKx2 output signals. CLKx2 operates at the full crystal frequency (8\*Fsc), whereas CLKx1 operates at half the crystal frequency (4\*Fsc). Either fundamental or third harmonic crystals may be used. Alternatively, CMOS oscillators may be used.

#### 1.1.7 Output Interface

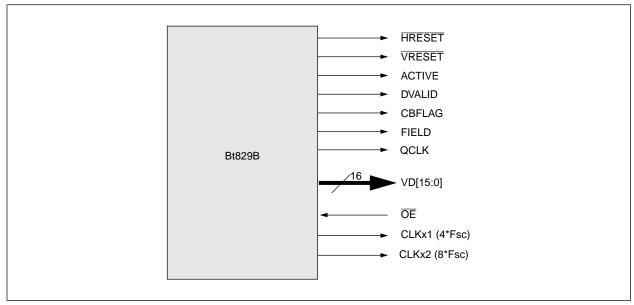

The Bt829B and Bt827B support a Synchronous Pixel Interface (SPI) mode.

The SPI supports a YCrCb 4:2:2 data stream over an 8- or 16-bit-wide path. When the pixel output port is configured to operate 8-bits wide, 8 bits of chrominance data are output on the first clock cycle followed by 8 bits of luminance data on the next clock cycle for each pixel. Two clocks are required to output one pixel in this mode, thus a 2x clock is used to output the data.

The Bt829B/827B outputs all horizontal and vertical blanking pixels in addition to the active pixels synchronous with CLKX1 (16-bit mode) or CLKX2 (8-bit mode). It is also possible to insert control codes into the pixel stream using chrominance and luminance values that are outside the allowable chroma and luma ranges. These control codes can be used to flag video events such as ACTIVE, HRESET, and VRESET. Decoding these video events downstream enables the video controller to eliminate pins required for the corresponding video control signals. Both Bt829B and Bt827B can output (or receive) all digital timing, clock, and data signals at either 5 V or 3.3 V levels for connection to 5 V or 3.3 V graphics/video controllers.

♠ Rockwell

D829BDSA

5

1.1 Functional Overview

VideoStream II Decoders

#### 1.1.8 VBI Data Pass-Through

The Bt829B/827B provides VBI data passthrough capability. The VBI region ancillary data is captured by the video decoder and made available to the system for subsequent software processing. The Bt829B/827B may operate in a VBI Line Output mode, in which the VBI data is only made available during select lines. This mode of operation is intended to enable capture of VBI lines containing ancillary data as well as processing normal YCrCb video image data. In addition, the Bt829B/827B supports a VBI Frame Output mode, in which every line in the video signal is treated as if it was a vertical interval line and no image data is output. This mode of operation is designed for use in still-frame capture/processing applications.

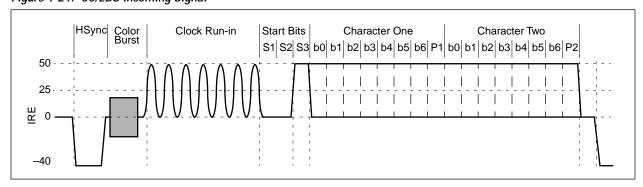

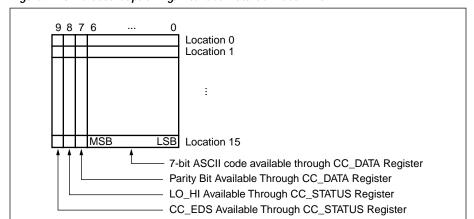

#### 1.1.9 Closed Caption Decoding

The Bt829B and Bt827B provide a Closed Captioning (CC) and Extended Data Services (EDS) decoder. Data presented to the video decoder on the CC and EDS lines is decoded and made available to the system through the CC\_DATA and CCSTATUS registers.

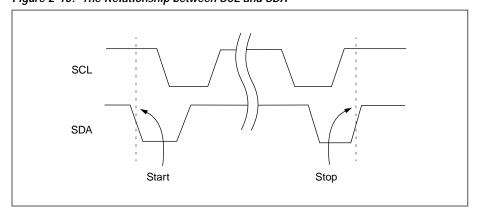

#### 1.1.10 I<sup>2</sup>C Interface

The Bt829B/827B registers are accessed via a two-wire I<sup>2</sup>C interface. The Bt829B/827B operates as a slave device. Serial clock and data lines, SCL and SDA, transfer data from the bus master at a rate of 100 Kbits/s. Chip select and reset signals are also available to select one of two possible Bt829B/827B devices in the same system and to set the registers to their default values.

1.2 Pin Descriptions

### 1.2 Pin Descriptions

Figure 1-2 details the Bt829B and Bt827B pinout. Table 1-2 provides pin numbers, names, input and output functions, and descriptions.

Figure 1-2. Bt829B/827B Pinout Diagram

Table 1-2. Pin Descriptions Grouped By Pin Function (1 of 4)

| Pin #             | I/O              | Pin Name | Description                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|-------------------|------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                   | Input Stage Pins |          |                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 45, 50, 55,<br>57 | I                | MUX[3:0] | Analog composite video inputs to the on-chip input multiplexer. They are used to select between four composite sources or three composite and one S-Video source. Unused pins should be connected to GND.                                                                                                                                                                                           |  |  |

| 53                | 0                | MUXOUT   | The analog video output of the 4-to-1 multiplexer. Connected to the YIN pin.                                                                                                                                                                                                                                                                                                                        |  |  |

| 52                | I                | YIN      | The analog composite or luma input to the Y-ADC.                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 67                | I                | CIN      | The analog chroma input to the C-ADC.                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 59                | I                | SYNCDET  | The sync stripper input generates timing information for the AGC circuit. Can be optionally connected through a 0.1 $\mu$ F capacitor to the same source as the Y-ADC, to maintain compatibility with Bt829 board layouts. A 1 $M\Omega$ bleeder resistor can be connected to ground, to maintain compatibility with Bt829 board layouts. For new Bt829B designs, this pin may be connected to VAA. |  |  |

| 41                | А                | AGCCAP   | The AGC time constant control capacitor node. Must be connected to a $0.1 \mu F$ capacitor to ground.                                                                                                                                                                                                                                                                                               |  |  |

| 43                | 0                | REFOUT   | Output of the AGC which drives the YREF+ and CREF+ pins.                                                                                                                                                                                                                                                                                                                                            |  |  |

| 49                | А                | YREF+    | The top of the reference ladder of the Y-ADC. This should be connected to REFOUT.                                                                                                                                                                                                                                                                                                                   |  |  |

| 62                | А                | YREF-    | The bottom of the reference ladder of the Y-ADC. This should be connected to analog ground (AGND).                                                                                                                                                                                                                                                                                                  |  |  |

| 64                | А                | CREF+    | The top of the reference ladder of the C-ADC. This should be connected to REFOUT.                                                                                                                                                                                                                                                                                                                   |  |  |

| 73                | А                | CREF-    | The bottom of the reference ladder of the C-ADC. This should be connected to analog ground (AGND).                                                                                                                                                                                                                                                                                                  |  |  |

| 74                | А                | CLEVEL   | An input to provide the DC level reference for the C-ADC. For compatibility with Bt829 board layouts, the 30 k $\Omega$ divider resistors may be maintained. Note: This pin should be left to float for new Bt829B designs.                                                                                                                                                                         |  |  |

| 51                | А                | N/C      | No connect.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 46                | А                | N/C      | No connect.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 63, 68            | А                | N/C      | No connect.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 70                | А                | N/C      | No connect.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 69                | Α                | N/C      | No connect.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                   |                  |          | I <sup>2</sup> C Interface Pins                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 19                | 1                | SCL      | The I <sup>2</sup> C Serial Clock Line.                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 18                | 1/0              | SDA      | The I <sup>2</sup> C Serial Data Line.                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 14                | I                | 12CCS    | The I <sup>2</sup> C Chip Select Input (TTL compatible). This pin selects one of two Bt829B devices in the same system. This pin is internally pulled to ground with an effective 18 K $\Omega$ resistance.                                                                                                                                                                                         |  |  |

| 15                | I                | RST      | Reset Control Input (TTL compatible). A logical 0 for a minimum of four consecutive clock cycles resets the device to its default state. A logical 0 for less than eight XTAL cycles will leave the device in an undetermined state.                                                                                                                                                                |  |  |

1.2 Pin Descriptions

Table 1-2. Pin Descriptions Grouped By Pin Function (2 of 4)

| Pin#                   | I/O | Pin Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Video Timing Unit Pins |     |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

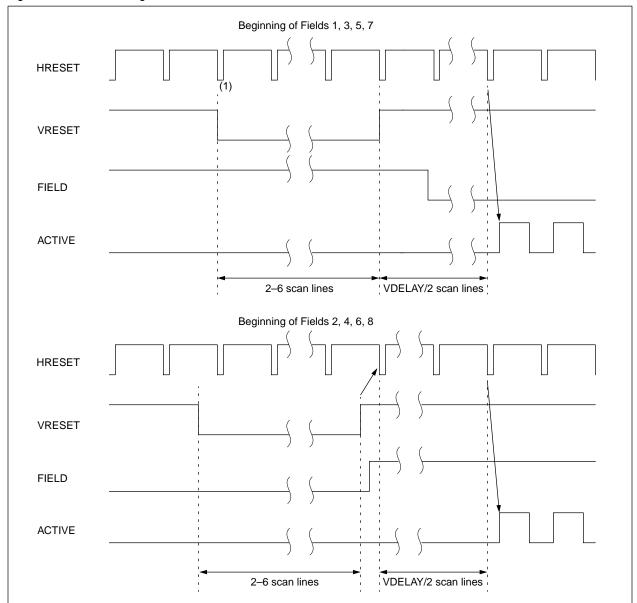

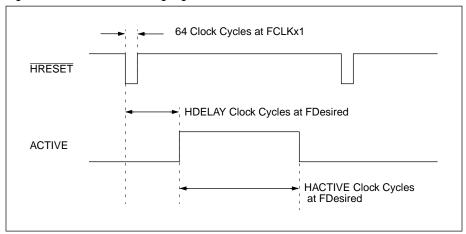

| 82                     | 0   | HRESET   | Horizontal Reset Output (TTL compatible). This signal indicates the beginning of a new line of video. This signal is 64 CLKx1 clock cycles wide. The falling edge of this output indicates the beginning of a new scan line of video. This pin may be defined in pixels as opposed to CLKx1 cycles. Refer to the HSFMT bit in the VTC register. Note: The polarity of this pin is programmable through the VPOLE register.                                                                                                                                                                                                                       |

| 79                     | 0   | VRESET   | Vertical Reset Output (TTL compatible). This signal indicates the beginning of a new field of video. This signal is output coincident with the rising edge of CLKx1, and is normally 6 lines wide. The falling edge of VRESET indicates the beginning of a new field of video.  Note: The polarity of this pin is programmable through the VPOLE register.                                                                                                                                                                                                                                                                                       |

| 83                     | 0   | ACTIVE   | Active Video Output (TTL compatible). This pin can be programmed to output the composite active or horizontal active signal via the VTC register. It is a logical high during the active/viewable periods of the video stream. The active region of the video stream is programmable.  Note: The polarity of this pin is programmable through the VPOLE register.                                                                                                                                                                                                                                                                                |

| 94                     | 0   | QCLK     | Qualified Clock Output. This pin provides a rising edge only during valid, active pixel data. This output is generated from CLKx1 (or CLKx2 in 8-bit mode), DVALID and, if programmed, ACTIVE. The phase of QCLK is inverted from the CLKx1 (or CLKx2) to ensure adequate setup and hold time with respect to the data outputs. QCLK is not output during control codes when using SPI mode 2.                                                                                                                                                                                                                                                   |

| 98                     | I   | ŌĒ       | Output Enable Control (TTL compatible). All video timing unit output pins and all clock interface output pins contain valid data following the rising edge of CLKx2, after $\overline{\text{OE}}$ has been asserted low. This function is asynchronous. The three-stated pins include: VD[15:0], $\overline{\text{HRESET}}$ , $\overline{\text{VRESET}}$ , $\overline{\text{ACTIVE}}$ , $\overline{\text{DVALID}}$ , $\overline{\text{CBFLAG}}$ , $\overline{\text{FIELD}}$ , $\overline{\text{QCLK}}$ , $\overline{\text{CLKx1}}$ , and $\overline{\text{CLKx2}}$ . See the OES bits in the OFORM register to disable subgroups of output pins. |

| 78                     | 0   | FIELD    | Odd/Even Field Output (TTL compatible). A high state on the FIELD pin indicates that an odd field is being digitized.  Note: The polarity of this pin is programmable through the VPOLE register.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 89                     | 0   | CBFLAG   | Cb Data Identifier (TTL compatible). A high state on this pin indicates that the current chroma byte contains Cb chroma information.  Note: The polarity of this pin is programmable through the VPOLE register.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2–9                    | 0   | VD[15:8] | Digitized Video Data Outputs (TTL compatible). VD[0] is the least significant bit of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 22–29                  | I/O | VD[7:0]  | the bus in 16-bit mode. VD[8] is the least significant bit of the bus in 8-bit mode. The information is output with respect to CLKx1 in 16-bit mode, and CLKx2 in 8-bit mode. In mode 2, this port is configured to output control codes as well as data. When data is output in 8-bit mode using VD[15:8], VD[7:0] can be used as general purpose I/O pins. See the P_IO register.                                                                                                                                                                                                                                                              |

| 84                     | 0   | DVALID   | Data Valid Output (TTL compatible). This pin indicates when a valid pixel is being output onto the data bus. The Bt829B digitizes video at eight times the subcarrier rate, and outputs scaled video. Therefore, there are more clocks than valid data. DVALID indicates when valid pixel data is being output.  Note: The polarity of this pin is programmable through the VPOLE register.                                                                                                                                                                                                                                                      |

| 87                     | 0   | CCVALID  | A logical low on this pin indicates that the CC FIFO is half full (8 characters). This pin may be disabled. This open drain output requires a pullup resistor for proper operation. However, if closed captioning is not implemented, this pin may be left unconnected.                                                                                                                                                                                                                                                                                                                                                                          |

1.2 Pin Descriptions

Table 1-2. Pin Descriptions Grouped By Pin Function (3 of 4)

| Pin# | I/O | Pin Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 91   | I   | PWRDN    | A logical high on this pin puts the device into power-down mode. This is equivalent to programming CLK_SLEEP high in the ADC register.                                                                                                                                                                                                                                                                                                                                  |

| 86   | 0   | VACTIVE  | Vertical Blanking Output (TTL compatible). The falling edge of VACTIVE indicates the beginning of the active video lines in a field. This occurs VDELAY/2 lines after the rising edge of VRESET. The rising edge of VACTIVE indicates the end of active video lines and occurs ACTIVE_LINES/2 lines after the falling edge of VACTIVE. VACTIVE is output following the rising edge of CLKx1.  Note: The polarity of the pin is programmable through the VPOLE register. |

| 85   | I   | OEPOLE   | A logical low on this pin allows the Bt829B/827B to power up in the same manner as the Bt829/827. A logical high on this pin, followed by a device reset will TRISTATE the video outputs, sync outputs, and clock outputs.                                                                                                                                                                                                                                              |

|      |     |          | Clock Interface Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12   | А   | XT0I     | Clock Zero pins. A 28.64 MHz (8*Fsc) fundamental (or third harmonic) crystal can be                                                                                                                                                                                                                                                                                                                                                                                     |

| 13   | A   | XT00     | tied directly to these pins, or a single-ended oscillator can be connected to XT0I. CMOS level inputs must be used. This clock source is selected for NTSC input sources. When the chip is configured to decode PAL but not NTSC (and therefore only one clock source is needed), the 35.47 MHz source is connected to this port (XT0).                                                                                                                                 |

| 16   | A   | XT1I     | Clock One pins. A 35.47 MHz (8*Fsc) fundamental (or third harmonic) crystal can be                                                                                                                                                                                                                                                                                                                                                                                      |

| 17   | А   | XT10     | tied directly to these pins, or a single-ended oscillator can be connected to XT11. CMOS level inputs must be used. This clock source is selected for PAL input sources. If only NTSC or PAL is being decoded, and therefore only XT01 and XT00 are connected to a crystal, XT11 should be tied either high or low, and XT10 <i>must</i> be left floating.                                                                                                              |

| 97   | 0   | CLKx1    | 1x clock output (TTL compatible). The frequency of this clock is 4*Fsc (14.31818 MHz for NTSC or 17.73447 MHz for PAL).                                                                                                                                                                                                                                                                                                                                                 |

| 99   | 0   | CLKx2    | 2x clock output (TTL compatible). The frequency of this clock is 8*Fsc (28.63636 MHz for NTSC, or 35.46895 MHz for PAL).                                                                                                                                                                                                                                                                                                                                                |

| 80   | I   | NUMXTAL  | Crystal Format Pin. This pin is set to indicate whether one or two crystals are present so that the Bt829B can select XT1 or XT0 as the default in auto format mode. A logical 0 on this pin indicates one crystal is present. A logical 1 indicates two crystals are present. This pin is internally pulled down to ground with an effective 18 $K\Omega$ resistance.                                                                                                  |

|      |     |          | JTAG Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 34   | I   | TCK      | Test Clock (TTL compatible). Used to synchronize all JTAG test structures. When JTAG operations are not being performed, this pin must be driven to a logical low.                                                                                                                                                                                                                                                                                                      |

| 36   | I   | TMS      | Test Mode Select (TTL compatible). JTAG input pin whose transitions drive the JTAG state machine through its sequences. When JTAG operations are not being performed, this pin must be left floating or tied high.                                                                                                                                                                                                                                                      |

| 37   | I   | TDI      | Test Data Input (TTL compatible). JTAG pin used for loading instruction into the TAP controller or for loading test vector data for boundary-scan operation. When JTAG operations are not being performed, this pin must be left floating or tied high.                                                                                                                                                                                                                 |

| 32   | 0   | TDO      | Test Data Output (TTL compatible). JTAG pin used for verifying test results of all JTAG sampling operations. This output pin is active for certain JTAG operations and will be three-stated at all other times.                                                                                                                                                                                                                                                         |

1.2 Pin Descriptions

Table 1-2. Pin Descriptions Grouped By Pin Function (4 of 4)

| Pin #                                                | 1/0 | Pin Name               | Description                                                                                                                                                                                                                                                          |  |  |  |

|------------------------------------------------------|-----|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 35                                                   | I   | TRST                   | Test Reset (TTL compatible). JTAG pin used to initialize the JTAG controller. This pin is tied low for normal device operation. When pulled high, the JTAG controller is ready for device testing.                                                                   |  |  |  |

|                                                      |     |                        | Power And Ground Pins                                                                                                                                                                                                                                                |  |  |  |

| 10, 38, 76,<br>88, 96                                | Р   | VDD +5 V               | Power supply for digital circuitry. All VDD pins must be connected together as close to the device as possible. A 0.1 $\mu$ F ceramic capacitor should be connected between each group of VDD pins and the ground plane as close to the device as possible.          |  |  |  |

| 1, 20, 30, 92                                        | Р   | VDDO + 3.3 V           | Power supply for 3.3 V digital circuitry. All VDDO pins must be connected together as close to the device as possible. A 0.1 $\mu$ F ceramic capacitor should be connected between each group of VDDO pins and the ground plane, as close to the device as possible. |  |  |  |

| 40, 44, 48,<br>60, 65, 72                            | Р   | VAA +5 V,<br>VPOS +5 V | Power supply for analog circuitry. All VAA pins and VPOS must be connected together as close to the device as possible. A 0.1 $\mu$ F ceramic capacitor should be connected between each group of VAA pins and the ground plane as close to the device as possible.  |  |  |  |

| 11, 21, 31,<br>33, 39, 77,<br>81, 90, 93,<br>95, 100 | G   | GND                    | Ground for digital circuitry. All GND pins must be connected together as close to the device as possible.                                                                                                                                                            |  |  |  |

| 42, 47, 54,<br>56, 58, 61,<br>66, 71, 75             | G   | AGND, VNEG             | Ground for analog circuitry. All AGND pins and VNEG must be connected together as close to the device as possible.                                                                                                                                                   |  |  |  |

- I/O Column Legend:

I = Digital Input

O = Digital Output

I/O = Digital Bidirectional

A = Analog

- G = Ground

- P = Power

# 1.3 Differences Between Bt829A/827A and Bt829B/827B

While both Bt829A/827A and Bt829B/827B video decoders are pin and software compatible, please note the differences, as described in Table 1-3.

A 3.3 V mode has been added which allows the Bt829B to interface to 3.3 V graphic/video controllers without the use of 5 V to 3.3 V level translators.

Table 1-3. Pin Function Differences

| Pins          | Bt829A/<br>827A | Bt829B/<br>827B | Comments                                                                                                |  |

|---------------|-----------------|-----------------|---------------------------------------------------------------------------------------------------------|--|

| 1, 20, 30, 92 | VDD             | VDDO            | For 3.3 V I/O, connect the pins to the 3.3 V supply. For 5 V I/O, connect these pins to the 5 V supply. |  |

See Figure 3-4 for typical power and ground connections when in 3.3 V I/O mode. The pins listed in Table 1-4 can output 3.3 V signal levels when pins 1, 20, 30, and 92 (VDDO) are connected to a 3.3 V power supply.

Table 1-4. 3.3 V Pin Output

| Pin Number | Pin Name |  |  |  |  |

|------------|----------|--|--|--|--|

| 82         | HRESET   |  |  |  |  |

| 79         | VRESET   |  |  |  |  |

| 83         | ACTIVE   |  |  |  |  |

| 94         | QCLK     |  |  |  |  |

| 78         | FIELD    |  |  |  |  |

| 89         | CBFLAG   |  |  |  |  |

| 2–9        | VD[15:8] |  |  |  |  |

| 22–29      | VD[7:0]  |  |  |  |  |

| 84         | DVALID   |  |  |  |  |

| 87         | CCVALID  |  |  |  |  |

| 86         | VACTIVE  |  |  |  |  |

| 97         | CLKX1    |  |  |  |  |

| 99         | CLKX2    |  |  |  |  |

| 32         | TDO      |  |  |  |  |

1.3 Differences Between Bt829A/827A and Bt829B/827B

The pins shown in Table 1-5 can receive 3.3 V signal levels when pins 1, 20, 30, and 92 (VDDO) are connected to a 3.3 V power supply:

Table 1-5. 3.3 V Pin Input

| Pin Number | Pin Name |  |  |  |

|------------|----------|--|--|--|

| 19         | SCL      |  |  |  |

| 18         | SDA      |  |  |  |

| 14         | I2CCS    |  |  |  |

| 15         | RST      |  |  |  |

| 98         | ŌĒ       |  |  |  |

| 91         | PWRDN    |  |  |  |

| 85         | OEPOLE   |  |  |  |

| 80         | NUMXTAL  |  |  |  |

| 34         | TCK      |  |  |  |

| 36         | TMS      |  |  |  |

| 37         | TDI      |  |  |  |

| 35         | TRST     |  |  |  |

When using the Bt829B/827B in the 3.3 V I/O mode with the third overtone crystal oscillators, the tank circuit required is different to the tank circuit when in 5 V I/O mode. See Figures 2-1, 2-2, 2-3, and 2-4.

1.4 UltraLock VideoStream II Decoders

#### 1.4 UltraLock

#### 1.4.1 The Challenge

The line length (the interval between the midpoints of the falling edges of succeeding horizontal sync pulses) of analog video sources is not constant. For a stable source such as a studio grade video source or test signal generators, this variation is very small:  $\pm 2$  ns. However, for an unstable source such as a VCR, laser disk player, or TV tuner, line length variation is as much as a few microseconds.

Digital display systems require a fixed number of pixels per line, despite these variations. The Bt829B employs a technique known as UltraLock to implement locking to the horizontal sync and the subcarrier of the incoming analog video signal and generating the required number of pixels per line.

#### 1.4.2 Operation Principles of UltraLock

UltraLock is based on sampling, using a fixed-frequency stable clock. Because the video line length will vary, the number of samples generated using a fixed-frequency sample clock will also vary from line-to-line. If the number of generated samples-per-line is always greater than the number of samples-per-line required by the particular video format, the number of acquired samples can be reduced to fit the required number of pixels per line.

The Bt829B requires an 8\*Fsc (28.64 MHz for NTSC and 35.47 MHz for PAL) crystal or oscillator input signal source. The 8\*Fsc clock signal, or CLKx2, is divided down to CLKx1 internally (14.32 MHz for NTSC and 17.73 MHz for PAL). Both CLKx2 and CLKx1 are made available to the system. UltraLock operates at CLKx1 although the input waveform is sampled at CLKx2 then low-pass filtered and decimated to CLKx1 sample rate.

At a 4\*Fsc (CLKx1) sample rate there are 910 pixels for NTSC and 1,135 pixels for PAL/SECAM within a nominal line time interval (63.5 µs for NTSC and 64 µs for PAL/SECAM). For square pixel NTSC and PAL/SECAM formats there should only be 780 and 944 pixels-per-video line, respectively. This is because the square pixel clock rates are slower than a 4\*Fsc clock rate: for example, 12.27 MHz for NTSC and 14.75 MHz for PAL.

UltraLock accommodates line length variations from nominal in the incoming video by always acquiring more samples (at an effective 4\*Fsc rate) than are required by the particular video format. It then outputs the correct number of pixels per line. UltraLock then interpolates the required number of pixels so that it maintains the stability of the original image, despite variation in the line length of the incoming analog waveform.

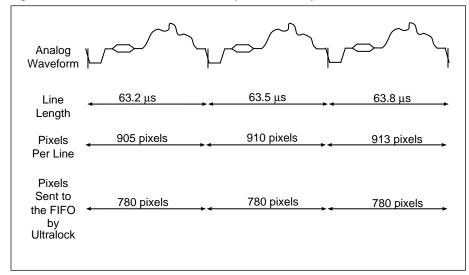

Figure 1-3 illustrates three successive lines of video being decoded for square pixel NTSC output. The first line is shorter than the nominal NTSC line time interval of 63.5  $\mu$ s. On this first line, a line time of 63.2  $\mu$ s sampled at 4\*Fsc (14.32 MHz) generates only 905 pixels. The second line matches the nominal line time of 63.5  $\mu$ s and provides the expected 910 pixels. Finally, the third line is too long at 63.8  $\mu$ s within which 913 pixels are generated. In all three cases, UltraLock outputs only 780 pixels.

VideoStream II Decoders 1.4 UltraLock

UltraLock can be used to extract any programmable number of pixels from the original video stream as long as the sum of the nominal pixel line length (910 for NTSC and 1,135 for PAL/SECAM) and the worst case line length variation from nominal in the active region is greater than or equal to the required number of output pixels per line, for example:

$$P_{Nom} + P_{Var} \ge P_{Desired}$$

where:  $P_{Nom}$  = Nominal number of pixels per line at 4\*Fsc sample rate (910 for NTSC, 1,135 for PAL/SECAM)

$P_{Var}$  = Variation of pixel count from nominal at 4\*Fsc (can be a positive or negative number)

$P_{Desired}$  = Desired number of output pixels per line

**NOTE:** For stable inputs, UltraLock guarantees the time between the falling edges of HRESET only to within one pixel. UltraLock does, however, guarantee the number of active pixels in a line as long as the stated relationship holds.

## 1.5 Composite Video Input Formats

The Bt829B supports several composite video input formats. Table 1-6 specifies the different video formats and some of the countries in which each format is used.

Table 1-6. Video Input Formats Supported by the Bt829B

| Format                                  | Lines | Fields | F <sub>SC</sub>        | Country                                |  |  |  |

|-----------------------------------------|-------|--------|------------------------|----------------------------------------|--|--|--|

| NTSC-M                                  | 525   | 60     | 3.58 MHz               | U.S., many others                      |  |  |  |

| NTSC-Japan <sup>(1)</sup>               | 525   | 60     | 3.58 MHz               | Japan                                  |  |  |  |

| PAL-B                                   | 625   | 50     | 4.43 MHz               | Many                                   |  |  |  |

| PAL-D                                   | 625   | 50     | 4.43 MHz               | China                                  |  |  |  |

| PAL-G                                   | 625   | 50     | 4.43 MHz               | Many                                   |  |  |  |

| PAL-H                                   | 625   | 50     | 4.43 MHz               | Belgium                                |  |  |  |

| PAL-I                                   | 625   | 50     | 4.43 MHz               | Great Britain, others                  |  |  |  |

| PAL-M                                   | 525   | 60     | 4.43 MHz               | Brazil                                 |  |  |  |

| PAL-N                                   | 625   | 50     | 4.43 MHz               | Paraguay, Uruguay                      |  |  |  |

| PAL-N combination                       | 625   | 50     | 3.58 MHz               | Argentina                              |  |  |  |

| SECAM                                   | 625   | 50     | 4.406 MHz<br>4.250 MHz | Eastern Europe, France,<br>Middle East |  |  |  |

| Notes: (1). NTSC-Japan has 0 IRE setup. |       |        |                        |                                        |  |  |  |

1.5 Composite Video Input Formats

The video decoder must be programmed appropriately for each of the composite video input formats. Table 1-7 lists the register values that need to be programmed for each input format.

Table 1-7. Register Values for Video Input Formats

| Register                                            | Bit                       | NTSC-M                                                 | NTSC-Japan                               | PAL-B, D,<br>G, H, I                                     | PAL-M                                    | PAL-N                                                 | PAL-N<br>Combination                    | SECAM                                                 |