# RCV144ACi-BA Desktop Integrated High Speed Data/Fax/Voice/Audio Modem Device Set

# INTRODUCTION

The Rockwell RCV144ACi-BA desktop integrated data/fax/voice/audio modem device set supports the Integrated Communications System program. The modem supports data throughput in excess of 176 kbps utilizing the Rockwell High Speed Interface (RHSI), fax operation up to 14400 bps, ADPCM voice compression/decompression at 7200 Hz, and audio 8- and 16-bit record/playback at 11.025 kHz or 7200 Hz. Extended "AT" commands provide data, fax class 1 and class 2, MNP 10, voice, and audio functions.

The modem device set consists of data/fax/voice/audio modem data pump (MDP) and microcontroller (MCU) devices with supporting MCU firmware.

As a data modem, the modem operates at line speeds to 14400 bps. Error correction (V.42/MNP 2-4), data compression (V.42 bis/MNP 5), and RHSI maximize data transfer integrity and boost data throughput beyond the normal maximum DTE speed. The modem also operates in non-error-correcting mode.

As a fax modem, the modem supports Group 3 send and receive rates up to 14400 bps and supports T.30 protocol.

The modem uses enhanced Adaptive Differential Pulse Coded Modulation (ADPCM) coding and decoding to support efficient digital storage of voice using 2-bit or 4-bit compression and decompression at 7200 bps. Coder silence deletion and decoder silence interpolation is available to significantly increase compression rates.

In audio mode, the modem supports record and playback of monophonic (mono) audio data in 8-bit unsigned linear pulse code modulation (PCM) or 16-bit signed linear PCM format at 11.025 kHz or 7200 Hz sampling rate.

Microsoft Windows is supported in the host using the proprietary RHSI. The use of RHSI overcomes the limitation of predefined UART speeds. Support for RHSI is in the form of modem microcomputer firmware and Windows driver RHSICOMM.DRV. The Rockwell RHSICOMM.DRV driver is downward compatible with the standard Microsoft Windows communications driver COMM.DRV. Use of RHSI allows slower PCs such as 16 MHz 386-based computers to sustain data rates of 115.2 kbps and higher.

A PC half-card, designed for superior voice and audio performance, is available in an AccelerATor Kit to minimize application design time and development costs. The kit also includes design layout files on floppy disk, sample modem devices, crystals, and full documentation.

# **FEATURES**

- Data modem throughput up to 57.6 kbps (beyond 57.6 kbps when RHSI is active)

- V.32 bis, V.32, V.22 bis, V.22A/B, V.23, and V.21; Bell 212A and Bell 103

- -V.42 LAPM and MNP 2-4 error correction

- -V.42 bis and MNP 5 data compression

- MNP 10 data throughput enhancement

- Haves AutoSync

- Fax modem send and receive rates up to 14400 bps –V.17, V.29, V.27 ter, and V.21 channel 2

- Voice mode

- -Enhanced ADPCM compression/decompression

- -Tone detection/generation and call discrimination

- -Concurrent DTMF detection

- -Timing marks

- Audio mode

- Record mono data using 8-bit or 16-bit audio data encoding at 11.025 kHz or 7200 Hz

- -Playback at 11.025 kHz or 7200 Hz

- -Concurrent DTMF/tone detection

- Supports business audio applications, e.g., digital answering machine, voice annotation, audio file play and record, and text-to-speech

- Communication software-compatible AT, fax class 1 and 2, and Rockwell voice commands

- Built-in parallel 16550A UART-compatible interface

- Proprietary Rockwell High Speed Interface (RHSI)

- · Line quality monitoring and auto retrain

- NVRAM directory and stored profiles

- · Flow control and speed buffering

- Automatic format/speed sensing

- · Parallel asynchronous data

- Auto dial and auto answer

- Tone, pulse, and adaptive dialing

- Calling Number Delivery (Caller ID) detect

- Diagnostics

- Extended operating temperature model available

- +5V operation; typical power consumption:

Operating Sleep mode

850 mW 21.0 mW

Two CMOS VLSI devices

-MCU: 84-pin PLCC; MDP: 68-pin PLCC

Integrated Communications System is a trademark of Rockwell International.

Microsoft is a registered trademark of Microsoft Corporation. Windows is a trademark of Microsoft Corporation. MNP is a trademark of Microcom, Inc.

Hayes is a trademark of Hayes Microcomputer Products, Inc.

Data Sheet (Preliminary)

Order No. MD106 April 22, 1994

# **TECHNICAL OVERVIEW**

## **GENERAL DESCRIPTION**

The modem device set provides the processing core of the modem. The OEM adds external memory, crystal, discrete components, and a digital access arrangement (DAA) circuit to complete the modem system.

# Modem Data Pump (MDP)

The MDP is a Rockwell RCV144DPi-BA data/fax/voice/audio modem data pump packaged in a 68-pin PLCC.

As a data modem, the MDP can operate in 2-wire, full-duplex, asynchronous modes at line rates up to 14400 bps.

As a fax modem, the MDP fully supports Group 3 facsimile send and receive speeds of 14400 12000, 9600, 7200, 4800, and 2400 bps.

# Microcontroller (MCU)

The MCU is a Rockwell C40 microcomputer packaged in a 84-pin PLCC. The MCU performs the command processing and host interface functions. The MCU connects to the host via a parallel microcomputer bus. The MCU connects to the MDP via dedicated lines and an external bus. The external bus also connects to the OEM-supplied 128k-byte ROM and 32k-byte RAM. The crystal frequency is 9.8304 MHz.

#### **MCU Firmware**

MCU firmware performs processing of general moder control, command sets, error correction, data compression, MNP 10, fax class 1 and class 2, voice, audio, RHSI, and DTE interface functions. The MCU firmware is provided by Rockwell in object code form for the OEM to program into external ROM. The MCU firmware may also be provided in source code form under a source code addendum license agreement.

#### SUPPORTED INTERFACES

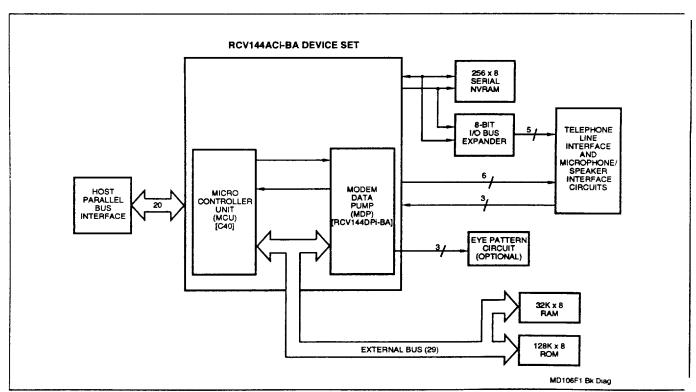

The major hardware signal interfaces of the modern device set are illustrated in Figure 1.

#### Parallel Interface

A 16550A UART-compatible parallel interface and a supporting stop mode control signal are provided.

Host Bus Interface. Eight data lines, three address lines, four DMA request/acknowledge lines, four control/status lines, and a reset line are supported.

#### **NVRAM** Interface

A serial interface to the optional OEM-supplied 256-byte non-volatile RAM (NVRAM) is provided. Data stored in NVRAM can take precedence over the factory default settings. The 256-byte NVRAM can store up to two user-selectable configurations and can store up to four 35-digit dial strings.

Figure 1. Modem Device Set General Interface

# Speaker Interface

A speaker output, controlled by AT commands, is provided for an optional OEM-supplied speaker circuit.

## MCU External Bus interface

The MCU external bus connects to MDP and to OEM-supplied 128k-byte ROM and 32k-byte RAM. The non-multiplexed bus supports eight bidirectional data lines and 17 address lines. Dedicated MDP, ROM, and RAM chip select outputs are also provided for selecting external devices.

#### Line Interface

MDP. The MDP connects to the line interface circuitry via a receive analog input, two transmit analog outputs, two relay driver outputs, and a ring signal input. The relay outputs may be used to drive Caller ID and voice relays.

MCU. The MCU provides one output to control the off-hook/pulse dial relay. The MCU also uses the NVR AM lines to control an 8-bit bus expander which outputs two encoded analog switch control signals to select RIN and TXA1/TXA2 routing. In addition, three outputs are provided by the bus expander to select volume control, control volume up/down direction, and volume increment. The MCU accepts ring signal and line current sense from the line interface.

# Eye Pattern Generator Interface

Eye pattern data, clock, and sync interface signals are provided to allow an external eye pattern generator circuit to be easily added in order to observe modem performance relative to line impairments.

# **COMMANDS**

The modem supports data modem, fax class 1 and 2, MNP 10, and voice commands and S Registers (See Tables 1 and 2, respectively) depending on the modem model.

**Data Modem Operation.** Data modem functions operate in response to the basic AT commands when +FCLASS=0. Default parameters support US/Canada operation.

MNP 10 Operation. MNP 10 functions operate in response to MNP 10 commands.

**AutoSync Operation.** AutoSync operates in response to the &Q4 command.

Fax Modem Operation. Facsimile functions operate in response to fax class 1 commands when +FCLASS=1 or #CLS=1 or to fax class 2 commands when +FCLASS=2 or #CLS=2.

**Voice Operation.** Voice mode functions operate in response to voice/audio commands when #CLS=8 and #VBS=2 or #VBS=4 is selected.

**Audio Operation.** Audio mode functions operate in response to voice/audio commands when #CLS=8 and #VBS=8 or #VBS=16 is selected. Sampling rate is determined by #VSR=11025 or #VSR=7200.

#### DATA MODEM OPERATION

# **ESTABLISHING DATA MODEM CONNECTIONS**

## **Telephone Number Directory**

The modem supports four telephone number entries in a directory that can be saved in a serial NVRAM. Each telephone number can be up to 35 characters in length. A telephone number can be saved using the &Zn=x command and a saved telephone number can be dialed using the DS=n command.

# Dialing

**DTMF Dialing.** DTMF dialing using DTMF tone pairs is supported in accordance with CCITT Q.23. The transmit tone level complies with Bell Publication 47001.

Pulse Dialing. Pulse dialing is supported in accordance with EIA/TIA-496-A.

Adaptive Dialing. If DTMF dialing is selected (T command) and the telephone network will not recognize DTMF tones, the modem will switch to pulse dialing. If pulse dialing is selected (P command), pulse dialing will be used.

**Blind Dialing.** The modern can blind dial in the absence of a dial tone if enabled by the X0, X1, or X3 command.

# **Modem Handshaking Protocol**

If a tone is not detected within the time specified in the S7 register after the last digit is dialed, the modem aborts the call attempt.

# **Call Progress Tone Detection**

Ringback, equipment busy, and progress tones can be detected in accordance with the applicable standard.

#### **Answer Tone Detection**

Answer tone detection can be detected over the frequency range of 2100  $\pm$  40 Hz in CCITT modes and 2225  $\pm$  40 Hz in Bell modes.

# Ring Detection

A ring signal can be detected from a TTL-compatible 15.3 Hz to 68 Hz square wave input.

# **Billing Protection**

When the modem goes off-hook to answer an incoming call, both transmission and reception of data are prevented for 2 seconds (data modem) or 4 seconds (fax adaptive answer) to allow transmission of the billing signal.

#### Connection Speeds

The modem functions as a data modem when the +FCLASS=0 command is active. The possible data connection modes/speeds are listed in Table 3. Two methods of establishing a connection are supported: use of the F command and use of N command, speed sense, and S37 register combination.

Table 1. AT Commands

| Command    | Function                                               |

|------------|--------------------------------------------------------|

|            | Basic AT Commands                                      |

| A/         | Re-execute command                                     |

| A          | Answer a call                                          |

| Bn         | Set CCITT or Bell Mode                                 |

| Cn         | Carrier control                                        |

| Dn         | Dial (originate a call)                                |

| l E        | Command echo                                           |

| Fn         | Select line modulation                                 |

| Hn         | Disconnect (hang-up)                                   |

| In         | Identification                                         |

| Ln         | Speaker volume                                         |

| Mn         | Speaker control                                        |

| Nn         | Automode enable                                        |

| On         | Return to on-line data mode                            |

| Р          | Set pulse dial default                                 |

| Qn         | Quiet results codes control                            |

| Sn=x       | Write to selected S Register                           |

| Sn?        | Read selected S Register                               |

| Τ          | Set tone dial default                                  |

| Vn         | Result code form                                       |

| Wn         | Error correction message control                       |

| Xn         | Extended result codes                                  |

| Yn         | Long space disconnect                                  |

| Zn         | Soft reset and restore profile                         |

| &Cn        | RLSD (DCD) option                                      |

| &Đn        | DTR option                                             |

| &F         | Restore factory configuration (profile)                |

| &Gn        | Select guard tone                                      |

| &Jn        | Telephone jack control                                 |

| &Kn        | Flow control                                           |

| &Ln        | Leased line operation                                  |

| &Mn        | Asynchronous/synchronous mode selection                |

| &Pn        | Select pulse dial make/break ratio                     |

| &Qn        | Asynchronous/synchronous mode selection                |

| &Rn        | RTS/CTS option                                         |

| &Sn        | DSR override                                           |

| &Tn        | Test and diagnostic                                    |

| &V         | Display current configuration and stored profiles      |

| &Wn        | Store current configuration                            |

| &Xn        | Select synchronous clock source                        |

| &Yn        | Designate a default reset profile                      |

| &Zn=x      | Store phone number                                     |

| 1          |                                                        |

| %En        | Enable/disable line quality monitor and                |

| 0/1        | auto-retrain or fallback/fall forward                  |

| %L<br>  %Q | Report line signal level                               |

| %U<br>%TTn | Report line signal quality PTT testing utilities       |

|            | -                                                      |

| \Gn        | Modem-to-modem flow control (XON/XOFF)                 |

| VKn        | Break control                                          |

| Wn         | Operating mode                                         |

| #CID       | Enable Caller ID detection and select reporting format |

|            | Download to flash memory                               |

| 1          | •                                                      |

|            |                                                        |

|            |                                                        |

|            |                                                        |

|            |                                                        |

Table 1. AT Commands (Cont'd)

| 1                | Table 1. AT Commands (Cont'd)                                     |

|------------------|-------------------------------------------------------------------|

| Command          | Function                                                          |

|                  | ECC AT Commands                                                   |

| %C               | Select data compression                                           |

| VAn              | Maximum MNP block size                                            |

| <b>VB</b> n      | Transmit BREAK to remote                                          |

| <b>\L</b> n      | MNP block transfer control                                        |

|                  | MNP 10 AT Commands                                                |

| )Mn              | Enable cellular power level adjustment                            |

| * Hn             | Set link negotiation speed                                        |

| -Kn              | MNP extended services                                             |

| -Qn              | Enable fallback to V.22 bis/V.22                                  |

| @Mn              | Select initial transmit level                                     |

|                  | Fax Class 1 AT+F Commands                                         |

| +FCLASS=n        | Service class                                                     |

| +FTS=n           | Stop transmission and wait                                        |

| +FRS=n           | Receive silence                                                   |

| +FTM=n           | Transmit data                                                     |

| +FRM=n           | Receive data                                                      |

| +FTH=n           | Transmit data with HDLC framing                                   |

| +FRH=n           | Receive data with HDLC framing                                    |

| FOLASS =         | Fax Class 2 AT+F Commands Service class                           |

| +FCLASS=n        |                                                                   |

|                  | Class 2 Action Commands                                           |

| +FCIG            | Set the polled station identification                             |

| +FDT             | Data transmission                                                 |

| +FET=N<br>+FDR   | Transmit page punctuation  Begin or continue Phase C receive data |

| +FK              | Terminate session                                                 |

| +FLPL            | Document for polling                                              |

| +FSPL            | Enable polling                                                    |

|                  | Class 2 DCE Responses                                             |

| +FCIG:           | Report the polled station identification                          |

| +FCON            | Facsimile connection response                                     |

| +FDCS:           | Report current session                                            |

| +FDIS:           | Report remote identification                                      |

| +FDTC:           | Report the polled station capabilities                            |

| +FCFR            | Indicate confirmation to receive                                  |

| +FTSI:           | Report the transmit station ID                                    |

| +FCSI:<br>+FPTS: | Report the called station ID Page transfer status                 |

| +FET:            | Post page message response                                        |

| +FHNG:           | Call termination with status                                      |

| +FPOLL           | Indicates polling request                                         |

|                  | Class 2 Session Parameters                                        |

| +FMFR?           | Identify manufacturer                                             |

| +FMDL?           | Identify model                                                    |

| +FREV?           | Identify revision                                                 |

| +FDCC            | DCE capabilities parameters                                       |

| +FDIS            | Current sessions parameters                                       |

| +FDCS            | Current session results                                           |

| +FLID            | Local ID string                                                   |

| +FPTS            | Page transfer status                                              |

| +FCR             | Capability to receive Adaptive answer                             |

| +FAA<br>+FBUF?   | Buffer size (read only)                                           |

| +FPHCTO          | Phase C time out                                                  |

| +FAXERR?         | Fax error value                                                   |

| +FBOR            | Phase C data bit order                                            |

|                  |                                                                   |

Table 1. AT Commands (Cont'd)

| •            | Table 1. AT Commands (Cont'd)            |

|--------------|------------------------------------------|

| Command      | Function                                 |

|              | Voice AT# Commands                       |

| #BDR         | Select baud rate                         |

| #CLS         | Select data, fax, voice, or audio        |

| #MDL?        | Identify model                           |

| #MFR?        | Identify manufacturer                    |

| #REV?        | Identify revision level                  |

| #TL          | Audio output transmit level              |

| #VBQ?        | Query buffer size                        |

| #VBS         | Bits per sample                          |

| #VBT         | Beep tone timer                          |

| #VCI?        | Identify compression method              |

| #VGT         | Volume selection                         |

| #VLS         | Voice line select                        |

| #VRA         | Ringback goes away timer (originate)     |

| #VRN         | Ringback never came timer (originate)    |

| #VRX         | Voice receive mode                       |

| #VSD         | Enable silence deletion                  |

| #VSK         | Buffer skid setting                      |

| #VSP         | Silence detection period (voice receive) |

| #VSR         | Sampling rate selection                  |

| #VSS         | Silence detection tuner (voice receive)  |

|              | DTMF/tone reporting                      |

| #VTD         | Place timing marks                       |

| #VTM         | Generate tone signals                    |

| #VTS<br>#VTX | Voice transmit mode                      |

| "VIA         | Voice dansmit mode                       |

| Note:        |                                          |

| Embedded [   | DLE commands and responses are described |

| in the AT Co | mmand Reference Manual.                  |

|              |                                          |

|              |                                          |

|              |                                          |

|              |                                          |

|              |                                          |

|              |                                          |

|              |                                          |

|              |                                          |

|              |                                          |

|              |                                          |

|              |                                          |

|              |                                          |

|              |                                          |

|              |                                          |

|              |                                          |

|              |                                          |

|              |                                          |

|              |                                          |

|              |                                          |

|              |                                          |

|              |                                          |

Table 2. S Registers

| Register | Function                           |

|----------|------------------------------------|

| S0       | Rings to auto-answer               |

| S1       | Ring counter                       |

| S2       | Escape character                   |

| S3       | Carriage return character          |

| S4       | Line feed character                |

| S5       | Backspace character                |

| S6       | Maximum time to wait for dial tone |

| S7       | Wait for carrier                   |

| S8       | Pause time for dial delay modifier |

| S9       | Carrier detect response time       |

| S10      | Carrier loss disconnect time       |

| S11      | DTMF Tone Duration -               |

| S12      | Escape code guard time             |

| S13      | Reserved                           |

| S14      | General bit mapped options         |

| S15      | Reserved                           |

| S16      | Test mode bit mapped options (&T)  |

| S17      | Reserved                           |

| S18      | Test timer                         |

| S19-S20  | Reserved                           |

| S21      | V24/general bit mapped options     |

| S22      | Speaker/results bit mapped options |

| S23      | General bit mapped options         |

| S24      | Sleep inactivity timer             |

| S25      | Delay to DTR (CT108) off           |

| S26      | RTS-to-CTS (CT105-to-CT106) delay  |

| S27      | General bit mapped options         |

| S28      | General bit-mapped options         |

| S29      | Flash modifier time                |

| S30      | Inactivity timer                   |

| S31      | General bit-mapped options         |

| S32      | XON character                      |

| S33      | XOFF character                     |

| S34-S35  | Reserved                           |

| S37      | Line connection speed              |

| S38      | Delay before forced hangup         |

| S39      | Flow control                       |

| S40      | General bit-mapped options         |

| S41      | General bit-mapped options         |

| S42-S45  | Reserved                           |

| S91      | PSTN transmit attenuation level    |

| S92      | Fax transmit attenuation level     |

| S95      | Result code messages control       |

| S99      | Leased line transmit level         |

|          | ECC S Registers                    |

| S36      | LAPM failure control               |

| S46      | Data compression control           |

| S48      | V.42 negotiation control           |

| S82      | Break handling control             |

| S86      | Call failure reason code           |

|          | Celiular Registers                 |

| S201     | Cellular transmit level            |

| 1        |                                    |

**Table 3. Connection Speed Options**

| Configuration | Rate                       |

|---------------|----------------------------|

| V.32 bis      | 14400, 12000, 9600, 7200,  |

|               | or 4800 bps                |

| V.32          | 9600 or 4800 bps           |

| V.22 bis      | 2400 or 1200 bps           |

| V.22          | 1200 bps                   |

| V.23          | 1200Tx/75Rx or 75Tx/1200Rx |

| V.21          | 0-300 bps                  |

| Bell 212A     | 1200 bps                   |

| Bell 103      | 0-300 bps                  |

#### **Automode**

Automode detection can be enabled by the N1 or F0 commands to allow the modern to connect to a remote modern in accordance with EIA/TIA-PN2330.

#### **DATA MODE**

Data mode exists when a telephone line connection has been established between modems and all handshaking has been completed.

# Speed Buffering (Normal Mode)

Speed buffering allows a DTE to send to, and receive data from, a modem at a speed different than the line speed. The modem supports speed buffering at all line speeds.

# Flow Control

**DTE-to-Modem Flow Control.** If the modem-to-line speed is less than the DTE-to-modem speed, the modem supports XOFF/XON or RTS/CTS flow control with the DTE to ensure data integrity.

Modem-to-Modem Flow Control. When enabled by the \G1 command, the modem supports XON/XOFF flow control with the remote modem to ensure data integrity. Modem-to-modem flow control is not used in error correction mode. In this case, flow control is accomplished within the error-correction protocol.

# **Escape Sequence Detection**

The "+++" escape sequence with guard time can be used to return control to the command mode from the data mode. Escape sequence detection is disabled by a S2 Register value greater than 127. Escape sequence detection is disabled in synchronous mode.

# **BREAK Detection**

The modem can detect a BREAK signal from either the DTE or the remote modem. The \Kn command determines the modem response to a received BREAK signal.

# **Telephone Line Monitoring**

**GSTN Cleardown (V.32 bis, V.32).** Upon receiving GSTN Cleardown from the remote modem in a non-error-correcting mode, the modem cleanly terminates the call.

Loss of Carrier. If carrier is lost for a time greater than specified by the S10 register, the modern will disconnect.

Receive Space Disconnect. If selected by the Y1 command in error-correction mode, the modern will disconnect after receiving  $1.6 \pm 10\%$  seconds of continuous SPACE

## Send SPACE on Disconnect

If selected by the Y1 command in non-error-correction mode, the modern will send  $4\pm10\%$  seconds of continuous SPACE when a locally commanded hang-up is issued by the &Dn or H command.

# Fall Forward/Fallback (V.32 bis/V.32)

During initial handshake, the modem will fallback to the optimal line connection within V.32 bis/V.32 mode depending upon signal quality if automode is enabled by the N1 command.

When connected in V.32 bis/V.32 mode, the modem will fall forward or fallback to the optimal line speed within V.32 bis/V.32 mode depending upon signal quality if fall forward/fallback is enabled by the %E2 command.

#### Retrain

The modem may lose synchronization with the received line signal under poor line conditions. If this occurs, retraining may be initiated to attempt recovery depending on the type of connection.

The modem initiates a retrain if line quality becomes unacceptable if enabled by the %E command. The modem continues to retrain until an acceptable connection is achieved or until 30 seconds elapse which will result in telephone line disconnect.

# **Programmable Inactivity Timer**

The modem will disconnect from the line if data is not sent or received for a specified length of time. In normal or error-correction mode, this inactivity timer is reset when data is received from either the DTE or from the line. This timer can be set to a value between 0 and 2550 seconds by register S30. A value of 0 disables the inactivity timer.

# ERROR CORRECTION AND DATA COMPRESSION

# V.42 Error Correction

V.42 supports two methods of error correction: LAPM and, as an alternative, MNP 4. The modern provides a detection and negotiation technique for determining and establishing the best method of error correction between two moderns.

## **MNP 2-4 Error Correction**

MNP 2-4 is a data link protocol that uses error correction algorithms to ensure data integrity. MNP block or stream mode operation may be selected by the \Ln command.

In stream mode, the modem sends data frames in varying lengths depending on the amount of time between characters coming from the DTE.

In block mode, the modem sends data frames of 256 characters in length. Special communication software must be used when using block mode.

6

# V.42 bis Data Compression

V.42 bis data compression mode, enabled by the %Cn or S46 command, operates when a LAPM or an MNP 10 connection is established.

The V.42 bis data compression employs a "string learning" algorithm in which a string of characters from the DTE is encoded as a fixed length codeword. Two 2k-byte dictionaries are used to store the strings. These dictionaries are dynamically updated during normal operation.

# **MNP 5 Data Compression**

MNP 5 data compression mode, enabled by the %Cn command, operates during an MNP connection.

In MNP 5, the modern increases its throughput by compressing data into tokens before transmitting it to the remote modern, and by decompressing encoded received data before sending it to the DTE.

## MNP 10 DATA THROUGHPUT ENHANCEMENT

MNP10 protocol, cellular functionality, and MNP Extended Services enhance performance under adverse channel conditions such as those found in rural, long distance, or cellular environments. An MNP 10 connection is established when a LAPM or an MNP 2-4 connection is negotiated with a remote modern supporting MNP 10. MNP 10 functions include:

Robust Auto-Reliability. Higher connection success rate is achieved by attempting to overcome channel interference during the modem negotiation phase while maintaining backward compatibility with non-MNP 10 modems.

Negotiated Speed Upshift. Initial connection and MNP handshake is performed at the most dependable speed, then the connection upshifts to the highest supported modem/channel speed. This function is particularly useful in channel conditions with high connection failure rates.

**Aggressive Adaptive Packet Assembly.** Frame size is dynamically changed to quickly adapt to varying levels of interference.

**Dynamic Speed Shifting.** Connection speed is shifted upward or downward to optimize data throughput for the channel conditions by continuously monitoring the line quality and link performance.

Dynamic Transmit Level Adjustment. Transmit level is dynamically adjusted to adapt to the varying cellular network environment and to prevent "clipping," which causes data corruption, due to the Preemphasis and Compander effect.

MNP Extended Services. The modem can quickly switch to MNP 10 operation when the remote modem supports MNP 10 and both modems are configured to operate in V.42.

**V.42 bis/MNP 5 Support.** MNP 10 can operate with V.42 bis or MNP 5 data compression.

## **FAX CLASS 1 AND CLASS 2 OPERATION**

The modem operates as a facsimile (fax) DCE whenever the +FCLASS=1, +FCLASS=2, #CLS=1, or #CLS=2 command is active. In the fax mode, the on-line behavior of the modem is different from the data (non-fax) mode. After dialing, modem operation is controlled by the fax commands. Some AT commands are still valid but may operate differently from data modem mode.

# **Calling Tone**

Calling tone is generated in accordance with T.30.

#### **VOICE/AUDIO MODE**

Voice and audio functions are supported by the Voice Mode. Voice Mode includes three submodes: Online Voice Command Mode, Voice Receive Mode, and Voice Transmit Mode. (See Table 1.)

Online Voice Command Mode. This mode results from the connection to the telephone line or a voice/audio I/O device (e.g., microphone, speaker, or handset) through the use of the #CLS=8 and #VLS commands. After mode entry, AT commands can be entered without aborting the connection.

Voice Receive Mode. This mode is entered when the #VRX command is active in order to record voice or audio data input at the RXA pin, typically from a microphone/handset or the telephone line.

Received analog voice samples are converted to digital form and compressed for reading by the host. AT commands control the codec bits-per-sample rate and, optionally, select silence deletion including silence detection period adjustment.

Received analog mono audio samples are converted to digital form and formatted into 8-bit unsigned linear PCM or 16-bit signed linear PCM format for reading by the host. AT commands control the bit length and sampling rate. Concurrent DTMF/tone detection is available at the 7200 Hz sample rate.

Voice Transmit Mode. This mode is entered when the #VTX command is active in order to playback voice or audio data to the TXA1/TXA2 output pins, typically to a speaker/handset or to the telephone line.

Digitized voice data is decompressed and converted to analog form at the original compression quantization sample-per-bits rate then output to the TXA1/TXA2 pins. Optional silence interpolation is enabled if silence deletion was selected for voice compression.

Digitized audio data is converted to analog form then output to the TXA1/TXA2 pins.

MD106C1

7

#### **DIAGNOSTICS**

# **Commanded Tests**

Diagnostics are performed in response to &T commands.

**Analog Loopback.** Data from the local DTE is sent to the modern, which loops the data back to the local DTE.

Analog Loop Self Test. An internally generated test pattem of alternating 1s and 0s (reversals) is sent to the modem. An error detector within the modem checks for errors in the string of reversals.

Remote Digital Loopback (RDL). Data from the local DTE is sent to the remote modern which loops the data back to the local DTE.

Remote Digital Loopback with Self Test. An internally generated pattern is sent from the local modem to the remote modem which loops the data back to the local modem.

Local Digital Loopback. When local digital loop is requested from the local DTE, two data paths are set up in the local modem. Data from the local DTE is looped back to the local DTE (path 1) and data received from the remote modem is looped back to the remote modem (path 2).

## **Power On Reset Tests**

Upon power on, or receipt of the Z command, the modem performs tests of the RAM, ROM, NVRAM, and MDP.

## LOW POWER SLEEP MODE

**Entry.** The modern will enter the low power sleep mode when no line connection exists and no host activity occurs for the period of time specified in the S24 register. All MCU circuits are turned off except the internal MCU clock circuitry in order to consume lower power but be able to immediately wake up and resume normal operation.

Wake-up. Wake-up occurs when the host writes to the modem or ring is detected on the telephone line.

# **CALLER ID**

Caller ID can be enabled/disabled using the #CID command. When enabled, caller ID information (date, time, caller code, and name) can be passed to the DTE in formatted or unformatted form. Inquiry support allows the current caller ID mode and mode capabilities of the modem to be retrieved from the modem.

# ADDITIONAL INFORMATION

Additional information is described in the RCV144ACi-BA Modern Designer's Guide (Order No. 1018) and the AT Command Reference Manual (Order No. 1019).

## HARDWARE INTERFACE

## HARDWARE INTERFACE SIGNALS

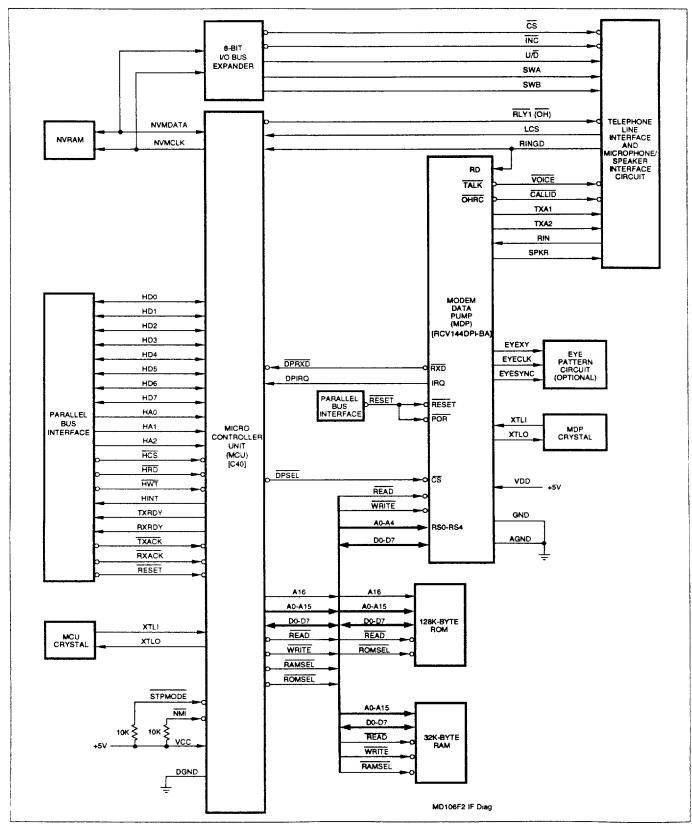

The modern hardware interface signals are shown in Figure 2.

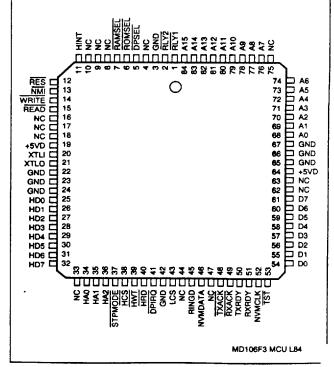

The MCU pin assignments are shown in Figure 3 and are listed in Table 4.

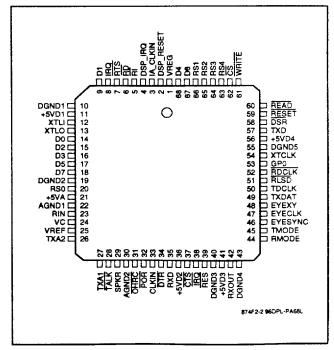

The MDP pin assignments are shown in Figure 4 and are listed in Table 5.

The MCU hardware interface signals are defined in Table 6.

The MDP hardware interface signals are defined in Table 7.

The digital electrical characteristics for the hardware interface signals are listed in Table 8.

The analog electrical characteristics for the hardware interface signals are listed in Table 9.

The current and power requirements are listed in Table 10. The absolute maximum ratings are listed in Table 11.

Table 12 shows the parallel interface registers and the corresponding bit assignments.

MD106C1

8

Figure 2. Hardware Interface Signals

MD106C2

9

Table 4. MCU Pin Signals - 84-Pin PLCC

| Pin      | MCU Signal                                   | I/O Type       | Modem Signal         |

|----------|----------------------------------------------|----------------|----------------------|

| 1        | PE0                                          | OA             | RLY1 (OH)            |

| 2        | PE1                                          | OA             | RLY2 (PULSE)         |

| 3        | GND                                          | GND            | GND                  |

| 4        | PB0                                          | OA             | A16                  |

| 5        | PB1                                          | Mi             | DPSEL                |

| 6        | PB2                                          | OA             | ROMSEL               |

| 7        | PB3                                          | OA             | RAMSEL               |

| 8        | PB4                                          |                | NC                   |

| 9        | PB5<br>PB6                                   |                | NC<br>NC             |

| 10       | PB7                                          |                | NC<br>MINIT          |

| 12       | RES                                          | OA<br>IC       | HINT<br>RES          |

| 13       | NMI                                          | "              | +5VD (Note 4)        |

| 14       | WT                                           | OA             | WRITE                |

| 15       | RD                                           | OA             | READ                 |

| 16       | PE2                                          |                | NC                   |

| 17       | PE3                                          |                | NC                   |

| 18       | NC                                           |                | NC                   |

| 19       | vcc                                          | PWR            | +5VD                 |

| 20       | XTLI                                         | ΙE             | XTLI                 |

| 21       | XTLO                                         | OE             | XTLO                 |

| 22       | GND                                          | GND            | GND                  |

| 23       | GND                                          | GND            | GND                  |

| 24       | GND                                          | GND            | GND                  |

| 25       | PC0<br>PC1                                   | IA/OA          | HD0                  |

| 26<br>27 | PC2                                          | IA/OA<br>IA/OA | HD1<br>HD2           |

| 28       | PC3                                          | IA/OA          | HD3                  |

| 29       | PC4                                          | IA/OA          | HD4                  |

| 30       | PC5                                          | IA/OA          | HD5                  |

| 31       | PC6                                          | IA/OA          | HD6                  |

| 32       | PC7                                          | IA/OA          | HD7                  |

| 33       | NC                                           |                | NC                   |

| 34       | PD0                                          | IA             | HA0                  |

| 35       | PD1                                          | IA             | HA1                  |

| 36       | PD2                                          | IA             | HA2                  |

| 37       | PD3                                          | IA             | STPMODE (Note 4)     |

| 38       | PD4                                          | IA I           | HCS                  |

| 39       | PD5                                          | IA I           | HWT                  |

| 40       | PD6<br>PD7                                   | IA<br>Mi       | HRD<br>DPIRQ         |

| 42       | GND                                          | GND            | GND                  |

| 43       | PE4                                          | IA             | LCS                  |

| 44       | PE5                                          | "              | NC                   |

| 45       | PAO                                          | IA             | RINGD                |

| 46       | PA1                                          | IA/OA          | NVMDATA (Note 4)     |

| 47       | PA2                                          |                | NC                   |

| 48       | PA3                                          | IA             | TXACK                |

| 49       | PA4                                          | IA             | RXACK                |

| 50       | PA5                                          | OA             | TXRDY                |

| 51       | PA6                                          | OA             | RXRDY                |

| 52       | PA7<br>TST                                   | OA             | NVMCLK               |

| 53<br>54 | i -                                          | IA/OA          | Connect to GND<br>D0 |

| 55       | D0<br>D1                                     | IA/OA          | D1                   |

| 56       | D2                                           | IA/OA          | D2                   |

| 57       | D3                                           | IA/OA          | D3                   |

| 58       | D4                                           | IA/OA          | D4                   |

| 59       | D5                                           | IA/OA          | D5                   |

| 60       | D6                                           | IA/OA          | D6                   |

| <b></b>  | <u>.                                    </u> |                |                      |

Table 4. MCU Pin Signals - 84-Pin PLCC (Cont'd)

| Pin   | MCU Signal | I/O Type | Modem Signal |

|-------|------------|----------|--------------|

| 61    | D7         | IA/OA    | D7           |

| 62    | PE6        |          | NC           |

| 63    | PE7        |          | NC           |

| 64    | vcc        | PWR      | +5VDC        |

| 65    | GND        | GND      | GND          |

| 66    | GND        | GND      | GND          |

| 67    | GND        | GND      | GND          |

| 68    | A0         | OA       | A0           |

| 69    | A1         | OA       | A1           |

| 70    | A2         | OA       | A2           |

| 71    | A3         | OA       | A3           |

| 72    | A4         | OA       | A4           |

| 73    | A5         | OA       | A5           |

| 74    | A6         | OA       | A6           |

| 75    | NC         |          | NC           |

| 76    | A7         | OA .     | A7           |

| 77    | A8         | OA       | AB           |

| 78    | A9         | OA       | A9           |

| 79    | A10        | OA       | A10          |

| 80    | A11        | OA       | A11          |

| 81    | A12        | OA       | A12          |

| 82    | A13        | OA       | A13          |

| 83    | A14        | OA       | A14          |

| 84    | A15        | OA       | A15          |

| Mates |            |          |              |

- 1. MI = Modern interconnect.

- 2. NC = No external connection.

- 3. NU = Not used; connect as noted.

- 4. Connect to +5 VDC through 10 KΩ.

Figure 3. MCU Pin Signals - 84-Pin PLCC

10

Table 5. MDP Pin Signals - 68-Pin PLCC

| P   | in        | Signal Label      | VO Type | Interface                     |

|-----|-----------|-------------------|---------|-------------------------------|

| П   | 1         | VREG <sup>3</sup> | MI      | To GND thru 0.1 μF (Optional) |

| 1   | 2         | DSP_RESET         | Mi      | MDP: RES                      |

| •   | 3         | IA CLKIN          | MI      | MDP: CLKIN                    |

|     | 4         | DSP_IRQ           | MI      | MDP: IRQ                      |

| 1   | 5         | RI                | OA      | NC                            |

| 1   | 6         | RD                | IA      | RINGD from Line Interface     |

| ŧ   | 7         | RTS               | iA      | To +5VD through 10KΩ          |

|     | 8         | IRQ               | OA      | MCU: DPIRQ                    |

| 1   | 9         | D1                | IA/OA   | MCU: D1                       |

|     | 0         | DGND1             | GND     | GND                           |

|     | 1         | +5VD1             | PWR     | +5VDC                         |

|     | 2         | XTLI              | 1       | Crystal/Clock Circuit         |

|     | 3         | XTLO              | o       | Crystal/Clock Circuit         |

| i   | 4         | D0                | IA/OA   | MCU: D0                       |

|     | 5         | D2                | IA/OA   | MCU: D2                       |

|     | 6         | D3                | IA/OA   | MCU: D3                       |

|     | 7         | D5                | IA/OA   | MCU: D5                       |

|     | 8         | D7                | IA/OA   | MCU: D7                       |

| ŧ   | 9         | DGND2             | GND     | GND                           |

| - 1 | 0         | RS0               | IA      | MCU: A0                       |

|     | 1         | +5VA              | PWR     | +5VA                          |

|     | 2         | AGND1             | GND     | GND                           |

| 1   | 3         | RIN               | I(DA)   | Line Interface                |

| 1   | 4         | vc                | '(5, )  | To GND through RC circuit     |

| 1   | 5         | VREF              |         | To VC through capacitors      |

| 1   | 6         | TXA2              | O(DD)   | Line Interface                |

|     | 7         | TXA1              | O(DD)   | Line Interface                |

| ı   | 8         | TALK              | OD      | VOICE to Line Interface       |

| 1 - | 9         | SPKR              | O(DF)   | Speaker Circuit               |

|     | 10        | AGND2             | GND     | GND                           |

| 1 3 | 1         | OHRC              | OD      | CALLID to Line Interface      |

| 3   | 12        | POR               | MI      | MDP. RESET                    |

| 3   | 3         | CLKIN             | MI      | MDP: IA_CLKIN                 |

| 3   | 4         | DTR               | IA      | To +5VD through 10KΩ          |

| 3   | 5         | RXD               | OA      | NC                            |

| 3   | 6         | +5VD2             | PWR     | +5VD                          |

| 3   | 7         | CTS               | OA      | NC                            |

| 3   | 8         | IRQ               | MI      | MDP. DSP_IRQ                  |

| 3   | 9         | RES               | Mi      | MDP: DSP_RESET                |

| 4   | 0         | DGND3             | GND     | GND                           |

| 4   | 1         | +5VD3             | PWR     | +5VD                          |

| 4   | 2         | RXOUT             | MI      | NC                            |

| 4   | 3         | DGND4             | GND     | GND                           |

| 4   | 4         | RMODE             | MI      | MDP: TMODE                    |

| 4   | 5         | TMODE             | MI      | MDP: RMODE                    |

| 4   | 16        | EYESYNC           | OA      | Eye Pattern Circuit           |

| 4   | 7         | EYECLK            | OA      | Eye Pattern Circuit           |

| 4   | 8         | EYEXY             | OA      | Eye Pattern Circuit           |

| 4   | 9         | TXDAT             | MI      | NC                            |

| 5   | 60        | TDCLK             | OA      | MCU: TXCLK                    |

| - 1 | 51        | RLSD              | OA      | NC                            |

| 5   | 2         | RDCLK             | OA      | NC                            |

| 5   | 3         | GP0               | Mi      | Connect to EYESYNC            |

|     | <b>54</b> | XTCLK             | IA      | NC                            |

|     | 55        | DGND5             | GND     | GND                           |

| 5   | 6         | +5VD4             | PWR     | +5VD                          |

|     | 57        | TXD               | IA      | To +5VD through 10KΩ          |

| - 1 | 8         | DSR               | OA      | NC                            |

| - 1 | 9         | RESET             | OA      | MDP. POR                      |

| _ 6 | 0         | READ              | 1A      | MCU: READ                     |

Table 5. MDP Pin Signals - 68-Pin PLCC (Cont'd)

| Pin | Signal Label | VO Type | Interface  |

|-----|--------------|---------|------------|

| 61  | WRITE        | IA      | MCU: WRITE |

| 62  | CS           | IA      | MCU: DPSEL |

| 63  | RS4          | IA      | MCU: A4    |

| 64  | RS3          | IA.     | MCU: A3    |

| 65  | RS2          | iA.     | MCU: A2    |

| 66  | RS1          | IA.     | MCU: A1    |

| 67  | D6           | IA/OA   | MCU: D6    |

| 68  | D4           | IA/OA   | MCU: D4    |

- 1. VO types:

- MI = Modern interconnect

Digital input (IA, IB, etc.) and output (OA, OB, etc.).

Analog input [I(DA)] and output [O(DD), O(DF), etc.]

- 2. NC = No external connection.

- VREG pin can be NC; capacitor connection required only for compatibility with future products.

Figure 4. MDP Pin Signals - 68-Pin PLCC

# Integrated Data/Fax/Voice/Audio Modem Device Set

Table 6. MCU Signal Definitions

| Labei      | I/O Type | Signal Name/Description                                                                                                                                                                                                                                 |

|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XTLI, XTLO | IE, OE   | MCU SYSTEM MCU Crystal/Clock In and Crystal Out. Connects to an external crystal circuit consisting of a 9.8304 MHz crystal and a capacitance network.                                                                                                  |

| RES        | IC       | MCU Reset. The active low RES input resets the MCU logic and returns the AT command set and S registers to factory default values and to "stored values" in NVRAM. The RES input is typically connected to the host bus RESET line through an inverter. |

| DPIRQ      | IA       | MDP Interrupt Request. Connects to the MDP IRQ output.                                                                                                                                                                                                  |

| DPRXD      | IA       | MDP Received Data. Connects to the MDP MRXD output.                                                                                                                                                                                                     |

| +5VD       | PWR      | +5V Digital Supply. +5VDC ± 5%.                                                                                                                                                                                                                         |

| GND        | GND      | Digital Ground. Connect to ground.                                                                                                                                                                                                                      |

|            |          | LINE INTERFACE                                                                                                                                                                                                                                          |

| RLY1       | OA       | Relay 1 Control. The active low RLY1 output can be used to control the normally open off-hook/pulse dial relay.                                                                                                                                         |

| LCS        | IA       | Line Current Sense. LCS is an active high input that indicates handset off-hook status.                                                                                                                                                                 |

| RINGD      | IA       | Ring Frequency. The RINGD input from an external ring detect circuit is monitored to determine when to wake up from sleep or stop mode.                                                                                                                 |

|            |          | NVRAM AND I/O BUS EXPANDER INTERFACE                                                                                                                                                                                                                    |

| NVMCLK     | OA       | NVRAM Clock. NVMCLK output high enables the NVRAM and the I/O Bus Expander.                                                                                                                                                                             |

| NVMDATA    | IA/OA    | NVRAM Data. The NVMDATA pin supplies a serial data interface to the NVRAM and the I/O Expander. Unique device addresses included in the data stream designate the data for the NVRAM or the I/O Bus Expander.                                           |

|            |          | EXTERNAL BUS INTERFACE                                                                                                                                                                                                                                  |

| A0-A15     | OA       | <b>Address Lines 0-15.</b> A0-A15 are the external bus address lines used to address the MDP interface memory registers and the external RAM and ROM.                                                                                                   |

| A16        | OA       | Address Line 16. A16 is a bank select line.                                                                                                                                                                                                             |

| D0-D7      | IA/OA    | Data Line 0-7. D0-D7 are the external bus data lines.                                                                                                                                                                                                   |

| READ       | OA       | Read Enable. READ output low enables data transfer from the selected device to the D0-D7 lines.                                                                                                                                                         |

| WRITE      | OA       | Write Enable. WRITE output low enables data transfer from the D0-D7 lines to the selected device.                                                                                                                                                       |

| DPSEL      | OA       | Modem Data Pump Select. DPSEL output low selects the MDP.                                                                                                                                                                                               |

| RAMSEL     | OA       | RAM Select. RAMSEL output low selects the external 32k-byte RAM.                                                                                                                                                                                        |

|            |          |                                                                                                                                                                                                                                                         |

Table 6. MCU Signal Definitions (Cont'd)

|                | I/O Type |                                                                                                                                                                                                                                         |                             | Signal Name/Description                                                                                                                                                                                                                                                                                                                                          |  |

|----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                |          |                                                                                                                                                                                                                                         | terface emula               | ACE<br>ates a 16550A UART interface. The parallel interface is compatible with<br>esigned to operate with a 16450/16550 interface.                                                                                                                                                                                                                               |  |

| HA0-HA2        | IA       | Host Bus Address Lines 0-2. During a host read or write operation, HA0-HA2 select an internal MCU 16550A-compatible register.                                                                                                           |                             |                                                                                                                                                                                                                                                                                                                                                                  |  |

| HD0-HD7        | IA/OA    | Host Bus Data Lines 0-7. HD0-HD7 are comprised of eight three-state input/output lines providing bidirectional communication between the host and the MCU. Data, control words, and status information are transferred through HD0-HD7. |                             |                                                                                                                                                                                                                                                                                                                                                                  |  |

| HCS            | IA       | Host Bus Chi                                                                                                                                                                                                                            | p Select. HCS               | input low selects the host bus.                                                                                                                                                                                                                                                                                                                                  |  |

| HRD            | IA       | Host Bus Rea                                                                                                                                                                                                                            | d. HRD is an information or | active low, read control input. When HCS is low, HRD low allows the host data from a selected MCU register.                                                                                                                                                                                                                                                      |  |

| <del>HWT</del> | IA       | Host Bus Writ                                                                                                                                                                                                                           | te. HWT is an               | active low, write control input. When HCS is low, HWT low allows the words into a selected MCU register.                                                                                                                                                                                                                                                         |  |

| HINT           | OA       | Host Bus Inte                                                                                                                                                                                                                           | rrupt. HINT o               | output is set high when the receiver error flag, received data available, empty, or modem status interrupt has an active high condition. HINT is ate interrupt service or master reset operation.                                                                                                                                                                |  |

| TXACK          | IA       | Host Transmi                                                                                                                                                                                                                            | t Acknowled                 | ge. TXACK is an active low transmit acknowledge input acknowledging ived the Transmit Ready (TXRDY) data transfer request output.                                                                                                                                                                                                                                |  |

| RXACK          | IA       | Host Receive                                                                                                                                                                                                                            | Acknowledg                  | e. RXACK is an active low receive acknowledge input acknowledging lived the Receiver Ready (RXRDY) data transfer request output.                                                                                                                                                                                                                                 |  |

| TXRDY          | OA       | Transmitter Ready. TXRDY is an active high transmit ready output in the FIFO mode (FCR0 = 1). When asserted, TXRDY indicates that the TX FIFO is not full, i.e., the TX FIFO can accept data to be transmitted.                         |                             |                                                                                                                                                                                                                                                                                                                                                                  |  |

| RXRDY          | OA       | Receiver Rea<br>When asserte<br>ready for trans                                                                                                                                                                                         | d, RXRDY ind                | s an active high receiver ready output in the FIFO mode (FCR0 = 1). dicates that the RX FIFO is not empty, i.e., the RX FIFO has received data                                                                                                                                                                                                                   |  |

|                |          | 8-BIT I/O EXP                                                                                                                                                                                                                           | ANDER TO I                  | MICROPHONE/SPEAKER INTERFACE                                                                                                                                                                                                                                                                                                                                     |  |

| SWA, SWB       | OA       | Analog Switc                                                                                                                                                                                                                            | h Control. E                | ncoded outputs select the RIN and TXA1/TXA2 routing as follows:                                                                                                                                                                                                                                                                                                  |  |

| 01111, 01112   |          |                                                                                                                                                                                                                                         |                             | Description                                                                                                                                                                                                                                                                                                                                                      |  |

|                |          | SW.                                                                                                                                                                                                                                     | ~ JiiD                      |                                                                                                                                                                                                                                                                                                                                                                  |  |

|                |          | <b>SW</b> .                                                                                                                                                                                                                             | 0                           | Data mode (connect RIN to the line and the speaker; connect TXA1/TXA2 to the line and the speaker).                                                                                                                                                                                                                                                              |  |

|                |          |                                                                                                                                                                                                                                         | 0                           | Data mode (connect RIN to the line and the speaker; connect TXA1/TXA2 to the line and the speaker).                                                                                                                                                                                                                                                              |  |

|                |          | 0                                                                                                                                                                                                                                       | •                           | Data mode (connect RIN to the line and the speaker; connect TXA1/TXA2 to the line and the speaker).  Voice mode - playback to or record from the line or the telephone set (connect RIN to the line; connect TXA1/TXA2 to the line).  Voice mode - record from the microphone                                                                                    |  |

|                |          | 0 0                                                                                                                                                                                                                                     | 1 0                         | Data mode (connect RIN to the line and the speaker; connect TXA1/TXA2 to the line and the speaker).  Voice mode - playback to or record from the line or the telephone set (connect RIN to the line; connect TXA1/TXA2 to the line).  Voice mode - record from the microphone (connect RIN to microphone input circuit; connect TXA1/TXA2 to line)               |  |

| U/ <u>D</u>    | OA       | 0<br>1<br>1<br><b>Volu<u>me</u> Up/</b> D                                                                                                                                                                                               | 1<br>0<br>1<br>pown Select. | Data mode (connect RIN to the line and the speaker; connect TXA1/TXA2 to the line and the speaker).  Voice mode - playback to or record from the line or the telephone set (connect RIN to the line; connect TXA1/TXA2 to the line).  Voice mode - record from the microphone                                                                                    |  |

| U/D<br>INC     | OA<br>OA | 0 1 1 Volume Up/D and CS = low.                                                                                                                                                                                                         | 1 0 1 nown Select.          | Data mode  (connect RIN to the line and the speaker; connect TXA1/TXA2 to the line and the speaker).  Voice mode - playback to or record from the line or the telephone set (connect RIN to the line; connect TXA1/TXA2 to the line).  Voice mode - record from the microphone  (connect RIN to microphone input circuit; connect TXA1/TXA2 to line).  Not used. |  |

Table 7. MDP Signal Definitions

| Label                                 | I/O Type  | Signal/Definition                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XTLI, XTLO                            | I, O      | OVERHEAD SIGNALS  Crystal in and Crystal Out. Connect to an external crystal circuit consisting of a 35.251200 MHz                                                                                                                                                                                                                                                            |

| RESET                                 | IA        | crystal, three capacitors, and an inductor, or to a square wave generator/sine wave oscillator.                                                                                                                                                                                                                                                                               |