# STEL-1130 Data Sheet

STEL-1130

**Quadrature Amplitude/Vector Modulator**

STANFORD TELECOM<sup>®</sup>

8585242 0002057 736

#### **FEATURES**

- 60 MHz THROUGHPUT CAPABILITY

- 12-BIT INPUTS

- OFFSET BINARY OR TWO'S COMPLEMENT INPUTS AT NCO PORTS

- TWO'S COMPLEMENT OR UNSIGNED INPUTS AT MODULATION PORTS

- PRODUCTS CAN BE ADDED OR SUBTRACTED

- Q OUTPUT AVAILABLE INDIVIDUALLY

- 12-BIT ROUNDED OR TRUNCATED PRODUCTS

#### **FUNCTIONAL DESCRIPTION**

The STEL-1130 Quadrature Amplitude Modulator is intended to be used to amplitude modulate the output of a Numerically Controlled Oscillator (NCO). Quadrature Amplitude Modulation (QAM), also known as Vector Modulation, can be produced with a suitable NCO, such as the STEL-1172B and the STEL-1177. The STEL-1130 is cascaded with the outputs of the NCO, resulting in modulated digitized signals suitable for digital to analog conversion or digital signal processing. The format of the signals at the NCO input (SIN, COS) ports can be either offset binary or two's complement, making the STEL-1130 compatible with most NCOs. The format of the signals at the modulation (I, Q) ports can be either two's complement or unsigned magnitude, allowing the STEL-1130 to be used for both suppressed carrier and unsuppressed carrier modulation. The quadrature modulation capability also makes it suitable for single sideband (SSB) suppressed carrier modulation, as well as QAM modulation in data modems.

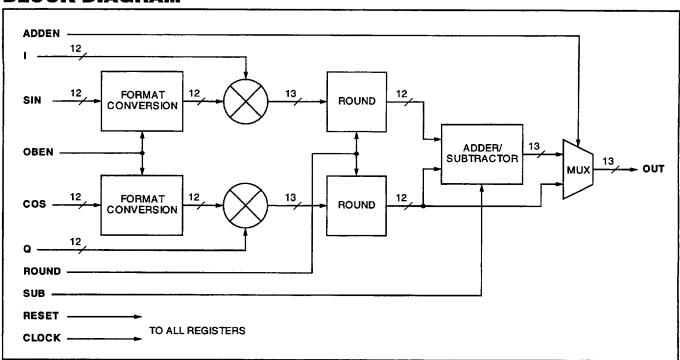

#### **BLOCK DIAGRAM**

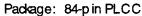

#### PIN CONFIGURATION

Package: 84 pin PLCC

Thermal coefficient,  $\theta_{ia} = 36^{\circ}C/W$

Package: 84 pin CLDCC

Thermal coefficient,  $\theta_{ja} = 34$ °C/W

Notes: (1) Tolerances on pin spacing are not cumulative.

- (2) Dimensions apply at seating plane.

- (3) PLCC and CLDCC packages have different corners and may not fit into sockets designed for the other type. Universal sockets are available without alignment locators.

#### **PIN CONNECTIONS**

| 11<br>12<br>13<br>14<br>15<br>16 | SIN <sub>3</sub> V <sub>DD</sub> SIN <sub>4</sub> SIN <sub>5</sub> SIN <sub>6</sub> SIN <sub>7</sub> SIN <sub>8</sub> | 19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33 | SIN <sub>10</sub> SIN <sub>11</sub> V <sub>SS</sub> CLK V <sub>SS</sub> RESET V <sub>SS</sub> COS <sub>0</sub> COS <sub>1</sub> COS <sub>2</sub> COS <sub>3</sub> COS <sub>4</sub> COS <sub>5</sub> COS <sub>6</sub> V <sub>DD</sub> COS <sub>7</sub> | 36<br>37<br>38<br>39<br>40<br>41<br>42<br>43<br>44<br>45<br>46<br>47<br>48<br>49<br>50 | COS <sub>9</sub> COS <sub>10</sub> COS <sub>11</sub> Q <sub>0</sub> Q <sub>1</sub> Q <sub>2</sub> Q <sub>3</sub> Q <sub>4</sub> V <sub>SS</sub> Q <sub>5</sub> Q <sub>6</sub> Q <sub>7</sub> Q <sub>8</sub> Q <sub>9</sub> Q <sub>10</sub> Q <sub>11</sub> | 53<br>54<br>55<br>56<br>57<br>58<br>59<br>60<br>61<br>62<br>63<br>64<br>65<br>66<br>67 | SUB  V <sub>SS</sub> V <sub>DD</sub> OUT <sub>0</sub> OUT <sub>1</sub> I.C.  V <sub>SS</sub> OUT <sub>2</sub> OUT <sub>3</sub> OUT <sub>4</sub> OUT <sub>5</sub> OUT <sub>6</sub> V <sub>SS</sub> OUT <sub>7</sub> OUT <sub>8</sub> OUT <sub>9</sub> | 70<br>71<br>72<br>73<br>74<br>75<br>76<br>77<br>78<br>79<br>80<br>81<br>82<br>83 | I <sub>1</sub> I <sub>2</sub> I <sub>3</sub> I <sub>4</sub> |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------|

| 16                               | -                                                                                                                     | 33                                                                                     |                                                                                                                                                                                                                                                       | 50                                                                                     |                                                                                                                                                                                                                                                            | 67                                                                                     | V                                                                                                                                                                                                                                                    |                                                                                  | •                                                           |

|                                  |                                                                                                                       |                                                                                        |                                                                                                                                                                                                                                                       |                                                                                        |                                                                                                                                                                                                                                                            |                                                                                        |                                                                                                                                                                                                                                                      |                                                                                  |                                                             |

Note: I.C. denotes Internal Connection. These pins must be left unconnected. Do not use for vias.

N.C. denotes No Connection. Can be used for vias.

### FUNCTION BLOCK DESCRIPTION

#### FORMAT CONVERSION BLOCKS

These blocks are used to convert the format of the input signals on the SIN<sub>11-0</sub> and COS<sub>11-0</sub> input busses from offset binary to the two's complement format used internally when the OBEN signal is set high.

#### **MULTIPLIER BLOCKS**

The multiplier blocks form the core of the QAM function. The two 12-bit signed inputs to each multiplier produce a 23-bit product, but this is truncated in the multipliers and only the 13 most significant bits are actually generated. The two 12-bit by 12-bit multipliers are pipelined and start a new 13-bit product every clock cycle. As a result, the STEL-1130 has a maximum throughput rate of 60 MHz.

#### **ROUNDING BLOCKS**

The two rounding blocks modify the 13-bit products from the multipliers to produce 12-bit rounded products when the **ROUND** signal is set high. The products will be truncated to 12 bits when **ROUND** is set low.

#### ADD/SUBTRACT BLOCK

This block is used to add or subtract the products from the multipliers. The resulting 13-bit sum-of-products is brought out on the OUT<sub>12-0</sub> bus in Two's Complement. Note that when ADDEN is set low the output is the 12-bit Q\*COS signal, in which case the MSB (OUT<sub>12</sub>) will be invalid.

#### **MUX BLOCK**

This block selects the data brought out on the  $OUT_{12-0}$  bus, depending on the state of the ADDEN input. When this signal is set high the function available at the  $OUT_{12-0}$  bus is  $I*SIN\pm Q*COS$ , and when it is set low the function available is Q\*COS.

#### **INPUT SIGNALS**

#### RESET

The RESET input is asynchronous and active low, and clears all the registers in the device. When RESET goes low, all registers are cleared within 20 nsecs, and normal operation will resume after this signal returns high. The data on the OUT<sub>12-0</sub> bus will remain at zero for 18 clock cycles after RESET returns high.

#### **CLOCK**

All synchronous functions performed within the NCO are referenced to the rising edge of the CLOCK input. The CLOCK signal should be nominally a square wave at a maximum frequency of 60 MHz. A non-repetitive CLOCK waveform is permissible as long as the minimum duration positive or negative pulse on the waveform is always greater than 5 nanoseconds.

I<sub>11</sub> through I<sub>0</sub>

Signals on the 12-bit  $I_{11-0}$  bus are multiplied by the signals on the  $SIN_{11-0}$  bus to form a 13-bit truncated product. This product is then rounded or truncated to a 12-bit product before being loaded into the Add/Subtract and Mux Blocks. There is a 16/18-cycle pipeline delay from when a value is applied at the  $I_{11-0}$  bus to the result of this value appearing at the output (see **ADDEN**).

#### Q<sub>11</sub> through Q<sub>0</sub>

Signals on the 12-bit  $\mathbf{Q}_{11-0}$  bus are multiplied by the signals on the  $\mathbf{COS}_{11-0}$  bus to form a 13-bit truncated product. This product is then rounded or truncated to a 12-bit product before being loaded into the Add/Subtract Block. There is a 16/18-cycle pipeline delay from when a value is applied at the  $\mathbf{Q}_{11-0}$  bus to the result of this value appearing at the output (see ADDEN).

#### SIN<sub>11</sub> through SIN<sub>0</sub>

Signals on the 12-bit  $SIN_{11-0}$  bus are multiplied by the signals on the  $I_{11-0}$  bus to form a 13-bit truncated product. This product is then rounded or truncated to a 12-bit product before being loaded into the Add/Subtract and Mux Blocks. There is a 16/18-cycle pipeline delay from when a value is applied at the  $SIN_{11-0}$  bus to the result of this value appearing at the output (see **ADDEN**).

#### COS<sub>11</sub> through COS<sub>0</sub>

Signals on the 12-bit  $COS_{11-0}$  bus are multiplied by the signals on the  $Q_{11-0}$  bus to form a 13-bit truncated product. This product is then rounded or truncated to a 12-bit product before being loaded into the Add/Subtract Block. There is a 16/18-cycle pipeline delay from when a value is applied at the  $COS_{11-0}$  bus to the result of this value appearing at the output (see ADDEN).

#### **OBEN**

The Offset Binary Enable signal controls the function of the Format Conversion Blocks. When this signal is set high the signals on the SIN<sub>11-0</sub> and COS<sub>11-0</sub> busses are converted from Offset Binary Format to the Two's Complement format used internally. Offset Binary is the format of the output signals of most NCOs, including both the STEL-1172B and the STEL-1177. When it is set low no conversion takes place, allowing signals in Two's Complement format to be used on these busses.

#### **ROUND**

The **ROUND** signal controls the function of the Rounding Blocks. When this signal is set high the 13-bit products from the two multipliers are rounded to 12-bit products, and when it is set low the products are truncated to 12 bits. If this signal is changed during operation of the device the result will appear at the output after a 5 clock cycle delay.

#### SUB

The Subtract signal controls the function of the Add/Subtract Block. When this signal is set high the function performed is I\*SIN - Q\*COS, and when it is set low the function performed is I\*SIN + Q\*COS. If this signal is changed during operation of the device the result will appear at the output after a 4 clock cycle delay.

#### **ADDEN**

The Add Enable signal controls the function of the Mux Block. When this signal is set high the function available at the  $OUT_{12-0}$  bus is  $I^*SIN \pm Q^*COS$ , and when it is set low the function available is  $Q^*COS$ . When ADDEN is set low the output is the 12-bit  $Q^*COS$  signal, in which case the MSB  $(OUT_{12})$  will be invalid. If this signal is changed during operation of the device the result will appear at the output after a 1 clock cycle delay. Note that when ADDEN is set high the pipeline delays from the  $SIN_{11-0}$ ,  $COS_{11-0}$ ,  $I_{11-0}$ , and  $Q_{11-0}$ , inputs is increased from 16 to 18 clock cycles.

#### **OUTPUT SIGNALS**

#### **OUT<sub>12-0</sub>**

The signal appearing on the OUT<sub>12-0</sub> output bus is the output of the Mux Block. When ADDEN is set low the output is the 12-bit Q\*COS signal, in which case the MSB (OUT<sub>12</sub>) will be invalid. The output data format is Two's Complement at all times.

## ELECTRICAL CHARACTERISTICS ABSOLUTE MAXIMUM RATINGS

Warning: Stresses greater than those shown below may cause permanent damage to the device. Exposure of the device to these conditions for extended periods may also affect device reliability. All voltages are referenced to  $V_{\rm ss}$ .

| Symbol               | Parameter                         | Range           | Units                |

|----------------------|-----------------------------------|-----------------|----------------------|

| $T_{stg}$            | Storage Temperature               | ∫-40 to +125    | °C (Plastic package) |

|                      |                                   | -65 to +150     | °C (Ceramic package) |

| $V_{\mathrm{DDmax}}$ | Supply voltage on V <sub>DD</sub> | -0.3 to + 7     | volts                |

| $V_{I(max)}$         | Input voltage                     | -0.3 to VDD + 0 | .B volts             |

| $\mathbf{I_i}$       | DC input current                  | ± 10            | mA                   |

#### RECOMMENDED OPERATING CONDITIONS

| Symbol         | Parameter                       | Range       | Units                         |  |  |

|----------------|---------------------------------|-------------|-------------------------------|--|--|

| $V_{DD}$       | Supply Voltage                  | ∫ +5±5%     | Volts (Commercial Conditions) |  |  |

|                |                                 | \ +5 ± 10%  | Volts (Military Conditions)   |  |  |

| T <sub>a</sub> | Operating Temperature (Ambient) | ∫ 0 to +70  | °C (Commercial Conditions)    |  |  |

|                |                                 | _55 to +125 | °C (Military Conditions)      |  |  |

### **D.C. CHARACTERISTICS** (Operating Conditions: $V_{DD}=5.0~V~\pm5\%$ , $V_{SS}=0~V$ , $T_a=0^\circ$ to 70° C, Commercial $V_{DD}=5.0~V~\pm10\%$ , $V_{SS}=0~V$ , $T_a=-55^\circ$ to 125° C, Military

| Symbol                              | Parameter                               | Min. | Тур.        | Max. | Units    | Conditions                        |

|-------------------------------------|-----------------------------------------|------|-------------|------|----------|-----------------------------------|

| $I_{DD(Q)}$                         | Supply Current, Quiescent               |      |             | 1.0  | mA       | Static, no clock                  |

| $I_{DD}$                            | Supply Current, Operational             |      |             | 2.0  | mA/MHz   | $f_{CLK} = 60 \text{ MHz}$        |

| V <sub>IH(min)</sub>                | High Level Input Voltage                |      |             |      |          |                                   |

|                                     | Commercial Operating Conditions         | 2.0  |             |      | volts    | Logic '1'                         |

|                                     | Military Operating Conditions           | 2.25 |             |      | volts    | Logic '1'                         |

| V <sub>IL(max)</sub>                | Low Level Input Voltage                 |      |             | 0.8  | volts    | Logic '0'                         |

| I <sub>IL(max)</sub>                | Low Level Input Current                 | -130 | -45         | -15  | μА       | All inputs, $V_{IN} = V_{SS}$     |

| V <sub>OH(min)</sub>                | High Level Output Voltage               | 2.4  | 4.5         |      | volts    | $I_O = -4.0 \text{ mA}$           |

| V <sub>OL(max)</sub>                | Low Level Output Voltage                |      | 0.2         | 0.4  | volts    | $I_0 = +4.0 \text{ mA}$           |

| Ios                                 | Output Short Circuit Current            | 20   | 65          | 130  | mA       | $V_{OUT} = V_{DD}, V_{DD} = max$  |

|                                     |                                         | -10  | <b>-4</b> 5 | -130 | mA       | $V_{OUT} = V_{SS}, V_{DD} = \max$ |

| C <sub>IN</sub><br>C <sub>OUT</sub> | Input Capacitance<br>Output Capacitance |      | 2<br>4      |      | pF<br>pF | All inputs<br>All outputs         |

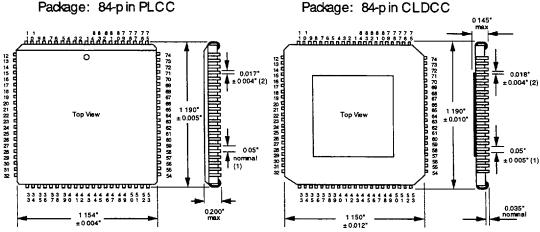

#### **TIMING DIAGRAM**

#### **ELECTRICAL CHARACTERISTICS**

**A.C. CHARACTERISTICS** (Operating Conditions:  $V_{DD}=5.0~V~\pm5\%$ ,  $V_{SS}=0~V$ ,  $T_a=0^\circ$  to 70° C, Commercial  $V_{DD}=5.0~V~\pm10\%$ ,  $V_{SS}=0~V$ ,  $T_a=-55^\circ$  to 125° C, Military

|                 |                                                 | Commercial |      |      | Military |      |      |       |                       |

|-----------------|-------------------------------------------------|------------|------|------|----------|------|------|-------|-----------------------|

| Symbol          | Parameter                                       | Min.       | Тур. | Max. | Min.     | Тур. | Max. | Units | Conditions            |

| t <sub>RS</sub> | RESET pulse width                               | 20         | ł    |      | 25       |      |      | nsec. |                       |

| t <sub>SR</sub> | RESET to CLOCK Setup                            | 7          |      |      | 9        |      |      | nsec. |                       |

| t <sub>CH</sub> | CLOCK High                                      | 5          |      |      | 6        |      |      | nsec. |                       |

| t <sub>CL</sub> | CLOCK Low                                       | 5          |      |      | 6        |      |      | nsec. |                       |

| t <sub>SU</sub> | ADDEN, OBEN, ROUND,                             | 5          |      |      | 5        | ļ    |      | nsec. |                       |

|                 | SUB, SIN <sub>11-0</sub> or COS <sub>11-0</sub> |            |      |      |          |      |      |       |                       |

|                 | to CLOCK Setup                                  |            |      |      |          |      |      |       |                       |

| t <sub>HD</sub> | ADDEN, OBEN, ROUND,                             | 6          |      |      | 7        |      |      | nsec. | <del> </del>          |

|                 | SUB, SIN or COS                                 |            |      |      |          |      |      | }     |                       |

|                 | to CLOCK Hold                                   |            |      |      |          |      |      |       |                       |

| t <sub>CD</sub> | CLOCK to OUT <sub>11-0</sub> Delay              | 3          |      | 12   | 2        |      | 20   | nsec. | $C_L = 15 \text{ pF}$ |

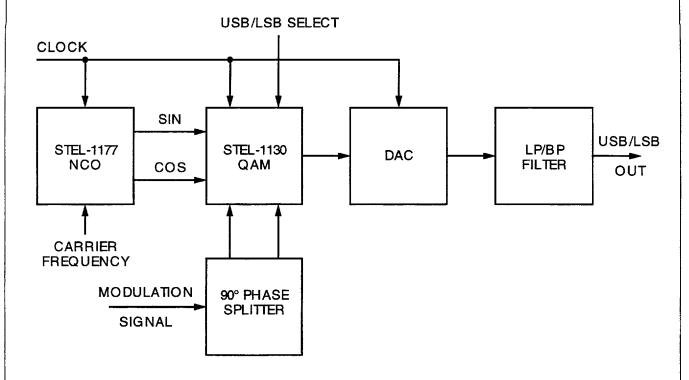

#### **TYPICAL APPLICATION - SINGLE SIDEBAND MODULATOR**

By utilizing the trigonometric identities:

$$\sin(\omega_c) \cdot \sin(\omega_m) = \frac{1}{2}\cos(\omega_c - \omega_m) - \frac{1}{2}\cos(\omega_c + \omega_m)$$

and

$$\cos(\omega_c) \cdot \cos(\omega_m) = \frac{1}{2}\cos(\omega_c - \omega_m) + \frac{1}{2}\cos(\omega_c + \omega_m)$$

it is possible to generate either an upper sideband ( $\omega_c + \omega_m$ ) or lower sideband ( $\omega_c - \omega_m$ ) signal directly without any need for a sharp cutoff filter to eliminate the unwanted sideband. The sum of the products gives the lower sideband signal and the difference of the products gives the upper sideband. Thus it is even possible to switch the sideband generated simply by toggling the SUB control signal on the STEL-1130, a feat not possible in conventional SSB modulators without using dual sideband filters.

# FOR FURTHER INFORMATION CALL OR WRITE STANFORD TELECOMMUNICATIONS

#### **Telecom Component Products**

Tel: (408) 541-9031 Fax: (408) 541-9030

480 Java Drive • Sunnyvale, CA 94089-1125

© 1991 - 1993 Stanford Telecommunications, Inc. 10/93