# T7274A Quad Differential Line Driver

#### **Features**

- Four line drivers per package

- Complementary outputs from each line driver

- 24-mA drive capability

- High output drive for 100- $\Omega$ , 110- $\Omega$ , and 150- $\Omega$  lines

- 2.0-ns minimum and 4.75-ns maximum propagation delays

- 0.1-ns output skew, typical

- 140 Mb/s data rate

- 300-mW maximum power dissipation

- Single 5 V supply

- 0 to 85 °C operating temperature

#### Description

The T7274A Quad Differential Line Driver integrated circuit is a single-input-to-balanced-output converter that drives differential transmission lines. The input requires typical CMOS signals, and the output has typical CMOS voltage swings and can drive  $100-\Omega$ ,  $110-\Omega$ , and  $150-\Omega$  twisted pair lines through a resistor attenuation network.

This CMOS device is similar to the general-trade 26LS31 device; however, it has decreased power consumption and generates lower levels of electromagnetic interference (EMI).

The T7274A line driver is compatible with many line receivers, including the AT&T T7275B and 41LF devices and the general-trade 26LS32 device. The quad differential line driver is available in a 16-pin plastic DIP and small-outline J-lead (SOJ) package.

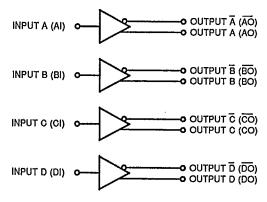

Figure 1. Logic Diagram

www.DataSheet4U.com

#### **User Information**

## **Pin Descriptions**

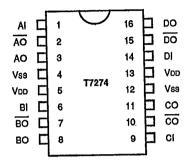

Figure 2. Pin Function Diagram

## Table 1. Pin Descriptions

| Symbol | Туре | Name                          |

|--------|------|-------------------------------|

| Al     | 1    | A-line driver input           |

| ĀŌ     | 0    | Inverted A-line_driver output |

| AO     | 0    | A-line driver output          |

| BI     | 1    | B-line driver input           |

| BO     | 0    | Inverted B-line driver output |

| во     | 0    | B-line driver output          |

| CI     | 1    | C-line driver input           |

| CO     | 0    | Inverted C-line driver output |

| co     | 0    | C-line driver output          |

| DI     | ı    | D-line driver input           |

| DO     | 0    | Inverted D-line driver output |

| DO     | 0_   | D-line driver output          |

| Vss    |      | Ground pins                   |

| VDD    |      | 5 V supply plns               |

#### **Characteristics**

# **Electrical Characteristics**

TA = 0 to 85 °C, VDD =  $5.0 \text{ V} \pm 0.25 \text{ V}$

| Parameter                                                                |                   | Min       | Тур             | Max           | Unit        |

|--------------------------------------------------------------------------|-------------------|-----------|-----------------|---------------|-------------|

| Output voltages, VDD = 4.75 V:* low, loL = +12.5 mA high, loH = -12.5 mA | Vol<br>Voh        | <br>4.25  | _               | 0.5<br>—      | V<br>V      |

| Output Impedance                                                         |                   |           | 20              | 40            | Ω           |

| Input voltages:** low high threshold                                     | VIL<br>VIH<br>VTH | 3.75<br>— | —<br>—<br>VDD/2 | 1.0<br>—<br>— | V<br>V<br>V |

| Output currents, short-circuit                                           | Isc               | -100      | _               | _200          | mA          |

| Input currents, VDD = 5.25 V:<br>low, ViN = 0.5 V<br>hlgh, VIN = 5.25 V  | IIL<br>IIH        |           | <u>-</u>        | -1.0<br>100   | μA<br>μA    |

| Power supply current, VDD = 5.25 V:<br>DC conditions<br>100 Mb/s         | IDD<br>IDD        | _<br>     | 0.25<br>75      | 0.5<br>80     | mA<br>mA    |

<sup>\*</sup> lot and lon can increase to 25 mA. The reduced Vol. and Von are computed from the output limple that splice the 4U.com \*\* Each input has typically 100 kΩ to Vss. Thus, a no connect input is pulled low.

### Maximum Ratings

| T-75-45-07 |

|------------|

|------------|

| Power supply voltage (VDD)               | 701/  |

|------------------------------------------|-------|

| Ambient operating temperature (TA) range | 7.U V |

| Storage temperature (Tstg) range         | 5 °C  |

| _40 to ±10                               | 5 VC  |

Maximum ratings are the limiting conditions that can be applied under all variations of circuit and environmental conditions without the occurrence of permanent damage.

External leads can be bonded or soldered safely at temperatures up to 300 °C.

#### **Timing Characteristics**

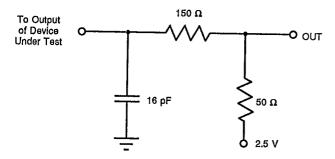

TA = 0 to 85 °C, VDD = 5.0 V  $\pm$  0.25 V, test circuit connected to output (see Figure 3).\*

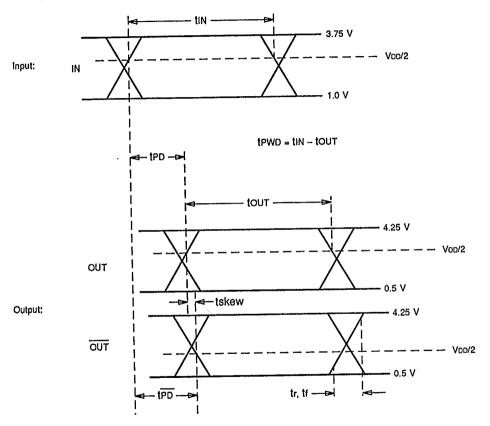

| Symbol     | Description                                                                 | Min        | Тур        | Max          | Unit     |

|------------|-----------------------------------------------------------------------------|------------|------------|--------------|----------|

| tPD<br>tPD | Propagation delay, input to output:  AO, BO, CO, and DO  AO, BO, CO, and DO | 2.0<br>2.0 | 3.0<br>3.0 | 4.75<br>4.75 | ns<br>ns |

| tskew      | Difference between propagation delays                                       |            | 100        | 300          | ps       |

| tPWD       | Pulse width distortion,   tin - tout                                        |            | 200        | 500          | ps       |

| tr, tf     | Rise and fall time (10% to 90%)                                             |            | 1.5        | 3.0          | ns       |

| tin        | Input pulse width                                                           | 7          | _          |              | ns       |

Input rise and fall times (10% to 90%) of less than 4 ns are necessary to guarantee maximum propagation delay, pulse width distortion, and skew characteristics.

Figure 3. Timing Test Circuit

www.DataSheet4U.com

#### **Timing Diagram**

Figure 4. Timing Waveforms