# DATA SHEET

# MOS INTEGRATED CIRCUIT $\mu$ PD30450

# VR4200™ 64-BIT MICROPROCESSOR

#### DESCRIPTION

The  $\mu$ PD30450 (VR4200) is one of NEC's RISC (Reduced Instruction Set Computer) microprocessors, VR series™, and is a high-performance 64-bit microprocessor employing the RISC architecture developed by MIPS.

The Vn4200 is intended for high-performance, low-cost systems, and features low power dissipation and low cost to realize low-power application.

The detailed functions of the Va4200 are described in the following manual. Be sure to read this manual in designing your system.

• VR4200 User's Manual: IEU-1392

#### **FEATURES**

- Employment of RISC architecture developed by MIPS

- · High-speed operation processing

- 5-stage pipeline processing

- : 55 SPECint92 · Integer operation performance Floating-point operation performance: 30 SPECfp92

- 64-bit registers, integer operation unit, floating-point operation unit

- Instruction set compatible with VR4000™ series (conforming to MIPS-I/II/III)

- Internal operating frequency: 80 MHz (input clock: 40 MHz)

- Cache memory (instruction: 16 KB, data: 8 KB)

- Low power dissipation (1.5 W TYP.)

- Low power mode

- System interface compatible with Vn4000PC™

- Supply voltage: 3.3 V

#### **APPLICATION**

- Work station of low-end model

- Battery-driven laptop or notebook type personal computers

- Embedded controller, etc.

#### ORDERING INFORMATION

μPD30450GD-80MML

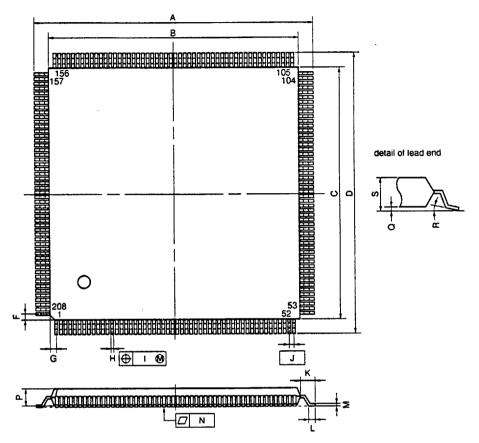

Maximum Internal Operating Frequency Pakage Part Number (MHz) 80 208-pin plastic QFP (fine pitch) (28 x 28 mm)

The information in this document is subject to change without notice.

Document No. U10127EJ2V0DS00 (2nd edition) (Previous No. ID-3194) Date Published October 1995 P Printed in Japan

The mark ★ shows major revised points.

KA 6427525 0088654 428 KA

© NEC Corporation 1994 © MIPS Technologies Inc. 1992

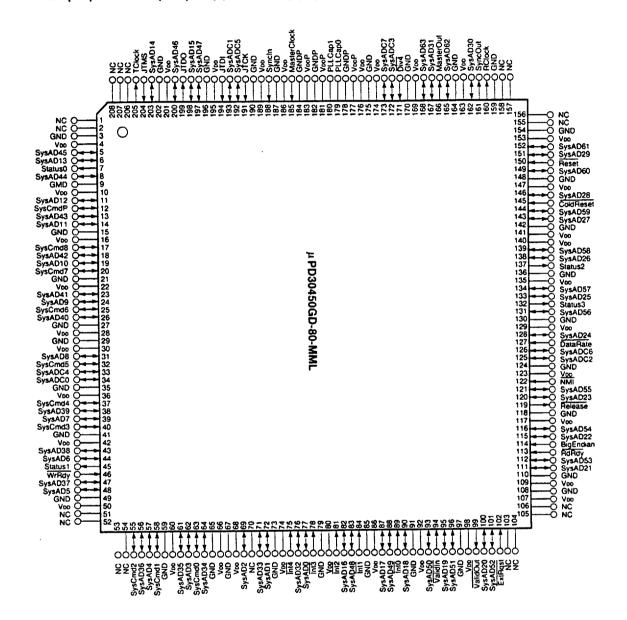

#### PIN CONFIGURATION

• 208-pin plastic QFP (fine pitch) (28 × 28 mm) (Top View)

#### Pin Name

BigEndian Big endian ColdReset Cold reset DataRate Data Rate Div4 Divide by 4 ExtRast External request Int (4:0) Interrupt request **JTCK** JTAG clock input JTDI JTAG data in **JTDO** JTAG data out

JTMS : JTAG command signal

MasterClock : Master clock

MasterOut : Master clock out

NMI : Non-maskable interrupt request PLLCap (1:0) : Phase Locked loop capacitance

RClock : Receive clock

RdRdy : Read ready

Release : Release

Reset : Reset

Status (3:0) : Status

SyncIn : Synchronization clock input

SyncOut : Synchronization clock output

SysAD (63:0) : System address/data bus

SysADC (7:0) : System address/data check

SysCmd (8:0) : System command/data ID bus

SysCmdP : System command parity

TClock : Transmit clock

ValidIn : Valid in

ValidOut : Valid out

WrRdy : Write ready

Vpo : Power supply

V<sub>DD</sub>P : Power supply for PLL

GND : Ground

GNDP : Ground for PLL NC : No Connection

# CONTENTS

| 1. | PIN                  | FUNCT                              | TONS                                       | 6  |  |  |  |  |  |  |

|----|----------------------|------------------------------------|--------------------------------------------|----|--|--|--|--|--|--|

| 2. | CPL                  |                                    | NAL ARCHITECTURE                           | 8  |  |  |  |  |  |  |

|    | 2.1                  |                                    | e                                          | 8  |  |  |  |  |  |  |

|    | 2.2                  | Interna                            | I Function Blocks                          | 9  |  |  |  |  |  |  |

|    | 2.3                  | Regist                             | 9rs                                        | 11 |  |  |  |  |  |  |

|    |                      | 2.3.1                              | CPU registers                              | 11 |  |  |  |  |  |  |

|    |                      | 2.3.2                              | CP0 registers                              | 12 |  |  |  |  |  |  |

|    | 2.4                  | Data F                             | ormat                                      | 14 |  |  |  |  |  |  |

|    | 2.5                  | Cache                              |                                            | 15 |  |  |  |  |  |  |

|    | 2.6                  | Virtual                            | Storage                                    | 17 |  |  |  |  |  |  |

|    |                      | 2.6.1                              | Virtual address space                      | 17 |  |  |  |  |  |  |

|    |                      | 2.6.2                              | Address conversion                         | 20 |  |  |  |  |  |  |

|    | 2.7                  | Except                             | tion Processing                            | 21 |  |  |  |  |  |  |

| 3. | FPL                  | INTER                              | NAL ARCHITECTURE                           | 22 |  |  |  |  |  |  |

|    | 3.1                  | FPU R                              | egisters                                   | 22 |  |  |  |  |  |  |

|    | 3.2                  | Data F                             | ormat                                      | 23 |  |  |  |  |  |  |

| 4. | INT                  | INTERFACE                          |                                            |    |  |  |  |  |  |  |

|    | 4.1 System Interface |                                    |                                            |    |  |  |  |  |  |  |

|    |                      | 4.1.1                              | System interface request                   | 24 |  |  |  |  |  |  |

|    |                      | 4.1.2                              | Data transfer rate control                 | 25 |  |  |  |  |  |  |

|    |                      | 4.1.3                              | Clock interface                            | 25 |  |  |  |  |  |  |

|    |                      | 4.1.4                              | Setting division ratio of system interface | 25 |  |  |  |  |  |  |

| 5. | INT                  | INTERNAL/EXTERNAL CONTROL FUNCTION |                                            |    |  |  |  |  |  |  |

|    | 5.1                  | Reset                              | Function                                   | 26 |  |  |  |  |  |  |

|    | 5.2                  | interru                            | pt Function                                | 26 |  |  |  |  |  |  |

|    | 5.3                  | JTAG                               | Boundary Scan Function                     | 27 |  |  |  |  |  |  |

|    | 5.4                  | Low P                              | ower Dissipation Design                    | 27 |  |  |  |  |  |  |

|    | 5.5                  | Low P                              | ower Mode                                  | 27 |  |  |  |  |  |  |

|    | 5.6                  | Hardw                              | are Debug Support Function                 | 28 |  |  |  |  |  |  |

|    |                      | 5.6.1                              | Output of internal processor status        | 28 |  |  |  |  |  |  |

|    |                      | 5.6.2                              | Output of branch destination address       | 28 |  |  |  |  |  |  |

| 6. | INS                  | TRUCT                              | ION SET                                    | 29 |  |  |  |  |  |  |

|    | 6.1                  |                                    |                                            |    |  |  |  |  |  |  |

|    | 6.2                  |                                    | nstruction Set                             | 29 |  |  |  |  |  |  |

|    | 6.3                  |                                    |                                            |    |  |  |  |  |  |  |

|    | 6.4                  |                                    | ction Execution Time                       | 36 |  |  |  |  |  |  |

|    | ٠.,                  | 6.4.1                              | · · · · · · · ·                            | 36 |  |  |  |  |  |  |

|    |                      | •                                  | FPU instruction                            | 37 |  |  |  |  |  |  |

| 7. | ELECTRICAL SPECIFICATIONS                                 | 39 |

|----|-----------------------------------------------------------|----|

| 8. | PACKAGE DRAWING                                           | 45 |

| 9. | RECOMMENDED SOLDERING CONDITION                           | 46 |

| ΑP | PENDIX DIFFERENCES AMONG VR4200, VR4000PC, AND VR4400PCTM | 47 |

# 1. PIN FUNCTIONS

| Pin Name     | Function                                                                                                                                                           | 1/0            |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| ExtRqest     | External request.  This signal is issued by an external agent to request permission to issue an external request.                                                  | ı              |

| Release      | Releases interface.  This signal indicates that the processor releases the system interface to the slave status in response to the ExtRqst signal.                 | 0              |

| RdRdy        | Read ready.  This signal indicates that the external agent is ready to accept a read request from the processor.                                                   | ı              |

| SysAD (63:0) | System address/data bus.  These pins form a 64-bit address/data bus for communication between the processor and external agent.                                    | 1/O<br>(3-stat |

| SysADC (7:0) | System address/data chek bus.  These pins form an 8-bit bus including a check bit for the SysAD bus.                                                               | I/O<br>(3-stat |

| SysCmd (8:0) | System command/data ID bus.  These pins form a 9-bit bus for communication of commands and data identifiers between the processor and external agent.              | I/O<br>(3-stat |

| SysCmdP      | System command/data ID bus parity. This is an even parity bit for the SysCmd bus.                                                                                  | I/O<br>(3-stat |

| Validln      | Valid in.  This signal indicates that the external agent drives a valid address or data on the SysAD bus and a valid command or data identifier on the SysCmd bus. | l              |

| ValidOut     | Valid out.  This signal indicates that the processor drives a valid address or data on the SysAD bus and a valid command or data identifier on the SysCmd bus.     | 0              |

| WrRdy        | Write ready.  This signal indicates that the external agent is ready to accept a write request from the processor.                                                 | ı              |

| Int (4:0)    | Interrupt.  These are general processor interrupt requests by which the input statuses of bits 14 to 10 of the cause register can be checked.                      |                |

| NMI          | Non-maskable interrupt.  This is an interrupt request that cannot be masked.                                                                                       | 1              |

| JTDI         | JTAG data input. Inputs JTAG serial data.                                                                                                                          | t              |

| JTCK         | JTAG clock input. Inputs JTAG serial clock. If the tag interface is not used, please set it to low level.                                                          | ı              |

| JTDO         | JTAG data output. Outputs JTAG serial clock.                                                                                                                       | 0              |

| JTMS         | JTAG command.  JTAG command signal. Indicates that the input serial data is command data.                                                                          | 1              |

| MasterClock  | Master clock.  Inputs the master clock as the operating frequency of the processor.                                                                                | ı              |

\*

| Pin Name     | Function                                                                                                                                                                                                                                                                           | 1/0 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| MasterOut    | Master clock output.  Master clock output in synchronization with the master clock.                                                                                                                                                                                                | 0   |

| RClock       | Receive clock.  Received clock as the system interface frequency.                                                                                                                                                                                                                  | 0   |

| TClock       | Transmit clock. Transmit clock as the system interface frequency.                                                                                                                                                                                                                  | 0   |

| SyncOut      | Synchronization clock output.  Outputs a synchronization clock. SyncOut must be connected to SyncIn via the model of delay cause among MasterOut, TClock, RClock, and external agent.                                                                                              | 0   |

| Syncin       | Synchronization clock input. Inputs a synchronization clock.                                                                                                                                                                                                                       | 1   |

| ColdReset    | Cold reset.  This signal is asserted on power-ON reset or cold reset.  SClock, TClock, and RClock start output in synchronization with the deassert edge of this signal. This signal must also be deasserted in synchronization with MasterClock.                                  | ı   |

| Reset        | Reset.  This signal is asserted on power-ON reset, cold reset, or software reset.  This signal must be deasserted in synchronization with MasterClock.                                                                                                                             | ı   |

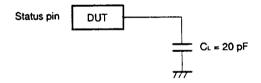

| Status (3:0) | Status display.  These pins output the internal statuses of the current processor cycle.                                                                                                                                                                                           | 0   |

| BigEndian ·  | Big endian. Sets the endian mode of the system interface. 0: little endian, 1: big endian                                                                                                                                                                                          | ı   |

| DataRate     | Data transfer rate.  Sets the transfer rate of data at which the processor transfers data to the external agent.  0: DDx, 1: Dxx                                                                                                                                                   | ١   |

| Div4         | Divide by 4 (operating frequency of system interface).  Sets the division ratio of the system interface frequency with respect to the pipeline clock.  0: 1/4PClock, 1: 1/2PClock  However, a setting through this pin is not supported by the current Va4200.  Fix this pin to 1. | 1   |

| PLLCap (1:0) | Phase Locked Loop capacitance.  Connect a capacitor to adjust the internal PLL across these pins.                                                                                                                                                                                  |     |

| VooP         | Voo for PLL. Power supply for the internal PLL.                                                                                                                                                                                                                                    | _   |

| GNDP         | Ground for PLL. Ground for the internal PLL.                                                                                                                                                                                                                                       | _   |

| Voo          | Power supply                                                                                                                                                                                                                                                                       |     |

| GND          | Ground                                                                                                                                                                                                                                                                             | _   |

#### 2. CPU INTERNAL ARCHITECTURE

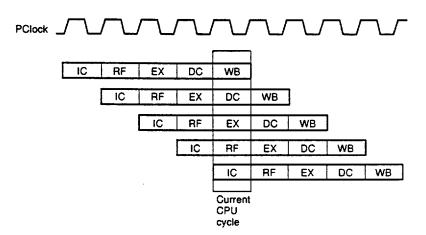

# 2.1 Pipeline

Each instruction is executed in the following five steps:

- (1) IC Instruction cache fetch

- (2) RF Register fetch

- (3) EX Execution

- (4) DC Data cache fetch

- (5) WR Write back

The Va4200 uses a 5-stage pipeline. The pipeline operates in accordance with a clock (PClock) two times that of MasterClock, and instructions are executed at almost one per cycle. Therefore, ordinary instructions are executed overlapping with each other, as shown in Figure 2-1.

Figure 2-1. Pipeline of VR4200 (5 stages)

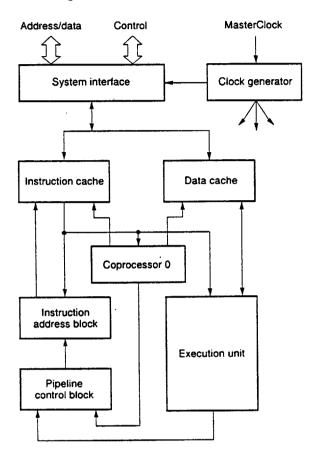

# 2.2 Internal Function Blocks

The Vn4200 consists of several functional blocks, such as an execution unit, coprocessor 0, instruction cache, data cache, and system interface.

Figure 2-2. Internal Block Diagram

#### (1) System interface

This block performs interfacing when the processor accesses an external device (such as a memory). This interface is compatible with the system interface bus used by the Va4000. The external device is accessed by a 64-bit address/data multiplexed bus.

#### (2) Clock generator

The clock generator doubles the frequency of an externally input clock (MasterClock) to generate a pipeline clock (PClock). PClock is further divided by two and used as a system interface clock.

#### (3) Instruction cache

The instruction cache consists of direct mapping, virtual index, and physical tag type, and has a capacity of 16K bytes.

#### (4) Execution unit

This block executes integer and floating-point operations. It consists of a 64-bit register file, 64-bit integer/mantissa data bus, and exponent data bus.

#### (5) Coprocessor 0 (CP0)

This block performs exception processing. It contains a memory management unit (MMU), and manages addresses. Virtual addresses are converted into physical addresses by TLB (Translation Lookaside Buffer: high-speed conversion buffer mechanism).

#### (6) Data cache

This cache consists of direct mapping, virtual index, and physical tag type, and has a capacity of 8K bytes.

#### (7) Instruction address block

This block calculates the effective address of the instruction to be fetched next. It consists of a program counter (PC) increment block, target address addition block, and branch address select block.

#### (8) Pipeline control block

This block controls stall so that the pipeline can operate normally.

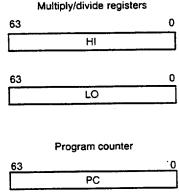

#### 2.3 Registers

#### 2.3.1 CPU registers

Figure 2-3 shows the CPU registers of the Vn4200. The bit width of these registers is determined by the operation mode of the processor (in 32-bit mode: 32 bits, in 64-bit mode: 64 bits).

Of the 32 general registers, the following two have special meanings:

- Register r0: The contents of this register are always 0. This register can be described as the target register of an instruction when the result of an operation is to be discarded. When the value of 0 is necessary, this register can be used as a source register.

- Register r31: This register is a link register for the JAL and JALR instructions. Therefore, do not use this register by any other instructions.

The two multiply/divide registers (HI, LO) store the result of an integer multiplication, or the quotient (LO) and remainder (HI) resulting from an integer division.

Figure 2-3. CPU Registers

General registers Multiply/div

|     | 0                                    |

|-----|--------------------------------------|

| r0  |                                      |

| r1  |                                      |

| r2  |                                      |

| •   |                                      |

| •   |                                      |

| •   |                                      |

| 129 |                                      |

| r30 |                                      |

| r31 |                                      |

|     | r0<br>r1<br>r2<br>·<br>·<br>·<br>r29 |

No program status word (PSW) is provided. The function of the PSW is executed by the status register and cause register integrated to the system control coprocessor (CP0).

# 2.3.2 CP0 registers

The system control coprocessor 0 (CP0) supports virtual memory systems and exception processing.

Registers used for memory management system Registers used for exception processing Entry Lo0 2\* BadVAddr Entry Hi Index Context 10° Entry Lo1 Count Compare Random 1. 11" 31 Status Cause Page mask 12\* 13\* TLB **EPC** Watch Lo Wired PRId Watch Hi X context ("Safe" entry) 15\* 19\* 201 0 127 0 Cache error Parity error Config 16\* Error EPC LLAddr Tag Lo Tag Hi 17\* 28\* 29.

Figure 2-4. CP0 Registers

Remark "\*" indicates a register number.

Table 2-1. CP0 Registers

| No.   | Register     | Description                                           |

|-------|--------------|-------------------------------------------------------|

| 0     | Index        | Programmable pointer to TLB array                     |

| 1 1   | Random       | Pseudo random pointer to TLB array (read only)        |

| 2     | Entry Lo0    | Second half of TLB entry for even VPN                 |

| 3     | Entry Lo1    | Second half of TLB entry for odd VPN                  |

| 4     | Context      | Pointer to virtual PTE table of kernel in 32-bit mode |

| 5     | Page master  | Specifies page size                                   |

| 6     | Wired        | Number of wired TLB entries                           |

| 7     | _            | RFU (Reserved for Future Use: reserved)               |

| 8     | BadVAddr     | Displays virtual address where error occurs last      |

| 9     | Count        | Timer count                                           |

| 10    | Entry Hi     | First half of TLB entry (including ASID)              |

| 11    | Compare      | Timer compare value                                   |

| 12    | Status       | Sets operation status                                 |

| 13    | Cause        | Displays cause of exception that occurs last          |

| 14    | EPC          | Exception program counter                             |

| 15    | PRId         | Processor revision ID                                 |

| 16    | Config       | Sets memory system mode                               |

| 17    | LLAddr       | Displays address of LL instruction                    |

| 18    | Watch Lo     | Lower bits of memory reference trap address           |

| 19    | Watch Hi     | Higher bits of memory reference trap address          |

| 20    | X context    | Pointer to virtual PTE table of kernel in 64-bit mode |

| 21–25 | _            | RFU                                                   |

| 26    | Parity error | Parity bit of cache                                   |

| 27    | Cache error  | Cache error and status register                       |

| 28    | Tag Lo       | Cache tag register, low                               |

| 29    | Tag Hi       | Cache tag register, high                              |

| 30    | Error EPC    | Error exception program counter                       |

| 31    | _            | RFU                                                   |

#### 2.4 Data Format

The Vr4200 uses four data formats: double word (64-bit), word (32-bit), half word (16-bit), and byte (8-bit) formats. The byte order can be configured in either big-endian or little-endian order.

Figure 2-5. Byte Address in Word

#### (a) Big endian

|                | 31 24 | 23 16 | 15 8 | 7 0 | Word address |

|----------------|-------|-------|------|-----|--------------|

| Higher address | 8     | 9     | 10   | 11  | 8            |

|                | 4     | 5     | 6    | 7   | 4            |

| Lower address  | 0     | 1     | 2    | 3   | ] o          |

- The highest byte is the lowest address.

- A word is addressed by the address of the highest byte.

# (b) Little endian

|                | 31 | 24 23 | 16 15 | 87 | 0 Word address |

|----------------|----|-------|-------|----|----------------|

| Higher address | 11 | 10    | 9     | 8  | 8              |

|                | 7  | 6     | 5     | 4  | 4              |

| Lower address  | 3  | 2     | 1     | 0  | ] 0            |

- The lowest byte is the lowest address.

- A word is addressed by the address of the lowest byte.

Figure 2-6. Byte Address in Double Word (1/2)

# (a) Big endian

|                | 63 |    |    |    |    |    |    | 0  | Double word address |

|----------------|----|----|----|----|----|----|----|----|---------------------|

| Higher address | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 16                  |

|                | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 8                   |

| Lower address  | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 0                   |

- The highest byte is the lowest address.

- A word is addressed by the address of the lowest byte.

Figure 2-6. Byte Address in Double Word (2/2)

#### (b) Little endian

|                | 63 |    |    |    |    |    |    | 0  | Double word address |

|----------------|----|----|----|----|----|----|----|----|---------------------|

| Higher address | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 16                  |

|                | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 8                   |

| Lower address  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  | 0                   |

- The lowest byte is the lowest address.

- A word is addressed by the address of the lowest byte.

#### 2.5 Cache

# (1) Instruction cache

The features of the instruction cache are as follows:

- · Internal cache memory

- · Capacity: 16K bytes

- · Direct mapping

- · Virtual index address

- · Physical tag check

- · 8-word (32-byte) cache line

# (2) Data cache

The features of the data cache are as follows:

- · Internal cache memory

- · Capacity: 8K bytes

- · Write back

- · Direct mapping

- · Virtual index address

- · Physical tag check

- · 4-word (16-byte) cache line

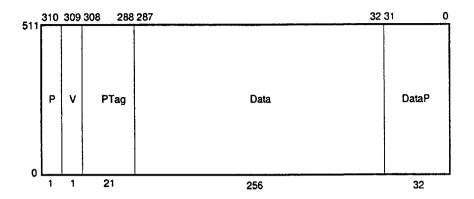

Figure 2-7. Cache Memory Block Diagram

# (a) Instruction cache

DataP: parity bit for data

Data: data (of 1 line)

PTag: physical tag

V: valid bit

P: tag parity

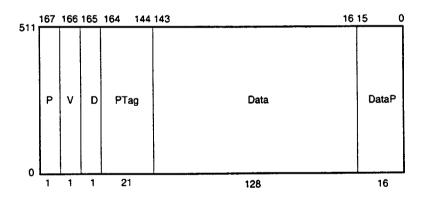

# (b) Data cache

DataP: parity bit for data

Data: data (of 1 line)

PTag: physical tag

D : Dirty bit (shows that it has been written)

V : valid bit

P : tag parity

#### 2.6 Virtual Storage

#### 2.6.1 Virtual address space

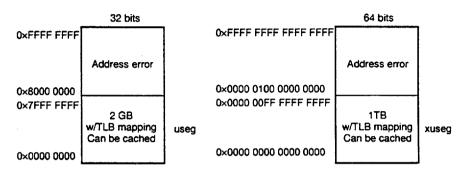

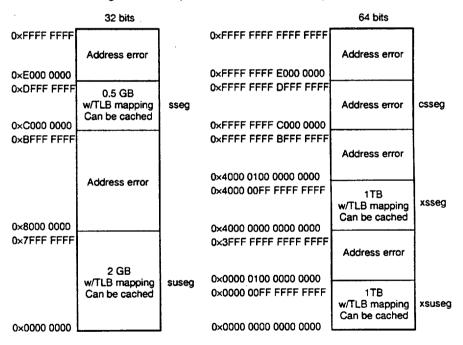

The Vn4200 has two operation modes: 32-bit and 64-bit modes. In addition, it also has three types of operating modes: user mode, supervisor mode, and kernel mode. The following figures show the virtual address space in the respective modes:

Figure 2-8. User Mode Address Space

Figure 2-9. Supervisor Mode Address Space

Figure 2-10. Kernel Mode Address Space

|                            | 32 bits                        |       |                                                | 64 bits                             |        |

|----------------------------|--------------------------------|-------|------------------------------------------------|-------------------------------------|--------|

| 0×FFFF FFFF                |                                |       | 0×FFFF FFFF FFFF FFFF                          | 0.5 GB<br>w/TLB mapping             | ckseg3 |

|                            | 0.5 GB<br>w/TLB mapping        | kseg3 | 0×FFFF FFFF E000 0000                          | Can be cached<br>0.5 GB             | •      |

|                            | Can be cached                  | Kacyo | 0×FFFF FFFF DFFF FFFF 0×FFFF FFFF C000 0000    | w/TLB mapping<br>Can be cached      | cksseg |

| 0×E000 0000                |                                |       | 0×FFFF FFFF BFFF FFFF                          | 0.5 GB<br>w/TLB mapping             | ckseq1 |

| 0×DFFF FFFF                |                                |       | 0×FFFF FFFF A000 0000                          | Can be cached                       | onsegi |

|                            | 0.5 GB<br>w/TLB mapping        |       | 0×FFFF FFFF 9FFF FFFF                          | w/TLB mapping<br>Can be cached Note | ckseg0 |

|                            | Can be cached                  | ksseg | 0xFFFF FFFF 8000 0000<br>0xFFFF FFFF 7FFF FFFF | Out of Guide                        |        |

| 0×C000 0000                |                                |       | 0×C000 00FF 8000 0000                          | Address error                       |        |

| 0×BFFF FFFF                |                                |       | 0xC000 00FF 7FFF FFFF                          | w/TLB mapping                       | .4     |

|                            | 0.5 GB<br>w/o TLB mapping      | kseg1 | 0×C000 0000 0000 0000                          | Can be cached                       | xkseg  |

|                            | Can be cached                  |       | 0xBFFF FFFF FFFF FFFF                          | Address error                       |        |

| 0×A000 0000<br>0×9FFF FFFF |                                |       | 0×9800 0002 0000 0000<br>0×9800 0001 FFFF FFFF |                                     |        |

| UNGITE TITE                | 0.5 GB                         |       |                                                | w/o TLB mapping<br>Can be cached    | xkphys |

|                            | w/o TLB mapping<br>Can be      | kseg0 | 0×9800 0000 0000 0000<br>0×97FF FFFF FFFF FFFF |                                     |        |

|                            | cachedNote                     |       | 0×9000 0002 0000 0000                          | Address error                       |        |

| 0×8000 0000<br>0×7FFF FFFF |                                |       | 0×9000 0001 FFFF FFFF                          | w/o TLB mapping                     | xkphys |

|                            |                                |       | 0×9000 0000 0000 0000                          | Can be cached                       |        |

|                            | 2 GB                           |       | 0x8FFF FFFF FFFF FFFF                          |                                     |        |

|                            | w/TLB mapping<br>Can be cached | kuseg |                                                | Address error                       |        |

|                            |                                |       | 0×4000 0100 0000 0000                          | ,                                   |        |

| 0¥0000 0000                |                                |       | 0×4000 00FF FFFF FFFF                          | 1 TB                                |        |

|                            | L                              | ı     |                                                | w/TLB mapping<br>Can be cached      | xksseg |

|                            |                                |       | 0×4000 0000 0000 0000                          | Oan be caches                       |        |

|                            |                                |       | 0×3FFF FFFF FFFF FFFF                          |                                     |        |

|                            |                                |       |                                                | Address error                       |        |

|                            |                                |       |                                                |                                     |        |

|                            |                                |       | 0x0000 0100 0000 0000<br>0x0000 00FF FFFF FFFF |                                     | !      |

|                            |                                |       |                                                | 1 TB<br>w/TLB mapping               | xkuseg |

|                            |                                |       |                                                | Can be cached                       |        |

|                            |                                |       | 0×0000 0000 0000 0000                          |                                     |        |

★ Note Whether kseg0 and ckseg0 are cache areas is determined by the K0 area of the config register.

Figure 2-11. Details of xkphys Area

| *      |      |      |      |                                              |

|--------|------|------|------|----------------------------------------------|

| 0xBFFF | FFFF | FFFF | FFFF | Address error                                |

| 0xB800 | 0002 | 0000 | 0000 |                                              |

| •      | 0001 |      |      | 8 GB<br>w/o TLB mapping                      |

| 0xB800 |      |      |      | Cache can be used                            |

| 0xB7FF |      |      |      | Address error                                |

| 0xB000 | 0002 | 0000 | 0000 |                                              |

| 0xB000 |      |      |      | 8 GB<br>w/o TLB mapping                      |

| 0xB000 | 0000 | 0000 | 0000 | Cache can be used                            |

| 0xAFFF | FFFF | FFFF | FFFF | Address error                                |

| 0xA800 | 0002 | 0000 | 0000 |                                              |

| 0xA800 | 0001 | FFFF | FFFF | 8 GB<br>w/o TLB mapping                      |

| 0xA800 | 0000 | 0000 | nnnn | Cache can be used                            |

| 0xA300 |      |      |      |                                              |

| 0×A000 | 0002 | 0000 | 0000 | Address error                                |

| 0xA000 |      |      |      | 8 GB                                         |

| UXAUUU | 0001 | rrrr | rrrr | w/o TLB mapping                              |

| 0×A000 | 0000 | 0000 | 0000 | Cache can be used                            |

| 0x9FFF | FFFF | FFFF | FFFF | Address error                                |

| 0x9800 | 0002 | 0000 | 0000 |                                              |

| 0×9800 |      | FFFF | FFFF | 8 GB<br>w/o TLB mapping<br>Cache can be used |

| 0x9800 |      |      | 0000 | Oache can be used                            |

| 0x97FF |      |      |      | Address error                                |

| 0x9000 |      |      | 0000 | 0.00                                         |

| 0x9000 | 0001 | FFFF | FFFF | 8 GB<br>w/o TLB mapping                      |

| 0x9000 |      |      |      | Cannot be cashed                             |

| 0x8FFF |      |      |      | Address error                                |

| 0x8800 |      |      |      |                                              |

| 0x8800 |      |      |      | 8 GB<br>w/o TLB mapping<br>Cache can be used |

| 0x8800 |      |      |      | Cache can be used                            |

| 0x87FF |      |      | FFFF | Address error                                |

| 0x8000 |      |      |      |                                              |

| 0x8000 |      |      |      | 8 GB<br>w/o TLB mapping                      |

| 0x8000 | 0000 | 0000 | 0000 | Cache can be used                            |

#### 2.6.2 Address conversion

Conversion from a virtual address to a physical address is carried out in page units by the internal TLB (Translation Lookaside Buffer). TLB is of full-associative configuration and has 64 entries at the virtual address side and 32 entries at the physical address side. The page size is variable from 4K bytes to 16M bytes.

If a TLB entry is not hit, a TLB unmatch exception occurs in the 32-bit mode, and a XTLB unmatch exception occurs in the 64-bit mode. Exchange the contents of TLB by software.

Figure 2-12. Outline of Address Translation

The following figure illustrates the outline of address conversion.

TLB

Physical address

2

Selector

3

ASID VPN Offset Virtual address

1 A virtual address page number (VPN) is compared with VPN in TLB.

② If the two VPNs coincide, a page frame number (PFN) indicating the higherbits of a physical address is output to the selector.

③ If the lowest bit of VPN is 0, an even page is selected; if the bit is 1, an odd page is selected. The selected page

4 The offset is output to the lower bits of the physical bit not via TLB.

address.

is output to the higher bits of the physical

A TLB entry is read/written by loading/storing the TLB entry indicated by the index register and random register among entry Hi, Entry Lo1, Entry Lo0, and page mask registers.

x x-1

4

The following figure outlines TLB manipulation.

x=12, 14, 16, 18, 20, 22, 24 y=31 (in 32-bit mode)

63 (in 64-bit mode)

Page mask register Entry Hi register Entry Lo1 register Entry Lo0 register

Index register

Random register

Figure 2-13. Outline of TLB Manipulation

#### 2.7 Exception Processing

When an exception is detected, interrupts are disabled, the operating mode is changed to the kernel mode, and execution jumps to a specified exception handler.

If an exception occurs, the EPC register holds a restart address that is used to resume execution. The restart address is the address of the instruction that has caused the exception, or the address of the branch instruction immediately before if the instruction has been executed in the branch delay slot.

Table 2-2. Exceptions

| Exception                   | Vector (32-bit mode)                                     | Cause                                                                                                                     |  |  |  |  |  |

|-----------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Reset                       | ·                                                        | Generates if ColdReset signal has been made active once and then inactive.                                                |  |  |  |  |  |

| Soft Reset                  | 0xBFC0 0000<br>(BEV bit is auto-<br>matically set to 1.) | Generates when Reset signal has been made active once and then inactive.                                                  |  |  |  |  |  |

| NMI                         |                                                          | Generates when NMI signal falls.                                                                                          |  |  |  |  |  |

| TLB Unmatch                 | 0×8000 0000 (BEV±0)<br>0×BFC0 0200 (BEV=1)               | If TLB entry matching address referenced in 32-bit mode is missing.                                                       |  |  |  |  |  |

| XTLB Unmatch                | 0×8000 0080 (BEV=0)<br>0×BFC0 0280 (BEV=1)               | If TLB entry matching address referenced in 64-bit mode is missing.                                                       |  |  |  |  |  |

| Cache Error                 | 0×A000 0100 (BEV=0)<br>0×BFC0 0300 (BEV=1)               | Generates if parity error of system bus and cache is detected.                                                            |  |  |  |  |  |

| TLB Invalid                 |                                                          | If TLB entry matching referenced physical address is invalid.                                                             |  |  |  |  |  |

| TLB Change                  |                                                          | If TLB entry matching physical address referenced by store instruction is valid but cannot be written.                    |  |  |  |  |  |

| Address Error               |                                                          | If word not positioned is accessed, or if virtual address that cannot be used in user and supervisor modes is referenced. |  |  |  |  |  |

| Bus Error                   |                                                          | If error is indicated by data identifier.                                                                                 |  |  |  |  |  |

| Integer Overflow            |                                                          | Generates if 2's complement overflow occurs as result of executing addition or subtraction.                               |  |  |  |  |  |

| Trap                        |                                                          | If condition becomes true when trap instruction is executed.                                                              |  |  |  |  |  |

| System Call                 | 0×8000 0180 (BEV=0)                                      | Generates when SYSCALL instruction is executed.                                                                           |  |  |  |  |  |

| Break Point                 | 0×BFC0 0380 (BEV=1)                                      | Generates when BREAK instruction is executed.                                                                             |  |  |  |  |  |

| Reserved Instruction        |                                                          | If attempt is made to execute undefined instruction.                                                                      |  |  |  |  |  |

| Coprocessor Cannot be Used  |                                                          | If use of corresponding coprocessor unit is not enabled when coprocessor instruction is executed.                         |  |  |  |  |  |

| Floating-point<br>Operation |                                                          | If error occurs when FPU instruction is executed.                                                                         |  |  |  |  |  |

| Watch                       |                                                          | If attempt is made to reference physical address in watch Lo/watch Hi register by load/store instruction.                 |  |  |  |  |  |

| Interrupt                   |                                                          | If one of eight interrupt sources becomes active. Can be classified into three types: external, software, and timer.      |  |  |  |  |  |

**Remark** The higher 32 bits of the exception vector are all 1 in the 64-bit mode, and the lower 32 bits are the same as the vector address in the 32-bit mode.

#### 3. FPU INTERNAL ARCHITECTURE

Unlike the Vn4000 and Vn4400™, The FPU (floating-point operation unit) of the Vn4200 is integrated to the CPU (integer operation unit). The CPU and FPU use the same data bus, and the FPU instructions are executed by the hardware of the CPU.

Vn4200 logically handles the FPU as an independent coprocessor and can execute all the floating-point instructions defined by MIPS ISA.

#### 3.1 FPU Registers

#### (1) Floating-point general registers (FGRs)

These registers are physical general registers and can be directly accessed. There are 32 general registers. The bit length of these registers varies depending on the content of the FR bit of the status register.

# (2) Floating-point registers (FPRs)

These 64-bit logical registers hold a floating-point value when a floating-point operation is executed. The number of FPRs varies depending on the contents of the FR bit of the status register.

#### (3) Floating-point control registers (FCRs)

There are the following two FCRs:

#### (a) Control/status register (FCR31)

This register controls and monitors exceptions, holds the result of a comparison operation, and sets a rounding mode.

# (b) Processor/revision register (FCR0)

This register holds the revision information of the FPU.

Figure 3-1. FPU Registers

# (a) FGR and FPR

| (i)                | When FR      | bit = 0                               | (ii) V                  | Vhen FR bit = 1                           | ′    |

|--------------------|--------------|---------------------------------------|-------------------------|-------------------------------------------|------|

| Floating-point reg | gister (FPR) | Floating-point general register (FGR) | Floating-point register | (FPR) Floating-point general register (FG | R)   |

|                    | 31           | 0                                     | _                       | 63                                        | 0    |

| FPR0 {             | (low)        | FGR0                                  | FPR0                    | FGR0                                      |      |

| FFRU }             | (high)       | FGR1                                  | FPR1                    | FGR1                                      |      |

|                    | (iow)        | FGR2                                  | PFR2                    | PGR2                                      |      |

| FPR2 {             | (high)       | FGR3                                  |                         | •                                         |      |

| . `                |              |                                       | ] .                     |                                           |      |

| •                  |              | •                                     | FPR29                   | FGR29                                     |      |

|                    | (low)        | FGR28                                 | FPR30                   | FGR30                                     |      |

| FPR28              | (high)       | FGR29                                 | PFR31                   | PGR31                                     |      |

| 50000              | (low)        | FGR30                                 | ]                       |                                           |      |

| FPR30              | (high)       | FGR31                                 |                         |                                           |      |

|                    |              |                                       |                         |                                           |      |

|                    |              |                                       | (b) FCR                 |                                           |      |

| (i) Co             | ntrol/stat   | us register (FCR31)                   | (ii) Processo           | or/revision register (F                   | CR0) |

|                    | 31           | 0                                     | 31                      | 0                                         |      |

# 3.2 Data Format

- (1) Floating-point format

FPU supports 32-bit (single-precision) and 64-bit (double-precision) IEEE754 floating-point operations.

- (2) Fixed-point format

The value of a fixed point is computed in the format of 2's complement.

#### 4. INTERFACE

#### 4.1 System Interface

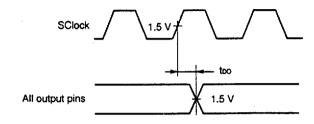

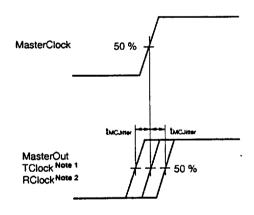

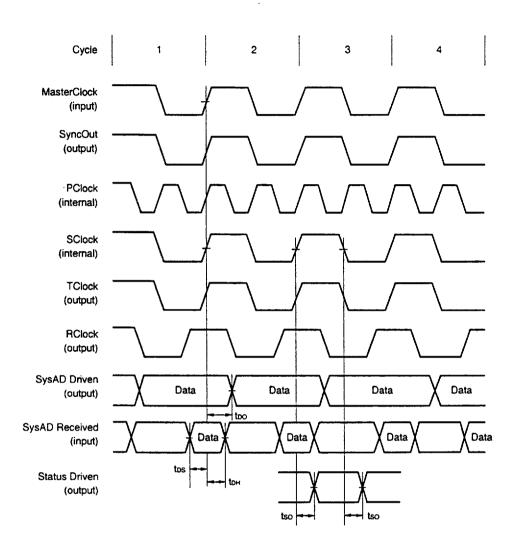

The input/output timing of the processor is as follows:

- The processor output starts changing at the rising edge of SClock.

- · The processor input is latched at the rising edge of SClock.

The following two buses are used for system interfacing:

- · SysAD (63: 0) : This bus transfers addresses and data.

- SysCmd (8: 0) : This bus transfers commands and data identifiers.

The SysAD and SysCmd buses are bidirectional buses and are driven by the processor or external agent.

These buses enter the following two states depending on the direction in which they are driven:

- Master state : The buses are driven by the processor to issue a processor request.

- Slave state : The buses are driven by the external agent to issue an external request.

The following two cycles are used depending on the information included in the SysAD bus:

- · Address cycle : The valid address is included in the SysAD bus.

- Data cycle : The valid data is included in the SysAD bus.

Here are brief descriptions of the interface control signals:

- ValidOut : This signal is asserted by the processor when the SysAD and SysCmd buses are valid in the master

- ValidIn : This signal is asserted by the external agent when the SysAD and SysCmd buses are valid in the slave state.

- ExtRqst : This signal is asserted by the external agent when the external agent issues an external request.

- Release : This signal is used by the processor to place the system interface in the slave state.

- RdRdy

This signal is used by the external agent to inform that it is ready to accept a processor read request.

WrRdy

This signal is used by the external agent to inform that it is ready to accept a processor write request.

#### 4.1.1 System interface request

The system interface supports the following requests:

| Request                 | Outline                             | Data Unit              |  |  |

|-------------------------|-------------------------------------|------------------------|--|--|

| Processor Read Request  | Read request to main memory or I/O  | 4.71.4.0446            |  |  |

| Processor Write Request | Write request to main memory or I/O | 1-7 bytes, 2/4/8 words |  |  |

| External null Request   | Request to release system interface | -                      |  |  |

| External Write Request  | Interrupt request from system bus   | 1 word                 |  |  |

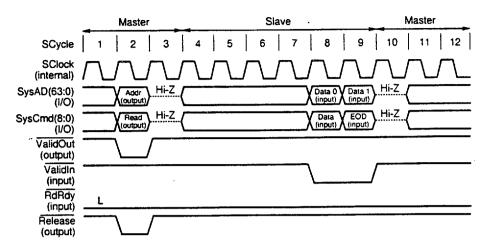

As an example of the protocol of the system interface request, Figure 4-1 shows the timing of the processor read request and read response.

Figure 4-1. Timing of Processor Read Request and Read Response (block transfer)

#### 4.1.2 Data transfer rate control

The system interface supports a data transfer rate of double words per 1 SCycle maximum.

# (1) To transfer data from external agent to processor

The external agent can transfer data at any transfer rate. The data is accepted only in a cycle in which ValidIn is asserted.

# (2) To transfer data from processor to external agent

The transfer rate is selected by the DataRate pin at reset from DDx and Dxx (D: data cycle, x: vacant cycle).

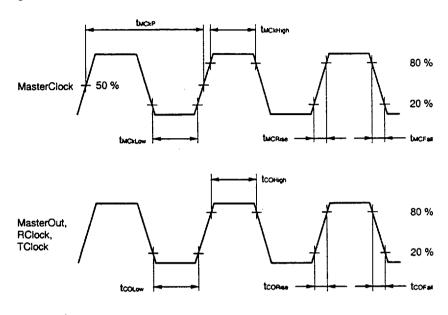

#### 4.1.3 Clock interface

The input clock of the Vn4200 is called MasterClock. This clock is internally multiplied to generate PClock based on which the pipeline operation is performed.

The system bus operates based on SClock. However, SClock is externally output. Instead, the CPU supplies the external agent with RClock as the reference input clock and TClock as the reference output clock. The operating frequencies of SClock, RClock, and TClock are usually half that of PClock, and the same as that of MasterClock.

# 4.1.4 Setting division ratio of system interface

The division ratio of the system interface is set from the Div4 pin at reset<sup>Note</sup>. The pipeline operating frequency can be divided by two or four.

Where the external clock is 40 MHz, the pipeline operates at 80 MHz; therefore, the operating frequency of the system bus is 40 MHz or 20 MHz.

Note Setting by this pin is not supported by the current Vn4200.

#### 5. INTERNAL/EXTERNAL CONTROL FUNCTION

#### 5.1 Reset Function

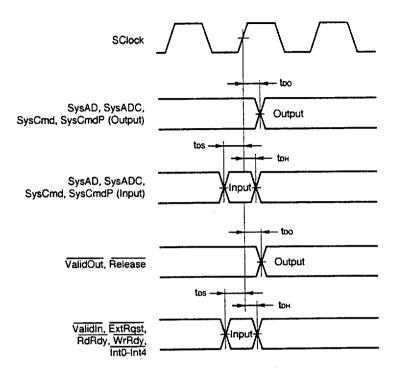

Reset can be effected in three ways: power-ON reset, cold reset, and soft reset.

Cold reset and soft reset is effected with the power turned ON.

The internal status is initialized at reset. When soft reset is effected, however, only the contents of the system interface and cache memory become undefined, and the other internal status is not initialized but the status before reset is retained.

#### (1) Power-ON reset and cold reset

Power-ON reset or cold reset is effected when both the ColdReset and Reset signals are made active. During reset, data is input from the initial setting pin to set the internal initial status of the processor. Table 5-1 shows the set contents of each pin.

Table 5-1. Setting of Initial Status

| Pin Name  | Set Contents                                                        |  |  |  |  |  |

|-----------|---------------------------------------------------------------------|--|--|--|--|--|

| BigEndian | Byte order 0: little endian 1: big endian                           |  |  |  |  |  |

| DataRate  | Data transfer rate of external device 0: DDx pattern 1: Dxx pattern |  |  |  |  |  |

| Div4 Note | Operating speed of system interface (vs. PClock) 0: 1/4 1: 1/2      |  |  |  |  |  |

Note Setting of this pin is not supported by the current Vn4200. Set this pin to 1.

# (2) Soft reset

Soft reset is executed by making the Reset signal active. This reset does not input the initial status from the initial setting pin, but the status before reset is retained.

# 5.2 Interrupt Function

#### (1) Maskable interrupt

This interrupt is subject to mask control. Mask processing is performed by the status register (whether each interrupt is processed or interrupts are processed all at once can be specified). No priority is assigned to each interrupt.

# (a) Hardware interrupts (5 sources)

These interrupts are accepted when an external write request is issued or when the Int(4:0) signal is asserted.

#### (b) Software interrupt (2 sources)

These interrupts are accepted when the IPO and IP1 bits of the cause register are set to 1.

#### (c) Timer interrupt (1 source)

This interrupt is accepted when the value of the count register becomes equal to the value of the compare register and when the IP7 bit of the cause register is set to 1.

#### (2) Non-maskable interrupt (1 source)

This interrupt cannot be masked. It is accepted when the external write request is issued or when the NMI signal is asserted.

## 5.3 JTAG Boundary Scan Function

Mutual connection of each device on the board can be tested by the boundary interface that uses the JTAG protocol (the Va4200 itself cannot be tested).

A TAP controller, JTAG instruction register, JTAG boundary scan register, and JTAG bypass register are incorporated according to the specifications of JTAG (however, JTAG of the Va4200 only has the external test function of the JTAG boundary scan register).

# 5.4 Low Power Dissipation Design

The VR4200 has made the following improvements to reduce the power dissipation, as compared with the VR4000 and VR4400:

- · Power management of cache in bank units

- · Cache prefetch (Two instructions are simultaneously fetched.)

- 3.3-V operation

- Employment of write back cache (to reduce the number of times the system bus is accessed)

- · Integrating integer operation unit and floating-point operation unit

- · Employment of simple 5-stage pipeline

- · Power management by modular execution unit

These features make it possible that the VR4200 operates on 1.5 W (TYP.).

Moreover, a low power mode in which the power dissipation can be dynamically reduced during operation can also be used (refer to **5.5 Low Power Mode**).

#### 5.5 Low Power Mode

The Vn4200 is set in the low power mode when the bit 27 (RP bit) of the status register is set to 1.

Normally, the processor operates with the frequency of the CPU internal clock (PClock) two times higher than that of MasterClock and the frequency of the system bus clock (SClock, TClock, RClock) the same as that of MasterClock.

In the low power mode, however, the frequencies of PClock and the clock of the system bus are reduced to the 1/4 of those in the normal operation mode. This means that the frequency of PClock is reduced to the 1/2 of that of MasterClock and that the frequency of the clock of the system bus is reduced to the 1/4 of that of MasterClock.

This mode can therefore reduce the power dissipation of the CPU to about the 1/4 of that in the normal operation mode.

#### 5.6 Hardware Debug Support Function

The Vn4200 has a function to output which instruction is currently executed by the pipeline to Status (3:0).

Moreover, it can also output a branch destination physical address from SysAD (63:0) if the instruction address is changed as a result of execution of a branch or jump instruction or generation of an exception.

These functions can be used when the bit 24 (ITS bit: instruction trace) of the status register is set to 1.

#### 5.6.1 Output of internal processor status

Status (3:0) outputs the current operation status of the pipeline and the category of the instruction executed in the WB stage.

Status (3:0) is output in synchronization with the rising edge of PClock.

#### 5.6.2 Output of branch destination address

This function forcibly generates an instruction cache miss in the following cases:

- · If the branch condition is satisfied when a branch instruction is executed

- If the contents of PC are changed as a result of executing a jump instruction or generation of an exception.

If an instruction cache miss occurs, SysAD (63:0) issues a processor block read request, which allows the external agent to know changes in addresses.

In response to the processor block read request, return response data in the same manner as to the normal request. The output address is not the value of the PC (virtual address), but a physical address.

# 6. INSTRUCTION SET

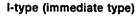

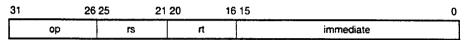

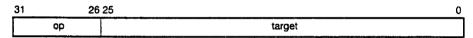

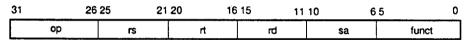

An instruction of the Va4200 consists of 1 word (32 bits) located at the word boundary. There are the three types of instruction formats, as shown in Figure 6-1. By using only three instruction formats, decoding an instruction is simplified. Operations and addressing modes that are complicated and are not used so frequently are realized by the compiler.

#### 6.1 Instruction Format

Figure 6-1. Instruction Format

#### J-type (jump type)

## R-type (register type)

| ор        | 6-bit op code                                                  |

|-----------|----------------------------------------------------------------|

| rs        | 5-bit source register specifier                                |

| rt        | 5-bit target (source/destination) register or branch condition |

| immediate | 16-bit immediate, branch displacement, or address displacement |

| target    | 26-bit unconditional branch target address                     |

| rd        | 5-bit destination register specifier                           |

| sa        | 5-bit shift amount                                             |

| funct     | 6-bit function field                                           |

#### 6.2 CPU Instruction Set

The CPU instructions of the Va4200 can be classified into an instruction set that is common to all the Va series processors (ISA: Instruction Set Architecture), the instruction set that is executed by the Va4000 series (extended ISA), and a system control coprocessor instruction set. The list of each instruction set is shown on the following pages.

Table 6-1. CPU Instruction Set: ISA (1/3)

| Instruction    | Desc                            | ription    |    |    |     |        | Fo     | rmat          |          |

|----------------|---------------------------------|------------|----|----|-----|--------|--------|---------------|----------|

| Load/store in  | structions                      | op base rt |    |    |     | offset |        |               | ]        |

| LB             | Load Byte                       | 7          |    |    |     | LB     |        | rt, offset (b | ase)     |

| LBU            | Load Byte Unsigned              |            |    |    |     | LBU    |        | rt, offset (b | ase)     |

| LH             | Load Halfword                   |            |    |    |     | LH     |        | rt, offset (b | ase)     |

| LHU            | Load Halfword Unsigned          |            |    |    | 1   | LHU    |        | rt, offset (b | ase)     |

| LW             | Load Word                       |            |    |    |     | LW     |        | rt, offset (b | ase)     |

| LWL            | Load Word Left                  |            |    |    |     | LWL    |        | rt, offset (b | ase)     |

| LWR            | Load Word Right                 | •          |    |    |     | LWR    |        | rt, offset (b | ase)     |

| SB             | Store Byte                      |            |    |    |     | SB     |        | rt, offset (b | ase)     |

| SH             | Store Halfword                  |            |    |    |     | SH     |        | rt, offset (b | ase)     |

| sw             | Store Word                      |            |    |    |     | sw     |        | rt, offset (b | ase)     |

| SWL            | Store Word Left                 |            |    |    | - 1 | SWL    |        | rt, offset (b | ase)     |

| SWR            | Store Word Right                |            |    |    |     | SWR    |        | rt, offset (b | ase)     |

|                | 1                               |            |    |    |     |        |        |               |          |

| ALU immedia    | ate instructions                | op         | rs | rt |     |        | offset |               |          |

| ADDI           | Add Immediate                   |            |    |    |     | ADDI   |        | rt, rs, imme  | ediate   |

| ADDIU          | Add Immediate Unsigned          |            |    |    | -   | ADDIU  |        | rt, rs, imme  | ediate   |

| SLTI           | Set On Less Than Immediate      |            |    |    |     | SLTI   |        | rt, rs, imme  | ediate   |

| SLTIU          | Set On Less Than Immediate Ur   | nsigned    |    |    | 1   | SLTIU  |        | rt, rs, imme  | ediate   |

| ANDI           | And Immediate                   | •          |    |    |     | ANDI   |        | rt, rs, imme  | ediate   |

| ORI            | Or Immediate                    |            |    |    | İ   | ORI    |        | rt, rs, imme  | ediate   |

| XORI           | Exclusive Or Immediate          |            |    |    | İ   | XORI   |        | rt, rs, imme  | ediate   |

| LUI            | Load Upper Immediate            |            |    |    |     | LUI    |        | rt, immedia   | ite      |

| 3-operand ty   | pe instructions                 | ор         | rs | rt |     | rd     | sa     | funct         | ]        |

| ADD            | Add                             |            |    |    |     | ADD    | 2      | rd, rs, rt    |          |

| ADDU           | Add Unsigned                    |            |    |    |     | ADDU   |        | rd, rs, rt    |          |

| SUB            | Subtract                        |            |    |    |     | SUB    |        | rd, rs, rt    |          |

| SUBU           | Subtract Unsigned               |            |    |    |     | SUBU   |        | rd, rs, rt    |          |

| SLT            | Set On Less Than                |            |    |    |     | SLT    |        | rd, rs, rt    |          |

| SLTU           | Set On Less Than Unsigned       |            |    |    |     | SLTU   |        | rd, rs, rt    |          |

| AND            | And                             |            |    |    |     | AND    |        | rd, rs, rt    |          |

| OR             | Or                              |            |    |    |     | OR     |        | rd, rs, rt    |          |

| XOR            | Exclusive Or                    |            |    |    |     | XOR    |        | rd, rs, rt    |          |

| NOR            | Nor                             |            |    |    |     | NOR    |        | rd, rs, rt    |          |

|                |                                 |            | T  | 1  | T   |        |        | 1             |          |

| Shift instruct | ions                            | ор         | rs | rt | Ш   | rd     | sa     | funct         | <u> </u> |

| SLL            | Shift Left Logical              | -          |    |    |     | SLL    |        | rd, rt, sa    |          |

| SRL            | Shift Right Logical             |            |    |    |     | SRL    |        | rd, rt, sa    |          |

| SRA            | Shift Right Arithmetic          |            |    |    |     | SRA    |        | rd, rt, sa    |          |

| SLLV           | Shift Left Logical Variable     |            |    |    |     | SLLV   |        | rd, rt, sa    |          |

| SRLV           | Shfit Right Logical Variable    |            |    |    |     | SRLV   |        | rd, rt, rs    |          |

| SRAV           | Shfit Right Arithmetic Variable |            |    |    |     | SRAV   |        | rd, rt, rs    |          |

Table 6-1. CPU Instruction Set: ISA (2/3)

| Instruction     | Descr                         | ription    |          |             |                    | Forr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | nat            | -    |

|-----------------|-------------------------------|------------|----------|-------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|

| Multiply/divide | e instructions                | ор         | rs       | rt          | rd                 | sa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | funct          |      |

| MULT            | Multiply                      |            |          |             | MULT rs, rt        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |      |

| MULTU           | Multiply Unsigned             |            |          |             | MULTU              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | rs, rt         |      |