## **GENERAL DESCRIPTION**

The EM65240 is a 240-channel LCD driver LSI used to drive large scale dot matrix LCD panels, like PDA, personal computers and workstations. Which is made by power CMOS high voltage process technology. Through the use of TCP technology, it is deal for substantially decreasing the size of LCD module frame. This product can function as a common and a segment driver, which is used for liquid crystal dot matrix display.

In common driver mode, it can be selected in single mode and dual mode by a mode pin (MD), data input/output pins are bi-directional, four data shift direction are pin selectable. In segment driver mode, it can be selected 4-bit parallel input mode or 8-bit parallel input mode by a mode pin (MD).

## FEATURES

## Both common mode and segment mode

- Display duty application: up to 1/480 duty

- Supply voltage for the logic system: +2.5 to +5.5V

- Supply voltage for LCD driver: +15 to +42V

- Number of LCD driver outputs: 240

- Low output impedance

- Low power consumption

- CMOS silicon process (P-type Silicon substrate)

- 268 pin TCP (tape carrier package) package: EM65240U

## Common mode

- Shift clock frequency: 4.0MHz (Max.) (V<sub>DD</sub>=+2.5 to +5.5)

- Built-in 240 bits bi-directional shift register (divisible into 120bits\*2)

- Available in a single mode or in a dual mode

- Data input/output pins are bi-directional, four data shift direction are pin selectable.

- Shift register circuit reset function when /DSPOF active

## Preliminary

## Segment mode

- Shift clock frequency: 20MHz(Max.) (V<sub>DD</sub>=+ 5V±10%)

15MHz(Max.) (V<sub>DD</sub>=+ 3.5V to + 4.5V)

- 12MHz(Max.) (V<sub>DD</sub>=+ 2.5V to + 3.0V)

- Adopts a data bus system

- 4-bits/8-bits parallel input mode are selected by MD pin

- Automatic transfer function of an enable signal

- Automatic counting function which, in the chip select, causes the internal clock to be stopped by automatically counting 240 of input data

- Line latch circuit reset function when /DSPOF active

## **PIN CONFIGURATION**

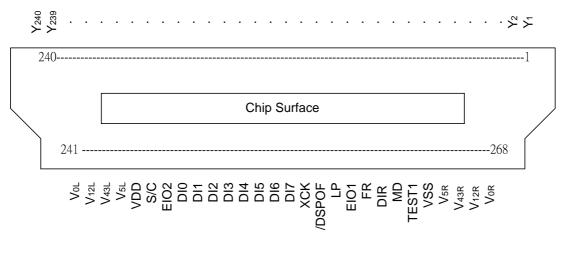

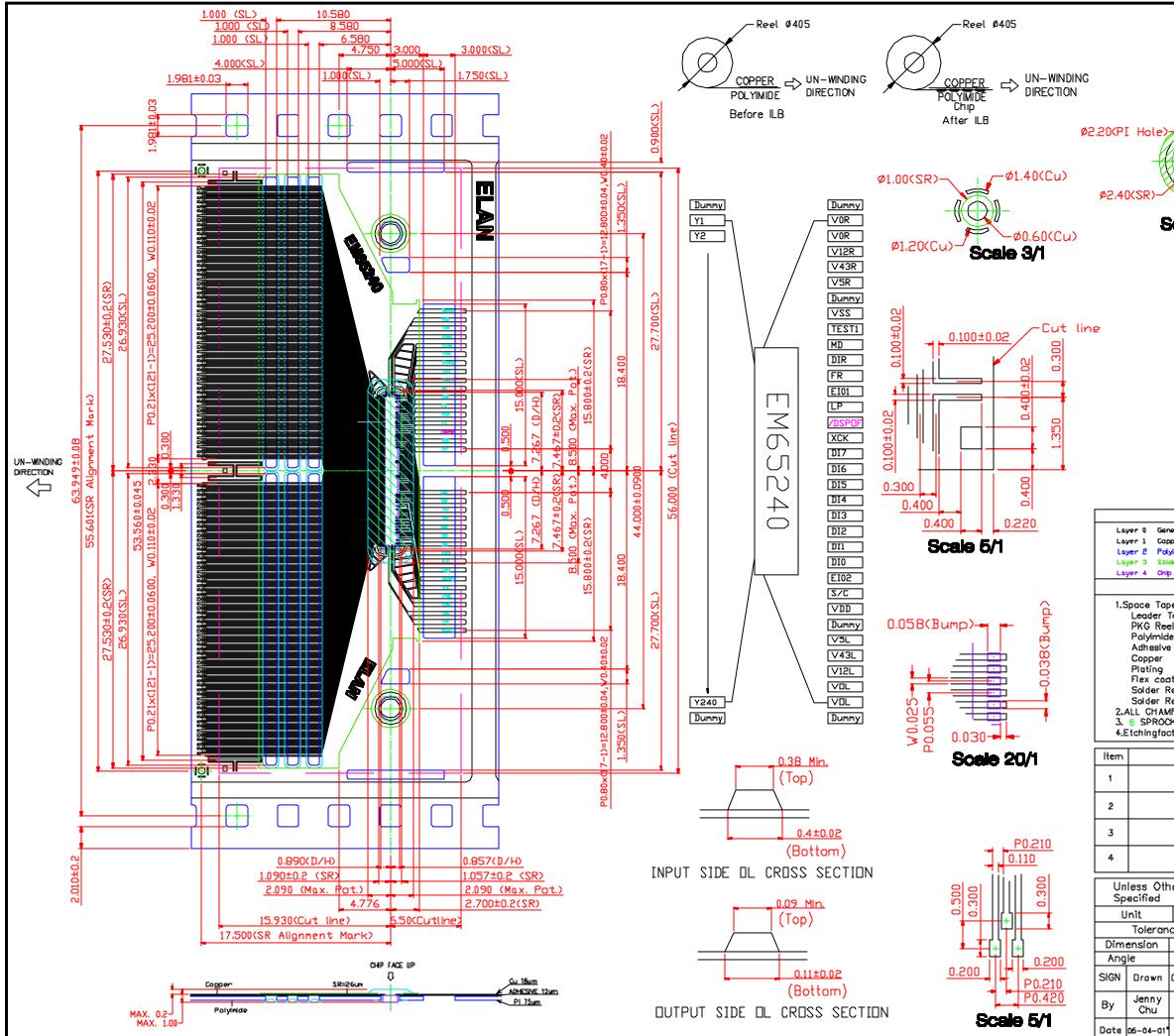

Figure1 pin configuration

# Preliminary

## Table 1 pin designation

| Pin NO.    | Symbol                             | I/O | Description                                    |

|------------|------------------------------------|-----|------------------------------------------------|

|            |                                    |     |                                                |

| 1 to240    | $Y_1 - Y_{240}$                    | 0   | LCD driver output                              |

| 241,268    | V <sub>OL</sub> ,V <sub>OR</sub>   | -   | Power supply for LCD driver                    |

| 242,267    | V <sub>12L</sub> ,V <sub>12R</sub> | -   | Power supply for LCD driver                    |

| 243,266    | V <sub>43L</sub> ,V <sub>43R</sub> | -   | Power supply for LCD driver                    |

| 244,265    | $V_{5L}, V_{5R}$                   | -   | Power supply for LCD driver                    |

| 245        | V <sub>DD</sub>                    | -   | Power supply for logic system                  |

| 246        | S/C                                | I   | Segment/common mode selection                  |

| 247        | EIO <sub>2</sub>                   | I/O | Input /output for chip select or data of shift |

| 259        | EIO <sub>1</sub>                   |     | register                                       |

| 248 to 254 | $DI_0 - DI_6$                      | I   | Display data input for segment mode            |

| 255        | DI <sub>7</sub>                    |     | Dual mode data input for common mode           |

| 256        | XCK                                | I   | Display data shift clock input for segment     |

|            |                                    |     | mode                                           |

| 257        | /DSPOF                             |     | Control input for non-select output level      |

| 258        | LP                                 | I   | Latch pulse input/shift clock input for shift  |

|            |                                    |     | register                                       |

| 260        | FR                                 | I   | AC-converting signal input for LCD driver      |

|            |                                    |     | waveform                                       |

| 261        | DIR                                | I   | Display data shift direction selection         |

| 262        | MD                                 | I   | Mode selection input                           |

| 263        | TEST <sub>1</sub>                  | I   | Test mode selection input                      |

| 264        | V <sub>SS</sub>                    | -   | Ground (0 V)                                   |

## **PIN DESCRIPTIONS**

## Segment mode

Table2 pin description of segment mode

| Symbol                                                                                                                                                                                           | I/O | Connected to | Functions                                                                                                                                                                                                                                                                              |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| V <sub>DD</sub>                                                                                                                                                                                  | Ι   | Power Supply | Power supply for internal logic connects to +2.5 to +5.5V                                                                                                                                                                                                                              |  |  |

| V <sub>SS</sub>                                                                                                                                                                                  | I   | GND          | Connect to Ground                                                                                                                                                                                                                                                                      |  |  |

| V <sub>0R</sub> <sup>,</sup> V <sub>0L</sub><br>V <sub>12R</sub> <sup>,</sup> V <sub>12L</sub><br>V <sub>34R</sub> <sup>,</sup> V <sub>34L</sub><br>V <sub>5R</sub> <sup>,</sup> V <sub>5L</sub> | Ι   | Power Supply | Power supply for LCD driver level<br>• Normally , the bias voltage used is set<br>resistor divider<br>• Ensure that the voltage are set such th<br>$V_{SS} \leq V_5 < V_{34} < V_{12} < V_0$<br>• To further reduce the difference betwee<br>the output waveforms of LCD driver output |  |  |

|                                                                                                                                                                                                  |     |              | pin $Y_1$ and $Y_{240}$ , externally connect $V_{iR}$ and $V_{iL}$ (i=0 , 12 , 34 , 5)                                                                                                                                                                                                 |  |  |

| DI <sub>0</sub> – DI <sub>7</sub>                                                                                                                                                                | I   | Controller   | Input for display data<br>• In 4-bit parallel input mode · input data<br>into 4 pins DI <sub>0</sub> – DI <sub>3</sub><br>• In 8-bit parallel input mode · input data<br>into8 pins DI <sub>0</sub> – DI <sub>7</sub>                                                                  |  |  |

| XCK                                                                                                                                                                                              | Ι   | Controller   | Clock signal for taking display data<br>Data is read on the falling of the clock<br>pulse                                                                                                                                                                                              |  |  |

| LP                                                                                                                                                                                               | Ι   | Controller   | Latch signal for display data <ul> <li>Data is latched on the falling edge of the clock pulse</li> </ul>                                                                                                                                                                               |  |  |

| S/C                                                                                                                                                                                              | Ι   | Controller   | Selection of segment mode/common modeS/CMode selectionHsegment modeLcommon mode                                                                                                                                                                                                        |  |  |

# Preliminary

## Segment mode (continuous)

| DIR    | I | Controller | Directional selection for reading display data            |  |  |  |

|--------|---|------------|-----------------------------------------------------------|--|--|--|

|        |   |            | DIR Data read direction                                   |  |  |  |

|        |   |            | L Y <sub>240</sub> to Y <sub>1</sub>                      |  |  |  |

|        |   |            | H Y <sub>1</sub> to Y <sub>240</sub>                      |  |  |  |

|        |   |            |                                                           |  |  |  |

| /DSPOF | I | Controller | Control signal for output deselect level                  |  |  |  |

|        |   |            | • The input signal is level-shifted from logic            |  |  |  |

|        |   |            | voltage level to LCD driver voltage level ,               |  |  |  |

|        |   |            | and controls LCD drive circuit                            |  |  |  |

|        |   |            | • When the signal is low $,$ the output (Y <sub>1</sub> – |  |  |  |

|        |   |            | $Y_{240}$ ) of LCD drive be set to level $V_5$ , the      |  |  |  |

|        |   |            | contents of line latch are reset, but read the            |  |  |  |

|        |   |            | display data in the data latch regardless of              |  |  |  |

|        |   |            | condition of /DSPOF                                       |  |  |  |

|        |   |            | <ul> <li>When this signal return to high, the</li> </ul>  |  |  |  |

|        |   |            | operation returns to the normal status.                   |  |  |  |

| FR     | I | Controller | AC signal for LCD driver                                  |  |  |  |

|        |   |            | <ul> <li>Input a frame inversion signal</li> </ul>        |  |  |  |

|        |   |            | The LCD driver output voltage level can                   |  |  |  |

|        |   |            | be set by line latch output signal and FR                 |  |  |  |

|        |   |            | signal                                                    |  |  |  |

| MD     | I | Controller | Mode selection                                            |  |  |  |

|        |   |            | MD Mode selection                                         |  |  |  |

|        |   |            | H 4-bit parallel input                                    |  |  |  |

|        |   |            | L 8-bit parallel input                                    |  |  |  |

|        |   |            |                                                           |  |  |  |

# Preliminary

## Segment mode (continuous)

| EIO <sub>1</sub> , EIO <sub>2</sub>                   | 1/0 | Controller | Input/output for chip selection<br>• In output state , after 240-bit of data have<br>been read , set to "L" then set to "H"<br>• In input state , the chip is selected when<br>EI is set to "L", then 240-bit of data have<br>been read, the ship is deselected<br><u>DIR EIO<sub>1</sub> EIO<sub>2</sub><br/>H input output<br/>L output input</u> |  |  |  |  |

|-------------------------------------------------------|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Y <sub>1</sub> -Y <sub>240</sub><br>TEST <sub>1</sub> | 0   |            | LCD driver output.<br>• One of four levels is output according to<br>the combination of the FR signal and<br>display data<br>Test mode selection<br>• during normal operation , connect to V <sub>ss</sub>                                                                                                                                          |  |  |  |  |

# Preliminary

## Common mode

Table3 pin description of common mode

| Symbol             | I/O  | Connected to | Functions                                                             |  |  |  |

|--------------------|------|--------------|-----------------------------------------------------------------------|--|--|--|

| 0,11001            | ., 🗸 |              |                                                                       |  |  |  |

|                    |      |              |                                                                       |  |  |  |

| V <sub>DD</sub>    | I    | Power supply | Power supply for internal logic connects to                           |  |  |  |

|                    |      |              | +2.5 to +5.5V                                                         |  |  |  |

| V <sub>SS</sub>    |      | GND          | Connect to Ground                                                     |  |  |  |

| $V_{0R}, V_{0L}$   | I    | Power supply | Power supply for LCD driver level                                     |  |  |  |

| $V_{12R}, V_{12L}$ |      |              | <ul> <li>Normally</li> <li>the bias voltage used is set by</li> </ul> |  |  |  |

| $V_{34R}, V_{34L}$ |      |              | resistor divider                                                      |  |  |  |

| $V_{5R}, V_{5L}$   |      |              | <ul> <li>Ensure that the voltage are set such that</li> </ul>         |  |  |  |

|                    |      |              | $V_{SS} \leq V_5 < V_{34} < V_{12} < V_0$                             |  |  |  |

|                    |      |              | • To further reduce the difference between                            |  |  |  |

|                    |      |              | the output waveforms of LCD driver output                             |  |  |  |

|                    |      |              | pin $Y_1$ and $Y_{240}$ , externally connect $V_{iR}$ and             |  |  |  |

|                    |      |              | V <sub>iL</sub> (i=0 , 12 , 34 , 5)                                   |  |  |  |

| $EIO_1$ , $EIO_2$  | I/O  |              | Data input/output shift for bi-directional shift                      |  |  |  |

|                    |      |              | register                                                              |  |  |  |

|                    |      |              | • When EIO1(EIO <sub>2</sub> ) is input , it will be                  |  |  |  |

|                    |      |              | pull-down                                                             |  |  |  |

|                    |      |              | • When EIO1(EIO <sub>2</sub> ) is output <sup>,</sup> it will not be  |  |  |  |

|                    |      |              | pull- <u>down</u>                                                     |  |  |  |

|                    |      |              | DIR EIO <sub>1</sub> EIO <sub>2</sub>                                 |  |  |  |

|                    |      |              | H input output                                                        |  |  |  |

|                    |      |              | L output input                                                        |  |  |  |

|                    |      |              |                                                                       |  |  |  |

|                    |      |              |                                                                       |  |  |  |

|                    |      |              |                                                                       |  |  |  |

| LP                 | -    | Controller   | Shift clock for bi-directional shift register                         |  |  |  |

|                    | 1    | CONTOLLE     | Data is shifted on the falling edge of the                            |  |  |  |

|                    |      |              | clock                                                                 |  |  |  |

| DIR                |      | Controller   | Directional selection of bi-directional shift                         |  |  |  |

|                    | 1    |              | register                                                              |  |  |  |

|                    |      |              | DIR Data read direction                                               |  |  |  |

|                    |      |              | $L$ $Y_{240}$ to $Y_1$                                                |  |  |  |

|                    |      |              | H Y <sub>1</sub> to Y <sub>240</sub>                                  |  |  |  |

|                    |      |              | · · · · · · · · · · · · · · · · · · ·                                 |  |  |  |

## Common mode (continuous)

| /DSPOF                           | I | Controller              | Control signal for output deselect level<br>• The input signal is level-shifted from logic<br>voltage level to LCD driver voltage level ,<br>and controls LCD drive circuit<br>• When the signal is low , the output $(Y_1 - Y_{240})$ of LCD drive be set to level $V_5$ , the<br>contents of shift register are reset not read<br>• When this signal return to high, the<br>operation returns to the normal status. |  |  |  |

|----------------------------------|---|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| FR                               | Ι | Controller              | <ul> <li>AC signal for LCD drive</li> <li>Input a frame inversion signal</li> <li>The LCD driver output voltage level can<br/>be set by shift register output signal and FR<br/>signal</li> </ul>                                                                                                                                                                                                                     |  |  |  |

| MD                               | I | Controller              | Mode selectionMDMode selectionHDual modeLSingle mode                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| S/C                              | I | Controller              | Selection of segment mode/common modeS/CMode selectionHsegment modeLcommon mode                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| DI <sub>7</sub>                  | I | Controller              | Dual mode data input <ul> <li>In dual mode</li> <li>data can input from 121<sup>st</sup></li> </ul> bit                                                                                                                                                                                                                                                                                                               |  |  |  |

| DI <sub>0</sub> -DI <sub>6</sub> | Ι | $V_{SS}$ or $V_{DD}$    | Not used                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| XCK                              | I | V <sub>SS</sub> or open | Not used                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Y <sub>1</sub> -Y <sub>240</sub> | 0 | •                       | LCD driver output.<br>• One of four voltage levels is output<br>according to the data of shift register and<br>FR signal                                                                                                                                                                                                                                                                                              |  |  |  |

| TEST₁                            | Ι |                         | Test mode select<br>• during normal operation <sup>,</sup> connect to V <sub>SS</sub>                                                                                                                                                                                                                                                                                                                                 |  |  |  |

8

Preliminary

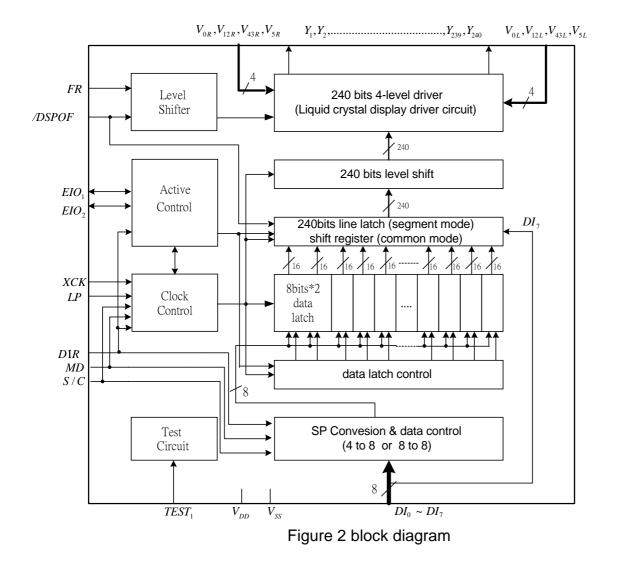

## **BLOCK DIAGRAM**

## FUNCTIONAL DESCRIPTIONS

### . Active Control

In case of segment mode, controls the selection or deselection of the chip. Following a LP signal, and after the chip select signal is input, a select signal is generated internally until 240 bits of data have been read in. Once data input has been completed, a select signal for cascade connection is output, and the chip is non-selected. In case of common mode, controls the input/output data of bi-directional pins.

#### . SP Conversion & Data Control

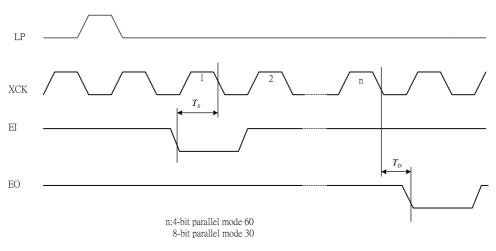

In case of segment mode, keep input data which are 2 clocks of XCK at 4-bit parallel mode into latch circuit, or keep input data which are 1 clock of XCK at 8-bits parallel mode into latch circuit, after that they are put on the internal data bus 8 bits at a time.

#### . Data Latch Control

In case of segment mode, selects the state of the data latch which reads in the data bus signals. The shift direction is controlled by the control logic, for every 16 bits of data read in, the selection signal shifts one bit based on the state of the control circuit.

#### . Data Latch

In case of segment mode, latches the data on the data bus. The latched state of each LCD driver output pin is controlled by the control logic and the data latch control, 240 bits of data are read in 30 sets of 8 bits.

#### . Line Latch / Shift Register

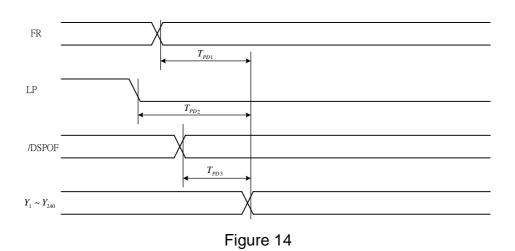

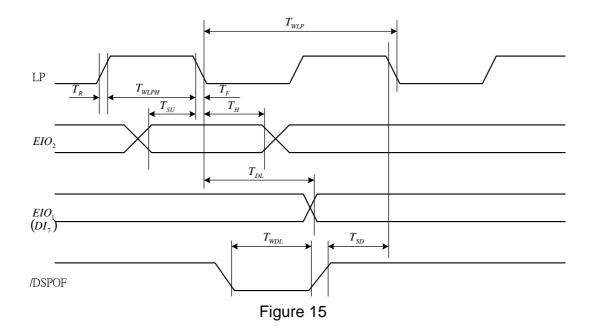

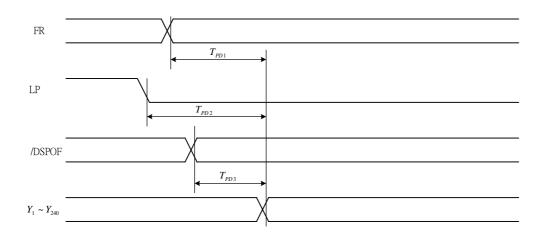

In case of segment mode, all 240 bits, which have been read into the data latch are simultaneously latched on the falling edge of the LP signal, and output to the level shifter block. In case of common mode, shifts data from the data input pin on the falling edge of the LP signal.

#### . Level Shifter

The logic voltage signal is level-shifted to the LCD driver voltage level, and output to the driver block.

## . 4-level Driver

Drive the LCD driver output pins from the line latch/shift register data, selecting one of 4 levels  $(V_0, V_{12}, V_{43}, V_5)$  based on the S/C, FR and /DSPOF

## . Control Logic

Controls the operation of each block. In case of segment mode, when a LP signal has been input, all blocks are reset and the control logic waits for the selection signal output from the active control block.

Once the selection signal has been output, operation of the data latch and data transmission are controlled, 240 bits of data are read in, and the chip is deselected. In case of common mode, controls the direction of data shift.

## .Test Circuit

The circuit for the test. During normal operation, it doesn't act.

## Relation between FR <sup>,</sup> Latch data <sup>,</sup> /DSPOF and output level

#### Table 4 LCD driver output voltage level

(a) Segment mode

| FR                          | Latch data         | /DSPOF              | Driver output voltage level  |

|-----------------------------|--------------------|---------------------|------------------------------|

| Н                           | Н                  | Н                   | V <sub>0</sub>               |

| Н                           | L                  | Н                   | V <sub>12</sub>              |

| L                           | Н                  | Н                   | V <sub>5</sub>               |

| L                           | L                  | Н                   | V <sub>43</sub>              |

| Х                           | Х                  | L                   | V <sub>5</sub>               |

|                             |                    |                     |                              |

|                             |                    |                     |                              |

| $V_{SS} \le V_{5} < V_{43}$ | $< V_{12} < V_0$ H | :V <sub>DD</sub> L: | V <sub>SS</sub> X:Don't care |

#### (b) Common mode

| FR                                   | Latch data               | /DSPOF               | Driver output voltage level  |

|--------------------------------------|--------------------------|----------------------|------------------------------|

| Н                                    | Н                        | Н                    | V <sub>5</sub>               |

| Н                                    | L                        | Н                    | V <sub>12</sub>              |

| L                                    | Н                        | Н                    | V <sub>0</sub>               |

| L                                    | L                        | Н                    | V <sub>43</sub>              |

| Х                                    | Х                        | L                    | V <sub>5</sub>               |

|                                      |                          |                      |                              |

|                                      |                          |                      |                              |

| V <sub>SS</sub> ≦V <sub>5</sub> < V₄ | $_{13} < V_{12} < V_0$ H | l:V <sub>DD</sub> L: | V <sub>SS</sub> X:Don't care |

## Relationship between the display data and driver output pin

Table 5 Relationship between the display data and driver output pin (a)Segment mode (4-bit parallel mode)

| MD | DIR | EIO <sub>1</sub> | EIO <sub>2</sub> | Data   | Figure of clock  |                  |                  |  |                         |                         |                         |

|----|-----|------------------|------------------|--------|------------------|------------------|------------------|--|-------------------------|-------------------------|-------------------------|

|    |     |                  |                  | Input  | 1 <sub>st</sub>  | 2 <sub>nd</sub>  | 3 <sub>rd</sub>  |  | <b>38</b> <sub>th</sub> | <b>39</b> <sub>th</sub> | <b>60</b> <sub>th</sub> |

| Н  | Н   | Input            | Output           | $DI_0$ | $Y_4$            | Y <sub>8</sub>   | Y <sub>12</sub>  |  | Y <sub>232</sub>        | Y <sub>236</sub>        | Y <sub>240</sub>        |

|    |     |                  |                  | $DI_1$ | Y <sub>3</sub>   | Y <sub>7</sub>   | Y <sub>11</sub>  |  | Y <sub>231</sub>        | Y <sub>235</sub>        | Y <sub>329</sub>        |

|    |     |                  |                  | $DI_2$ | $Y_2$            | $Y_6$            | Y <sub>10</sub>  |  | Y <sub>230</sub>        | Y <sub>234</sub>        | Y <sub>238</sub>        |

|    |     |                  |                  | $DI_3$ | $Y_1$            | $Y_5$            | Y <sub>9</sub>   |  | Y <sub>229</sub>        | Y <sub>233</sub>        | Y <sub>237</sub>        |

| Н  | L   | Output           | Input            | $DI_0$ | Y <sub>237</sub> | Y <sub>233</sub> | Y <sub>229</sub> |  | Y <sub>9</sub>          | $Y_5$                   | Y <sub>1</sub>          |

|    |     |                  |                  | $DI_1$ | Y <sub>238</sub> | Y <sub>234</sub> | Y <sub>230</sub> |  | Y <sub>10</sub>         | Y <sub>6</sub>          | Y <sub>2</sub>          |

|    |     |                  |                  | $DI_2$ | Y <sub>239</sub> | Y <sub>235</sub> |                  |  | Y <sub>11</sub>         | Y <sub>7</sub>          | Y <sub>3</sub>          |

|    |     |                  |                  | $DI_3$ | Y <sub>240</sub> | Y <sub>236</sub> | Y <sub>232</sub> |  | Y <sub>12</sub>         | Y <sub>8</sub>          | Y <sub>4</sub>          |

## (b) Segment mode (8-bit parallel mode)

| MD | DIR | EIO1   | EIO2   | Data   |                  |                  | Figu             | re of c | clock                   |                         |                         |

|----|-----|--------|--------|--------|------------------|------------------|------------------|---------|-------------------------|-------------------------|-------------------------|

|    |     |        |        | Input  | 1 <sub>st</sub>  | 2 <sub>nd</sub>  | 3 <sub>rd</sub>  |         | <b>28</b> <sub>th</sub> | <b>29</b> <sub>th</sub> | <b>30</b> <sub>th</sub> |

| L  | Н   | Input  | Output | $DI_0$ | Y <sub>8</sub>   | Y <sub>16</sub>  | Y <sub>24</sub>  |         | Y <sub>224</sub>        | Y <sub>232</sub>        | Y <sub>240</sub>        |

|    |     |        |        | $DI_1$ | Y <sub>7</sub>   | Y <sub>15</sub>  | Y <sub>23</sub>  |         | Y <sub>223</sub>        | Y <sub>231</sub>        | Y <sub>239</sub>        |

|    |     |        |        | $DI_2$ | $Y_6$            | Y <sub>14</sub>  | Y <sub>22</sub>  |         | Y <sub>222</sub>        | Y <sub>230</sub>        | Y <sub>238</sub>        |

|    |     |        |        | $DI_3$ | $Y_5$            | Y <sub>13</sub>  | Y <sub>21</sub>  |         | Y <sub>221</sub>        | Y <sub>229</sub>        | Y <sub>237</sub>        |

|    |     |        |        | $DI_4$ | $Y_4$            | Y <sub>12</sub>  | Y <sub>20</sub>  |         | Y <sub>220</sub>        | Y <sub>228</sub>        | Y <sub>236</sub>        |

|    |     |        |        | $DI_5$ | $Y_3$            | Y <sub>11</sub>  | Y <sub>19</sub>  |         | Y <sub>229</sub>        | Y <sub>227</sub>        | Y <sub>235</sub>        |

|    |     |        |        | $DI_6$ | $Y_2$            | Y <sub>10</sub>  | Y <sub>18</sub>  |         | Y <sub>228</sub>        | Y <sub>226</sub>        | Y <sub>234</sub>        |

|    |     |        |        | $DI_7$ | $Y_1$            | Y۹               | Y <sub>17</sub>  |         | Y <sub>227</sub>        | Y <sub>225</sub>        | Y <sub>233</sub>        |

| L  | L   | Output | Input  | $DI_0$ | Y <sub>233</sub> | Y <sub>225</sub> | Y <sub>217</sub> |         | Y <sub>17</sub>         | Y <sub>9</sub>          | Y <sub>1</sub>          |

|    |     |        |        | $DI_1$ | Y <sub>234</sub> | Y <sub>226</sub> | Y <sub>218</sub> |         | Y <sub>18</sub>         | Y <sub>10</sub>         | Y <sub>2</sub>          |

|    |     |        |        | $DI_2$ | $Y_{235}$        | Y <sub>227</sub> | Y <sub>219</sub> |         | Y <sub>19</sub>         | Y <sub>11</sub>         | Y <sub>3</sub>          |

|    |     |        |        | $DI_3$ | Y <sub>236</sub> | Y <sub>228</sub> | Y <sub>220</sub> |         | Y <sub>20</sub>         | Y <sub>12</sub>         | Y <sub>4</sub>          |

|    |     |        |        | $DI_4$ | Y <sub>237</sub> | Y <sub>229</sub> | Y <sub>221</sub> |         | Y <sub>21</sub>         | Y <sub>13</sub>         | Y <sub>5</sub>          |

|    |     |        |        | $DI_5$ | Y <sub>238</sub> | Y <sub>230</sub> | Y <sub>222</sub> |         | Y <sub>22</sub>         | Y <sub>14</sub>         | Y <sub>6</sub>          |

|    |     |        |        | $DI_6$ | $Y_{239}$        | Y <sub>231</sub> | Y <sub>223</sub> |         | Y <sub>23</sub>         | Y <sub>15</sub>         | Y <sub>7</sub>          |

|    |     |        |        | $DI_7$ | Y <sub>240</sub> | Y <sub>232</sub> | Y <sub>224</sub> |         | Y <sub>24</sub>         | Y <sub>16</sub>         | Y <sub>8</sub>          |

#### (c) Common mode

| MD       | DIR | Data transfer direction             | EIO <sub>1</sub> | EIO <sub>2</sub> | DI <sub>7</sub> |

|----------|-----|-------------------------------------|------------------|------------------|-----------------|

| Н        | Н   | Y <sub>1</sub> ~Y <sub>120</sub>    | Input            | Output           | Input           |

| (Dual)   |     | Y <sub>121</sub> ~Y <sub>240</sub>  |                  |                  |                 |

|          | L   | Y <sub>240</sub> ~ Y <sub>121</sub> | Output           | Input            | Input           |

|          |     | Y <sub>120</sub> ~ Y <sub>1</sub>   |                  |                  |                 |

| L        | Н   | Y <sub>1</sub> ~Y <sub>240</sub>    | Input            | Output           | Х               |

| (Single) | L   | Y <sub>240</sub> ~ Y <sub>1</sub>   | Output           | Input            | Х               |

|          |     |                                     |                  |                  |                 |

|          |     | H:V <sub>DD</sub> L:V <sub>SS</sub> | X:Dor            | n't care         |                 |

Preliminary

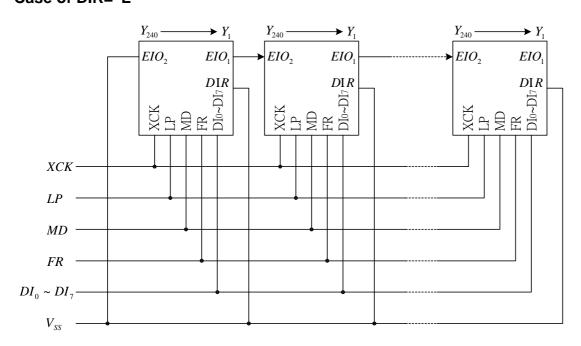

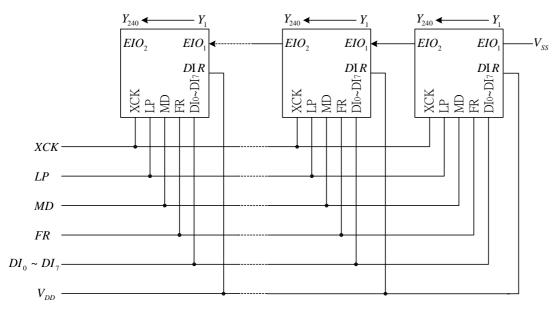

## Connection example of plural segment driver Case of DIR="L"

Case of DIR="H"

Preliminary

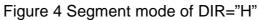

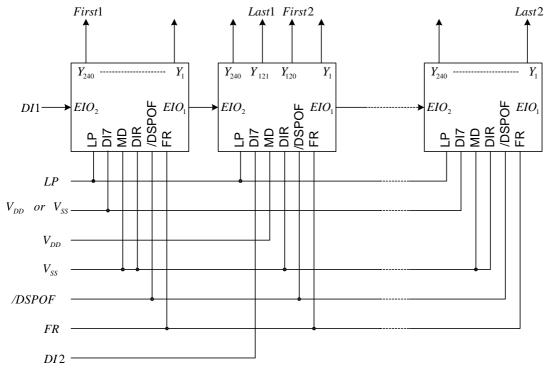

## Connection of plural common driver Single mode DIR="L"

mode DIR="L"

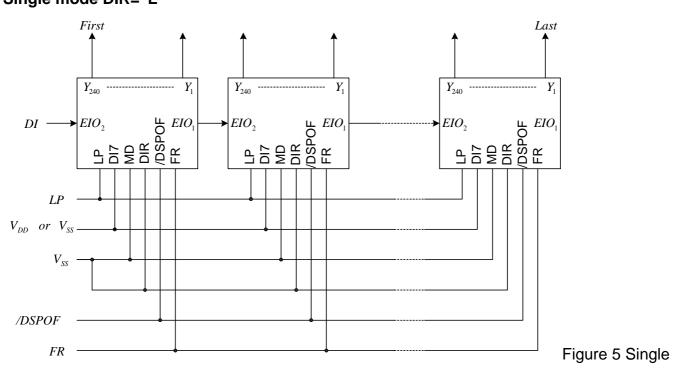

## Single mode DIR="H"

Preliminary

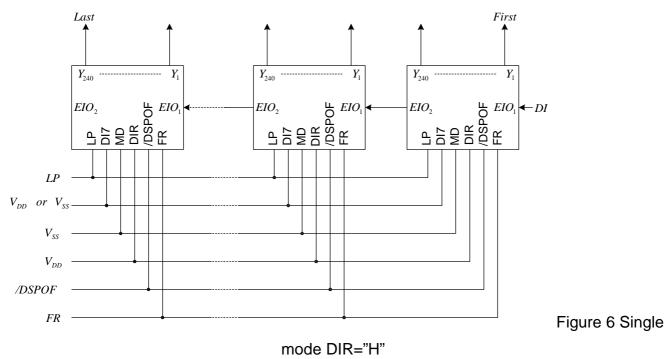

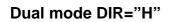

## Connection of plural common driver

Dual mode DIR="L"

Figure 7 Dual mode DIR="L"

Preliminary

Timing chart of 4-device cascade connection of segment driver

| FR                             | _χ                                          |           |

|--------------------------------|---------------------------------------------|-----------|

| LP                             | Л                                           |           |

| ХСК                            |                                             | Л         |

| $DI_0 \sim DI_7$               | Top data<br>n 1 2 3 n 1 2 3 n 1 2 3 n 1 2 3 | Last data |

| EI                             | device A device B device C device D         | L         |

| (device A)<br>EO<br>(device A) |                                             |           |

| EO<br>(device B)               |                                             |           |

| EO<br>(device C)               |                                             |           |

|                                | n:4-bit parallel mode 60                    |           |

8-bit parallel mode 30

Figure 9 Timing chart of 4-device cascade connection of segment driver

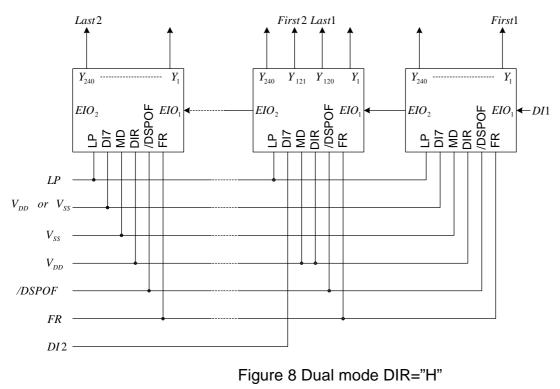

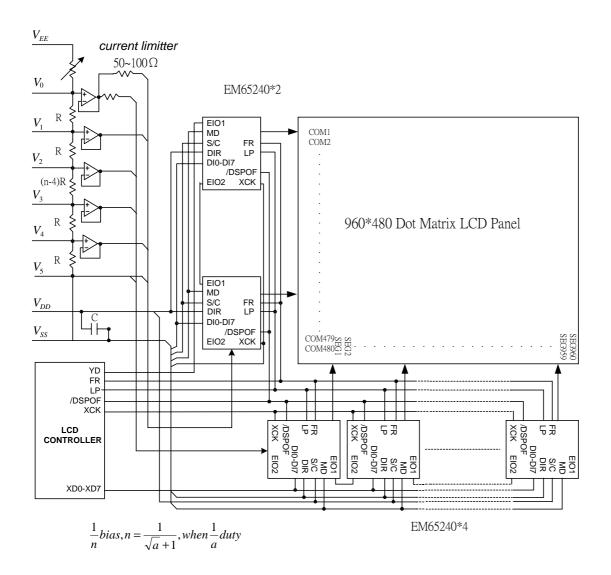

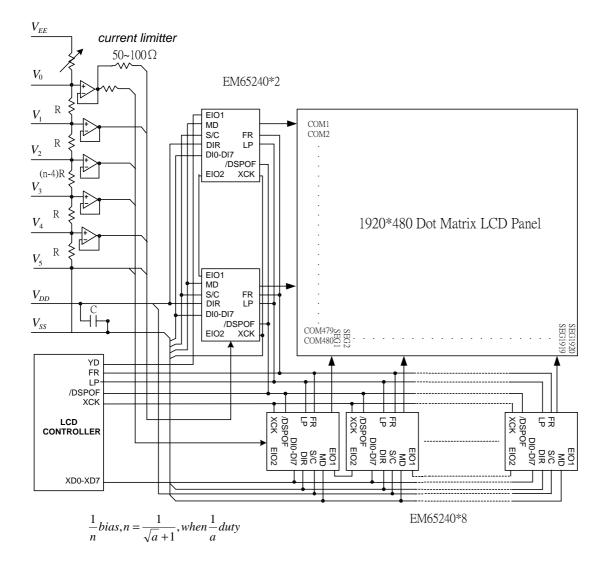

## Power supply circuit for liquid crystal drive

Precaution when Connecting or Disconnecting the Power

This LSI has a high-voltage LCD driver, so it may be permanently damaged by a high current which may flow if a voltage is supplied to the LCD driver power supply while the logic system power supply is floating.

. We recommend you connecting the serial resistor (50~100  $\Omega$ ) or fuse to the LCD drive power V<sub>0</sub> of the system as a current limiter. And set up the suitable of the resistor in consideration of LCD display grade.

<sup>\*</sup> This specification are subject to be changed without notice.

When connecting the power supply, show the following recommend sequence.

## Drive by operational amplifier

In graphic displays, the size of the liquid crystal becomes larger and the display duty ratio becomes smaller, so the stability of liquid crystal drive level is more important than a small display system.

Since the liquid crystal for graphic display is large and has many picture elements, the load capacitance becomes large. The high impedance of power supply for liquid crystal drive produce distortion in the drive waveforms, and degrades display quality. For the reason, the liquid crystal drive level impedance should be reduced with operational amplifiers.

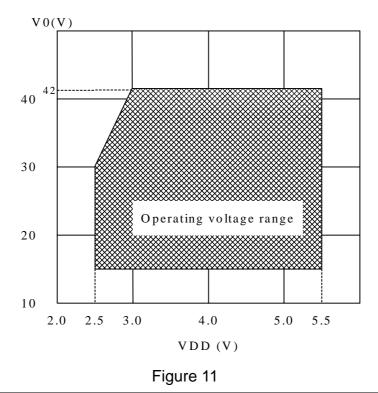

## Range of Operating Voltage: V0

It is necessary to set the voltage for V0 within the VDD operating voltage range shown in the diagram below.

\* This specification are subject to be changed without notice.

Preliminary

## ABSOLUTE MAXIMUM RATINGS

| Parameter          | Symbol           | Conditions           | Applicable pins                     | Ratings              | Unit |

|--------------------|------------------|----------------------|-------------------------------------|----------------------|------|

| Supply voltage (1) | $V_{DD}$         | T <sub>a</sub> =25℃  | V <sub>DD</sub>                     | -0.3 to +7.0         | V    |

|                    | V <sub>0</sub>   | Reference            | V <sub>0L</sub> , V <sub>0R</sub>   | -0.3 to +45.0        | V    |

| Supply voltage (2) | V <sub>12</sub>  | d to                 | V <sub>12L</sub> , V <sub>12R</sub> | -0.3 to              | V    |

|                    |                  | V <sub>SS</sub> (0V) |                                     | V <sub>0</sub> +0.3  |      |

|                    | V <sub>43</sub>  |                      | V <sub>43L</sub> , V <sub>43R</sub> | -0.3 to              | V    |

|                    |                  |                      |                                     | V <sub>0</sub> +0.3  |      |

|                    | V <sub>5</sub>   |                      | V <sub>5L</sub> , V <sub>5R</sub>   | -0.3 to              | V    |

|                    |                  |                      |                                     | V <sub>0</sub> +0.3  |      |

| Input voltage      | VI               |                      | DI <sub>0-7</sub> , XCK, LP,        | -0.3 to              | V    |

|                    |                  |                      | DIR,                                | V <sub>DD</sub> +0.3 |      |

|                    |                  |                      | FR, MD, S/C, EIO <sub>1</sub> ,     |                      |      |

|                    |                  |                      | EIO <sub>2</sub> ,                  |                      |      |

|                    |                  |                      | /DSPOF,TEST <sub>1</sub>            |                      |      |

| Storage            | T <sub>stg</sub> |                      |                                     | -45 to +125          | °C   |

| temperature        | Ŭ                |                      |                                     |                      |      |

#### Table 6 absolute maximum ratings

## **Recommended operation conditions**

| Parameter                | Symbol           | Conditions                   | Applicable       | Min. | Тур. | Max  | Unit |  |  |

|--------------------------|------------------|------------------------------|------------------|------|------|------|------|--|--|

|                          |                  |                              | pins             |      |      |      |      |  |  |

| Supply voltage (1)       |                  | Reference                    | $V_{DD}$         | +2.5 |      | +5.5 | V    |  |  |

| Supply voltage (2)       | V <sub>0</sub>   | d to V <sub>SS</sub><br>(0V) | $V_{0L}, V_{0R}$ | +15  |      | +42  | V    |  |  |

| Operating<br>temperature | T <sub>opr</sub> |                              |                  | -20  |      | +85  | °C   |  |  |

Table 7 recommended operation conditions

Preliminary

## **DC CHARACTERISTICS**

### Segment mode

#### Table 8 DC characteristics of segment mode

$(V_{SS} = V_5 = 0V, V_{DD} = +2.5 \text{ to } +5.5V, V_0 = +15 \text{ to } +42V, T_a = -20 \approx +85^{\circ}C)$

| Parameter                                | Symbo            |                                 | ditions                  | Applicable                                                              | Min                      |      |                   | Unit |

|------------------------------------------|------------------|---------------------------------|--------------------------|-------------------------------------------------------------------------|--------------------------|------|-------------------|------|

| Farameter                                | J                | Cond                            | unions                   | pins                                                                    | IVIIII                   | Туре | Wax               | Unit |

| Input<br>voltage                         | V <sub>IH</sub>  |                                 |                          | DI₀ -DI⁊, XCK,<br>LP,DIR,FR,M                                           | 0.8V <sub>D</sub>        |      |                   | V    |

| Ū                                        | V <sub>IL</sub>  |                                 |                          | D,<br>S/C,EIO <sub>1</sub> ,<br>EIO <sub>2</sub> , /DSPOF               | _                        |      | 0.2V <sub>D</sub> | V    |

| Output<br>voltage                        | V <sub>OH</sub>  | I <sub>ОН</sub> =-0             | .4mA                     | EIO <sub>1</sub> , EIO <sub>2</sub>                                     | V <sub>DD</sub> -0.<br>4 |      |                   | V    |

| -                                        | V <sub>OL</sub>  | $I_{OL}=+0$                     | .4mA                     |                                                                         |                          |      | +0.4              | V    |

| Input                                    | I <sub>LIH</sub> | V <sub>I</sub> =V <sub>DI</sub> | )                        | DI <sub>0</sub> -DI <sub>7</sub> , XCK,                                 |                          |      | +10               | uA   |

| leakage<br>current                       | I <sub>LIL</sub> | V <sub>I</sub> =V <sub>SS</sub> | 3                        | LP, DIR, FR,<br>MD, S/C,EIO <sub>1</sub> ,<br>EIO <sub>2</sub> , /DSPOF |                          |      | -10               | uA   |

| Output<br>resistance                     | R <sub>ON</sub>  | ∆<br>V <sub>ON</sub>            | V <sub>0</sub> =+40<br>V |                                                                         |                          | 1.0  | 1.5               | kΩ   |

|                                          |                  | =0.5V                           | V <sub>0</sub> =+30<br>V |                                                                         |                          | 1.5  | 2.0               |      |

|                                          |                  |                                 | V <sub>0</sub> =+20<br>V |                                                                         |                          | 2.0  | 2.5               |      |

| Stand-by<br>current                      | I <sub>STB</sub> | *1                              |                          | V <sub>SS</sub>                                                         |                          |      | 75.0              | uA   |

| Consumed<br>current<br>(Deselectio<br>n) | I <sub>DD1</sub> | *2                              |                          | V <sub>DD</sub>                                                         |                          |      | 2.0               | mA   |

| Consumed<br>current<br>(Selection)       | I <sub>DD2</sub> | *3                              |                          | V <sub>DD</sub>                                                         |                          |      | 12.0              | mA   |

| Consumed current                         | I <sub>0</sub>   | *4                              |                          | V <sub>0</sub>                                                          |                          |      | 1.5               | mA   |

NOTE : 1.  $V_{DD}$  = +5V,  $V_0$  = +42V,  $V_1$  =  $V_{SS}$

2.  $V_{DD} = +5V$ ,  $V_0 = +42V$ ,  $f_{XCK} = 20MHz$ , No-load, EI =  $V_{DD}$ The input data is turned over by data taking clock (4-bit parallel input mode) 3.  $V_{DD} = +5V$ , V0 = +42V,  $f_{XCK} = 20MHz$ , No-load, EI =  $V_{SS}$ The input data is turned over by data taking clock (4-bit parallel input mode) 4.  $V_{DD} = +5V$ , V0 = +42V,  $f_{XCK} = 20MHz$ ,  $f_{LP} = 41.6$ kHz,  $f_{FR} = 80$ Hz, No-load The input data is turned over by data taking clock (4-bit parallel input mode)

## Preliminary

## Common mode

### Table 9 DC characteristics of common mode

#### (VSS = V5 = 0V, VDD = +2.5 to 5.5V, V0 = +15 to +42V, Ta = -20~85°C)

| Parameter                     | Symbo            | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Applicable                                                                                        | Min                  | Тур | Max               | Unit |

|-------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------|-----|-------------------|------|

|                               | Ī                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | pins                                                                                              |                      | e   |                   |      |

| Input                         | V <sub>IH</sub>  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DI <sub>0</sub> -DI <sub>7</sub> , XCK,                                                           | $0.8V_{DD}$          |     |                   | V    |

| voltage                       | VIL              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LP,DIR,FR,M                                                                                       |                      |     | $0.2V_{\text{D}}$ | V    |

|                               |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | D,                                                                                                |                      |     | D                 |      |

|                               |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | S/C,EIO <sub>1</sub> ,                                                                            |                      |     |                   |      |

|                               |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | EIO <sub>2</sub> , /DSPOF                                                                         |                      |     |                   |      |

| Output                        | V <sub>OH</sub>  | I <sub>OH</sub> = -0.4mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | EIO <sub>1</sub> , EIO <sub>2</sub>                                                               | V <sub>DD</sub> -0.4 |     | <u> </u>          | V    |

| voltage                       | V <sub>OL</sub>  | $I_{OL}$ = +0.4mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                   |                      |     | +0.4              | V    |

| Input<br>leakage<br>current   | I <sub>LIH</sub> | VI=V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DI <sub>0</sub> -DI <sub>7</sub> , XCK,<br>LP, DIR, FR,<br>MD, S/C,<br>/DSPOF                     |                      |     | +10               | uA   |

|                               | I <sub>LIL</sub> | V <sub>I</sub> =V <sub>SS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $DI_0$ - $DI_7$ , XCK,<br>LP, DIR, FR,<br>MD, S/C,EIO <sub>1</sub> ,<br>EIO <sub>2</sub> , /DSPOF |                      |     | -10               | uA   |

| Output<br>resistance          | R <sub>ON</sub>  | $ \Delta $ V <sub>0</sub> =+40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Y <sub>1</sub> - Y <sub>240</sub>                                                                 |                      | 1.0 | 1.5               | kΩ   |

| Tesistance                    |                  | $ V_{ON}  = 0.5V  V_0=+30  V_$ | -                                                                                                 |                      | 1.5 | 2.0               |      |