# Am25S18

Quad D Register with Standard and Three-State Outputs

#### DISTINCTIVE CHARACTERISTICS

- Advanced Schottky technology

- Four D-type flip-flops

- · Four standard totem-pole outputs

- Four three-state outputs

- 75MHz clock frequency

#### **GENERAL DESCRIPTION**

The Am25S18 consists of four D-type flip-flops with a buffered common clock. Information meeting the set-up and hold requirements on the D inputs is transferred to the Q outputs on the LOW-to-HIGH transition of the clock.

The same data as on the Q outputs is enabled at the threestate Y outputs when the "output control" ( $\overline{OE}$ ) input is LOW. When the  $\overline{OE}$  input is HIGH, the Y outputs are in the high-impedance state.

The Am25S18 is a 4-bit, high speed Schottky register intended for use in real-time signal processing systems

where the standard outputs are used in a recursive algorithm and the three state outputs provide access to a data bus to dump the results after a number of iterations.

The device can also be used as an address register or status register in computers or computer peripherals.

Likewise, the Am25S18 is also useful in certain display applications where the standard outputs can be decoded to drive LED's (or equivalent) and the three-state outputs are bus organized for occasional interrogation of the data as displayed.

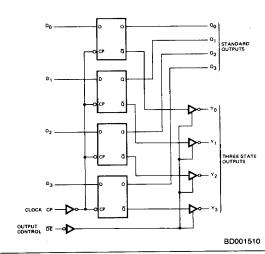

#### **BLOCK DIAGRAM**

#### **RELATED PRODUCTS**

| Part No.   | Description |  |

|------------|-------------|--|

| Am25S07    | Register    |  |

| Am25S08    | Register    |  |

| Am25S09    | Register    |  |

| Am25S374   | Register    |  |

| Am29821-26 | Register    |  |

03613B

Refer to Page 13-1 for Essential Information on Military Devices

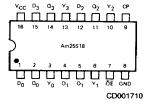

# **CONNECTION DIAGRAM Top View**

Note: Pin 1 is marked for orientation

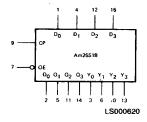

### LOGIC SYMBOL

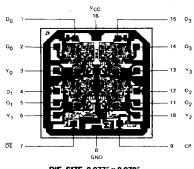

#### **METALLIZATION AND PAD LAYOUT**

DIE SIZE 0.077" x 0.079"

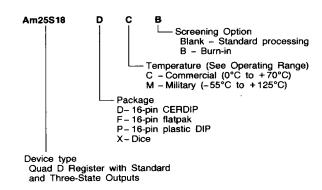

#### ORDERING INFORMATION

AMD products are available in several packages and operating ranges. The order number is formed by a combination of the following: Device number, speed option (if applicable), package type, operating range and screening option (if desired).

01150

| Valid Combinations |                              |  |  |  |  |

|--------------------|------------------------------|--|--|--|--|

| Am25S18            | PC<br>DC, DM<br>FM<br>XC, XM |  |  |  |  |

#### **Valid Combinations**

Consult the AMD sales office in your area to determine if a device is currently available in the combination you wish.

03613B

### PIN DESCRIPTION

| Pin No. | Name | 1/0 | Description                                                                                                                                                                                                                   |

|---------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Di   | ī   | The four data inputs to the register.                                                                                                                                                                                         |

|         | Qi   | 0   | The four data outputs of the register with standard totem-pole active pull-up outputs. Data is passed non-inverted.                                                                                                           |

|         | Yi   | 0   | The four three-state data outputs of the register. When the three-state outputs are enabled, data is passed non-inverted. A HIGH on the "output control" input forces the Y <sub>i</sub> outputs to the high-impedance state. |

| 9       | СР   | 1   | Clock. The buffered common clock for the register. Enters data on the LOW-to-HIGH transition.                                                                                                                                 |

| 7       | ŌĒ   | 0   | Output Control. When the OE input is HIGH, the Y <sub>i</sub> outputs are in the high-impedance state. When the OE input is LOW, the TRUE register data is present at the Y <sub>i</sub> outputs.                             |

#### TRUTH TABLE

|    | INPUTS      |   | оит |                  |       |

|----|-------------|---|-----|------------------|-------|

| ŌĒ | CLOCK<br>CP | D | Q   | Y                | NOTES |

| Н  |             | Х | NC  | Z                | _     |

| н  | н           | х | NC  | Z<br>Z<br>Z<br>Z | -     |

| Н  | 1           | L | L   | Z                | -     |

| Н  | Ť           | н | н   | Z                | -     |

| L  | 1           | L | L   | L                | l   – |

| L  | İ †         | н | Н   | Н                | -     |

| L  | _           | - | L   | L                | 1     |

| L  | -           |   | н   | Н                | 1     |

L = LOW NC = No change

H = HIGH t = LOW to HIGH transition

X = Don't care Z = High impedance

Note: 1. When OE is LOW, the Y output will be in the same logic state as the Q output.

# **LOADING RULES (In Unit Loads)**

|                |             |                    | Fan-out                 |     |  |

|----------------|-------------|--------------------|-------------------------|-----|--|

| Input/Output   | Pin<br>Nos. | Input<br>Unit Load | Output Outp<br>HIGH LOV |     |  |

| D <sub>0</sub> | 1           | 1                  | -                       |     |  |

| Q <sub>0</sub> | 2           | -                  | 20                      | 10* |  |

| Yo             | 3           | -                  | 40/130                  | 10* |  |

| D <sub>1</sub> | 4           | 1                  | -                       | -   |  |

| Q <sub>1</sub> | 5           | -                  | 20                      | 10* |  |

| Y <sub>1</sub> | 6           | _                  | 40/130                  | 10* |  |

| ŌĒ.            | 7           | 1                  | -                       | -   |  |

| GND            | 8           | _                  | -                       | -   |  |

| CP             | 9           | 1                  | -                       | -   |  |

| Y <sub>2</sub> | 10          | _                  | 40/130                  | 10* |  |

| Q <sub>2</sub> | 11          | _                  | 20                      | 10* |  |

| D <sub>2</sub> | 12          | 1                  | -                       | _   |  |

| Y <sub>3</sub> | 13          |                    | 40/130                  | 10* |  |

| Q <sub>3</sub> | 14          | -                  | 20                      | 10* |  |

| D <sub>3</sub> | 15          | 1                  |                         |     |  |

| Vcc            | 16          |                    | -                       |     |  |

A Schottky TTL Unit Load is defined as  $50\mu A$  measured at 2.7V HIGH and -2.0mA measured at 0.5V LOW.

03613B

<sup>\*</sup>Fan-out on each  $Q_i$  and  $Y_i$  output pair should not exceed 15 unit loads (30mA) for  $i=0,\ 1,\ 2,\ 3$

03613B

#### ABSOLUTE MAXIMUM RATINGS

| Storage Temperature65°C to +150°C              |

|------------------------------------------------|

| (Ambient) Temperature Under Bias55°C to +125°C |

| Supply Voltage to Ground Potential             |

| (Pin 16 to Pin 18) Continuous0.5V to +7.0V     |

| DC Voltage Applied to Outputs For              |

| HIGH Output State0.5V to +V <sub>CC</sub> max  |

| DC Input Voltage0.5V to +5.5V                  |

| DC Output Current, Into Outputs 30mA           |

| DC Input Current30mA to +5.0mA                 |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

| Commerciał (C) Devices Temperature                                      |                          |

|-------------------------------------------------------------------------|--------------------------|

| Military (M) Devices                                                    |                          |

| Temperature                                                             | 55°C to +125°C           |

| Supply Voltage                                                          | + 4.5V to + 5.5V         |

| Operating ranges define those limits ality of the device is guaranteed. | over which the function- |

# DC CHARACTERISTICS over operating range unless otherwise specified

| Parameters               | Description                              | Description Test Conditions (Note 2)                                                                   |     |                            | 2)           | Min  | Typ<br>(Note 1) | Max   | Units |

|--------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------|-----|----------------------------|--------------|------|-----------------|-------|-------|

|                          | 1                                        |                                                                                                        |     |                            | MIL          | 2.5  | 3.4             |       |       |

|                          |                                          | V <sub>CC</sub> = MiN.                                                                                 | Q K | Q lon = -1mA o             |              | 2.7  | 3.4             |       |       |

| VoH                      | Output HiGH Voltage                      | VIN = VIH or VIL                                                                                       |     | XM, I <sub>OH</sub> = -2mA |              | 2.4  | 3.4             |       | Volts |

|                          |                                          |                                                                                                        | Y   | XC, IOH -                  | -6.5mA       | 2.4  | 3.2             |       |       |

| VoL                      | Output LOW Voltage (Note 6)              | V <sub>CC</sub> = MIN., I <sub>OL</sub> = 20mA<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> |     |                            |              |      | 0.5             | Volts |       |

| VIH                      | Input HIGH Level                         | Guaranteed input logical HIGH voltage for all inputs                                                   |     |                            |              | 2.0  |                 |       | Volts |

| VIL                      | Input LOW Level                          | Guaranteed input logical LOW voltage for all inputs                                                    |     |                            |              |      | 0.8             | Volts |       |

| VI                       | Input Clamp Voltage                      | V <sub>CC</sub> = MIN., I <sub>IN</sub> = -18mA                                                        |     |                            |              |      | -1.2            | Volts |       |

| (Note 3)                 | Input LOW Current                        | V <sub>CC</sub> = MAX., V <sub>IN</sub> = 0.5V                                                         |     |                            |              |      | -2.0            | mA    |       |

| I <sub>IH</sub> (Note 3) | Input HIGH Current                       | V <sub>CC</sub> = MAX., V <sub>IN</sub> = 2.7V                                                         |     |                            |              |      | 50              | μА    |       |

| ų                        | input HiGH Current                       | V <sub>CC</sub> = MAX., V <sub>IN</sub> = 5.5V                                                         |     |                            |              |      | 1.0             | mA    |       |

|                          | Y Output Off-State                       | $V_{CC} = MAX.$ $V_{O} = 2.4V$ $V_{O} = 0.4V$                                                          |     |                            | $V_O = 2.4V$ |      |                 | 50    |       |

| lo                       | Leakage Current                          |                                                                                                        |     |                            |              | - 50 | μΑ              |       |       |

| ISC                      | Output Short Circuit Current<br>(Note 4) | V <sub>CC</sub> = MAX.                                                                                 |     |                            | -40          |      | - 100           | mA    |       |

| lcc                      | Power Supply Current                     | V <sub>CC</sub> = MAX. (Note                                                                           | 5)  |                            |              | 1    | 80              | 130   | mA    |

- Notes: 1. Typical limits are at V<sub>CC</sub> = 5.0V, T<sub>A</sub> = 25°C ambient and maximum loading.

2. For conditions shown as MIN. or MAX., use the appropriate value specified under Operating Ranges for the applicable device type.

3. Actual input currents = Unit Load Current x Input Load Factor (See Loading Rules).

4. Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

5. I<sub>CC</sub> is measured with all inputs at 4.5V and all outputs open.

6. Measured on Q outputs with Y outputs open. Measured on Y outputs with Q outputs open.

# SWITCHING CHARACTERISTICS ( $T_A = +25^{\circ}C$ , $V_{CC} = 5.0V$ , $R_L = 280\Omega$ )

| Parameters       | Description              |         | Test Conditions         | Min | Тур  | Max  | Units |

|------------------|--------------------------|---------|-------------------------|-----|------|------|-------|

| t <sub>PLH</sub> | 8                        |         |                         |     | 6.0  | 9.0  | ns    |

| t <sub>PHL</sub> | Clock to Q Output        |         |                         |     | 8.5  | 13   | ns ns |

|                  | Clastic Bules Middle     | HIGH    |                         | 7.0 |      |      |       |

| t <sub>pw</sub>  | Clock Pulse Width        | LOW     |                         | 9.0 |      |      | ns    |

| ts               | Data                     |         | C <sub>L</sub> = 15pF   | 5.0 |      |      | ns    |

| h ,              | Data Clock to Y Output   |         |                         | 3.0 |      |      | ns    |

| t <sub>PLH</sub> |                          |         |                         |     | 6.0  | 9.0  |       |

| t <sub>PHL</sub> | (ÕĒ LOW)                 |         | Г                       |     | 8.5  | 13   | ns    |

| t <sub>ZH</sub>  |                          |         | 0 45-5                  |     | 12.5 | 19   | 1     |

| <sup>l</sup> ZL  | Output Control to Output |         | C <sub>L</sub> = 15pF ~ |     | 12   | 18   | 1     |

| tHZ              |                          |         | 0 - 5 n=                |     | 4.0  | 6.0  | ns    |

| LZ               |                          |         | C <sub>L</sub> = 5.0pF  | *   | 7.0  | 10.5 | 1     |

| fmax             | Maximum Clock Fro        | equency | C <sub>L</sub> = 15pF   | 75  | 100  | ·    | MHz   |

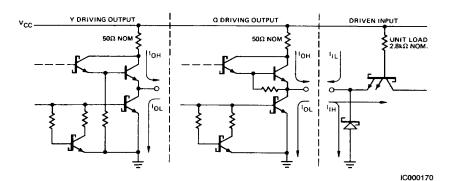

# SCHOTTKY INPUT/OUTPUT CURRENT INTERFACE CONDITIONS

Note: Actual current flow direction shown.