# High Speed, Combi-Sense®, Synchronous MOSFET Driver for Mobile Applications

## POWER MANAGEMENT

#### Description

The SC1211VX is a high speed, Combi-Sense®, dual output driver designed to drive high-side and low-side MOSFETs in a synchronous Buck converter. These drivers combined with Combi-Sense® PWM controllers, such as Semtech SC2643VX or SC2643, provide a cost effective multi-phase voltage regulator for advanced microprocessors.

The Combi-Sense  $\ensuremath{\mathbb{R}}$  is a technique to sense the inductor current for peak current mode control of voltage regulator without using sensing resistor. It provides the following advantages:

- No costly precision sensing resistor

- Lossless current sensing

- High level noise free signal

- Fast response

- Suitable for wide range of duty cycle

- Only two small signal components (third optional) The detailed explanation of the technique can be found in the Applications Information section.

A 30ns max propagation delay from input transition to the gate of the power FET's guarantees operation at high switching frequencies. Internal overlap protection circuit prevents shoot-through from Vin to PGND in the main and synchronous MOSFETs. The adaptive overlap protection circuit ensures the bottom FET does not turn on until the top FET source has reached 1V, to prevent crossconduction.

High current drive capability allows fast switching, thus reducing switching losses at high (up to 1.5MHz) frequencies without causing thermal stress on the driver.

Under-voltage-lockout and over-temperature shutdown features are included for proper and safe operation. Timed latches and improved robustness are built into the housekeeping functions such as the Under Voltage Lockout and adaptive Shoot-through protection circuitry to prevent false triggering and to assure safe operation. The SC1211VX is offered in a Power SOIC-8L package.

#### Features

- High efficiency

- High peak drive current

- Adaptive non-overlapping gate drives provide shoot-through protection

- Support Combi-Sense® and VID-on-fly operations

- Fast rise and fall times (15ns typical with 3000pf load)

- Ultra-low (<30ns) propagation delay (BG going low)

- Floating top gate drive

- Crowbar function for over voltage protection

- High frequency (to 1.5 MHz) operation allows use of small inductors and low cost ceramic capacitors

- Under-voltage-lockout

- Low quiescent current

- Power SOIC-8L package, fully RoHS and WEEE compliant

#### Applications

- ◆ Intel Pentium<sup>®</sup> processor power supplies

- AMD Athlon<sup>™</sup> and AMD-K8<sup>™</sup> processor power supplies

- High efficiency portable and notebook computers

- Battery powered applications

- High current low voltage DC-DC converters

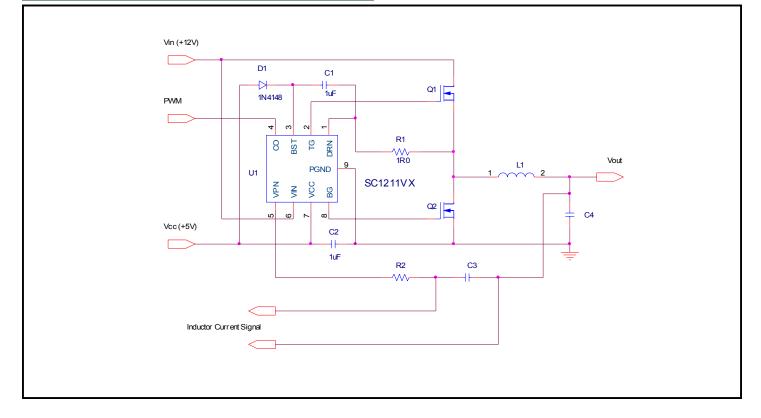

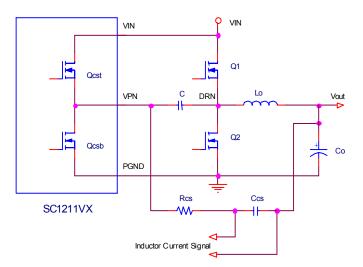

**Typical Application Circuit**

# SC1211VX

#

# POWER MANAGEMENT

### Absolute Maximum Ratings

Exceeding the specifications below may result in permanent damage to the device, or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not implied.

| Parameter                            | Symbol                 | Conditions                                   | Maximum     | Units |

|--------------------------------------|------------------------|----------------------------------------------|-------------|-------|

| V <sub>cc</sub> Supply Voltage       | V <sub>cc</sub>        |                                              | 10          | V     |

| VIN to PGND                          | V <sub>IN</sub>        |                                              | 30          | V     |

| BST to DRN                           | V <sub>BST-DRN</sub>   |                                              | 10          | V     |

| BST to PGND                          | V <sub>BST-PGND</sub>  |                                              | 36          | V     |

| BST to PGND Pulse                    | V <sub>BST_PULSE</sub> | t <sub>PULSE</sub> < 100ns                   | 41          | V     |

| DRN to PGND                          | V <sub>DRN-PGND</sub>  |                                              | -2 to 29    | V     |

| DRN to PGND Pulse                    |                        | t <sub>PULSE</sub> < 100ns                   | -4 to 34    | V     |

| VPN to PGND                          | V <sub>PN</sub>        |                                              | 30          | V     |

| PWM Input                            | СО                     |                                              | -0.3 to 5   | V     |

| Continuous Power Dissipation         | P <sub>D</sub>         | T <sub>A</sub> = 25°C, T <sub>J</sub> =125°C | 2.56        | W     |

| Thermal Resistance Junction to Case  | θ <sub>JC</sub>        |                                              | 8           | °C/W  |

| Operating Junction Temperature Range | TJ                     |                                              | 0 to +125   | °C    |

| Storage Temperature Range            | T <sub>STG</sub>       |                                              | -65 to +150 | °C    |

| Lead Temperature (Soldering) 10 Sec. | T <sub>LEAD</sub>      |                                              | 300         | °C    |

#### NOTE:

(1) This device is ESD sensitive. Use of standard ESD handling precautions is required.

#### **Electrical Characteristics**

Unless specified:  $T_A = 25^{\circ}C$ ;  $V_{CC} = 5V$

| Parameter                    | Symbol                | Conditions | Min | Тур | Мах | Units |

|------------------------------|-----------------------|------------|-----|-----|-----|-------|

| Power Supply                 |                       |            |     |     |     |       |

| Supply Voltage               | V <sub>cc</sub>       |            | 4.3 | 5   | 6.0 | V     |

| Quiescent Current, Operating | lq_op                 |            |     | 3.0 |     | mA    |

| Under Voltage Lockout        |                       |            |     |     |     |       |

| Start Threshold              | V <sub>CC_START</sub> |            |     | 4   | 4.3 | V     |

| Hysteresis                   | Vhys <sub>uvlo</sub>  |            |     | 160 |     | mV    |

# SEMTECH

## **POWER MANAGEMENT**

# Electrical Characteristics (Cont.)

Unless specified:  $T_A = 25^{\circ}C$ ;  $V_{cc} = 5V$

| Parameter                        | Symbol                | Conditions                                           | Min | Тур  | Мах | Units  |

|----------------------------------|-----------------------|------------------------------------------------------|-----|------|-----|--------|

| со                               |                       |                                                      | -   |      |     |        |

| High Level Input Voltage         | V <sub>CO_H</sub>     |                                                      | 2.0 |      |     | V      |

| Low Level Input Voltage          | V <sub>co_L</sub>     |                                                      |     |      | 0.8 | V      |

| Thermal Shutdown                 | 1                     |                                                      |     |      |     |        |

| Over Temperature Trip Point      | T <sub>OTP</sub>      |                                                      |     | 155  |     | °C     |

| Hysteresis                       | T <sub>HYST</sub>     |                                                      |     | 10   |     | °C     |

| High Side Driver (TG)            |                       |                                                      |     |      |     |        |

| Output Impodance                 | R <sub>SRC_TG</sub>   |                                                      |     | 1.24 | 1.8 | - Ohms |

| Output Impedance                 | R <sub>SINK_TG</sub>  | $V_{BST} - V_{DRN} = 5V$                             |     | 0.86 | 1.3 |        |

| Rise Time                        | t <sub>R_TG</sub>     | CL = 3.3nF, V <sub>BST</sub> - V <sub>DRN</sub> = 5V |     | 8    |     | ns     |

| Fall Time                        | t <sub>F_TG</sub>     | CL = 3.3nF, V <sub>BST</sub> - V <sub>DRN</sub> = 5V |     | 8    |     | ns     |

| Propagation Delay, TG Going High | t <sub>PDH_TG</sub>   | $V_{BST} - V_{DRN} = 5V$                             |     | 20   |     | ns     |

| Propagation Delay, TG Going Low  | t <sub>PDL_TG</sub>   | $V_{BST} - V_{DRN} = 5V$                             |     | 25   |     | ns     |

| Low-Side Driver (BG)             |                       |                                                      |     |      |     |        |

| Output Resistance                | R <sub>SRC_BG</sub>   | V <sub>BST</sub> - V <sub>DRN</sub> = 5V             |     | 1.28 | 1.7 | Ohms   |

|                                  | R <sub>SINK_BG</sub>  |                                                      |     | 0.6  | 1.2 |        |

| Rise Time                        | t <sub>R_BG</sub>     | $CL = 3.3 nF, V_{BST} - V_{DRN} = 5V$                |     | 8    |     | ns     |

| Fall Time                        | t <sub>F_BG</sub>     | $CL = 3.3nF, V_{BST} - V_{DRN} = 5V$                 |     | 4    |     | ns     |

| Propagation Delay, BG Going High | t <sub>PDH_BG</sub>   | $V_{BST} - V_{DRN} = 5V$                             |     | 20   |     | ns     |

| Propagation Delay, BG Going Low  | t <sub>PDL_BG</sub>   | $V_{BST} - V_{DRN} = 5V$                             |     | 25   |     | ns     |

| Under-Voltage-Lockout Time Dela  | у                     |                                                      |     |      |     |        |

| V <sub>cc</sub> ramping up       | t <sub>PDH_UVLO</sub> |                                                      |     | 2    |     | μs     |

| V <sub>cc</sub> ramping down     | t <sub>PDL_UVLO</sub> |                                                      |     | 2    |     | μs     |

# POWER MANAGEMENT

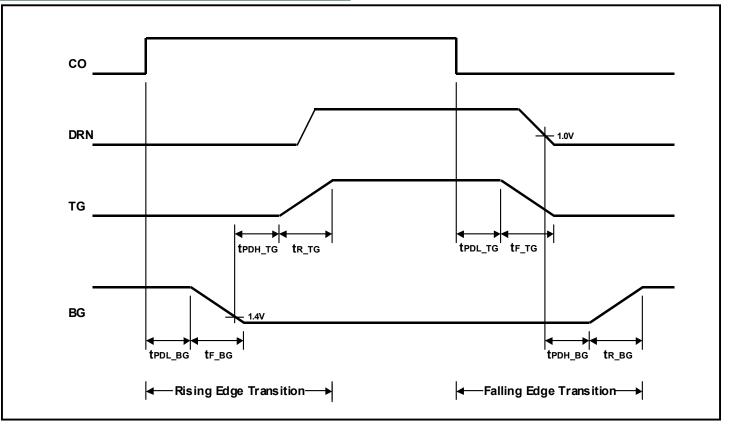

Timing Diagrams

# EMTECH

# POWER MANAGEMENT

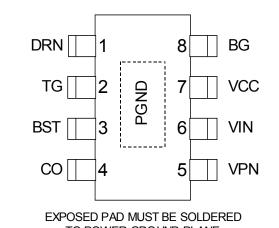

## Pin Configuration

TO POWER GROUND PLANE

#### **Pin Descriptions**

#### Pin # **Pin Name Pin Function** The power phase node (or switching node) of the synchronous Buck converter. This pin can be 1 DRN subjected to a negtative spike up to -Vcc relative to PGND without affecting operation. 2 TG Output gate drive for the switching (top) MOSFET. Bootstrap pin. A capacitor is connected between BST and DRN pins to develop the floating 3 BST bootstrap voltage for the high-side MOSFET. The capacitor value is typically 1µF (ceramic). Logic level PWM input signal to the SC1211VX supplied by external controller. An internal 50kohm 4 CO resistor is connected from this pin to PGND. Virtual Phase Node. Connect an RC between this pin and the output sense point of the converter to VPN 5 enable Combi-Sense ® operation. See the Typical Application Circuit. Sensing input for internal Combi-Sense ® circuitry. Connect as close as possible to the Drain of 6 VIN the top MOSFET. Supply power for the SC1211VX. Connect to 5V supply for optimum operation. A 1.0uF-4.7uF 7 VCC Capacitor must be connected from this pin to PGND as close as possible. 8 BG Output gate drive for the synchronous (bottom) MOSFET. PAD PGND Ground. Keep this pin close to the synchronous MOSFET source.

## Ordering Information

| Device <sup>(1)</sup>       | Package  | Temp Range (T <sub>J</sub> ) |

|-----------------------------|----------|------------------------------|

| SC1211VXSTR                 | EDP SO-8 | 0° to 125°C                  |

| SC1211VXSTRT <sup>(2)</sup> | EDP SO-8 | 0° to 125°C                  |

Note:

(1) Only available in tape and reel packaging. A reel contains 2500 devices.

(2). SC1211VXSTRT is lead free part.

# POWER MANAGEMENT

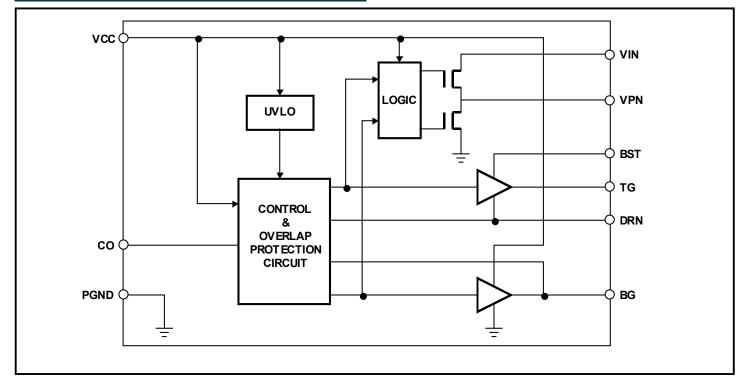

# Block Diagram

#### **Applications Information**

#### THEORY OF OPERATION

The SC1211VX is a high speed, Combi-Sense®, dual output driver designed to drive top and bottom MOSFETs in a synchronous Buck converter. It features adaptive delay for shoot-through protection and VID-on-Fly operation; 5V gate drive voltage; and Virtual Phase Node for Combi-Sense® solution. These drivers combined with PWM controller SC2643VX form a multi-phase voltage regulator for advanced microprocessors. A three-phase voltage regulator with 19V input 60A output is shown in the Typical Application Circuit section.

#### Startup and UVLO

To startup the driver, a supply voltage applied to VCC pin of the SC1211VX. The top and bottom gates are held low until VCC exceeds UVLO threshold of the driver, typically 4.2V. Then the top gate remains low and the bottom gate is pulled high to turn on the bottom FET. Once VIN exceeds UVLO threshold of the PWM controller, typically 7.5V, the soft-start begins and the PWM signal takes fully control of the gate transitions.

#### Gate Transition and Shoot through Protection

Refer to the Timing Diagrams section, the rising edge of the PWM input initiates the bottom FET turn-off and the top FET turn-on. After a short propagation delay (tPDL\_BG), the bottom gate begins to fall (tF\_BG). An adaptive circuit in the SC1211VX monitors the bottom gate voltage to drop below 1.4V. Then after a preset delay time (tPDH\_TG) is expired, the top gate turns on. The delay time is set to be 20ns typically. This prevents the top FET from turning on until the bottom FET is off. During the transition, the inductor current is freewheeling through the body diode of either bottom FET or top FET, upon the direction of the inductor current. The phase node could be low (ground) or high (VIN).

The falling edge of the PWM input controls the top FET turn-off and the bottom FET turn-on. After a short propagation delay (tPDL\_TG), the top gate begins to fall (tF\_TG). As the inductor current is commutated from the top FET to the body diode of the bottom FET, the phase node begins to fall. The adaptive circuit in the SC1211VX detects the phase node voltage. It holds the bottom FET off until the phase node voltage has dropped below 1.0V. This prevents the top and bottom FETs from conducting

#### **VID-on-Fly Operation**

Certain new processors have required to changing the VID dynamically during the operation, or refered as VIDon-Fly operation. A VID-on-Fly can occur under light load or heavy load conditions. At light load, it could force the converter to sink current. Upon turn-off of the top FET, the reversed inductor current has to be freewheeling through the body diode of the top FET instead of the bottom FET. As a result, the phase node voltage remains high. The SC1211VX incorporates the ability by pulling the bottom gate to high internally, which over rides the adaptive circuit and turns the bottom FET on. The delay time from the PWM falling egde to the bottom gate turnon is set at 200ns typically.

#### Virtual Phase Node for Combi-Sense®

Peak-Current-Mode control is widely employed in multiphase voltage regulators. It features phase current balance, fast transient response, and over current protection, etc. These are essential to low-voltage high-current regulators designed for advanced microprocessors. Usually, a costly current sensing resistor is required to obtain the output inductor current information for the peak current control. The Combi-Sense® technique featured by the SC1211VX is an approach to sense inductor current without using sensing resistor.

The above circuit shows the concept of Combi-Sense® technique. An internal totem pole (Qcst, Qcsb) generates a VPN (Virtual Phase Node) signal. This VPN follows the DRN (or the Power Phase Node) with the same timing. A RC network (Rcs and Ccs) is connected between

#### Applications Information (Cont.)

VPN and Vout. During Q1 turn-on, Qcst turns on as well. The voltage drop across Q1 and Lo charges Ccs. During Q2 turn-on, Qcsb turns on as well. The voltage drop across Q2 and Lo discharges Ccs. Both voltage drops are proportional to the inductor current and a resistance equal to FET's Rdson plus ESR of the inductor. If the time constant Rcs x Ccs is close to the Lo/Ro of the inductor, where Ro is given by

$$Ro = R_{inductor} + R_{dson\ hs} * D + R_{dson\ ls} * (1-D)$$

the signal developed across Ccs will be proportional to the inductor current, where Ro is the equivalent current sensing resistance. In the above equation, Rinductor is ESR of the inductor, Rdson\_hs and Rdson\_ls are the top and bottom FET's Rdson, and D is the duty cycle of the converter.

Since a perfect timing match down to the nanosecond is impossible, the VPN totem pole is held in tri-state during the communitations of DRN in the SC1211VX. This avoids errors and offset on the current detection which can be significant since the timing mismatch is multiplied by the input voltage. An optional capacitor between VPN and DRN allows these two nodes to be AC coupled during the tri-state window, hence yields a perfect timing match. Refer to Semtech SC2643VX Combi-Sense® Current Mode Controller about the details of the Combi-Sense® technique.

#### Thermal Shut Down

The SC1211VX will shut down by pulling both driver outputs low if its junction temperature, Tj, exceeds 155°C.

#### COMPONENT SELECTION

#### Switching Frequency, Inductor and MOSFETs

The SC1211VX is capable of providing up to 3.5A peak drive current, and operating up to 1.5MHz PWM frequency without causing thermal stress on the driver. The selection of switching frequency, together with inductor and FETs is a trade-off between the cost, size, and thermal management of a multi-phase voltage regulator. In modern microprocessor applications, these parameters could

| Switching Frequency | 100kHz to 500kHz per phase      |

|---------------------|---------------------------------|

| Inductor Value      | 0.2uH to 2uH                    |

| FETs                | 4m-ohm to 20m-ohm Rdson         |

|                     | 20nC to 100nC total gate charge |

#### **Bootstrap Circuit**

The SC1211VX uses an external bootstrap circuit to provide a voltage for the top FET drive. This voltage, referring to the Phase Node, is held up by a bootstrap capacitor. The capacitor value can be calculated based on the total gate charge of the top FET, QTOP, and an allowed voltage ripple on the capacitor,  $\Delta VBST$ , in one PWM cycle:

#### $CBST > QTOP / \Delta VBST$

Typically, it is recommended to use a 1uF ceramic capacitor with 25V rating and a commonly available diode IN4148 for the bootstrap circuit. In addition, a small resistor (one ohm) has to be added in between DRN of the SC1211VX and the Phase Node. The resistor is used to allievate the stress of the SC1211VX from exposing to the negative spike at the Phase node. A negative spike could occur at the Phase Node during the top FET turnoff due to parasitic inductance in the switching loop. The spike could be minimized with a careful PCB layout. In those applications with TO-220 package FETs, it is recommended to use a clamping diode on the DRN pin to mitigate the impact of the excessive phase node negative spike.

#### Filters for Supply Power

For VCC pin of the SC1211VX, it is recommended to use a 1uF to 4.7uF, 25V rating ceramic capacitor for decoupling.

#### LAYOUT GUIDELINES

The switching regulator is a high di/dt power circuit. Its Printed Circuit Board (PCB) layout is critical. A good layout can achieve an optimum circuit performance while minimized the component stress, resulting in better system reliability. For a multi-phase voltage regulator, the SC1211VX driver, FETs, inductor, and supply decoupling capacitors in each phase have to be considered as a

### Applications Information (Cont.)

whole during PCB layout. Refer to Semtech SC2643VX/ SC1211VX EVB Layout Guideline.

For the SC1211VX driver, the following guidelines are typically recommended during PCB layout:

1. Place the SC1211VX close to the FETs for shortest gate drive traces and ground return paths.

2. Connect the bypass capacitor as close as possible to pin VCC and PGND for decoupling.

3. Locate the components of the bootstrap circuit close to the SC1211VX.

#### SOLDERING CONSIDERATION

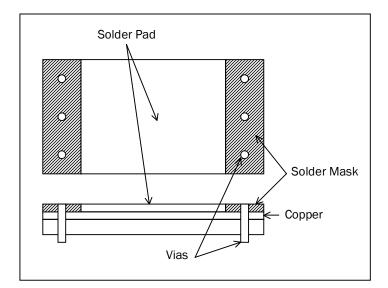

The exposed die pad of the SC1211VX is used for ground return and thermal release of the driver. The pad must be soldered to the ground plane that is further connected to the system ground in the inner layer through multiple vias. For better electrical and thermal performance, it is recommended to use all copper available under the driver as the ground plane, and place the vias as close as possible to the solder pad. Meanwhile, the vias have to be masked out to prevent solder leakage during reflow. The layout arrangement is detailed in the above figure, which also can be found in the "Land Pattern – Power SOIC-8" section.

SC1211VX

# SEMTECH

# SC1211VX

# POWER MANAGEMENT

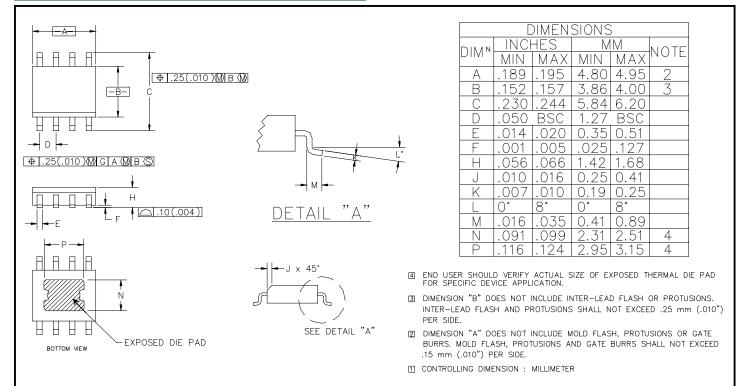

## Outline Drawing - Power SOIC-8L

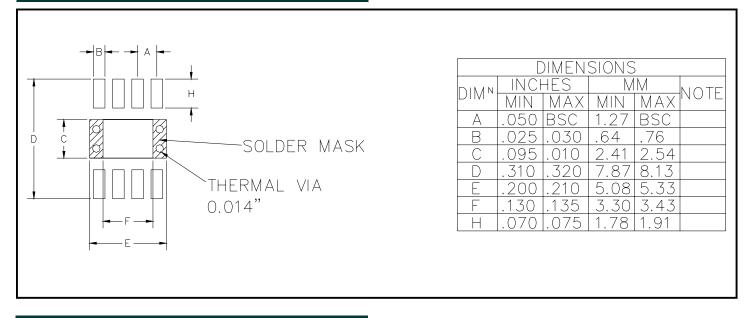

### Land Pattern - Power SOIC-8

## **Contact Information**

Semtech Corporation Power Management Products Division 200 Flynn Rd., Camarillo, CA 93012 Phone: (805)498-2111 FAX (805)498-3804