Preliminary Data Sheet

## FEATURES

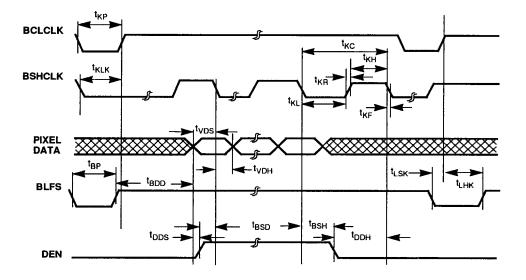

FEB

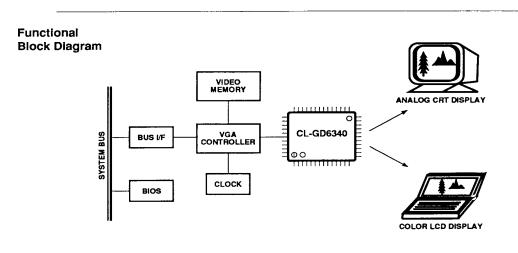

- 100% IBM<sup>®</sup> VGA compatible at the display level

- Supports SimulSCAN<sup>™</sup> displays on CRT and LCD simultaneously

- Provides full-color VGA on 8- or 512-color TFT (Thin Film Transistor) and other active-matrix or color STN (Super Twist Nematic) LCD panels:

- -256 display colors in Mode 13

- 16 display colors in Mode 12

- Enhanced color palette

- Supports VGA color modes on monochrome LCD panels:

- 64 shade grayscale in Mode 13 (direct-multiplexed panels)

- 16 shade grayscale in Mode 12 (direct-multiplexed panels)

- Supports Automap<sup>™</sup>, color-to-grayscale mapping in text and graphics modes

- Support for monochrome, color TFT active matrix, and color STN LCD panels

- On-chip buffers and logic to support monochrome and color active matrix and direct-multiplexed (Passive) LCDs, of both single- and dual-panel construction

- Fully integrated and compatible with the existing CL-GD610/620 and CL-GD6410 VGA chipsets, as well as future Cirrus Logic flat panel controllers

(cont. next page)

## Color LCD Interface Controller

## **OVERVIEW**

The CL-GD6340 color LCD (Liquid Crystal Display) interface controller provides full-color VGA graphics on LCD panels. By using proprietary techniques for color shading, the CL-GD6340 is able to increase the number of colors that the LCD panel can display. On an eight-color active-matrix LCD panel, a palette of over 4,000 display colors can be generated, from which up to 256 colors can be displayed at one time in VGA Mode 13. On a 512-color active-matrix LCD panel, the number of available colors is over 185,000. The CL-GD6340 also provides a palette of over 226,000-color palette on eight-color STN panels, as well as up to 64 shades of gray on monochrome panels.

The CL-GD6340 integrates the following major functions:

- Shading logic for generating grayscale and color on LCDs,

(cont. next page)

## FEATURES (cont.)

- 32 MHz operation for compatibility with high-performance VGA chips

- Support for flat panels includes buffers to the panels, STN LCDs with monochrome (single and dual panels) and color (single and dual panels)

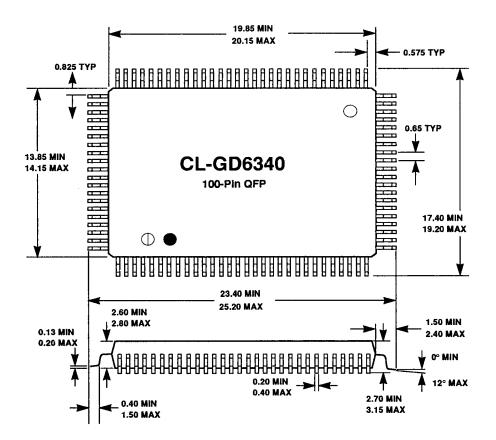

- Packaged in EIAJ-standard 100-pin plastic Quad Flat Pack (QFP) package

- Low-power CMOS construction

- Enhanced power management features

- Provides power-up/down sequence control to flat panel displays

- Programmable grayscale circuits

- Integrated CRT RAMDAC compatible with IMS<sup>®</sup> 171/174 or Brooktree<sup>®</sup> 471/475

- Low chip count solution

## ADVANTAGES

- Expands the number of display colors

- Flexible architecture includes a programmable panel interface with buffers, timing, and power sequencing logic

- Provides simultaneous display on analog CRT and digital LCD (SimulSCAN)

- CL-GD6340-based portable computers, driving internal and external displays simultaneously, can be used for live presentations

- Integrates VGA RAMDAC

- Provides LCD image quality comparable with that of a CRT in all VGA modes

- Thousands of display colors provide subtlety of shading necessary for real-life and three-dimensional images

- Supports multiple panels and types; color, monochrome, passive, and active-matrix panels

- Provides a highly integrated solution for minimum-form-factor designs

## OVERVIEW (cont.)

Highly programmable flat-panel interface with buffers, timing, and power sequencing output that enables the use of many different panels from various manufacturers, and

RAMDAC with RGB color lookup table and digital-toanalog converter

The CL-GD6340 is optimized to provide full VGA graphics on monochrome or color LCD panels. The programmable architecture allows the flexibility to support LCD panels from a large variety of vendors, as well as other display technologies including gas plasma, electro-luminescent, and CRT.

The CL-GD6340 handles subtle gradations of shade and hue, expands the total color (or grayscale) capability of an LCD, and provides a display quality that compares to an analog CRT. With a complete Cirrus Logic color LCD VGA solution, even eightcolor panels can support all VGA modes (including Mode 13), displaying 256 colors simultaneously from a palette of thousands. This color range is critical to lifelike, three-dimensional images, and is increasingly important for graphical user interfaces.

The CL-GD6340 can simultaneously drive analog CRTs and digital outputs to LCD panels. Its integrated RAMDAC enables the design of a minimumsize VGA solution, providing unequaled color capacity for the portable and flat panel markets.

2 PRELIMINARY

## Table of Contents

| See              | ction Page                                      |

|------------------|-------------------------------------------------|

| 1.               | PIN INFORMATION5                                |

| 1.1              | Pin Diagram5                                    |

| 1.2              | Pin Assignment Table                            |

|                  |                                                 |

| 2.               | DETAILED PIN DESCRIPTION8                       |

| 2.1              | CPU Interface (28 pins)8                        |

| 2.2              | External Interface (2 pins)8                    |

| 2.3              | Graphic Controller Interface (14 pins)9         |

| 2.4              | CRT Interface (8 pins)10                        |

| 2.5              | Panel Interface (24 pins)11                     |

| 2.6              | Frame-Accelerator Memory Interface              |

|                  | (16 pins)12                                     |

| 2.7              | Power (8 pins)12                                |

| 2                | FUNCTIONAL DESCRIPTION13                        |

| <b>3.</b><br>3.1 |                                                 |

| 3.1              | CPU Interface14<br>Graphic Controller Interface |

| 3.3              | Frame-Accelerator Controller                    |

| 3.4              | RAMDAC                                          |

| 3.5              | Analog Monitor Sense                            |

| 3.6              | Panel Power Sequencing                          |

| 3.6.1            | Panel Inactive Sequence                         |

| 3.6.2            | 2 Panel Active Sequence                         |

| 3.7              | CRT Sequence Control22                          |

| 3.8              | Power-Down Modes23                              |

| 3.9              | Sleep Mode25                                    |

| 4.               | VGA/EGA REGISTER TABLE26                        |

| -                |                                                 |

| 5.               | RAMDAC I/O PORT SUMMARY                         |

|                  | TABLE27                                         |

| 5.1              | RAMDAC Pixel Mask: PELMSK                       |

| 5.2              | RAMDAC Pixel Read Address: PELRD29              |

| 5.3              | RAMDAC Pixel Write Address: PELWR30             |

| 5.4<br>5.5       | RAMDAC Border Color Register: BDRCLR 31         |

| <b>D</b> .D      | RAMDAC Pixel Data Register: PELDATA .32         |

| 6.               | CL-GD6340 EXTENSION                             |

| •.               | REGISTERS                                       |

| 6.1              | Extensions Index Register: ERX                  |

| 6.2              | Miscellaneous Control Register 2: MISC2 .35     |

| 6.3              | LCD Control Register 1: LCDCNTLI                |

| 6.4              | LCD Control Register 2: LCDCNTLI                |

| 6.5              | Miscellaneous Register 3: MISC3                 |

| 6.6              | Red Frame Color Register: RFRCLR                |

| 6.7              | Green Frame Color Register: GFRCLR40            |

| 6.8              | Blue Frame Color Register: BFRCLR41             |

| Octo             | ber 1991                                        |

| Sec         | tion                                           | Page |

|-------------|------------------------------------------------|------|

| 6.9<br>6.10 |                                                |      |

| 6.11        | Row Offset Register: ROWOFF                    | 43   |

|             | Panel Row Segment Total Register:<br>PRST      |      |

| 6.13        |                                                | 46   |

| 6.14        | Panel Control Register 2: PNLCTLII             |      |

| 6.15        | Grayscale Control Register 1: GSCNTL           | 1 48 |

| 6.16        | Programmable Retrace LLCLK Register<br>PRLLCLK |      |

| 6.17        | Modulation Register: MOD                       | 50   |

| 6.18        | Enable Readback Register: ENRDBK               | 50   |

| 6.19        | Scratch Pad Registers: VSCR0-7                 | 51   |

| 6.20        | VIPAC Chip Revision Level Register:<br>VIPREV  |      |

| 6.21        | Programmable CL1 Delay Register:               |      |

| 0.21        | PRGCL1                                         | 54   |

| 6.22        | Border Control Register: BDRCTRL               | 55   |

| 6.23        |                                                |      |

| ••          | Register 1: GSCF1                              | 56   |

| 6.24        |                                                |      |

|             | Register 2: GSCF2                              | 57   |

| 6.25        | Panel Control Register 3: PNCTRL3              | 58   |

| 6.26        | Panel Control Register 4: PNCTRL4              |      |

| 6.27        | VSYNC Delay Register: VSDY                     | 60   |

| 6.28        | Number of Grayscales                           |      |

|             | Register: NGRAY                                | 61   |

| 6.29        | Panel Interface Control Register 1:<br>PNCTRL1 |      |

| 6.30        | Frame Rate Duty Control                        |      |

|             | Register 1: FRDC1                              | 64   |

| 6.31        | Frame Rate Duty Control                        |      |

| •.•.        | Register 2: FRDC2                              | 65   |

| 6.32        | Panel Interface Control Register 2:            |      |

|             | PNCTRL2                                        | 66   |

| 6.33        | VGA Interface Register: VGAI                   | 67   |

| 7.          | ELECTRICAL SPECIFICATIONS                      | 68   |

| 7.1         | Absolute Maximum Ratings                       | 68   |

| 7.2         | DC Characteristics (Digital)                   |      |

| 7.3         | DC Characteristics (RAMDAC)                    | 70   |

| 7.4         | AC Specifications                              | 71   |

7.4.1 Index of Timing Information ......71

\_\_\_\_

## Table of Contents (cont.)

| Sec                                  | tion                                                                                                                                             | Page            | Figu                                          | res Pa                                                                                                                                                                                            | ige                             |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

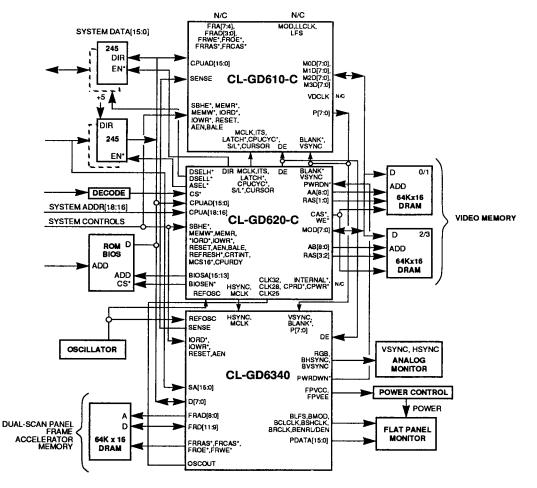

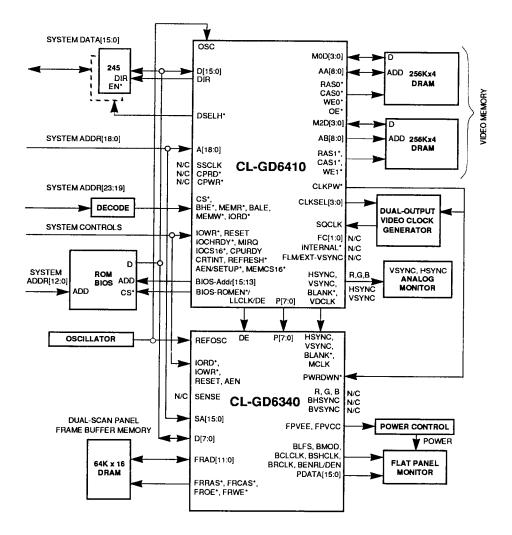

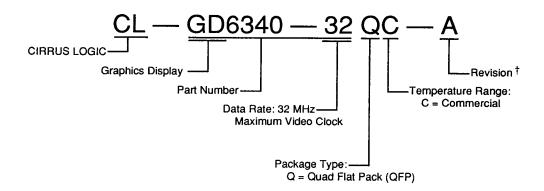

| <b>8.</b><br>8.1<br>8.2<br><b>9.</b> | VGA CONTROLLER TO<br>CL-GD6340 INTERFACES<br>CL-GD610/620-C-to-CL-GD6340<br>Interface<br>CL-GD6340-to-CL-GD6410 Interface<br>PACKAGE INFORMATION | 82<br>83        | 1–1<br>3–1<br>3–3<br>3–3<br>3–4<br>3–5<br>3–6 | CL-GD6340 Pin Diagram<br>CL-GD6340 Block Diagram<br>CPU Interface<br>Graphics Controller Interface<br>Frame-Accelerator Block Diagram<br>RAMDAC Block Diagram<br>Sequencing for Power and Signals | .13<br>.14<br>.15<br>.16<br>.18 |

| 9.1                                  | 100-Pin QFP                                                                                                                                      | 84              | 3–7                                           | Sequencing for Power and Signals (cont.)                                                                                                                                                          |                                 |

| <b>10.</b><br>10.1                   | ORDERING INFORMATION<br>Numbering Guide<br>Glossary<br>Index                                                                                     | 85<br><b>86</b> | 8–1<br>8–2<br>9–1                             | CL-GD610/620-C to CL-GD6340<br>System Block Diagram<br>CL-GD6340 to CL-GD6410<br>System Block Diagram<br>100-Pin Plastic Quad Flat Pack                                                           | .83                             |

|                                      |                                                                                                                                                  |                 | 9-1<br>10-1                                   |                                                                                                                                                                                                   | -<br>                           |

## SimulSCAN Operation

SimulSCAN operation, a Cirrus Logic technique for allowing simultaneous CRT and LCD operation, is a feature unique to the Cirrus Logic controllers. SimulSCAN allows the portable computer to become a key part of presentation environments for sales force automation, field service, and educational organizations.

#### SimulSCAN Functions

- Simultaneous display on internal LCD and external CRT

- Compatible with VGA modes

- Compatible with VGA applications software

#### SimulSCAN Features

- An external display for audience presentations

fixed frequency or multi-frequency analog CRT

- An internal display for computer operation

single-scan or dual-scan LCD (6.3 MHz panel speed required for dual-scan LCD)

- Reverse intensity (optional) on the internal monochrome display; simultaneous with normal operation of the external display

SimulSCAN allows the portable computer to be used in large audience presentation/demonstration environments. With SimulSCAN, the computer provides an analog RGB video signal for overhead projection systems, standard CRTs, or large-screen CRTs, for the audience to view while maintaining operation of the computer's internal LCD display for the computer operator to view.

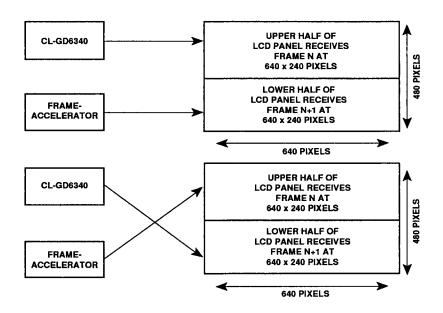

To achieve SimulSCAN operation, the CL-GD6340 provides separate CRT and LCD display data output paths. Resolution-mapping logic converts the various CRT resolutions to the fixed resolution of the LCD. Clock management logic converts the CRT timing to LCD timing, and CL-GD6340 is able to provide clock signals at different rates to two displays simultaneously. The Frame-Accelerator stores half of the screen image, and effectively re-formats the data path to dual-scan LCDs.

4 PRELIMINARY

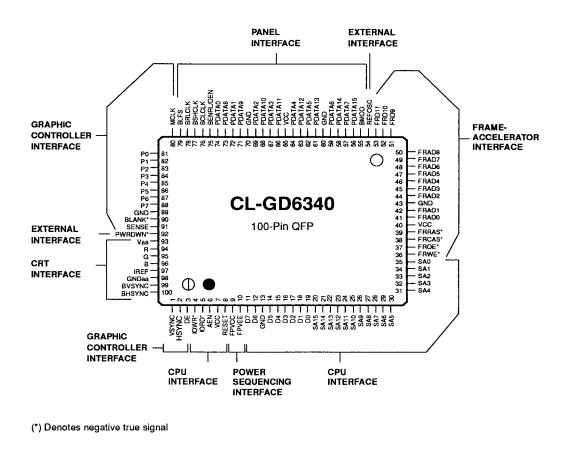

## **1. PIN INFORMATION**

The CL-GD6340 is available in a 100-pin Quad Flat Pack (QFP). The diagram below shows the pinout of this package.

#### 1.1 Pin Diagram

346340-1

October 1991

\_\_\_\_\_

### 1.2 Pin Assignment Table

| Symbol Pin       | Туре                      | Description                                                                                       |

|------------------|---------------------------|---------------------------------------------------------------------------------------------------|

| CPU INTERFACE (  | 28 PINS)                  |                                                                                                   |

| RESET 8          | 1                         | System Reset                                                                                      |

| SA[15:0] 20-     | 35 I                      | Latched CPU Address Bus                                                                           |

|                  | 12, 14-19 I/O             | CPU Data Bus                                                                                      |

| AEN 6            | 1                         | Address Enable for DMA usage only                                                                 |

| IORD* 5          | l                         | Read Enable to internal registers                                                                 |

| IOWR* 4          | I                         | Write Enable to internal register                                                                 |

| EXTERNAL INTERI  | FACE (2 PINS)             |                                                                                                   |

| REFOSC 54        | 1                         | Oscillator Input must be connected to a clock, usually the 14 MHz system oscillator.              |

| PWRDWN* 92       | I                         | Power-Down Input                                                                                  |

| GRAPHIC CONTRO   | OLLER INTERFACE (14       | PINS)                                                                                             |

| P[7:0] 81-8      |                           | Pixel Data Bits [7:0]                                                                             |

| MCLK 80          |                           | Master Clock                                                                                      |

| BLANK* 90        | iC                        | Video Blanking Signal                                                                             |

| DE 3             | IC                        | Display Enable                                                                                    |

| HSYNC 2          | iC                        | Horizontal Sync                                                                                   |

| VSYNC 1          | IC                        | Vertical Sync                                                                                     |

| SENSE 91         | 0                         | Monitor Sense Output                                                                              |

| CRT INTERFACE (8 | B PINS)                   |                                                                                                   |

| IREF 97          | OA                        | Current Reference Input.                                                                          |

|                  |                           | An external current reference must sink 6.7 mA.                                                   |

| Vaa 93           | P                         | Analog Power                                                                                      |

| GNDaa 98         | G                         | Analog Ground                                                                                     |

| R, G, B 94-9     | 96 OA                     | Output, high-impedance current source to directly drive a doubly terminated 75 ohm coaxial cable. |

| BHSYNC 100       | то                        | Buffered HSYNC for direct connection to an analog monitor.                                        |

| BVSYNC 99        | то                        | Buffered VSYNC for direct connection to an analog monitor.                                        |

| PANEL INTERFACE  | E (24 PINS)               |                                                                                                   |

| BLFS 79          | то                        | Buffered LCD Frame Start                                                                          |

| BMOD 55          | то                        | Buffered MODulation                                                                               |

|                  | 59, 61-64 TO<br>69, 71-74 | Panel Data                                                                                        |

| BCLCLK 76        | то                        | Buffered Column Line Clock for TFT/STN Panels                                                     |

| BRLCLK 78        | то                        | Buffered Row Line Clock for TFT Panels                                                            |

| BENRL/DEN 75     | то                        | Enable Row Line Clock for TFT or Display Enable                                                   |

| BSHCLK 77        | TO                        | Buffered Shift Clock to Panel Shift Register                                                      |

| FPVCC 9          | 0                         | Power Sequence Control Bit 1 (Vcc on)                                                             |

| FPVEE 10         | õ                         | Power Sequence Control Bit 0 (Vee on)                                                             |

6 PRELIMINARY

-----

### **1.2 Pin Assignment Table** (cont.)

| Symbol     | Pin                  | Туре      | Description                                                       |

|------------|----------------------|-----------|-------------------------------------------------------------------|

| FRAME-ACC  | ELERATOR MEN         | ORY INTER | RFACE (16 PINS)                                                   |

| FROE*      | 37                   | 0         | Frame-Accelerator Output Enable                                   |

| FRCAS*     | 38                   | 0         | Frame-Accelerator CAS*                                            |

| FRRAS*     | 39                   | 0         | Frame-Accelerator RAS*                                            |

| FRWE*      | 36                   | 0         | Frame-Accelerator Write Enable                                    |

| FR-AD[8:0] | 41, 42,44-50         | 1/0       | Frame-Accelerator Multiplexed Address/Data                        |

| FR-D[11:9] | 51,52,53             | I/O       | Frame-Accelerator Upper 3 bits of data for dual-scan color panels |

| POWER (8 P | INS)                 |           |                                                                   |

| vcc        | 7, 40, 65            | Р         | 3 VCC pads total                                                  |

| GND        | 13, 43, 60<br>70, 89 | G         | 5 GND pads total                                                  |

#### NOTE:

The following conventions are used in the pin assignment tables:

| (*) in                       | dicates that a signal is asserted low | (TO) = CMOS Output |                    |  |

|------------------------------|---------------------------------------|--------------------|--------------------|--|

| (G)                          | = Ground                              | (I)                | = TTL-Level Input  |  |

| (IA)                         | = Analog Input                        | (IC)               | = CMOS-Level Input |  |

| (1/0)                        | = CMOS-Level Input/Output             | (OA                | ) = Analog Output  |  |

| $\langle \mathbf{O} \rangle$ |                                       |                    |                    |  |

- (O) = CMOS-Level Output

- (P) = Power

## 2. DETAILED PIN DESCRIPTION

The following conventions are used in the pin assignment tables: (\*) indicates that a signal is asserted low; (03) indicates Tri-state; (G) indicates Ground; (I) indicates TTL-Level Input; (IA) indicates Analog Input; (IC) indicates CMOS-Level Input; (I/O) indicates TTL-Level Input/Output; (O) indicates CMOS-Level Output; (OA) indicates Analog Output; (O) indicates TTL-Level Output and (P) indicates Power.

#### 2.1 CPU Interface (28 pins)

| Symbol   | Pin           | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET    | 8             | I    | System Reset: This input is normally connected to the System Reset Bus Signal and is used as a hardware reset.                                                                                                                                                                                                                                                                                                                                               |

| SA[15:0] | 20-35         | I    | Latched CPU System Address Bus: Demultiplexed address<br>bus for direct connection between the CPU and the CL-GD6340<br>for video RAM addresses and I/O register addresses.                                                                                                                                                                                                                                                                                  |

| D[7:0]   | 11, 12, 14-19 | I/O  | <b>CPU Data Bus:</b> Data Bus between the CPU and the chip for video RAM addresses, I/O register addresses, and data. In CL-GD610/620-controller-based systems, these pins are connected to the controller side of the Multiplexed Address/Data Bus buffers. In CL-GD6410-based systems, these pins are either connected to the controller side of the data buffers (if any) or directly to the system data bus. (if there are less than four ISA Bus slots) |

| AEN      | 6             | I    | Address Enable for DMA Usage Only: Host CPU bus signal that distinguishes between DMA and non-DMA bus cycles. The signal is high for a DMA Cycle.                                                                                                                                                                                                                                                                                                            |

| IORD*    | 5             | I    | Input/Output Read Enable to Internal Registers: When low,<br>this signal indicates that an IORD* Cycle is taking place. The<br>CL-GD6340 will respond only if proper I/O port addresses have<br>been decoded, and AEN is low.                                                                                                                                                                                                                                |

| IOWR*    | 4             | I    | Input/Output Write Enable to Internal Register: When low,<br>this signal indicates that an IOWR* Cycle is taking place. The<br>CL-GD6340 will respond only if proper I/O port addresses have<br>been decoded, and AEN is low.                                                                                                                                                                                                                                |

8 PRELIMINARY

## 2.2 External Interface (2 pins)

| Symbol  | Pin | Туре | Description                                                                                                                                                                                                                                         |

|---------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFOSC  | 54  | I    | <b>Oscillator Input:</b> This signal is used to control the timing of the CL-GD6340 power sequencing circuitry. This input must be connected to a continuously running clock, usually the 14 MHz system oscillator. (MIN = 5 MHz, MAX = 14.318 MHz) |

| PWRDWN* | 92  | I    | <b>Power-Down Input:</b> When this pin is asserted low, the CL-GD6340 goes into Suspend Mode.                                                                                                                                                       |

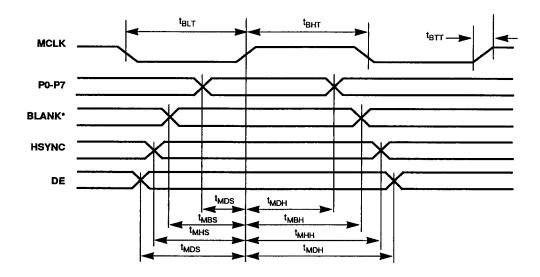

## 2.3 Graphic Controller Interface (14 pins)

| Symbol | Pin   | Туре | Description                                                                                                                                                                          |

|--------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P[7:0] | 81-88 | IC   | Pixel Data Bits [7:0]: Input from the VGA controller.                                                                                                                                |

| MCLK   | 80    | IC   | Master Clock: This is the display (pixel) clock from the VGA controller.                                                                                                             |

| BLANK* | 90    | IC   | Video Blanking Signal: When this signal is high, display on screen is enabled. When low, screen is blanked.                                                                          |

| DE     | 3     | IC   | <b>Display Enable:</b> When this signal is high, it indicates valid display data. This signal is low during overscan or retrace and pulses high for each line of non-displayed data. |

| HSYNC  | 2     | IC   | Horizontal Sync: Horizontal Sync Input.                                                                                                                                              |

| VSYNC  | 1     | IC   | Vertical Sync: Vertical Sync Input.                                                                                                                                                  |

| SENSE  | 91    | 0    | Monitor Sense Output: IBM-standard analog SENSE output<br>to the VGA controller. This signal is used for detecting monitor<br>type and presence.                                     |

October 1991

\_\_\_\_\_

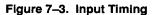

## 2.4 CRT Interface (8 pins)

| Symbol | Pin   | Туре | Description                                                                                                                                                                                                                                         |

|--------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IREF   | 97    | OA   | <b>RAMDAC Current Reference Input:</b> An external current reference must sink 6.7 mA.                                                                                                                                                              |

| Vaa    | 93    | Р    | RAMDAC Analog Power Input                                                                                                                                                                                                                           |

| GNDaa  | 98    | G    | RAMDAC Analog Ground Input                                                                                                                                                                                                                          |

| R,G,B  | 94-96 | OA   | Analog Red, Analog Green, and Analog Blue: High-imped-<br>ance PS/2-compatible current source to directly drive a doubly<br>terminated 75 ohm coaxial cable.                                                                                        |

| BHSYNC | 100   | то   | Buffered Horizontal Sync: For direct connection to an analog<br>monitor. The active polarity of this signal can be selected by Bit<br>6 of the Miscellaneous Output Register (I/O address 3C2H), or<br>Bit 6 of the Timing Control Register (ER85). |

| BVSYNC | 99    | то   | <b>Buffered Vertical Sync:</b> For direct connection to an analog monitor. The active polarity of this signal can be selected by Bit 7 of the Miscellaneous Output Register (I/O address 3C2H), or Bit 7 of the Timing Control Register (ER85).     |

## 2.5 Panel Interface (24 pins)

| Symbol      | Pin                           | Туре                                                                                                                                | Description                                                                                                                                                                                           |

|-------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BLFS        | 79                            | то                                                                                                                                  | Buffered LCD Frame Start: LCD frame start pulse indicates<br>the start of a new frame, reset of horizontal and vertical logic to<br>the first nibble of the first (of top and bottom panel) scanline. |

| BMOD        | 55                            | то                                                                                                                                  | <b>Buffered MOD:</b> Buffered Modulation (AC Inversion) is used to prevent DC polarization of LCD panels. The BMOD period is programmable. See ERD9 for details.                                      |

| PDATA[15:0] | 56-59, 61-64,<br>66-69, 71-74 | то                                                                                                                                  | Panel Data: Video data output for direct connection to LCD panels.                                                                                                                                    |

| BCLCLK      | 76                            | то                                                                                                                                  | Buffered Column Line Clock for TFT and STN panels: LCD column clock used to load column drivers with horizontal shift register data.                                                                  |

| BRLCLK      | 78                            | то                                                                                                                                  | Buffered Row Line Clock for TFT panels                                                                                                                                                                |

| BENRL/DEN   | 75                            | то                                                                                                                                  | Enable Row Line Clock for TFT panels or Display Enable                                                                                                                                                |

|             |                               | Buffered Shift Clock to Panel Shift Register: LCD line clock used to latch column segment data into the horizontal shift registers. |                                                                                                                                                                                                       |

| FPVCC       | 9                             | 0                                                                                                                                   | Power Sequence Control Bit 1 (Vcc on): TTL-level output to control flat panel logic voltage.                                                                                                          |

| FPVEE       | 10                            | 0                                                                                                                                   | Power Sequence Control Bit 0 (Vee on): TTL-level output to control flat panel back-light power and contrast voltage.                                                                                  |

October 1991

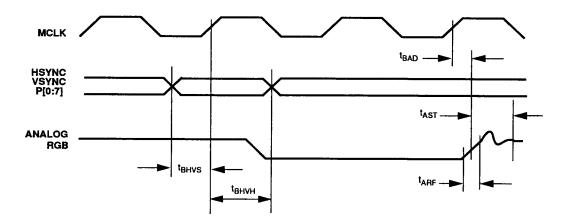

## 2.6 Frame-Accelerator Memory Interface (16 pins)

| Symbol    | Pin           | Туре | Description                                |

|-----------|---------------|------|--------------------------------------------|

| FROE*     | 37            | OC   | Frame-Accelerator Output Enable            |

| FRCAS*    | 38            | OC   | Frame-Accelerator CAS*                     |

| FRRAS*    | 39            | oc   | Frame-Accelerator RAS*                     |

| FRWE*     | 36            | OC   | Frame-Accelerator Write Enable             |

| FRAD[8:0] | 41, 42, 44-50 | I/O  | Multiplexed Frame-Accelerator Address/Data |

| FRD[11:9] | 51-53         | 1/0  | Upper three bits of data for color modes.  |

## 2.7 Power (8 pins)

| Symbol | Pin                   | Туре | Description            |

|--------|-----------------------|------|------------------------|

| vcc    | 7, 40, 65             | Р    | Three VCC pads, total. |

| GND    | 13, 43, 60,<br>70, 89 | G    | Five GND pads, total.  |

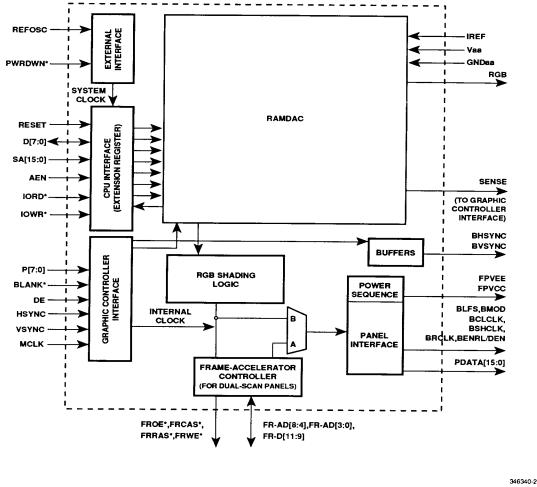

## 3. FUNCTIONAL DESCRIPTION

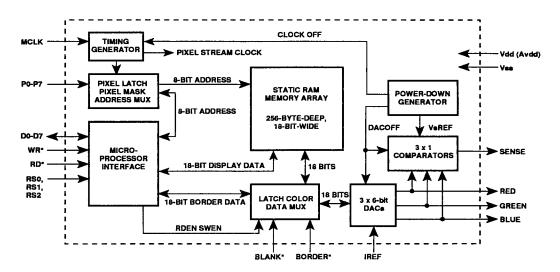

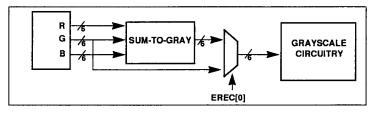

The data path in the CL-GD6340 operates as follows:

- 1) The Input P[7:0] is used to address the RAMDAC,

- 2) RAMDAC color values are modified by Stippling and Sum-to-Gray Logic, and

- 3) Output is then either stored into the Frame-Accelerator or sent to the Panel Interface Logic, which bit shuffles the data according to panel type.

The following sections discuss each item in detail.

Figure 3–1. CL-GD6340 Block Diagram

October 1991

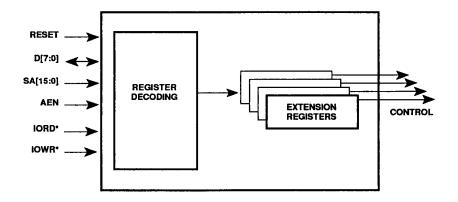

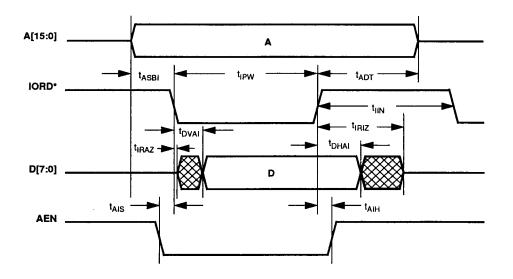

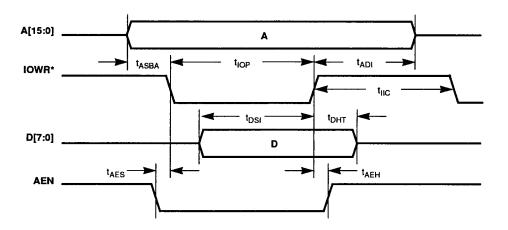

#### 3.1 CPU Interface

The CPU Interface connects the CL-GD6340 to the PC AT bus. The CPU Interface contains the signals (IORD\*, IOWR\*, AEN, SA[15:0], and Reset) required to latch information from the bus and ignore DMA transfers. The Reset Signal resets all the registers, except scratch registers, to a known default state. In addition to the above signals, a multiplexed Address/Data Bus is also needed.

There are two types of registers in the CL-GD6340: indexed and non-indexed. To read or write a nonindexed register, an I/O Read or I/O Write is sufficient. The CL-GD6340 decodes the address bits A[15:0] along with the IORD\* or IOWR\* to determine which register is to be accessed, and the direction of the data transfer.

An indexed addressing scheme is used to control access to the CL-GD6340 extension registers. In order to read or write an extension register, the desired register's index must first be written to the Extensions Index Register (ERX) with an I/O Write. Upon the next I/O Operation, the CL-GD6340 decodes the address bits A[15:0] along with IORD\* and IOWR\* to determine which register is to be accessed and which operation will be performed. If the selected register is an Extension Register, the Extensions Index Register (ERX) is used as an index into the Extension Register set.

14 PRELIMINARY

October 1991

346340-3

### 3.2 Graphic Controller Interface

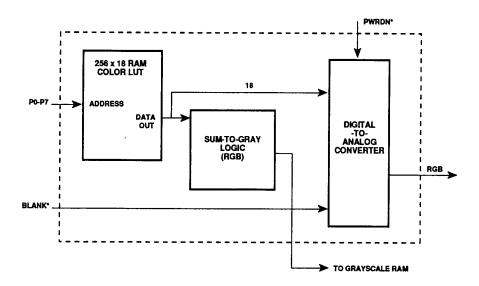

The data path is from P[7:0] through the 256 x 18 RAM. This RAM Output is then passed through the DAC (to generate RGB signals) as well as the grayscale logic. During PWRDN\* by External Pin, the R, G, and B signals become 'black', and BHSYNC and BVSYNC become tri-stated.

Figure 3–3. Graphics Controller Interface

October 1991

PRELIMINARY 15

346340-4

#### 3.3 Frame-Accelerator Controller

The CL-GD6340 includes a proprietary Frame-Accelerator to allow the VGA controller to function at half the clock rate of other controllers for a given refresh rate. The Frame-Accelerator allows the CL-GD6340 to take advantage of a dual-panel LCD configuration to refresh the entire display in half the time a screen refresh would normally take. The CL-GD6340 sends frame data to one half of the display and to Frame-Accelerator. As new data is stored in the Frame-Accelerator, the previous data is used to update the other half of the display. The Frame-Accelerator and the CL-GD6340 then switch display and accelerator responsibilities. This occurs continuously and allows faster screen refresh with power dissipated by the system.

346340-5

October 1991

Figure 3-4. Frame-Accelerator Block Diagram

The Frame-Accelerator memory must have 64K addressable locations with a width equal to four times the number of data bits associated with each pixel write cycle. Most monochrome applications require 4-bit-wide memory: one bit per pixel multiplied by four write cycles. In 8-color applications, 12 bits are needed to support four pixel writes of three data bits each (Red, Green, and Blue). Using one 64K x 16 DRAM (64K x 4 is sufficient if only monochrome dual-scan panels are to be supported) is one way to achieve a versatile solution.

The Frame-Accelerator DRAM(s) must be the same speed as Video Memory and is connected directly to the CL-GD6340 with no intervening circuitry. The Frame-Accelerator memory must support the following:

- Page Mode

- CAS precharge time of 25 ns or less

- CAS-before-RAS refresh

- RAS low time greater than the horizontal display period (see example, below)

**Worst-Case Example:** Three MHz pixel clock (BSHCLK), where the RAS (FFRAS\*) will be low for a period of 67 μsec, which is the entire LCD line display time.

RAS-low required = (Shift Clock Period)\* [(Pixels per line/Pixels per clock) +1] = 333 ns \* [(800/4) +1]

= 333 ns \* 201 = 67 us

#### 3.3.1 VGA/Panel Frame-Accelerator DRAM Combinations

| Panel Type               | Panel Operation                                                                 | Number of DRAMs                       |

|--------------------------|---------------------------------------------------------------------------------|---------------------------------------|

| Monochrome               | – Dual-Panel, Dual-Drive*<br>– Single-Panel, Single-Drive                       | One 64K x 4<br>NONE                   |

| Color<br>(Non-active)    | <ul> <li>Dual-Panel, Dual-Drive</li> <li>Single-Panel, Single-Drive*</li> </ul> | One 64K x 16 or three 64K x 4<br>NONE |

| Color<br>(Active matrix) | - Single-Panel, Single-Drive*                                                   | NONE                                  |

NOTE: (\*) indicates that the majority of system integrators use this panel.

October 1991

### 3.4 RAMDAC

The CL-GD6340 internal RAMDAC consists of a 256 x 18 RAM with three 6-bit DAC output channels. The read and write operations involving the RAMDAC are compatible with IBM VGA Palette Memory. The registers are accessed by the CPU through I/O Read/Write instructions. The RAM Register is the data register that is also accessed by I/O Read/Write instructions.

NOTE: This diagram shows the RAMDAC as an external device. Not all signals shown are available externally in the CL-GD6340.

346340-6

#### Figure 3–5. RAMDAC Block Diagram

The CL-GD6340 includes an on-chip, high-speed memory with a Digital-to-Analog Converter (RAMDAC). The RAMDAC circuitry processes the video data from the VGA controller and converts it into PS/2-compatible analog signals.

An 8-bit address value applied on the Pixel Address input defines the memory location for reading an 18bit color data word from the color lookup table. This data is partitioned as three fields of six bits each, which is applied to the individual DAC inputs.

A pixel word mask is incorporated to allow the incoming Pixel Address to be altered or masked, permitting changes to the color lookup table contents to be made immediately. This feature allows special display operations such as flashing objects and overlays to be created.

The color lookup table contents are accessed via its 8-bit-wide host interface. An internal synchronizing circuit allows the RAMDAC memory contents to be accessed during active video time without flicker.

18 PRELIMINARY

#### RAMDAC Video Operation

In video operation, pixel addresses P0 through P7, and BLANK\* are sampled on the rising edge of the pixel clock (MCLK). Their effect appears at the DAC outputs after three further rising edges of MCLK.

BLANK\* is an active-low signal. When the BLANK\* input is low, a binary '0' is applied to the DAC inputs, producing a zero-volt DAC output.

To put the DAC into a power-down state, any one of the following conditions must be true:

| Suspend   | = ERA7[4]     | = 1    |

|-----------|---------------|--------|

| Standby   | = ER8A[7]     | = 1    |

| CRT (off) | = ERF6[3]     | = 0    |

| PWRDWN*   | = External Pi | in = 0 |

When any of the above conditions is true, the DACs in the RAMDAC are totally inoperative. During this time, the three DAC channels output zero volts, which results in the power dissipation being reduced to the Standby Mode minimum. When the above conditions become false, several MCLK cycles are required before the DACs in the RAMDAC will function properly.

#### Analog Outputs

The DAC outputs are designed to produce 0.7 volt peak amplitude with a reference current ( $I_{REF}$ ) of 6.7 mA when driving a doubly terminated 75 ohm load, which corresponds to an effective DAC output load of 37.5 ohms ( $R_{effective}$ ).

#### Writing to the Color Lookup Table

To write a color definition to the lookup table, a value specifying an address location in the lookup table is first written to PELWR. The color values for the red, green, and blue intensities are then written in succession to PELDATA. After the blue data is latched, and to cause PELWR to automatically increment, this new color data is then written into the lookup table at the defined address.

Since PELWR increments after each transfer of data to the lookup table, it is best to write a set of consecutive locations with new color data. The start address of the set of locations is first written to the Write Address Mode Register. When the write is complete, the color data for each address location is then sequentially written to PELDATA. The RAMDAC automatically writes data to the lookup table and increments PELWR after each host transfer of three bytes of color data.

#### Reading from the Color Lookup Table

To read color data from the lookup table, a value specifying the address location of the data is written to PELRD. After the address is latched, the data from this location is automatically read out to the PELDATA, and PELRD automatically increments.

Color intensity values can then be read from the PELDATA by a sequence of three I/O Read (IORD\*) commands: in sequence, Red, Green, then Blue. After the Blue value is transferred out, PELRD is automatically incremented and new data is read from the lookup table from the new address and placed in PELDATA.

October 1991

Resetting Color Lookup Table Reads and Writes

If the PELWR is loaded with a new starting address while an unfinished read or write sequence is in progress, the RAMDAC aborts the current sequence and starts a new one.

#### 3.5 Analog Monitor Sense

The CL-GD6340 contains an onboard comparator that detects the voltages of the Red, Green, and Blue outputs. This comparator takes the RGB voltages from the internal DAC and compares them to a reference voltage. The result of this comparison is then placed on the SENSE output pin.

NOTE: SENSE is output only when reading address 3C2 and ERF6[5]\*(Disable Sense)\* = 0 and the DAC is not in Power-down Mode.

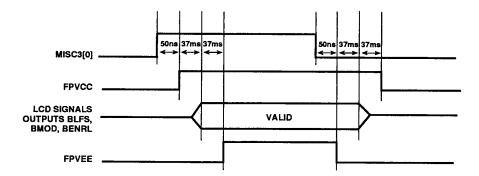

## 3.6 Panel Power Sequencing

To power-up any panel, certain signals must be presented in a specific order. The Panel Active Sequence is as follows:

- a. Logic power

- b. Signals

c. Panel drivers and backlight

NOTE: The Panel Inactive Sequence is the reverse.

Two pins are assigned to facilitate power management: FPVCC and FPVEE. These output pins from the CL-GD6340 are TTL-level outputs that are sequenced properly for LCD panels. They are intended to be used to control panel logic power, backlight and contrast voltages.

NOTE: Because the CL-GD6340 is unable to provide the high current and various voltages necessary to drive LCD panels, these outputs are intended to be used as control signals for power circuitry.

The signal FPVCC is intended to be used to activate circuitry that supplies power to the desired panel logic. The signal FPVEE is used to activate circuitry that supplies the desired contrast voltage to the panel. The following diagram shows how FPVCC is always high before and after FPVEE changes state.

Figure 3-6. Sequencing for Power and Signals

October 1991

PRELIMINARY 21

346340-7

.....

#### 3.6.1 Panel Inactive Sequence

To shut the panel off, write '0' to MISC3[0].

The CL-GD6340 then performs the following operations:

- a. Approximately 50 ns delay

- b. FPVEE transitions to a '0'

- c. Approximately 37 ms delay

- d. LCD signals become tri-state

- e. Approximately 37 ms delay

- f. FPVCC transitions to a '0'

#### 3.6.2 Panel Active Sequence

The power-on sequence is the reverse order of the Panel Inactive Sequence shown above.

To turn the panel on, write '1' to MISC3[0].

The CL-GD6340 then performs the following operations:

- a. Approximately 50 ns delay

- b. FPVCC transitions to a '1'

- c. Approximately 37 ms delay

- d. LCD signals become active

- e. Approximately 37 ms delay

- f. FPVEE transitions to a '1'

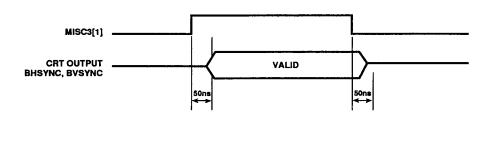

### 3.7 CRT Sequence Control

MISC3[1] is used to directly control the CRT. When MISC3[1] is a '0', BHSYNC and BVSYNC are tri-stated and RGB is blanked. When MISC3[1] is a '1', BHSYNC, BVSYNC, and RGB are output.

Figure 3-7. Sequencing for Power and Signais (cont.)

22 PRELIMINARY

October 1991

346340-8

#### 3.8 Power-Down Modes

The CL-GD6340 has multiple modes for enhanced power management. Following is a description of the various modes and their effect on the graphics subsystem.

#### Table 3–1. Power-Down Modes

| MODES                                | internal<br>Clocks | RAMDAC<br>Palette R/W | DAC   | CPU<br>I/F | Panel<br>I/F | Frame<br>Accel. | CRT<br>I/F |

|--------------------------------------|--------------------|-----------------------|-------|------------|--------------|-----------------|------------|

| Standby Mode<br>ER8A[7]              | OFF 1*             | ON                    | ON 1* | ON         | 3*           | 4*              | 3*         |

| Suspend Mode<br>ERA7[4]              | OFF                | OFF                   | OFF   | OFF        | 3*           | 4*              | 3*         |

| <b>PWRDWN*</b><br>External Pin = '0' | OFF                | OFF                   | OFF   | OFF        | OFF 2*       | OFF 2*          | OFF 2      |

#### NOTES:

This table shows conditions of the CL-GD6340 in each mode only, not in multiple modes.

- 1) MCLK is shut off internally and is supplied to RAMDAC only during RAMDAC I/O reads and writes.

- The outputs are driven to zeroes.

- Remains in previous state, determined by, ERF6[3:2] and ERA7[1:0].

- 4) If ERF2[6] (dual-scan panel) is set, this remains in previous state, determined by ERF6[2], otherwise off.

To insure the panel is not damaged and minimum power consumption in all of the above modes, the panel and CRT must be sequenced off with ERA7[1:0], SENSE must be disabled with ERF6[5], and the display type select bits ERF6[3:2] should be set to zero PRIOR to entering any power-down modes.

Entering power-down modes is accomplished by writing the correct values into Power-down Register Bits ER8A[7] or ERA7[4] or pulling the PWRDWN\* pin down.

Exiting power down modes is accomplished by writing the appropriate values into the register bits ER8A[7] or ERA7[4] or pulling the PWRDWN\* pin up. The states of ERA7[1:0] and ERF6[3:2] should be restored upon exit from power-down modes.

October 1991

#### 3.8.0.1 External Pin Power-Down Sequence

This mode is activated by forcing the PWRDWN\* Pin to '0'. This causes the CL-GD6340 to ignore any CPU access and internally forces MCLK = 1 in less than 100 ns.

**NOTE:** To prevent panel damage, the LCD panel MUST have been power-sequenced 'off' prior to 'PWRDWN\* = 0'.

Upon forcing the PWRDWN\* Pin to '0', the CL-GD6340 then causes the following to occur:

- Panel Interface outputs are forced to '0'

- · Frame-Accelerator outputs are forced to '0'

- FPVEE, FPVCC stays in previously programmed state until ERA7[0] changes state from '1' to '0'

- CRT interface outputs BHSYNC, BVSYNC, R, G, B = '0'

- SENSE outputs a '0'

- **NOTE:** Holding the Frame-Accelerator outputs low will allow the Accelerator DRAM to be totally powered-off with no resultant latchup problems or leakage current conducting through the forward-biased CMOS input protection diodes.

#### 3.8.0.2 External Power-Up Sequence

This causes the CL-GD6340 to resume operation in less than 100 ns. Activated by PWRDWN\* = '1'. The CL-GD6340 then performs the following operations:

- MCLK Input into the CL-GD6340 is enabled

- Enables Frame-Accelerator

- Enables CRT Interface

- Enables Sense

- **NOTE:** Power Sequencing is unaffected by the PWRDWN\* Pin. The display MUST be sequenced-off before power-down and sequenced-on after power-up.

For more details as to the function of specific display control bits, see ERF6[3:2] and ERA7[1:0].

For more details as to the function of specific power-down bits, see ER8A[7] or ERA7[4].

### 3.9 Sleep Mode

The CL-GD6340 responds to the sleep port at I/O location 3C3 or 46E8 depending on ERF6[7]. In either case, ER87[6] (Arm Video Subsystem) must be a '1' for the CL-GD6340 to go into Sleep Mode via the selected sleep port.

Sleep Mode shuts off CPU access (IORD and IOWR) to the CL-GD6340 registers. However, the active sleep register itself can always be written to. During reading of the sleep registers, only the selected sleep register can be read back.

The selection between the two above is determined by ERF6[7]. If set then 46E8 Register is selected as the sleep register. If reset, then 3C3 is selected as the sleep register.

|   | odes<br>1F6<br>2 | LCD<br>Dispiay | CRT<br>Display | MCLK | Panel<br>Clock | RAMDAC<br>Palette<br>R/W | DAC | CPU<br>I/F | Frame<br>Accelerator |

|---|------------------|----------------|----------------|------|----------------|--------------------------|-----|------------|----------------------|

| 0 | 0                | OFF            | OFF            | OFF  | OFF            | OFF                      | OFF | OFF        | 2                    |

| 0 | 1                | ON             | OFF            | ON   | ON             | OFF                      | OFF | OFF        | 1                    |

| 1 | 0                | OFF            | ON             | ON   | OFF            | OFF                      | ON  | OFF        | 1                    |

| 1 | 1                | ON             | ON             | ON   | ON             | OFF                      | ON  | OFF        | 1                    |

#### Table 3–2. Sleep Mode

#### NOTES:

1) On only if ERF2[6] = 1 and ERF6[2] output zeroes if ERF2[6] = 0.

2) If On (ERF2[6] = '1', dual-scan panel) then it is not toggling due to no MCLK; otherwise, Off.

## 4. VGA/EGA REGISTER TABLE

The CL-GD6340 maintains a copy of the following bits contained within standard IBM VGA registers. These bits are needed by the CL-GD6340, therefore the BIOS keeps them updated. For the function of these specific bits, please refer to the *CL-GD610/620-C Technical Reference Manual*.

| Abbreviations | Register Name                                                                             | Port               | Index | Bits         |

|---------------|-------------------------------------------------------------------------------------------|--------------------|-------|--------------|

| AR10          | Attribute Controller Mode Control<br>(Pixel Doubling Clock Select)                        | 3C0<br>(3C1)       | 10    | 6 and 0      |

| CR9           | CRTC Character Cell Height Register<br>(Scanline Doubling)                                | 3?5                | 09    | 7 and 4-0    |

| SR1<br>MODE   | Sequencer Clocking Mode Register<br>CMGA Mode Register                                    | 3C5<br>3?8         | 01    | 3 and 0<br>4 |

| GR5           | Graphics Controller Mode Register<br>Motherboard Sleep Register<br>Adapter Sleep Register | 3CF<br>3C3<br>46E8 | 05    | 6<br>0<br>3  |

| MISC          | Miscellaneous Output Register                                                             | 3C2(W)<br>3CC(R)   |       | 7, 6, and 0  |

**NOTE:** ? = 'D' hex for color and 'B' for monochrome.

26 PRELIMINARY

## 5. RAMDAC I/O PORT SUMMARY TABLE

The CL-GD6340 contains an on-chip, high-speed, VGA-compatible RAMDAC. The following table provides a summary of each register associated with RAMDAC operation and function; see the referenced pages for complete register descriptions. See Section 3.4 for a more complete description of RAMDAC functions.

| Port Address | Abbreviation    | VGA/EGA Port                               | ERF6[6] | Access     | Page     |

|--------------|-----------------|--------------------------------------------|---------|------------|----------|

| 03C6         | PELMSK          | RAMDAC Pixel Mask<br>RESERVED              | 0<br>1  | R/W        | 28       |

| 03C7         | PELRD           | RAMDAC Pixel Read Address<br>RESERVED      | 0<br>1  | w          | 29       |

| 03C8         | PELWR<br>BDRCOL | RAMDAC Pixel Write Address<br>Border Color | 0<br>1  | R/W<br>R/W | 30<br>31 |

| 03C9         | PELDATA         | RAMDAC Pixel Data<br>RESERVED              | 0<br>1  | R/W        | 32       |

#### 5.1 RAMDAC Pixel Mask: PELMSK

I/O Port Address: 3C6 (R/W) ERF6[6] = '0' Read Protection Bit: EREC[3]

| Bit    | Description      | Access | <b>Reset State</b> |

|--------|------------------|--------|--------------------|

| 7(MSB) | Pixel Mask Bit 7 | R/W    | x                  |

| 6      | Pixel Mask Bit 6 | R/W    | x                  |

| 5      | Pixel Mask Bit 5 | R/W    | x                  |

| 4      | Pixel Mask Bit 4 | R/W    | x                  |

| 3      | Pixel Mask Bit 3 | R/W    | x                  |

| 2      | Pixel Mask Bit 2 | R/W    | x                  |

| 1      | Pixel Mask Bit 1 | R/W    | x                  |

| 0      | Pixel Mask Bit 0 | R/W    | ×                  |

Bit 7-0 **Pixel Mask Bits:** This register is initialized to FFh by the BIOS when a new video mode is selected. The Pixel Mask Register can be used to mask selected bits of the Pixel Address value applied to the Pixel Address inputs P[7:0]. A '1' in any position in the Pixel Mask Register leaves that corresponding bit in the Pixel Address unaltered. A '0' in any position in the Pixel Mask Register sets that bit to zero. The Pixel Mask Register does not affect the address generated by the microprocessor interface when the LUT is being read.

NOTE: ERF6[6] must be '1' to access this register. When ERF6[6] = '0', this register is RESERVED.

28 PRELIMINARY

#### 5.2 RAMDAC Pixel Read Address: PELRD

I/O Port Address: 3C7 (W) ERF6[6] = '0'

| Bit    | Description                            | Access | <b>Reset State</b> |

|--------|----------------------------------------|--------|--------------------|

| 7(MSB) | Pixel Data Register Read Address Bit 7 | w      | x                  |

| 6      | Pixel Data Register Read Address Bit 6 | W      | x                  |

| 5      | Pixel Data Register Read Address Bit 5 | W      | ×                  |

| 4      | Pixel Data Register Read Address Bit 4 | W      | x                  |

| 3      | Pixel Data Register Read Address Bit 3 | W      | x                  |

| 2      | Pixel Data Register Read Address Bit 2 | W      | x                  |

| 1      | Pixel Data Register Read Address Bit 1 | W      | x                  |

| 0      | Pixel Data Register Read Address Bit 0 | W      | x                  |

Bit 7-0 **Pixel Data Register Read Address Bits:** The address written to this register is actually the index (00H-FFH decimal) that selects one of 256 data registers in the LUT. After an address is written to this register, three consecutive reads should be performed at the 3C9 PELDATA port. Each read will yield a color value in the six LSBs of the 8-bit PELDATA Register. The first read value being R(Red), the next G(Green), and finally B(Blue). After reading three successive color values, the PELRD register will automatically increment to the next index.

The read cycle should not be interrupted by writing to the PELDATA Register as this may affect palette RAM contents. The PELRD Register may be written at any time. If the read cycle is interrupted by another read or write request (i.e., loading either the PELRD or PELWR Registers with data), the current cycle will be aborted.

#### NOTES:

- 1) Interrupts should be disabled during RAMDAC access.

- 2) ERF6[6] must be '1' to access this register. When ERF6[6] = '0', this register is RESERVED.

- 3) Writing a value to this register specifies an address within the color LUT, and loads the data register with the contents of the location in the color LUT addressed. Then the Address Read Register increments. This normally precedes reading one or more color values from the color LUT.

October 1991

\_\_\_\_\_

#### 5.3 RAMDAC Pixel Write Address: PELWR

I/O Port Address: 3C8 (R/W) ERF6[6] = '0' Read Protection Bit: EREC[3]

| Bit    | Description                             | Access | <b>Reset State</b> |

|--------|-----------------------------------------|--------|--------------------|

| 7(MSB) | Pixel Data Register Write Address Bit 7 | R/W    | x                  |

| 6      | Pixel Data Register Write Address Bit 6 | R/W    | x                  |

| 5      | Pixel Data Register Write Address Bit 5 | R/W    | x                  |

| 4      | Pixel Data Register Write Address Bit 4 | R/W    | ×                  |

| 3      | Pixel Data Register Write Address Bit 3 | R/W    | x                  |

| 2      | Pixel Data Register Write Address Bit 2 | R/W    | x                  |

| 1      | Pixel Data Register Write Address Bit 1 | R/W    | x                  |

| 0      | Pixel Data Register Write Address Bit 0 | R/W    | ×                  |

Bit 7-0 **Pixel Data Register Write Address Bits:** The address written to this register is actually the index (00H-FFH) that selects one of 256 data registers in the LUT. After an address is written to this register, three consecutive writes should be performed at the 3C9 PELDATA port. Each 8-bit write to the PELDATA port should contain valid data in the six LSBs. The first write being R(Red), the next G(Green), and the third B(Blue). After writing three successive color values, this register will automatically increment to the next index.

# The write cycle should not be interrupted by reading the PELDATA Register as this may affect palette RAM contents. The PELWR Register may be written at any time.

If the write cycle is interrupted by another read or write request (loading either the PELRD or PELWR Registers with data), the current cycle will be aborted and will not affect the contents of the RAMDAC palette.

#### NOTES:

- 1) Interrupts should be disabled during RAMDAC access.

- 2) Writing a value to this register specifies an address within the color LUT and initializes the RAM Data Register.

- 3) These operations would normally precede writing one or more color values to the color LUT.

30 PRELIMINARY

### 5.4 RAMDAC Border Color Register: BDRCOL

I/O Port Address: 3C8 (R/W) ERF6[6] = '1' Read Protection Bit: EREC[3]

| Bit    | Description             | Access | Reset State |

|--------|-------------------------|--------|-------------|

| 7(MSB) | Border Color Data Bit 7 | R/W    | x           |

| 6      | Border Color Data Bit 6 | R/W    | x           |

| 5      | Border Color Data Bit 5 | R/W    | x           |

| 4      | Border Color Data Bit 4 | R/W    | x           |

| 3      | Border Color Data Bit 3 | R/W    | x           |

| 2      | Border Color Data Bit 2 | R/W    | x           |

| 1      | Border Color Data Bit 1 | R/W    | x           |

| 0      | Border Color Data Bit 0 | R/W    | x           |

Bit 7-0 **Border Color Data Bits:** This register controls the RAMDAC border color to the LCD panel. To modify this border color, three consecutive writes should be performed to this register. Each 8-bit write should contain valid data in the six LSBs; the first write being B(Blue), the next G(Green), and the third R(Red). Displaying the border color on the LCD panel is accomplished by setting EREB[7-4] = 6.

#### NOTES:

1) Interrupts should be disabled during RAMDAC access.

2) This register should be written to three consecutive times to change the contents of the Border Color Register; this register should *always* be written to in multiples of three.

October 1991

#### 5.5 RAMDAC Pixel Data Register: PELDATA

I/O Port Address: 3C9 (R/W) ERF6[6] = '0' Read Protection Bit: EREC[3]

| Bit    | Description               | Access | Reset State |

|--------|---------------------------|--------|-------------|

| 7(MSB) | RESERVED                  | R/W    | x           |

| 6      | RESERVED                  | R/W    | x           |

| 5      | Pixel Data Register Bit 5 | R/W    | x           |

| 4      | Pixel Data Register Bit 4 | R/W    | x           |

| 3      | Pixel Data Register Bit 3 | R/W    | x           |

| 2      | Pixel Data Register Bit 2 | R/W    | x           |

| 1      | Pixel Data Register Bit 1 | R/W    | x           |

| 0      | Pixel Data Register Bit 0 | R/W    | x           |

|        |                           |        |             |

Bit 7-6 RESERVED

Bit 5-0 **Pixel Data Register Bits:** This register contains a 6-bit value used to read/write the current RAMDAC color table entry pointed to by the address in PELRD or PELWR Address Register.

For a correct loading sequence operation, an 8-bit write containing valid data in the six LSBs must be written to the PELDATA Register three consecutive times. For a correct reading sequence operation, the PELDATA Register is read three consecutive times. The valid data is contained in the six LSBs of this register. Each value corresponds to the respective Red, Green, and Blue color components of the lookup table entry at the address pointed to by the corresponding address register.

**NOTE:** If consecutive locations of the RAMDAC palette need to be accessed, only the first one needs to be specified by loading its address in either PELWR or PELRD. At the end of an Red, Green, and Blue sequence, the value in PELWR or PELRD will be automatically incremented. The read or write sequence should not be mixed with write or read operations to the PELDATA Register. Such interruption may affect palette RAM contents.

The PELRD or PELWR Register may be written at any time. The read or write sequence to PELDATA is interrupted by another read or write request (loading enter the PELWR on PELRD Registers with data). The current cycle will be aborted and will not affect the content of the RAMDAC palette. The next read or write to PELDATA will affect the Red value of the new index.

NOTE: Successive reading or writing operations on PELDATA must be separated by at least 240 ns.

32 PRELIMINARY

-----

## 6. CL-GD6340 EXTENSION REGISTERS

The extension registers provide additional functions to the CL-GD6340 beyond the standard EGA and VGA.

| Register | Abbreviations | Register Name                            | Port | Index | Access | Page |

|----------|---------------|------------------------------------------|------|-------|--------|------|

| ERX      | -             | Extensions Index Register                | 3C4  | -     | R/W    | 34   |

| ER87     | MISC2         | Miscellaneous Control Register 2         | 3C5  | 87    | R/W    | 35   |

| ER8A     | LCDCNTLI      | LCD Control Register 1                   | 3C5  | 8A    | R/W    | 36   |

| ERA7     | MISC3         | Miscellaneous Register 3                 | 3C5  | A7    | R/W    | 37   |

| ERC2     | LCDCNTLII     | LCD Control Register 2                   | 3C5  | C2    | R/W    | 38   |

| ERCD     | RFRCLR        | Red Frame Color Register                 | 3C5  | CD    | R/W    | 39   |

| ERCE     | GFRCLR        | Green Frame Color Register               | 3C5  | CE    | R/W    | 40   |

| ERCF     | BFRCLR        | Blue Frame Color Register                | 3C5  | CF    | R/W    | 41   |

| ERD0     | COLOFF        | Column Offset Register                   | 3C5  | D0    | R/W    | 42   |

| ERD1     | PHDIS         | Panel Horizontal Displayed Register      | 3C5  | D1    | R/W    | 43   |

| ERD2     | ROWOFF        | Row Offset Register                      | 3C5  | D2    | R/W    | 44   |

| ERD3     | PRST          | Panel Row Segment Total Register         | 3C5  | D3    | R/W    | 45   |

| ERD4     | PNLCTLI       | Panel Control Register 1                 | 3C5  | D4    | R/W    | 46   |

| ERD5     | PNLCTLII      | Panel Control Register 2                 | 3C5  | D5    | R/W    | 47   |

| ERD6     | GSCNTL1       | Grayscale Control Register 1             | 3C5  | D6    | R/W    | 48   |

| ERD7     | PRLLCLK       | Programmable Retrace LLCLK Register      | 3C5  | D7    | R/W    | 49   |

| ERD9     | MOD           | Modulation (AC Inversion) Register       | 3C5  | D9    | R/W    | 50   |

| ERE0     | ENRDBK        | Enable Readback Register                 | 3C5  | E0    | R/W    | 51   |

| ERE1-E8  | VSCR0-7       | Scratch Pad Registers                    | 3C5  | E1-E8 | R/W    | 52   |

| ERE9     | VIPREV        | VIPAC Chip Revision Level Register       | 3C5  | E9    | R      | 53   |

| EREA     | PRGCL1        | Programmable CL1 Delay Register          | 3C5  | EA    | R/W    | 54   |

| EREB     | BDRCTRL       | Border Control Register                  | 3C5  | EB    | R/W    | 55   |

| EREC     | GSCF1         | Grayscale and Color Functions Register 1 | 3C5  | EC    | R/W    | 56   |

| ERED     | GSCF2         | Grayscale and Color Functions Register 2 | 3C5  | ED    | R/W    | 57   |

| EREE     | PNCTRL3       | Panel Control Register 3                 | 3C5  | EE    | R/W    | 58   |

| EREF     | PNCTRL4       | Panel Control Register 4                 | 3C5  | EF    | R/W    | 59   |

| ERF0     | VSDY          | VSYNC Delay Register                     | 3C5  | F0    | R/W    | 60   |

| ERF1     | NGRAY         | Number of Grayscales Register            | 3C5  | F1    | R/W    | 61   |

| ERF2     | PNCTRL1       | Panel Interface Control Register 1       | 3C5  | F2    | R/W    | 62   |

| ERF3     | FRDC1         | Frame Rate Duty Control Register 1       | 3C5  | F3    | R/W    | 64   |

| ERF4     | FRDC2         | Frame Rate Duty Control Register 2       | 3C5  | F4    | R/W    | 65   |

| ERF5     | PNCTRL2       | Panel Interface Control Register 2       | 3C5  | F5    | R/W    | 66   |

| ERF6     | VGAI          | VGA Interface Register                   | 3C5  | F6    | R/W    | 67   |

| ERF7-FF  |               | RESERVED                                 | 3C5  | F7-FF | R/W    | -    |

NOTE: Extensions Index Register 3C4 is also read and write enabled by EXTSEL or ALLSEL, and is read and write protected by 'sleep'.

October 1991

#### 6.1 Extensions Index Register: ERX

I/O Port Address: 3C4

Read/Write Protection Bit: EXTSEL or ALLSEL

| Bit     | Description                      | Access | <b>Reset State</b> |

|---------|----------------------------------|--------|--------------------|

| 7 (MSB) | Extensions Index Bit 7           | R/W    | 0                  |

| 6       | Extensions Index Bit 6           | R/W    | 0                  |

| 5       | Extensions Index Bit 5           | R/W    | 0                  |

| 4       | Extensions Index Bit 4           | R/W    | 0                  |

| 3       | Extensions Index Bit 3           | R/W    | 0                  |

| 2       | Sequencer/Extensions Index Bit 2 | R/W    | 0                  |

| 1       | Sequencer/Extensions Index Bit 1 | R/W    | 0                  |

| 0 (LSB) | Sequencer/Extensions Index Bit 0 | R/W    | 0                  |

Bits 7-0 Extensions Index Bits: The Sequencer/Extensions Index Register defines which registers, Sequencer Registers or CL-GD6340 Extensions Registers are accessible through 3C5. In standard IBM EGA/VGA, the three least significant bits determine the Sequencer Register to be accessed at 3C5. In the CL-GD6340, Bits 3-7 were added to allow more registers to be accessed through 3C5. In order to access the standard Sequencer Registers, Bits 3-7 should be programmed to '0'. When accessing extended registers, all eight bits are used to specify which extension register will be accessed.

34 PRELIMINARY

#### 6.2 Miscellaneous Control Register 2: MISC2

I/O Port Address: 3C5 Index: 87

Read/Write Protection Bit: EXTSEL or ALLSEL

| Bit         | Description             | Access                  | Reset State            |        |

|-------------|-------------------------|-------------------------|------------------------|--------|

| 7(MSB)      | Unused                  |                         | x                      |        |

| 6           | Arm Video Subsystem     | R/W                     | 0                      |        |

| 5           | Unused                  |                         | x                      |        |

| 4           | Unused                  |                         | x                      |        |

| 3           | Unused                  |                         | x                      |        |

| 2           | Unused                  |                         | x                      |        |

| 1           | Unused                  |                         | x                      |        |

| 0           | Unused                  |                         | x                      |        |

| Bits 7, 5-0 | Unused                  |                         |                        |        |

| Bit 6       | Arm Video Subsystem: Wh | en this bit is '1', the | active Sleep Address B | eaiste |

6 Arm Video Subsystem: When this bit is '1', the active Sleep Address Register, determined by ERF6[7], is made visible. The CL-GD6340 can be put to sleep (disable memory and I/O) by writing '1' to the active sleep port. While system is asleep, only the active sleep port will be recognized. Writing a '0' to this port will reawaken the video subsystem. Typically, an adapter video BIOS will recognize the presence of a motherboard video BIOS, put it to sleep and perform the display switch BIOS function call.

October 1991

......

### 6.3 LCD Control Register 1: LCDCNTLI

I/O Port Address: 3C5

Index: 8A

Read/Write Protection Bit: EXTSEL or ALLSEL

| Bit     | Description                                                                                                                                                                                                                                                                                                                                                  | Access                                | Reset State                       |          |