# SELF-TIMED BICMOS ECL STATIC RAM 64K (16K x 4-BIT) STRAM

PRELIMINARY IDT10496RL IDT100496RL IDT101496RL

### **FEATURES:**

- 16,384-words x 4-bit organization

- Self-Timed, with registers on inputs and latches on outputs

- Balanced Read/Write cycle time: 10/12/15 ns

- Access time: 10/12/15 ns (max.)

- · Fully compatible with ECL logic levels

- · Through-hole DIP and surface-mount packages

### **DESCRIPTION:**

The IDT10496RL, IDT100496RL and IDT101496RL are 65,536-bit high-speed BiCEMOS™ ECL static random access memories organized as 16K x 4, with inputs and outputs fully compatible with ECL levels. Clocked registers on inputs

and latches on outputs, and the self-timed write operation, provide enhanced system performance over conventional RAMs, providing easier design and improved system level cycle times.

Inputs are captured by the leading edge of an externally supplied differential clock. The small input valid window required means more marginfor system skews. Logic-to-memory propagation delay is included in device cycle time calculation, allowing this device to deliver better system performance than asynchronous SRAMs and glue logic.

Write timing is controlled internally based on the clock. Write Enable has no special requirements. The device allows balanced read and write cycle times, and reads and writes can be inserted in any order.

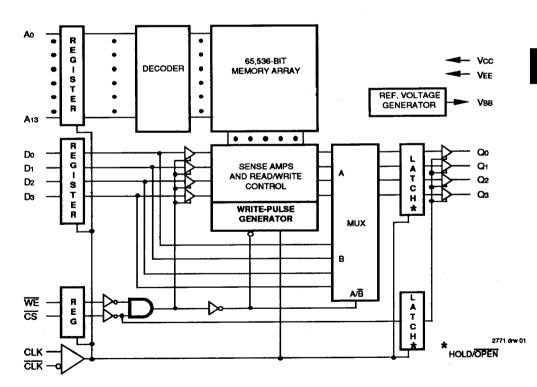

## FUNCTIONAL BLOCK DIAGRAM

BICEMOS is a trademark of integrated Device Technology, Inc.

**COMMERCIAL TEMPERATURE RANGE**

**AUGUST 1990**

© 1990 Integrated Device Technology, Inc.

5.6~

DSC-8007/1

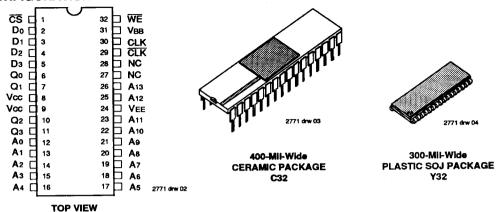

## **PIN CONFIGURATION**

## PIN DESCRIPTION

| Symbol         | Pin Name                               |

|----------------|----------------------------------------|

| Ao through A13 | Address Inputs                         |

| Do through Da  | Data Inputs                            |

| Qo through Q3  | Data Outputs                           |

| WE             | Write Enable Input                     |

| CS             | Chip Select Input (Internal pull down) |

| CLK, CLK       | Differential Clock Inputs              |

| VBB            | Reference Voltage Output (≈1.32V)      |

| VEE            | More Negative Supply Voltage           |

| Vcc            | Less Negative Supply Voltage           |

| NC             | No Connect - not internally bonded     |

| NC             | No Connect - not internally bond       |

# AC OPERATING RANGES(1)

| 10   | VEE              | Temperature                           |

|------|------------------|---------------------------------------|

| 10K  | -5.2V ±5%        | 0 TO 75°C, air flow exceeding 2 m/sec |

| 100K | -4.5V ±5%        | 0 TO 85°C, air flow exceeding 2 m/sec |

| 101K | -4.75V to -5.46V | 0 TO 75°C, air flow exceeding 2 m/sec |

| OTE  |                  | 2764 tb                               |

<sup>1.</sup> Referenced to Vcc

NOTE:

## CAPACITANCE (TA=+25°C, f=1.0MHz)

|        |                                        | D    | IP   | S    |      |            |

|--------|----------------------------------------|------|------|------|------|------------|

| Symbol | Parameter                              | Тур. | Max. | Тур. | Max. | Unit       |

| CINCLK | Input<br>Capacitance<br>CLK/CLK        | 6    | _    | 3    | -    | рF         |

| Cin    | Input<br>Capacitance<br>except CLK/CLK | 4    | -    | 3    | -    | рF         |

| COUT   | Output<br>Capacitance                  | 6    | -    | 3    | -    | рF         |

|        | · · · · · · · · · · · · · · · · · · ·  |      | -    |      |      | 2773 tbi ( |

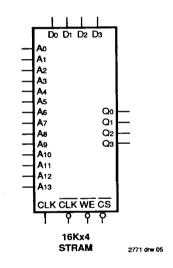

# LOGIC SYMBOL

## TRUTH TABLE(1)

| cs     | WE       | CLK                                          | DataouT(2) | Function   |

|--------|----------|----------------------------------------------|------------|------------|

| Н      | х        | t                                            | L          | Deselected |

| L      | Н        | t                                            | RAM Data   | Read       |

| L      | L        | t                                            | WRITE Data | Write      |

| IOTEO. | <u> </u> | <u> -                                   </u> |            | 2773 tbl 0 |

NOTES:

H=High, L=Low, X=Don't Care

DATAout initiated by falling edge of CLK.

# **ECL-10K ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>**

| Symbol | Ratin                                   | ng                 | Value                      | Unit       |

|--------|-----------------------------------------|--------------------|----------------------------|------------|

| VTERM  | Terminal Voltage<br>With Respect to GND |                    | +0.5 to -7.0               | V          |

| TA     | Operating Temp                          | perature           | 0 to +75                   | •c         |

| TBIAS  | Temperature Under Bias                  |                    | -55 to +125                | •c         |

| Тѕтс   | Storage<br>Temperature                  | Ceramic<br>Plastic | -65 to +150<br>-55 to +125 | °C         |

| Рт     | Power Dissipati                         | on                 | 2.0                        | W          |

| lout   | DC Output Current<br>(Output High)      |                    | -50                        | mA         |

| IOTE.  |                                         |                    |                            | 2771 tbl ( |

### NOTE:

NOTE:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **ECL-10K DC ELECTRICAL CHARACTERISTICS**

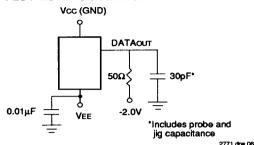

(VEE = -5.2V, RL =50 $\Omega$  to -2.0V, TA = 0 to +75°C for DIP, air flow exceeding 2 m/sec)

| Symbol | Parameter                     | Test C                                        | onditions               | Min. (B)                | Typ. <sup>(1)</sup>     | Max. (A)                | Unit                | TA                  |

|--------|-------------------------------|-----------------------------------------------|-------------------------|-------------------------|-------------------------|-------------------------|---------------------|---------------------|

| Vон    | Output HIGH Voltage           | V IN = V IHA O                                | -1000<br>-960<br>-900   | -885                    | -840<br>-810<br>-720    | mV                      | 0°C<br>25°C<br>75°C |                     |

| Vol    | Output LOW Voltage            | V IN = V IHA O                                | -1870<br>-1850<br>-1830 | -                       | -1665<br>-1650<br>-1625 | m∨                      | 0°C<br>25°C<br>75°C |                     |

| Vонс   | Output Threshold HIGH Voltage | V IN = V IHB O                                | -1020<br>-980<br>-920   | _                       | -                       | mV                      | 0°C<br>25°C<br>75°C |                     |

| Volc   | Output Threshold LOW Voltage  | V IN = V IHB O                                | -                       | _                       | -1645<br>-1630<br>-1605 | m∨                      | 0°C<br>25°C<br>75°C |                     |

| ViH    | Input HIGH Voltage            | Guaranteed I<br>High for All Ir               | -1145<br>-1105<br>-1045 | _                       | -840<br>-810<br>-720    | mV                      | 0°C<br>25°C<br>75°C |                     |

| VIL    | Input LOW Voltage             | Guaranteed I<br>Low for All In                |                         | -1870<br>-1850<br>-1830 | _                       | -1490<br>-1475<br>-1450 | m∨                  | 0°C<br>25°C<br>75°C |

| Liн    | Input HIGH Current            | V IN = V IHA                                  | cs                      | T -                     | _                       | 220                     | μА                  | -                   |

|        |                               |                                               | Others                  | T -                     |                         | 110                     | μА                  | ]                   |

| l IL   | Input LOW Current             | VIN = VILB                                    | CS                      | 0.5                     | -                       | 170                     | μА                  | -                   |

|        |                               |                                               | Others                  | -50                     | _                       | 90                      | μA                  |                     |

| IEE    | Supply Current                | All Inputs and Outputs<br>Open <sup>(2)</sup> |                         | -260                    | -200                    | -                       | mA                  | -                   |

### NOTES:

Typical parameters are specified at VEE = -5.2V, TA = +25°C and maximum loading.

Except CLK and CLK, one of which is tied low and one is tied high.

# **ECL-100K ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>**

| Symbol | Ratir                              | ng           | Value       | Unit |

|--------|------------------------------------|--------------|-------------|------|

| VTERM  | Terminal Voltag<br>With Respect to | +0.5 to -7.0 | ٧           |      |

| TA     | Operating Temp                     | perature     | 0 to +85    | °C   |

| TBIAS  | Temperature U                      | nder Bias    | -55 to +125 | °C   |

| Тѕтс   | Storage<br>Temperature             |              |             | °C   |

| Рт     | Power Dissipati                    | on           | 2.0         | W    |

| lout   | DC Output Current<br>(Output High) |              | -50         | mA   |

### NOTE:

27/110/0/

## **ECL-100K DC ELECTRICAL CHARACTERISTICS**

(VEE = -4.5V, RL =50 $\Omega$  to -2.0V, TA = 0 to +85°C, air flow exceeding 2 m/sec)

| Symbol | Parameter                     | Test C                                                        | onditions | Min. (B) | Typ.(1)  | Max. (A) | Unit |

|--------|-------------------------------|---------------------------------------------------------------|-----------|----------|----------|----------|------|

| Vон    | Output HIGH Voltage           | V IN = V IHA OI                                               | r VILB    | -1025    | -955     | -880     | mV   |

| VOL    | Output LOW Voltage            | V IN = V IHA O                                                | V ILB     | -1810    | -1715    | -1620    | mV   |

| Vонс   | Output Threshold HIGH Voltage | V IN = V IHB O                                                | r VILA    | -1035    | -        |          | mV   |

| Volc   | Output Threshold LOW Voltage  | V IN = V IHB OI                                               | VILA      | -        |          | -1610    | mV   |

| VIH    | Input HIGH Voltage            | Guaranteed I<br>High for All In                               |           | -1165    | _        | -880     | mV   |

| VIL    | Input LOW Voltage             | Guaranteed Input Voltage<br>Low for All Inputs <sup>(2)</sup> |           | -1810    | <u> </u> | -1475    | mV   |

| I #4   | Input HIGH Current            | V IN = V IHA                                                  | cs        | -        | _        | 220      | μА   |

|        |                               | · ·                                                           | Others    | _        | -        | 110      | ]    |

| I IL   | Input LOW Current             | VIN = VILB                                                    | cs        | 0.5      | _        | 170      | μА   |

|        | <b>!</b> .                    |                                                               | Others    | -50      | -        | 90       | 1    |

| IEE    | Supply Current                | All Inputs and Outputs<br>Open <sup>(2)</sup>                 |           | -240     | -180     | _        | mA   |

NOTES:

2. Except CLK and CLK, one of which is tied low and one is tied high.

2771 tbl 08

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

<sup>1.</sup> Typical parameters are specified at VEE = -4.5V, TA = +25°C and maximum loading.

# **ECL-101K ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>**

| Ratio                              | ng                                                                                                                                | Value                                                   | Unit                                                                                                                                                                                                                                  |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                    | +0.5 to -7.0                                                                                                                      | ٧                                                       |                                                                                                                                                                                                                                       |

| Operating Tem                      | perature                                                                                                                          | 0 to +75                                                | •¢                                                                                                                                                                                                                                    |

| Temperature U                      | nder Bias                                                                                                                         | -55 to +125                                             | •c                                                                                                                                                                                                                                    |

| Storage<br>Temperature             |                                                                                                                                   |                                                         | °C                                                                                                                                                                                                                                    |

| Power Dissipat                     | ion                                                                                                                               | 2.0                                                     | W                                                                                                                                                                                                                                     |

| DC Output Current<br>(Output High) |                                                                                                                                   | -50                                                     | mA                                                                                                                                                                                                                                    |

|                                    | Terminal Voltag<br>With Respect to<br>Operating Tem<br>Temperature U<br>Storage<br>Temperature<br>Power Dissipat<br>DC Output Cur | Temperature Plastic Power Dissipation DC Output Current | Terminal Voltage With Respect to GND  Operating Temperature Temperature Under Bias Storage Temperature Plastic Power Dissipation  DC Output Current  +0.5 to -7.0  to +75  Ceramic Plastic -55 to +125  -55 to +125  -55 to +125  -50 |

NOTE:

## **ECL-101K DC ELECTRICAL CHARACTERISTICS**

(VEE = -5.2V, RL =50 $\Omega$  to -2.0V, TA = 0 to +75°C for DIP, air flow exceeding 2 m/sec)

| Symbol | Parameter                     | Test C                                                        | onditions | Min. (B) | Typ. <sup>(1)</sup> | Max. (A) | Unit |

|--------|-------------------------------|---------------------------------------------------------------|-----------|----------|---------------------|----------|------|

| VOH .  | Output HIGH Voltage           | V IN = V IHA O                                                | r VILB    | -1025    | -955                | -880     | m۷   |

| VOL    | Output LOW Voltage            | VIN = VIHA O                                                  | r VILB    | -1810    | -1715               | -1620    | m۷   |

| Vohc   | Output Threshold HIGH Voltage | V IN = V IHB O                                                | r VILA    | -1035    | -                   | -        | m۷   |

| Volc   | Output Threshold LOW Voltage  | V IN = V IHB O                                                | r VILA    | -        | -                   | -1610    | m۷   |

| VIH    | Input HIGH Voltage            | Guaranteed I<br>High for All Ir                               |           | -1165    | <del>-</del> .      | -880     | mV   |

| VIL    | Input LOW Voltage             | Guaranteed Input Voltage<br>Low for All Inputs <sup>(2)</sup> |           | -1810    | _                   | -1475    | mV   |

| 1 114  | Input HIGH Current            | V IN = V IHA                                                  | <u>cs</u> | _        | -                   | 220      | μА   |

|        |                               |                                                               | Others    | _        | -                   | 110      | 1    |

| l IL   | Input LOW Current             | V IN = V ILB                                                  | cs        | 0.5      | -                   | 170      | μА   |

|        | •                             |                                                               | Others    | -50      | _                   | 90       | 1    |

| lee    | Supply Current                | All Inputs and Outputs<br>Open <sup>(2)</sup>                 |           | -260     | -200                | -        | mA   |

NOTES:

<sup>1.</sup> Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

<sup>1.</sup> Typical parameters are specified at VEE = -5.2V, TA = +25°C and maximum loading.

2. Except CLK and CLK, one of which is tied low and one is tied high.

## **AC TEST LOAD CONDITION**

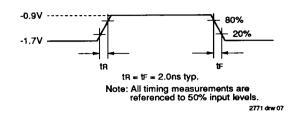

## **AC TEST INPUT PULSE**

### **RISE/FALL TIME**

| Symbol | Parameter        | Test Condition | Min. | Тур. | Max. | Unit     |

|--------|------------------|----------------|------|------|------|----------|

| tR     | Output Rise Time |                | -    | 2    | 1    | ns       |

| tF     | Output Fall Time | _              | -    | 2    | 1    | ns       |

|        |                  |                |      |      |      | 0774 614 |

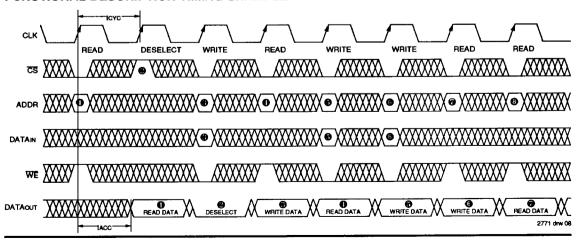

### **FUNCTIONAL DESCRIPTION**

The IDT10496RL, IDT100496RL and IDT101496RL Self-Timed BiCMOS ECL static RAMs (STRAM) provide high speed with low power dissipation typical of BiCMOS ECL. On-chip logic additionally helps improve system performance. The ECL-101K meets electrical specifications that combine the ECL-100K temperature and voltage compensated output levels with the high-speed of ECL-10K VEE compatibility (-5.2V).

As can be seen in the Functional Block Diagram on the title page, this device contains clocked input registers to sample and hold addresses, input data, and control status. Inputs are sampled on the rising edge of the clock (CLK) input (falling edge of  $\overline{\text{CLK}}$ ). In the case of a write cycle, the memory cell is written during the clock-high time, and write data conducted to

the outputs. Output data flows out the output latch and is held into the next cycle.

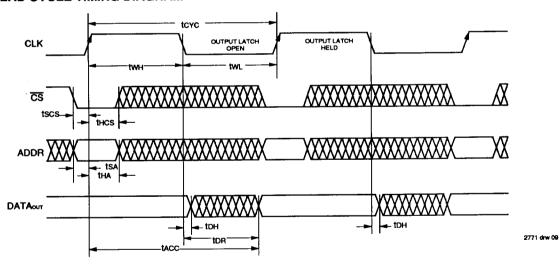

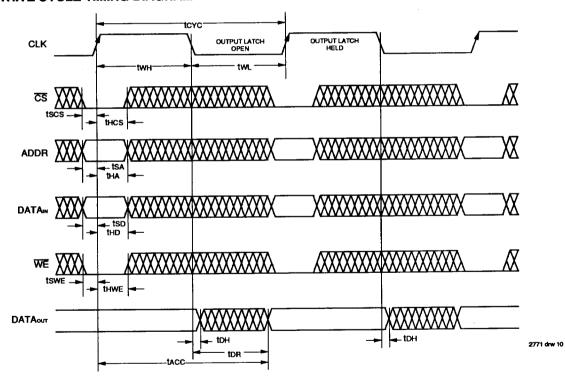

### **READ TIMING**

In a typical read cycle, the read address is captured by the rising edge of clock, as at **1** below. Then, when clock goes low, the read data for the read address clocked in at **1** is gated through the output latch to the output pins. There is a short delay from falling clock to output ready, called ton (see Read Cycle Timing). If the clock-high time (twH) is shorter than the inherent access-time of the cell, output is guaranteed valid after the specified tacc. But if twH is longer than the cell access-time, output data will be valid ton after clock goes low. Thus, the time it takes from clock-to-output for any given

### **FUNCTIONAL DESCRIPTION TIMING EXAMPLE**

5.6~6

address (the latency, or tACC) is tACC = tACC or (tWH + tDR),

whichever is larger.

The output latch takes some time to change state for the next cycle, but this time is very short. Therefore, data hold time from clock low (tDH) is specified as zero minimum hold time.

### **DESELECT TIMING**

Because the outputs are latched, they will continue to drive the output pins until a disable state is clocked through the device. The deselected state is achieved by de-asserting chip select (CS high) at rising edge of clock. This case occurs at below. Outputs then attain the disable state (low) tACC later. Status of other inputs do not effect the disabling of the device when chip select is de-asserted with the proper relation to clock.

### **WRITE TIMING**

Write cycles are identical to read cycles, except that write enable and write data need also be supplied, with the appropriate setup and hold timing. The device has on-chip timing that handles all aspects of writing data into the addressed RAM cell without the need for external write-pulse generation. The timing logic uses the clock-high time as the write pulse, and thus determines the minimum clock-high time, twH.

In addition to writing to the RAM cell, the write data is fed to the output register by a multiplexer, so that write data is available on the output pins in the appropriate time slot (i.e. after tw++tpR). This function is sometimes called "Transparent Write," and is useful for write-through cache applications. Thus the input data sampled at  $\Theta$  is available on the output at the end of the cycle.

There are no restrictions on the order of read cycles and write cycles.

AC ELECTRICAL CHARACTERISTICS (Over the AC Operating Range)

|                     |                             | Test      | 10496RL10<br>100496RL10<br>101496RL10 |      | 10496RL12<br>100496RL12<br>101496RL12 |      | 10496RL15<br>100496RL15<br>101496RL15 |          |          |

|---------------------|-----------------------------|-----------|---------------------------------------|------|---------------------------------------|------|---------------------------------------|----------|----------|

| Symbol              | Parameter <sup>(1)</sup>    | Condition | Min.                                  | Max. | Min.                                  | Max. | Min.                                  | Max.     | Unit     |

| Read Cyck           |                             |           |                                       |      |                                       |      |                                       |          |          |

| tcyc                | Cycle Time                  | _         | 10                                    | _    | 12                                    | _    | 15                                    |          | ns       |

| tacc <sup>(2)</sup> | Access Time from Clock High | _         | _                                     | 10   | -                                     | 12   |                                       | 15       | ns       |

| tWL                 | Clock Low Pulse Width       | _         | 5                                     | -    | 5                                     |      | 6                                     |          | ns       |

| twn                 | Clock High Pulse Width      | _         | 5                                     | -    | 5                                     |      | 6                                     |          | ns       |

| tscs                | Setup Time for Chip Select  | -         | 1                                     | -    | 1                                     |      | 1                                     |          | ns       |

| tsa                 | Setup Time for Address      | _         | 1                                     | -    | 1                                     | _    | 1                                     |          | ns       |

| tHCS                | Hold Time for Chip Select   | _         | 2                                     | -    | 2.5                                   | _    | 2.5                                   | <u> </u> | ns       |

| tha                 | Hold Time for Address       | _         | 2                                     | _    | 2.5                                   | -    | 2.5                                   | -        | ns       |

| tDH                 | Data Hold from Clock Low    | _         | 2                                     | -    | 2                                     |      | 2                                     |          | ns       |

| ton                 | Data Ready from Clock Low   | _         | 0                                     | 5    | 0                                     | 5    | 0                                     | 5        | ns       |

| IOTEC:              |                             |           |                                       |      |                                       |      |                                       |          | 2771 tbl |

NOTES:

1. Input and Output reference level is 50% point of waveform.

2. Access time is the larger of tACC or tWH + IDR.

## **READ CYCLE TIMING DIAGRAM**

## AC ELECTRICAL CHARACTERISTICS (Over the AC Operating Range)

| Symbol     | Parameter <sup>(1)</sup>    | Test<br>Condition | 10496RL10<br>100496RL10<br>101496RL10 |      | 10496RL12<br>100496RL12<br>101496RL12 |      | 10496RL15<br>100496RL15<br>101496RL15 |          |                   |

|------------|-----------------------------|-------------------|---------------------------------------|------|---------------------------------------|------|---------------------------------------|----------|-------------------|

|            |                             |                   | Min.                                  | Max. | Min.                                  | Max. | Min.                                  | Max.     | Unit              |

| Write Cyck | (2)                         |                   |                                       |      |                                       |      |                                       |          |                   |

| tswe       | Setup Time for Write Enable | -                 | 1                                     | -    | 1                                     |      | 1                                     |          | ns                |

| tSD        | Setup Time for Data In      | -                 | 1                                     | -    | 1                                     |      | 11                                    |          | ns                |

| tHWE       | Hold Time for Write Enable  |                   | 2                                     |      | 2.5                                   | -    | 2.5                                   | <u> </u> | ns                |

| tHD        | Hold Time for Data In       |                   | 2                                     | _    | 2.5                                   |      | 2.5                                   |          | ns<br>2771 thi 12 |

NOTES:

1. Input and Output reference level is 50% point of waveform.

## WRITE CYCLE TIMING DIAGRAM

<sup>2.</sup> All Setup, Hold, and Access timing are the same as the Read Cycle with the addition of above requirements. Write Data appears on output pins after falling edge of clock.

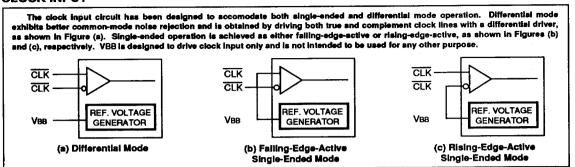

## **CLOCK INPUT**

2771 drw 11

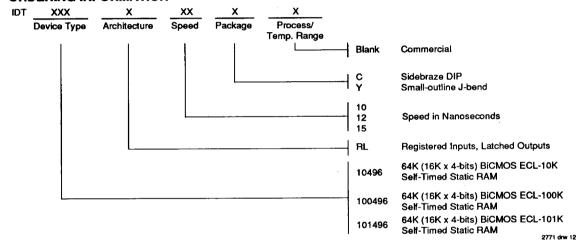

### ORDERING INFORMATION