|     | REVISIONS                                                                                                |          |          |

|-----|----------------------------------------------------------------------------------------------------------|----------|----------|

| LTR | DESCRIPTION                                                                                              | DATE     | APPROVED |

| А   | Change drawing CAGE number to 67268<br>and add a vendor CAGE no. 66958.<br>Editorial changes throughout. | 6 NOV 87 | RREvous  |

## **CURRENT CAGE CODE 67268**

| REV                          | 1 1 1       | 1. | .11 | i     |     |        |    |     |      |    |     |    | l  |    | Ц.  |     | <u>.                                    </u> |      | <u> </u> |     |       |       | L   |     |    | -   | _    |

|------------------------------|-------------|----|-----|-------|-----|--------|----|-----|------|----|-----|----|----|----|-----|-----|----------------------------------------------|------|----------|-----|-------|-------|-----|-----|----|-----|------|

| PAGE                         |             | Т  |     |       |     |        |    |     |      |    |     |    |    |    |     |     |                                              |      | L        |     |       |       |     | Щ   |    |     |      |

| REV STATUS                   | REV         | Α  | Α   | Α     |     | Α      | Α  | Α   | Α    | Α  |     |    |    |    |     |     |                                              |      | Α        | Α   | Α     | Α     | Α   |     |    |     |      |

| OF PAGES                     | PAGES       | 1  | 2   | 3     | 4   | 5      | 6  | 7   | 8    | 9  | 10  | 11 | 12 | 13 | 14  | 15  | 16                                           | 17   | 18       | 19  | 20    | 21    | 22  |     |    |     |      |

| Defense Elec<br>Supply Cente | r           |    | PRI | - ' , | RE  | 1      | Đ) |     | · 6! | ્ય | 1 \ |    |    |    |     | his | dra<br>epar                                  | win  | g is     | ava | ailal | ole ' | for | use | by |     |      |

| Dayton, Ohio                 |             |    | SH  | EC)   | KED |        | Y  | _ ! | S    | _  |     |    |    |    |     |     | of I                                         |      |          |     |       |       |     |     |    |     |      |

| Original date of drawing:    |             |    | 47  |       |     | $\neg$ | 8  | 7   | 1    | -· |     |    |    | ٦  | ΓIT | LE: |                                              | ·CH/ | ANNI     |     | SÍI   | LIC   | ON  | GAT | Ε, | SEF | RIAL |

| 16 July 19                   | 186         |    | SIZ | _     |     | CO     |    | 49  | 33   | T. | NO  | •  |    | D١ | wg  | N   | O·<br>·                                      | 59   | 62       | - 8 | 155   | 518   | 3   |     |    |     |      |

| AMSC N/A                     |             |    | RE  | V     | Α   |        |    |     |      |    |     |    |    |    |     | 1   | PAG                                          | E    |          | 1   | C     | F     |     | 22  |    |     |      |

|                              | <del></del> |    |     |       |     |        |    |     |      |    | Ā   |    |    |    |     |     |                                              |      |          |     |       |       | -   |     | Ę  | 962 | 2-E6 |

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

DESC FORM 193

- 1. SCOPE

- 1.1 Scope. This drawing describes device requirements for class B microcircuits in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices".

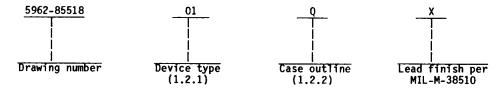

- 1.2 Part number. The complete part number shall be as shown in the following example:

1.2.1  $\underline{\text{Device types}}$ . The device types shall identify the circuit function as follows:

| Device type | Generic number | Frequency | Circuit                          |

|-------------|----------------|-----------|----------------------------------|

| 01          | Z8030A         | 6.0 MHz   | Serial communications controller |

| 02          | Z8030          | 4.0 MHz   | Serial communications controller |

1.2.2  $\underline{\text{Case outlines}}$ . The case outlines shall be as designated in appendix C of MIL-M-38510, and as follows:

# Outline letter Q D-5 (40-lead, 9/16" x 2"), dual-in-line package Y C-5 (44-terminal, .650" x .650"), square chip carrier package

1.3 Absolute maximum ratings.

| V <sub>CC</sub> supply voltage range (referenced to ground) Voltage on any pin (referenced to ground) | -0.3 V dc to +7.0 V dc<br>-0.3 V dc to +7.0 V dc |

|-------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Storage temperature range Maximum power dissipation:                                                  | -65°C to +150°C                                  |

| At -55°C                                                                                              | 2.0 W                                            |

| Lead temperature (soldering, 10 seconds) Maximum junction temperature (T):                            | +270°C                                           |

| Maximum junction temperature (T <sub>J</sub> ): _At T <sub>C</sub> = +125 C                           | +161°C                                           |

| Thermal resistance, junction-to-case (O <sub>JC</sub> ):<br>Cases Q and Y                             | (See MIL-M-38510, appendix C)                    |

|                                                                                                       |                                                  |

1.4 Recommended operating conditions.

| The state of the s |                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4.5 V dc minimum to 5.5 V dc maximum                    |

| Minimum high level input voltage $(V_{TH})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.2 V dc                                                |

| Minimum high level input voltage ( $V_{IH}$ ) Maximum low level input voltage ( $V_{IL}$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.8 V dc                                                |

| Frequency of operation:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                         |

| Device type 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0.5 MHz to 6.0 MHz                                      |

| Device type 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0.5 MHz to 4.0 MHz                                      |

| Device type 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -55°C to +125°C                                         |

| Device type 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15 ns maximum rise, 10 ns maximum fall<br>20 ns maximum |

| MILITARY DRAWING                  | SIZE |          | DWG NO | ).          |   |  |

|-----------------------------------|------|----------|--------|-------------|---|--|

| DEFENSE ELECTRONICS SUPPLY CENTER | A    |          | 59     | 62-85518    |   |  |

| DAYTON, OHIO                      |      | REV      |        | PAGE        | 2 |  |

| DESC FORM 193A                    |      | <u> </u> |        | <del></del> |   |  |

2.1 <u>Government specification and standard</u>. Unless otherwise specified, the following specification and standard, of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

#### **SPECIFICATION**

MILITARY

MIL-M-38510

Microcircuits, General Specification for.

STANDARD

MILITARY

MIL-STD-883

Test Methods and Procedures for Microelectronics.

(Copies of the specification and standard required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

2.2 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

#### 3. REQUIREMENTS

- 3.1 Item requirements. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein.

- 3.2 <u>Design</u>, construction, and physical dimensions. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 and herein.

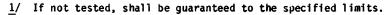

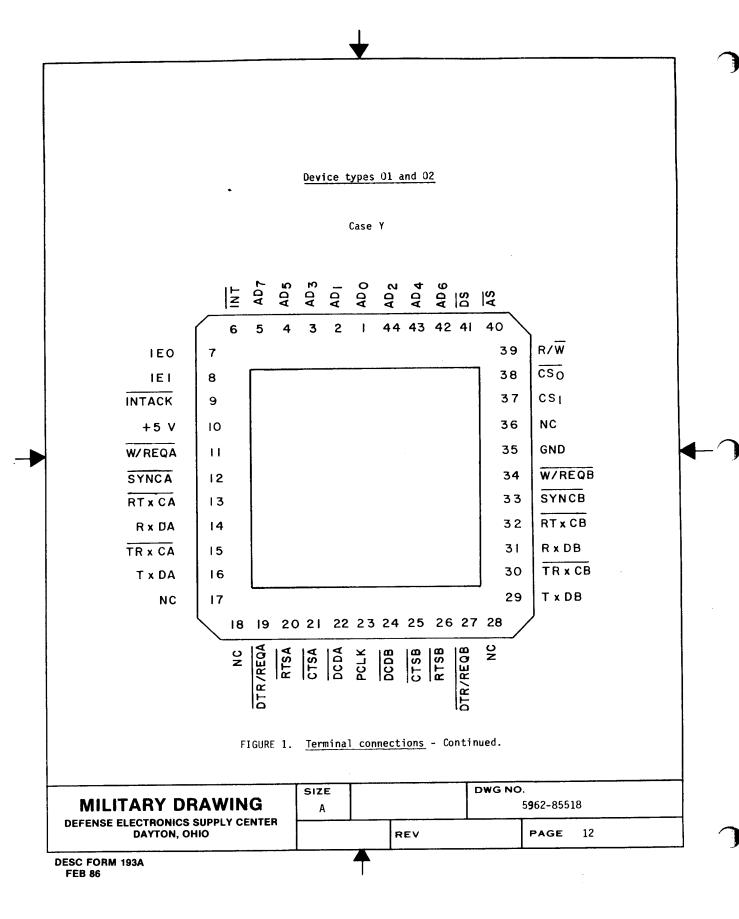

- 3.2.1 Terminal connections. The terminal connections shall be as specified on figure 1.

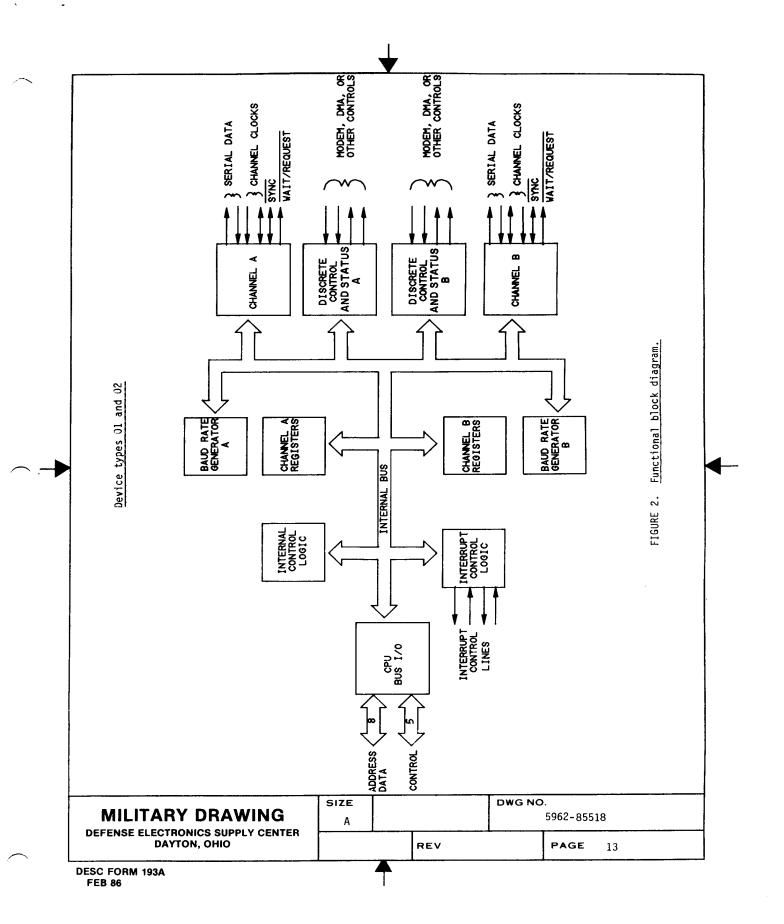

- 3.2.2 Block diagram. The block diagram shall be as specified on figure 2.

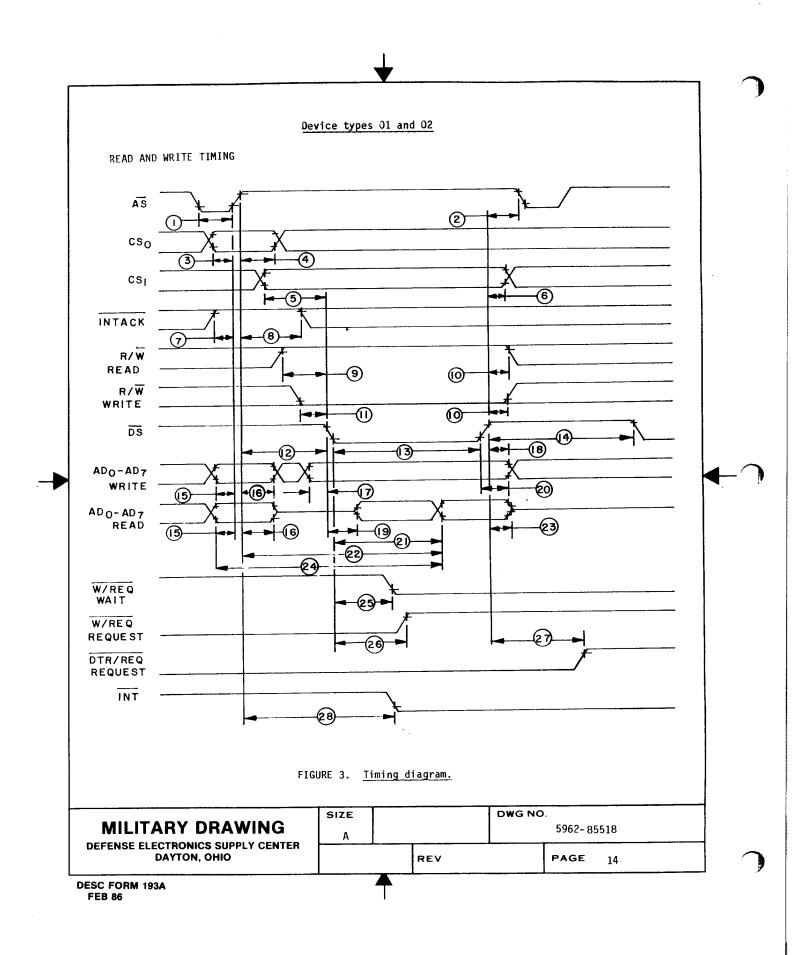

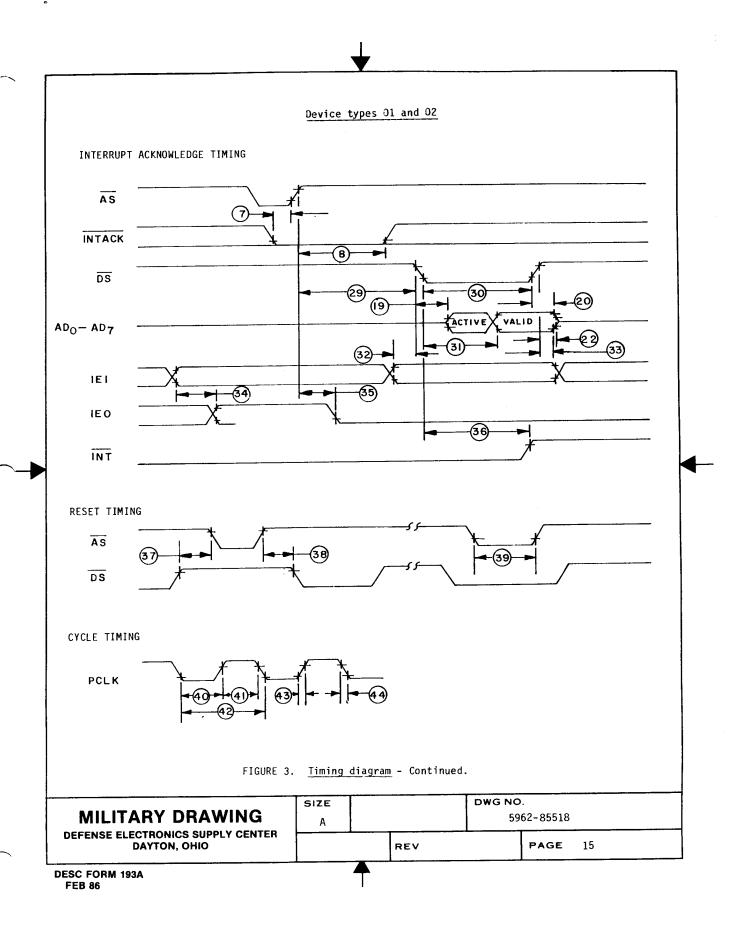

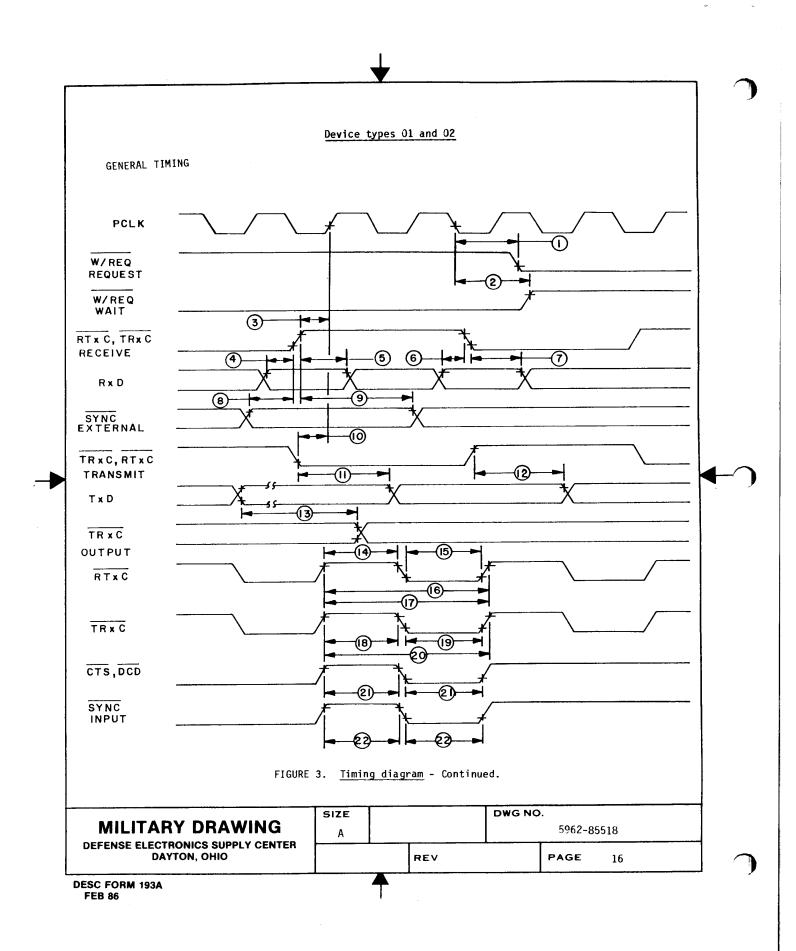

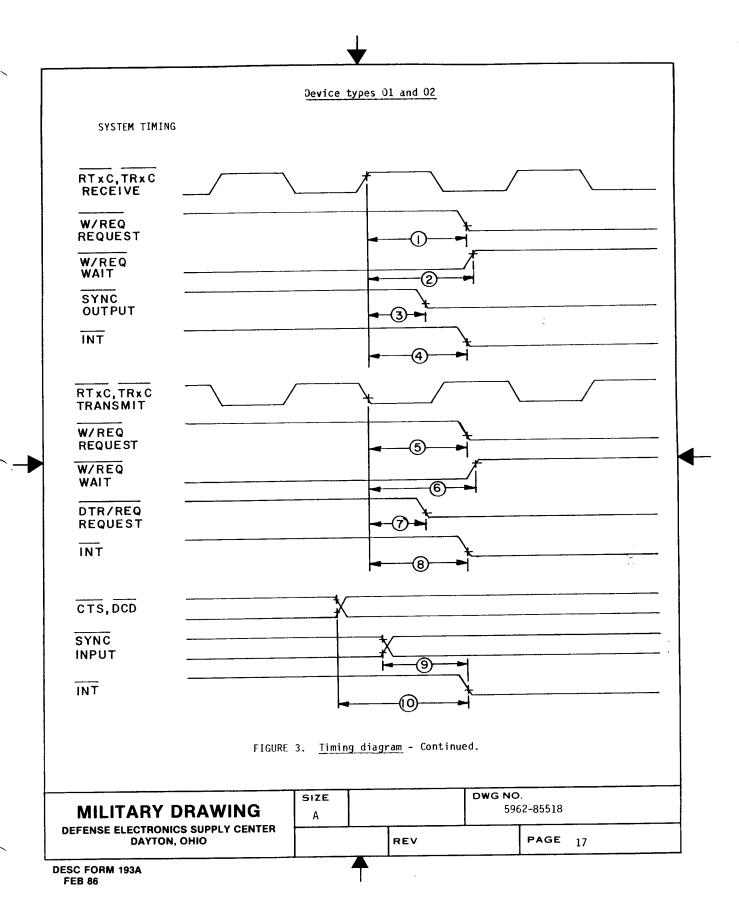

- 3.2.3 <u>Timing diagram</u>. The timing diagram shall be as specified on figure 3.

- 3.2.4 Case outlines. The case outlines shall be in accordance with 1.2.2 herein.

- 3.3 <u>Electrical performance characteristics</u>. Unless otherwise specified, the electrical performance characteristics are as specified in table I and apply over the full recommended case operating temperature range.

- 3.4 Marking. Marking shall be in accordance with MIL-STD-883 (see 3.1 herein). The part shall be marked with the part number listed in 1.2 herein. In addition, the manufacturer's part number may also be marked as listed in 6.5 herein.

| MILITARY DRAWING                               | SIZE<br>A |     |   | DWG NO | )<br>962-85518 | - |

|------------------------------------------------|-----------|-----|---|--------|----------------|---|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO |           | REV | A |        | PAGE           | 3 |

| Test                           | Symbol          | Conditions                                                                                                      |                     | Device   | Lim            | its            | Unit       |

|--------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------|---------------------|----------|----------------|----------------|------------|

|                                |                 | $ -55^{\circ}C \le T_{C} \le +125^{\circ}C$<br>$ V_{CC} = 5.0^{\circ}V \pm 10\%$<br> unless otherwise specified | subgroups<br> <br>  | type<br> | Min            | Max            | T<br>I     |

| High input voltage             | VIH             | <br>                                                                                                            | 1, 2, 3             | l ALL    | 2.2            | $V_{CC}^{1/2}$ | ٧          |

| Low input voltage              | V <sub>IL</sub> |                                                                                                                 | 1, 2, 3             | ALL      | 1/<br>  -0.3   | +0.8           | ٧          |

| Low output voltage             | VOL             | I <sub>OL</sub> = 2.0 mA                                                                                        | 1, 2, 3             | ALL      |                | +0.4           | ٧          |

| High output voltage            | VOH             | I <sub>OH</sub> = -250 μA                                                                                       | 1, 2, 3             | ALL      | +2.4           |                | ٧          |

| Power supply current           | Icc             |                                                                                                                 | 1, 2, 3             | ALL      | <br> <br> <br> | 350            | mA         |

| Output leakage current<br>low  | ILOL            | Y <sub>IN</sub> = 0.4 Y                                                                                         | 1, 2, 3             | ALL      | -10            | +10            | μА         |

| Output leakage current<br>high | ILOH            | V <sub>IN</sub> = 2.4 V                                                                                         | 1, 2, 3             | ALL      | <br> -10<br>   | <br>  +10      | μА         |

| Input low current              | IIL             | <br> Y <sub>IN</sub> = 0.4 V                                                                                    | 1, 2, 3             | ALL      | <br> -10<br>   | +10            | μА         |

| Input high current             | IIH             | <br> V <sub>IN</sub> = 2.4 V                                                                                    | <br>  1, 2, 3  <br> | ALL      | <br> -10<br>   | +10            | μА         |

| Maximum frequency <u>1</u> /   | FMAX            |                                                                                                                 | <br> 9, 10, 11 <br> | 01<br>02 | 6.0<br>4.0     |                | MHz<br>MHz |

| Input capacitance              | CIN             |                                                                                                                 | 4                   | ALL      |                | 10 <u>1</u> /  | pF         |

| Output capacitance             | COUT            |                                                                                                                 | 4                   | ALL      |                | 15 <u>1</u> /  | pF         |

| Bidirectional<br>capacitance   | c1/0            |                                                                                                                 | 4                   | ALL      |                | 20 1/          | рF         |

| ee footnotes at end of to      | able.           |                                                                                                                 | <u> </u>            |          | <u> </u>       | <u> </u>       |            |

|                                |                 |                                                                                                                 |                     |          |                |                |            |

|                                |                 |                                                                                                                 |                     |          |                |                |            |

|                                |                 |                                                                                                                 |                     |          |                |                |            |

REV

5962-85518

PAGE

4

DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO

| Toot                                                    | Combal              | Conditions                                                                                            | 10            |             |    |                      |                 |                | type                      |             |               |

|---------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------|---------------|-------------|----|----------------------|-----------------|----------------|---------------------------|-------------|---------------|

| Test                                                    | Symbol              | $1 -55^{\circ}C \le T_{C} \le +125^{\circ}C$<br>$1 V_{CC} - 5.0 V \pm 10\%$<br>[unless otherwise spec | lsu           | oup<br>bgro |    | Refer-<br>  ence<br> | Ť               | T              | 02<br>Min                 |             | Nnit<br> <br> |

| AS low width                                            |                     | l<br> See figure 3                                                                                    | <br> 9,       | 10,         | 11 | l<br>1               | l<br>I 50       | 1              | <br>  70                  | <br>        | l<br>Ins      |

| $\overline{DS}$ + to $\overline{AS}$ $^{\dagger}$ deTay | <br> TdDS(AS)       | 「C <sub>L =</sub> 50 pF ±10%<br>_unless otherwise spec                                                | T             |             |    |                      | 25              |                | 50                        |             | l ns          |

| CS <sub>0</sub> to AS + 1/2/<br>setup time              | TsCSO(AS)           | <br>                                                                                                  | 9,            | 10,         | 11 | <br>  3<br>          | 0               | <br> <br>      | 0                         |             | l<br>ns       |

| CS <sub>0</sub> to AS + hold time                       | <br> ThCSO(AS)<br>  | <br> <br><u> </u>                                                                                     | 9,            | 10,         | 11 | <br>  4<br>          | 40              | <br> <br> <br> | <br>  60<br>              | <br>        | l<br>ns       |

| CS <sub>1</sub> to DS + setup time                      | <br> TsCS1(0S)<br>  | <br> <br><u> </u>                                                                                     | 9,            | 10,         | 11 | <br>  5<br>          | 80              | 1              | 1 <u>1</u> /<br>  100<br> | <br> <br>   | l<br>Ins      |

| $CS_1$ to $DS + 2/$ hold time                           | ThCS1(DS)           | <br>                                                                                                  | 9,            | 10,         | 11 | 6                    | 1/<br>  40<br>  |                | 55                        | <br> <br>   | ns            |

| INTACK to AS + 1/ setup time                            | <br> TsIA(AS)<br>   | <br> <br>                                                                                             | 9,            | 10,         | 11 | 7                    | 0               |                | 0                         | <br> <br>   | ns            |

| INTACK to AS + 1/<br>hold time                          | <br> ThIA(AS)<br>   | <br> <br> -                                                                                           | 9,<br>        | 10,         | 11 | 8                    | 250             | <br> <br>      | 250<br>                   | <br> <br>   | ns            |

| R/W (Read) to DS + setup time                           | <br> TsRWR(DS)<br>  | <br> <br>                                                                                             | 9,            | 10,         | 11 | <br>  9<br>          | 80              | <br> <br>      | 100                       | <br> <br>   | ns            |

| $R/W$ to $\overline{DS}$ + $1/$ hold time               | <br> Thrw(DS)<br>   | <br> -<br> -                                                                                          | 9,            | 10,         | 11 | 10                   | 40              | <br> <br>      | 55                        | <br> <br>   | ns            |

| R/W (Write) to DS + 1/<br>setup time                    | <br> TsRWW(DS)<br>  |                                                                                                       | 9,            | 10,         | 11 | 11                   | 0               |                | 0                         |             | ns            |

| $\frac{1}{AS}$ + to $\frac{DS}{DS}$ + $\frac{1}{delay}$ | TdAS(DS)            | <br> <br> -                                                                                           | 9,            | 10,         | 11 | 12                   | 50              |                | 85                        |             | ns            |

| DS low width                                            | TwDS                |                                                                                                       | 9.            | 10.         | 11 | 13                   | 250             |                | 390                       | '           | ns            |

| Valid access $\frac{1}{3}$ / recovery time              | TrC<br>I            | <u> </u><br>                                                                                          | <del>9,</del> | 10,<br>10,  | 11 | 14                   | 6TcPC<br>  +130 |                | 6TcPC<br>+200             |             | ns            |

| Address to $\overline{\text{AS}}$ † 2/<br>setup time    | <br> TsA(AS)<br>    | <br>                                                                                                  | 9,            | 10,         | 11 | 15                   | 10              |                | 30                        | <br> <br>   | ns            |

| Address to AS † 2/<br>hold time                         | ThA(AS)             | <br>                                                                                                  | 9,<br>        | 10,         | 11 | 16                   | 30              |                | 50                        |             | ns            |

| Write data to DS ↓<br>setup time                        | TsDW(DS)            |                                                                                                       | 9,            | 10,         | 11 | 17                   | 20              |                | 30                        | <br> <br>   | ns            |

| Write data to DS + 1/<br>hold time                      | ThDW(DS)            |                                                                                                       | 9,            | 10,         | 11 | 18                   | 20              |                | 30                        |             | ns            |

| DS + to data active<br>delay                            | <br> TdDS(DA)  <br> |                                                                                                       | <br> 9,<br>   | 10,         | 11 | 19                   | 0               | <br>           | 0                         |             | ns            |

| See footnotes at end of 1                               | table.              |                                                                                                       |               |             |    |                      |                 |                |                           |             |               |

| MILITARY DR                                             | AWING               |                                                                                                       |               |             | C  | WG NO.               |                 |                |                           |             |               |

| DEFENSE ELECTRONICS S<br>DAYTON, OH                     |                     | TER A 1                                                                                               | REV           | Α.          |    | 596                  | 2-85518<br>Page | 5              | ·.                        | <del></del> |               |

| Test                                                                                 | <br> Symbol                    | Conditions                                                        |             | oup / |               | Refer-                                |                | Devic         | pe             | <br> Unit                    |          |  |  |

|--------------------------------------------------------------------------------------|--------------------------------|-------------------------------------------------------------------|-------------|-------|---------------|---------------------------------------|----------------|---------------|----------------|------------------------------|----------|--|--|

|                                                                                      | ļ<br>!                         | -55°C < T <sub>C</sub> < +125°C<br>  V <sub>CC</sub> = 5.0 V *10% | 1           | bgrou | lsqı.<br>İ    | ence                                  | +              | 01            | T              | 02                           | T<br>T   |  |  |

|                                                                                      |                                | unless otherwise specified                                        | ╀           |       | _             |                                       | Min            | Max           | Min<br>  1/    |                              | <u> </u> |  |  |

| DS + to read data<br>not valid delay                                                 | 1                              | See figure 3<br> C <sub>L</sub> = 50 pF ±10%                      | l           | 10,   | 11            | 20                                    | 0              | <u>i</u><br>! | jō             |                              | ns       |  |  |

| DS + to read data valid delay                                                        | TdDSf(DR)                      | Tunless otherwise specified<br> <br>                              |             | 10,   | 11            | 21                                    | <br> <br>      | 180           |                | <br> 250<br>                 | l<br>ns  |  |  |

| AS † to read data<br>valid delay                                                     | TdAS(DR)                       |                                                                   | + +         | 10,   | 11            | 22                                    |                | 335<br>       |                | <br>  520<br>                | ns       |  |  |

| DS <sup>†</sup> to read data<br>float delay                                          | <br> TdDS(DRZ)<br>             |                                                                   |             | 10,   | 11            | 23                                    |                | 45            | <br> <br>      | <br>  70<br>                 | ns       |  |  |

| Address required valid<br>to read data valid<br>delay                                | <br>  TdA (DR )<br>            |                                                                   | <br> 9,<br> | 10,   | 11  <br> <br> | 24                                    | <br> <br> <br> | <br>  420<br> | <br> <br> <br> | <br> 570<br>  <u>1</u> /<br> | ns       |  |  |

| delay                                                                                | TdDS(W)                        |                                                                   | 9,          | 10,   | 11            | 25                                    | <br> <br> -    | 200           | <br> <br>      | 240                          | ns       |  |  |

| DS <sup>†</sup> to W/REQ not  <br>valid delay                                        | TdDSf(REQ)                     |                                                                   | 9,          | 10,   | 11            | 26                                    |                | 200           | <br> <br>      | 240                          | ns       |  |  |

| DS <sup>†</sup> to DTR/REQ not <u>1/</u> valid delay                                 | TdDSr(REQ)                     |                                                                   | 9,          | 10,   | 11            | 27                                    | <br> <br>      | 5TcPC<br>+500 |                | <br> 5TcPC <br> +300         | ns       |  |  |

| $\frac{1/5}{AS}$ to $\overline{INT}$ valid   delay                                   | TdAS(INT)                      |                                                                   | 9,          | 10,   | 11            | 28                                    |                | 500           |                | 500                          | ns       |  |  |

| $\overline{AS}$ <sup>†</sup> to $\overline{DS}$ <sup>†</sup> 1/6/(acknowledge) delay | Tdas(DSA)                      | <u> </u>                                                          | 9,          | 10,   | 11            | 29                                    | <br>  250<br>  |               | 250            |                              | ns       |  |  |

| DS (acknowledge) <u>1</u> /  <br>low width                                           | TwuSA                          |                                                                   | 9,          | 10,   | 11            | 30                                    | 250            |               | 390            |                              | ns       |  |  |

| DS + (acknowledge)  <br>to read data valid  <br>delay <u>1</u> /                     | TdDSA(DR)                      |                                                                   | 9,          | 10,   | 11            | 31                                    |                | 180           |                | 250                          | ns       |  |  |

| IEI to DS + (acknowledge) setup time 1/                                              | TsIEI(DSA) <br> <br> <br> <br> | -<br>19<br>19<br>1                                                | 9,          | 10,   | 11            | 32                                    | 100            |               | 120            |                              | ns       |  |  |

| IEI to DS †  <br>(acknowledge)  <br>hold time <u>1</u> /                             | ThIEI(DSA)                     | -<br> <br> <br> <br> <br>                                         | 9,          | 10,   | 11            | 33                                    | 0              |               | 0              | <br> <br> <br>               | ns       |  |  |

| ee footnotes at end of                                                               | table.                         | ,                                                                 |             |       |               | · · · · · · · · · · · · · · · · · · · | !              |               |                | 1                            |          |  |  |

| MILITARY DE                                                                          | RAWING                         | SIZE                                                              |             |       | D             | WG NO.                                |                |               |                |                              |          |  |  |

| DEFENSE ELECTRONICS DAYTON, OF                                                       |                                | TER REV                                                           | ·           |       |               |                                       |                | 5962-85518    |                |                              |          |  |  |

| TA                                                                                    | BLE I. Elec | trical performance chara                                      | cteristics -           | Contir   | wed.   |                                |                                                  |                        |          |

|---------------------------------------------------------------------------------------|-------------|---------------------------------------------------------------|------------------------|----------|--------|--------------------------------|--------------------------------------------------|------------------------|----------|

| Test                                                                                  | Symbol      | Conditions                                                    | Group A                | Refer    |        | Device                         | typ                                              | е                      | Uni      |

|                                                                                       |             | -55°C < Tr < +125°C                                           | Isubaroups             |          |        | 01                             |                                                  | 02                     | Ţ        |

|                                                                                       |             | $V_{CC} = 5.0 \text{ V } \pm 10\%$<br>unless otherwise specif | ied                    | <u> </u> | Min    | Max                            | Min                                              | Max                    | <u> </u> |

| IEI to IEO delay 1/                                                                   |             | See figure 3<br>C <sub>L</sub> = 50 pF ±10%                   | 9, 10, 11              | 1 34     |        | 100                            | <u> </u>                                         | 120                    | ns       |

| AS to IEO delay                                                                       | TdAS(IEO)   | unless otherwise specif                                       | ied <br> 9, 10, 11<br> | 35       |        | 250                            | <br> <br>                                        | <br>  250<br>          | l ns     |

| DS <sup>†</sup> (acknowledge) <u>1/5/</u><br>to INT inactive<br>delay                 | TdDSA(INT)  |                                                               | 9, 10, 11              | 36       |        | 500                            |                                                  | 500                    | l ns     |

| $\overline{\text{DS}}$ to $\overline{\text{AS}}$ †delay $\underline{1}$ /for no reset |             | 9, 1                                                          | 9, 10, 11              | 1 37     | 15     |                                | 30                                               | <br> <br>              | ns       |

| $\frac{1}{AS}$ to $\overline{DS}$ delay for no reset                                  | TdASQ(DS)   |                                                               | 9, 10, 11              | 1 38     | 30     | <br> <br>                      | 30                                               | ]<br>                  | l ns     |

| $\overline{\text{AS}}$ and $\overline{\text{DS}}$ coincident low for reset $1/8/$     | Twres       | -                                                             | 9, 10, 11              | 39       | 250    |                                | 250                                              |                        | l ns     |

| PCLK low width                                                                        | TwPC1       | •                                                             | 9, 10, 11              | 40       | 70     | 1000                           |                                                  | 2000<br>1/             | l ns     |

| PCLK high width                                                                       | TwPCh       | •                                                             | 9, 10, 11              | 41       | 70     | 1000                           | 105                                              |                        | ns       |

| PCLK cycle time                                                                       | TcPC        | •                                                             | 9, 10, 11              | 42       | 165    | 2000                           | 250                                              | 4000<br>1/             | l ns     |

| PCLK rise time $1/$                                                                   | TrPC        | +                                                             | 9, 10, 11              | 43       | i<br>I | 1 15                           | <del>                                     </del> | 20                     | l ns     |

| PCLK fall time                                                                        | TfPC        |                                                               | 9, 10, 11              | 44       |        | 10                             |                                                  | 1/<br>  <del>2</del> 0 | ns       |

| PCLK ↓ to W/REQ   valid 1/                                                            | TdPC(REQ)   |                                                               | 9, 10, 11              | 1        |        | <br>  250<br>                  |                                                  | 250                    | ns       |

| PCLK <sup>†</sup> to wait<br>inactive delay                                           | TdPC(W)     |                                                               | 9, 10, 11              | 2        | i<br>I | 350                            |                                                  | 350                    | ns       |

| RxC <sup>†</sup> to PCLK <sup>†</sup> setup<br>time 9/12/<br>(PCLK 4 case only)       | TsRXC(PC)   |                                                               | 9, 10, 11              | 3        | 70     | <br> TwPCL<br>  <u>1</u> /<br> | <br>  80  <br>                                   | TwPCL 1/               | ns<br>ns |

| ee footnotes at end of                                                                | table.      |                                                               |                        |          | · '    |                                | ·······                                          |                        | ·        |

| MILITARY DR                                                                           |             | SIZE                                                          | D                      | WG NO.   | 2-8551 | 18                             |                                                  |                        |          |

| DEFENSE ELECTRONICS :<br>DAYTON, OF                                                   |             | RE                                                            | :                      |          | PAGE   |                                |                                                  |                        |          |

| DESC FORM 193A                                                                        |             |                                                               |                        |          |        |                                |                                                  |                        |          |

| Test                                                                                                                                                                | <br>  Symbol         | Conditions                                                                  | <br> Gr     | oup | Α  | <br> Refer-  |                | Device         | type          |                 | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------|-------------|-----|----|--------------|----------------|----------------|---------------|-----------------|------|

|                                                                                                                                                                     |                      | -55°C < T <sub>C</sub> < +125°C<br>V <sub>CC</sub> = 5.0 V ±10%             | sul         |     |    | lence        | 01             |                | 02            |                 |      |

| RxD to $\overline{\text{RxC}} \uparrow 1/9/$<br>setup time (X1 $\overline{\text{mode}}$ )                                                                           | TsRXD(RXCr)          | unless otherwise specified<br> See figure 3<br> C <sub>1</sub> = 50 pF ±10% | Т           | 10, | 11 | 4            | Min<br>  O     | Max<br> <br>   | Min<br>O      | Max<br> <br>    | ns   |

|                                                                                                                                                                     | ThRXD(RXCr)          | unless otherwise specified                                                  |             | 10, | 11 | 5            | 150            |                | 1/<br>T50     | <br> <br>       | ns   |

| $\frac{1}{\text{RxD to }} \frac{1}{\text{RxC}} + \frac{1}{\text{setup}}$ time (X1 mode)                                                                             | <br> TsRXD(RXCf)     |                                                                             | 9,          | 10, | 11 | <br>  6<br>  | 0              | <br>           | 0             | <br>  <br> <br> | ns   |

| $\frac{9/13}{RxD \text{ to } RxC + \text{hold}}$<br>time (X1 mode)                                                                                                  | <br> ThRXD(RXCf)     |                                                                             | 9,          | 10, | 11 | <br>  7<br>  | 150            | <br> <br>      | 1/<br>T50     | <br> <br>       | ns   |

| $\begin{array}{ccc} \hline \text{SYNC to } \overline{\text{RxC}} \uparrow \text{ setup} \\ \hline \text{time} & \underline{1}/\underline{9}/ \\ \hline \end{array}$ | <br> TsSY(RXC)<br>   |                                                                             | 9,          | 10, | 11 | <br>  8<br>  | -200           |                | -200          |                 | ns   |

| time                                                                                                                                                                | <br> ThSY(RXC)<br>   |                                                                             | 9,          | 10, | 11 | 9            | 3TcPC<br> +200 |                | 3TcPC<br>+200 |                 | ns   |

| setup time                                                                                                                                                          | TsTXC(PC)            |                                                                             | 9,          | 10, | 11 | 10           | 0              | <br>           | 0             | <br> <br>       | ns   |

| (X1 mode)                                                                                                                                                           | <br> TdTXCf(TXD)<br> | i<br>                                                                       | 9,          | 10, | 11 | 11           |                | 230            |               | 300             | ns   |

| $\frac{10}{1 \text{ TxC}}$ to TxD $\frac{10}{1 \text{ delay}}$ (X1 mode)                                                                                            | <br> TdTXCr(TXD)     |                                                                             | <br> 9,<br> | 10, | 11 | 12           |                | 230            |               | 300             | ns   |

| (send clock echo)                                                                                                                                                   | TdTXD(TRX)           | <u> </u>                                                                    | 9,          | 10, | 11 | 13           |                | 200            |               | 200             | ns   |

|                                                                                                                                                                     | T₩RTXh               |                                                                             | 9,          | 10, | 11 | 14           | 180            |                | 180           |                 | ns   |

|                                                                                                                                                                     | I<br> Twrtx1<br>     |                                                                             | <br> 9,<br> | 10, | 11 | <br>  15<br> | 180            | <br> <br>      | 180           | <br>            | ns   |

|                                                                                                                                                                     | TCRTX                |                                                                             | <br> 9,<br> | 10, | 11 | 16           | 400            | <br> <br>      | 400           | <br> <br>       | ns   |

| period                                                                                                                                                              | <br> TcRTXX<br>      |                                                                             | 9,          | 10, | 11 | <br>  17<br> | 250            | <br> 1000 <br> | 250           | 1000            | ns   |

| $\frac{1}{14}$                                                                                                                                                      | TwTRXh               |                                                                             | <br> 9,     | 10, | 11 | 18           | 180            |                | 180           |                 | ns   |

| 1/ 14/<br>TRXC low width                                                                                                                                            | TwTRX1               |                                                                             | <br> 9,     | 10, | 11 | 19           | 180            |                | 180           |                 | ns   |

| ee footnotes at end o                                                                                                                                               | f table.             |                                                                             |             |     |    |              |                |                |               |                 |      |

| MILITARY D                                                                                                                                                          |                      | 1 4                                                                         | <del></del> |     |    | DWG NO       | 62-855         | 18             |               |                 |      |

| DEFENSE ELECTRONIC DAYTON,                                                                                                                                          |                      | TER RE                                                                      | ······      | Α   |    |              | PAG            |                |               |                 |      |

| Test                                                                                             | Symbol     | Conditions                                                                                                      | Gr                                                           | oup | A  | <br> Refer-  | Device 01       |              | type<br>02  |                 | <br> Unit<br> |

|--------------------------------------------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----|----|--------------|-----------------|--------------|-------------|-----------------|---------------|

|                                                                                                  |            | $-55^{\circ}C \le T_{C} \le +125^{\circ}C$<br>  $V_{CC} = 5.0 \text{ V} \pm 10\%$<br> unless otherwise specifie | <pre>&lt; +125°C  subgroups 0 V ±10%   rise specified </pre> |     |    | lence        | Ť               |              | Min         | 1               | <u> </u><br>  |

| TRXC cycle time                                                                                  | TcTRX      | <br> See figure 3<br> C <sub>1</sub> = 50 pF ±10%                                                               | 9,                                                           | 10, | 11 | <br>  20<br> | 400             | <br> <br>    | 400         | <br>            | <br>  ns<br>  |

| DCD or CTS pulse width                                                                           | TwEXT      | Tuñless otherwise specifie<br> <br>                                                                             |                                                              | 10, | 11 | 21           | 200             | <br>         | 200         | T               | ns            |

| SYNC pulse width $\frac{1}{}$                                                                    | TwsY       | T<br> <br>                                                                                                      | 19,                                                          | 10, | 11 | 22           | 200             | <br>         | 200         |                 | ns            |

| RXC + to W/REQ valid delay 1/16/18/                                                              | TdRXC(REQ) | Ť<br> <br> <br>                                                                                                 | 19,                                                          | 10, | 11 | 1 1          | 8               | 12           | 8           | 12              | ns            |

| RxC + to wait inactive delay 1/15/16/18/                                                         |            | Ť<br> <br> -<br> -                                                                                              | 19,                                                          | 10, | 11 | 2            | 8               | 12           | 8           | 12              | ns            |

| $\overline{RxC}$ to $\overline{SYNC}$ valid delay $\underline{1}/\underline{16}/\underline{18}/$ | TdRXC(SY)  | T<br>                                                                                                           | 9,                                                           | 10, | 11 | 3            | 4               | 7            | 4           | 7               | l ns          |

| RxC + INT valid delay  <br>1/ 15/ 16/ 18/ 19/                                                    | TdRXC(INT) | T<br> <br>                                                                                                      | 9,                                                           | 10, | 11 | 4            | 8 +2            | 12           |             |                 | ns            |

| TxC + to W/REQ valid delay 1/17/18/                                                              | TdTXC(REQ) | †<br> <br> <br>                                                                                                 | 9,                                                           | 10, | 11 | 5<br>  5<br> | 5               | <br>  8<br>  | 5           | <br>  8<br>     | ns            |

| TxC + to wait inactive<br>delay 1/ 15/ 17/ 18/                                                   |            |                                                                                                                 | 19,                                                          | 10, | 11 | <br>  6<br>  | 5               | 8            | 5           | <br>  8<br>     | l ns          |

| TxC + to DTR/REQ valid<br>delay 1/17/18/                                                         | TdTXC(DRQ) |                                                                                                                 | 19,                                                          | 10, | 11 | <br>  7<br>  | 4               | <br>  7 <br> | 4           | 7               | ns            |

| Z/<br>TxC + to TNT valid  <br>delay <u>1/15/17/18/19</u> /                                       | TdTXC(INT) |                                                                                                                 | 19,                                                          | 10, | 11 | <br>  8<br>  | 4 +2            | 6            |             | 6 +3            | l ns          |

| SYNC transition to INT<br>valid delay 1/15/19/                                                   |            | T<br> <br>                                                                                                      | 9,                                                           | 10, | 11 | 9            | 2               | 3            | 2           | 3               | l ns          |

| DCD or CTS transition  <br>to INT valid delay<br>1/ 15/ 19/                                      | TdEXT(INT) | †<br> <br> -<br>                                                                                                | 9,                                                           | 10, | 11 | <br>  10<br> | 2               | 3            | 2           | 3<br> <br> <br> | ns            |

| ee footnotes at end of                                                                           | table.     |                                                                                                                 | <u> </u>                                                     |     |    | <u> </u>     | <del> </del>    | <u>'</u>     | <del></del> | <u>*</u> '      | <u>'</u>      |

| MILITARY DI                                                                                      | RAWING     | SIZE                                                                                                            |                                                              |     | D  | WG NO        |                 |              |             | ·               |               |

| DEFENSE ELECTRONICS<br>DAYTON, O                                                                 |            | TER A REV                                                                                                       | ,                                                            | Α   | 1  | 590          | 2-85518<br>PAGE | 9            |             |                 |               |

- 2/ Parameter does not apply to interrupt acknowledge transactions.

- 3/ Parameter applies only between transactions involving the SCC.

- $\frac{4}{}$  Float delay is defined as the time required for a  $\pm 0.5$  V change in the output with a maximum DC load and minimum AC load.

- 5/ Open-drain output, measured with open-drain test load.

- 6/ Parameter is system dependent. For any Z-SCC in the daisy chain TdAS(DSA) must be greater than the sum of TdAS(IEO) for the highest priority device in the daisy chain. TsIEI(DSA) for the Z-SCC and TdIEIf(IEO) for each device separating them in the daisy chain.

- 7/ Parameter applies only to a Z-SCC pulling INT low at the beginning of the interrupt acknowledge transactions.

- 8/ Internal circuitry allows for the reset provided by the Z8 to be recognized as a reset by the Z-SCC.

- 9/ RXC is RIXC or TRXC, whichever is supplying the receive clock.

- 10/ TXC is TRXC or RTXC, whichever is supplying the transmit clock.

- 11/ Both RTxC and SYNC have 30 pF capacitors to the ground connected to them.

- $\frac{12/}{\text{Parameter applies only if the data rate is one-fourth the PCLK rate.}} \text{ In all other cases, no phase relationship between $\overline{\text{RxC}}$ and $\text{PCLK}$ or $\overline{\text{TxC}}$ and $\text{PCLK}$ is required.}$

- 13/ Parameter applies only to FM encoding/decoding.

- Parameter applies only for transmitter and receiver; DPLL and baud rate generator timing requirements are identical to chip PCLK requirements.

- 15/ Open-drain output, measured with open-drain test load.

- 16/ RxC is RTxC or TRxC, whichever is supplying the receive clock.

- 17/ TxC is TRxC or RTxC, whichever is supplying the transmit clock.

- 18/ Units equal to TcPC.

- 19/ Units equal to AS.

| MILITARY DRAWING                               | SIZE |     | DWG NO.    |  |

|------------------------------------------------|------|-----|------------|--|

|                                                | A    |     | 5962-85518 |  |

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO |      | REV | PAGE 10    |  |

- 3.5 Certificate of compliance. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in 6.5. The certificate of compliance submitted to DESC-ECS prior to listing as an approved source of supply shall state that the manufacturer's product meets the requirements of MIL-STD-883 (see 3.1 herein) and the requirements herein.

- 3.6 Certificate of conformance. A certificate of conformance as required in MIL-STD-883 (see 3.1 herein) shall be provided with each lot of microcircuits delivered to this drawing.

- 3.7 Notification of change. Notification of change to DESC-ECS shall be required in accordance with MIL-STD-883 (see 3.1 herein).

- 3.8 Verification and review. DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 Sampling and inspection. Sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein).

- 4.2 Screening. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test (method 1015 of MIL-STD-883).

- Test condition A, B, C, or D using the circuit submitted with the certificate of compliance (see 3.5 herein).

- (2)  $T_A = +125^{\circ}C$ , minimum.

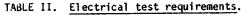

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

- 4.3 Quality conformance inspection. Quality conformance inspection shall be in accordance with method 5005 of MIL-STD-883 including groups A, B, C, and D inspections. The following additional criteria shall apply.

- 4.3.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. Subgroups 4, 5, and 6 in table I, method 5005 of MIL-STD-883 shall be omitted.

- c. Subgroup 7 tests shall include verification of the instruction set.

- 4.3.2 Groups C and D inspections.

- a. End-point electrical parameters shall be as specified in table II herein.

- b. Steady-state life test (method 1005 of MIL-STD-883) conditions:

- Test condition A, B, C, or D using the circuit submitted with the certificate of compliance (see 3.5 herein).

- (2)  $T_A = +125$ °C, minimum.

- (3) Test duration: 1,000 hours, except as permitted by appendix B of MIL-M-38510 and method 1005 of MIL-STD-883.

|                                                | SIZE         |     |     |   | DWG NO | ),       |    |

|------------------------------------------------|--------------|-----|-----|---|--------|----------|----|

| MILITARY DRAWING                               | A            |     |     |   | 59     | 62-85518 |    |

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO |              | F   | REV | A |        | PAGE     | 18 |

| DECC ECRM 1024                                 | <del>*</del> | A . |     |   |        | •        |    |

| MIL-STט-883 test requirements<br>                                        | Subgroups<br>(per method<br>  5005, table I) |

|--------------------------------------------------------------------------|----------------------------------------------|

| Interim electrical parameters<br> (method 5004)<br>                      |                                              |

| Final electrical test parameters<br>(method 5004)                        | 1*, 2, 3, 9                                  |

| Group A test requirements<br> (method 5005)<br>                          | 1 1, 2, 3, 7, 8,<br>9, 10, 11**              |

| Groups C and D end-point<br> electrical parameters<br> (method 5005)<br> | 1, 2, 3                                      |

\* PDA applies to subgroup 1.