# **OKI** Semiconductor MSM51V4222C

### 262,263-Word × 4-Bit Field Memory

# **GENERAL DESCRIPTION**

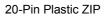

The OKI MSM51V4222C is a high performance 1-Mbit, 256 K  $\times$  4-bit, Field Memory. It is designed for highspeed serial access applications such as HDTVs, conventional NTSC TVs, VTRs, digital movies and Multi-media systems. It is a FRAM for wide or low end use as general commodity TVs and VTRs, exclusively. The MSM51V4222C is not designed for the other use or high end use in medical systems, professional graphics systems which require long term picture, and data storage systems and others. The 1-Mbit capacity fits one field of a conventional NTSC TV screen and cascaded directly without any delay devices among the MSM51V4222C. (Cascading of MSM51V4222C provides larger storage depth or a longer delay).

Each of the 4-bit planes has separate serial write and read ports. These employ independent control clocks to support asynchronous read and write operations. Different clock rates are also supported that allow alternate data rates between write and read data streams.

The MSM51V4222C provides high speed FIFO, First-In First-Out, operation without external refreshing: it refreshes its DRAM storage cells automatically, so that it appears fully static to the users. Moreover, fully static type memory cells and decoders for serial access enable refresh free serial access operation,

so that the serial read and/or write control clock can be halted high or low for any duration as long as the power is on. Internal conflicts of memory access and refreshing operations are prevented by special arbitration logic.

The MSM51V4222C's function is simple, and similar to a digital delay device whose delay-bit-length is easily set by reset timing. The delay length, number of read delay clocks between write and read, is determined by externally controlled write and read reset timings.

Additional SRAM serial registers, or line buffers for the initial access of  $256 \times 4$ -bit enable high speed first-bit-access with no clock delay just after the write or read reset timings.

The MSM51V4222C is similar in operation and functionality to OKI 2-Mbit Field Memory MSM51V8222A.

### **FEATURES**

- Single power supply:  $3.3 V \pm 0.3 V$

- $512 \text{ Rows} \times 512 \text{ Column} \times 4 \text{ bits}$

- Fast FIFO (First-in First-out) operation

- High speed asynchronous serial access Read/Write cycle time 30 ns/40 ns Access time 30 ns/35 ns

- Functional compatibility with OKI MSM51V8222A

- Self refresh (No refresh control is required)

Package options:

| • | Package options:              |                       |                             |

|---|-------------------------------|-----------------------|-----------------------------|

|   | 16-pin 300 mil plastic DIP    | (DIP16-P-300-2.54)    | (Product: MSM51V4222C-xxRA) |

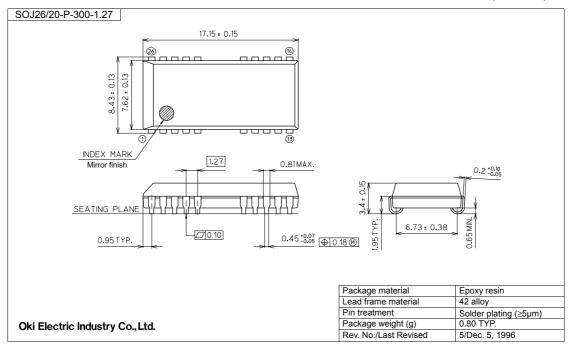

|   | 26/20-pin 300 mil plastic SOJ | (SOJ26/20-P-300-1.27) | (Product: MSM51V4222C-xxJA) |

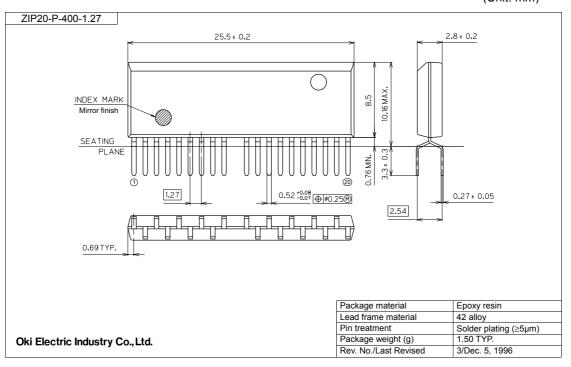

|   | 20-pin 400 mil plastic ZIP    | (ZIP20-P-400-1.27)    | (Product: MSM51V4222C-xxRD) |

|   |                               |                       | xx indicates speed rank.    |

# **PRODUCT FAMILY**

| Family Access Time (Max. |                     | Cycle Time (Min.) | Package                 |

|--------------------------|---------------------|-------------------|-------------------------|

| MSM51V4222C-30RA         | 30 ns               | 30 ns             | 200 mil 16 nin DID      |

| MSM51V4222C-40RA         | 35 ns               | 40 ns             | - 300 mil 16-pin DIP    |

| MSM51V4222C-30JA         | 30 ns               | 30 ns             | 200 mil 26/20 nin 60 l  |

| MSM51V4222C-40JA         | 35 ns               | 40 ns             | - 300 mil 26/20-pin SOJ |

| MSM51V4222C-30RD         | 30 ns               | 30 ns             | 400 mil 00 nin 71D      |

| MSM51V4222C-40RD         | 51V4222C-40RD 35 ns |                   | - 400 mil 20-pin ZIP    |

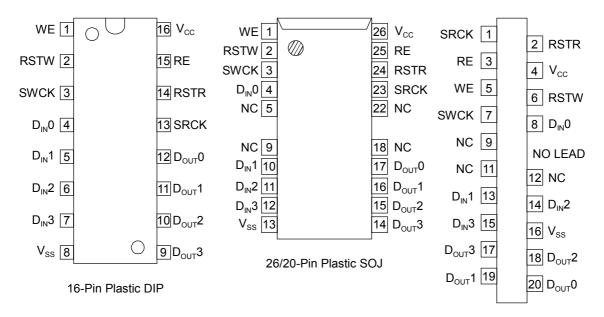

# **PIN CONFIGURATION (TOP VIEW)**

| Pin Name                | Function             |

|-------------------------|----------------------|

| SWCK                    | Serial Write Clock   |

| SRCK                    | Serial Read Clock    |

| WE                      | Write Enable         |

| RE                      | Read Enable          |

| RSTW                    | Write Reset Clock    |

| RSTR                    | Read Reset Clock     |

| D <sub>IN</sub> 0 to 3  | Data Input           |

| D <sub>OUT</sub> 0 to 3 | Data Output          |

| V <sub>cc</sub>         | Power Supply (3.3 V) |

| V <sub>SS</sub>         | Ground (0 V)         |

| NC                      | No Connection        |

|                         |                      |

# **BLOCK DIAGRAM**

### **OPERATION**

#### Write Operation

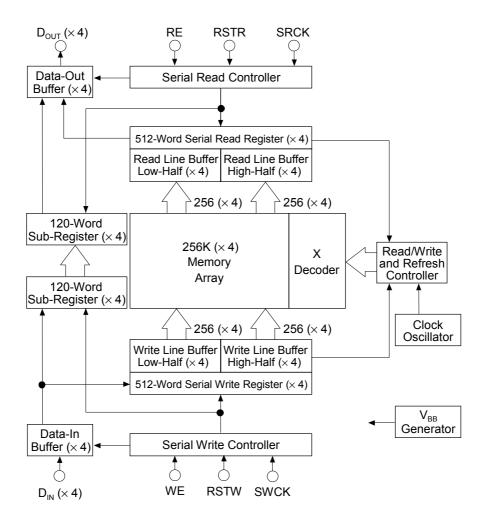

The write operation is controlled by three clocks, SWCK, RSTW, and WE. Write operation is accomplished by cycling SWCK, and holding WE high after the write address pointer reset operation or RSTW. Each write operation, which begins after RSTW, must contain at least 130 active write cycles, i.e. SWCK cycles while WE is high. To transfer the last data to the DRAM array, which at that time is stored in the serial data registers attached to the DRAM array, an RSTW operation is required after the last SWCK cycle.

### Write Reset: RSTW

The first positive transition of SWCK after RSTW becomes high resets the write address counters to zero. RSTW setup and hold times are referenced to the rising edge of SWCK. Because the write reset function is solely controlled by the SWCK rising edge after the high level of RSTW, the states of WE are ignored in the write reset cycle.

Before RSTW may be brought high again for a further reset operation, it must be low for at least two SWCK cycles.

### Data Inputs: D<sub>IN</sub>0 to 3

### Write Clock: SWCK

The SWCK latches the input data on chip when WE is high, and also increments the internal write address pointer. Data-in setup time  $t_{DS}$ , and hold time  $t_{DH}$  are referenced to the rising edge of SWCK.

#### Write Enable: WE

WE is used for data write enable/disable control. WE high level enables the input, and WE low level disables the input and holds the internal write address pointer. There are no WE disable time (low) and WE enable time (high) restrictions, because the MSM51V4222C is in fully static operation as long as the power is on. Note that WE setup and hold times are referenced to the rising edge of SWCK.

#### **Read Operation**

The read operation is controlled by three clocks, SRCK, RSTR, and RE. Read operation is accomplished by cycling SRCK, and holding RE high after the read address pointer reset operation or RSTR. Each read operation, which begins after RSTR, must contain at least 130 active read cycles, i.e. SRCK cycles while RE is high.

### **Read Reset: RSTR**

The first positive transition of SRCK after RSTR becomes high resets the read address counters to zero. RSTR setup and hold times are referenced to the rising edge of SRCK. Because the read reset function is solely controlled by the SRCK rising edge after the high level of RSTR, the states of RE are ignored in the read reset cycle. Before RSTR may be brought high again for a further reset operation, it must be low for at least two SRCK cycles.

### Data Out: D<sub>OUT</sub>0 to 3

### **Read Clock: SRCK**

Data is shifted out of the data registers. It is triggered by the rising edge of SRCK when RE is high during a read operation. The SRCK input increments the internal read address pointer when RE is high.

The three-state output buffer provides direct TTL compatibility (no pullup resistor required). Data out is the same polarity as data in. The output becomes valid after the access time interval  $t_{AC}$  that begins with the rising edge of SRCK. There are no output valid time restriction on MSM51V4222C.

### Read Enable: RE

The function of RE is to gate of the SRCK clock for incrementing the read pointer. When RE is high before the rising edge of SRCK, the read pointer is incremented. When RE is low, the read pointer is not incremented. RE setup times ( $t_{RENS}$  and  $t_{RDSS}$ ) and RE hold times ( $t_{RENH}$  and  $t_{RDSH}$ ) are referenced to the rising edge of the SRCK clock.

#### **Power-up and Initialization**

On power-up, the device is designed to begin proper operation after at least 100  $\mu$ s after V<sub>CC</sub> has stabilized to a value within the range of recommended operating conditions. After this 100  $\mu$ s stabilization interval, the following initialization sequence must be performed.

Because the read and write address counters are not valid after power-up, a minimum of 130 dummy write operations (SWCK cycles) and read operations (SRCK cycles) must be performed, followed by an RSTW operation and an RSTR operation, to properly initialize the write and the read address pointer. Dummy write cycles/RSTW and dummy read cycles/RSTR may occur simultaneously.

If these dummy read and write operations start while  $V_{CC}$  and/or the substrate voltage has not stabilized, it is necessary to perform an RSTR operation plus a minimum of 130 SRCK cycles plus another RSTR operation, and an RSTW operation plus a minimum of 130 SRCK cycles plus another RSTW operation to properly initialize read and write address pointers

### **Old/New Data Access**

There must be a minimum delay of 600 SWCK cycles between writing into memory and reading out from memory. If reading from the first field starts with an RSTR operation, before the start of writing the second field (before the next RSTW operation), then the data just written will be read out.

The start of reading out the first field of data may be delayed past the beginning of writing in the second field of data for as many as 119 SWCK cycles. If the RSTR operation for the first field read-out occurs less than 119 SWCK cycles after the RSTW operation for the second field write-in, then the internal buffering of the device assures that the first field will still be read out. The first field of data that is read out while the second field of data is written is called "old data".

In order to read out "new data", i.e., the second field written in, the delay between an RSTW operation and an RSTR operation must be at least 600 SRCK cycles. If the delay between RSTW and RSTR operations is more than 120 but less than 600 cycles, then the data read out will be undetermined. It may be "old data" or "new" data, or a combination of old and new data. Such a timing should be avoided.

#### **Cascade Operation**

The MSM51V4222C is designed to allow easy cascading of multiple memory devices. This provides higher storage depth, or a longer delay than can be achieved with only one memory device.

# **ELECTRICAL CHARACTERISTICS**

# **Absolute Maximum Ratings**

| Parameter Symbol      |                  | Condition                     | Rating      | Unit |

|-----------------------|------------------|-------------------------------|-------------|------|

| Input Output Voltage  | V <sub>T</sub>   | at Ta = 25°C, V <sub>ss</sub> | -1.0 to 4.6 | V    |

| Output Current        | I <sub>os</sub>  | Ta = 25°C                     | 50          | mA   |

| Power Dissipation     | PD               | Ta = 25°C                     | 1           | W    |

| Operating Temperature | T <sub>opr</sub> | _                             | 0 to 70     | °C   |

| Storage Temperature   | T <sub>stg</sub> | —                             | –55 to 150  | Ο°   |

# **Recommended Operating Conditions**

| Parameter            | Symbol          | Min. | Тур.            | Max.                  | Unit |

|----------------------|-----------------|------|-----------------|-----------------------|------|

| Power Supply Voltage | V <sub>cc</sub> | 3.0  | 3.3             | 3.6                   | V    |

| Power Supply Voltage | V <sub>SS</sub> | 0    | 0               | 0                     | V    |

| Input High Voltage   | V <sub>IH</sub> | 2.4  | V <sub>cc</sub> | V <sub>CC</sub> + 0.3 | V    |

| Input Low Voltage    | V <sub>IL</sub> | -0.3 | 0               | 0.8                   | V    |

# **DC** Characteristics

| Parameter Symbol                         |  | Condition                                         |   | Max. | Unit |

|------------------------------------------|--|---------------------------------------------------|---|------|------|

| Input Leakage Current I <sub>LI</sub>    |  | $0 < V_I < V_{CC}$ , Other Pins Tested at V = 0 V |   | 10   | μA   |

| Output Leakage Current I <sub>LO</sub>   |  | $0 < V_{O} < V_{CC}$                              |   | 10   | μA   |

| Output "H" Level Voltage V <sub>OH</sub> |  | I <sub>он</sub> = –1 mА                           |   | _    | V    |

| Output "L" Level Voltage V <sub>OL</sub> |  | I <sub>OL</sub> = 2 mA                            | _ | 0.4  | V    |

| Operating Current I <sub>CC1</sub>       |  | Minimum Cycle Time, Output Open                   |   | 30   | mA   |

| Standby Current I <sub>CC2</sub>         |  | Input Pin = V <sub>IH</sub> /V <sub>IL</sub>      |   | 3    | mA   |

# Capacitance

(Ta = 25°C, f = 1 MHz)

| Parameter                                                            | Symbol | Max. | Unit |

|----------------------------------------------------------------------|--------|------|------|

| Input Capacitance (D <sub>IN</sub> , SWCK, SRCK, RSTW, RSTR, WE, RE) | C      | 7    | pF   |

| Output Capacitance (D <sub>OUT</sub> )                               | Co     | 7    | pF   |

# **OKI** Semiconductor

### FEDS51V4222C-03

# MSM51V4222C

# **AC Characteristics**

|                                        |                    |                |      | $(V_{cc} = 3.3 \text{ V} \pm 0.3 \text{ V}, \text{ Ta} = 0 \text{ to } 70^{\circ}\text{C})$ |      |       |

|----------------------------------------|--------------------|----------------|------|---------------------------------------------------------------------------------------------|------|-------|

| Parameter                              | Symbol             | MSM51V4222C-30 |      | MSM51V4222C-40                                                                              |      | Unit  |

|                                        |                    | Min.           | Max. | Min.                                                                                        | Max. | ••••• |

| Access Time from SRCK                  | t <sub>AC</sub>    | —              | 30   | —                                                                                           | 35   | ns    |

| D <sub>OUT</sub> Hold Time from SRCK   | t <sub>DDCK</sub>  | 6              |      | 6                                                                                           |      | ns    |

| D <sub>OUT</sub> Enable Time from SRCK | t <sub>DECK</sub>  | 6              | 30   | 6                                                                                           | 35   | ns    |

| D <sub>OUT</sub> Hold Time from RE     | t <sub>DDRE</sub>  | 9              | —    | 9                                                                                           | —    | ns    |

| SWCK "H" Pulse Width                   | t <sub>wswH</sub>  | 12             | —    | 17                                                                                          | —    | ns    |

| SWCK "L" Pulse Width                   | t <sub>wswL</sub>  | 12             | —    | 17                                                                                          | —    | ns    |

| Input Data Setup Time                  | t <sub>DS</sub>    | 3              | _    | 5                                                                                           | _    | ns    |

| Input Data Hold Time                   | t <sub>DH</sub>    | 6              | _    | 6                                                                                           | _    | ns    |

| WE Enable Setup Time                   | t <sub>wens</sub>  | 0              | _    | 0                                                                                           | _    | ns    |

| WE Enable Hold Time                    | t <sub>wenh</sub>  | 5              | _    | 5                                                                                           | _    | ns    |

| WE Disable Setup Time                  | t <sub>wDSS</sub>  | 0              | _    | 0                                                                                           | _    | ns    |

| WE Disable Hold Time                   | t <sub>wDSH</sub>  | 5              | _    | 5                                                                                           | _    | ns    |

| WE "H" Pulse Width                     | t <sub>wwen</sub>  | 5              | _    | 10                                                                                          | _    | ns    |

| WE "L" Pulse Width                     | t <sub>wwel</sub>  | 5              | _    | 10                                                                                          | _    | ns    |

| RSTW Setup Time                        | t <sub>RSTWS</sub> | 0              | _    | 0                                                                                           | _    | ns    |

| RSTW Hold Time                         | t <sub>RSTWH</sub> | 10             | _    | 10                                                                                          | _    | ns    |

| SRCK "H" Pulse Width                   | t <sub>wsr</sub>   | 12             | _    | 17                                                                                          | _    | ns    |

| SRCK "L" Pulse Width                   | t <sub>wsrL</sub>  | 12             | _    | 17                                                                                          | _    | ns    |

| RE Enable Setup Time                   | t <sub>RENS</sub>  | 0              | _    | 0                                                                                           | _    | ns    |

| RE Enable Hold Time                    | t <sub>RENH</sub>  | 5              | _    | 5                                                                                           | _    | ns    |

| RE Disable Setup Time                  | t <sub>RDSS</sub>  | 0              | _    | 0                                                                                           | —    | ns    |

| RE Disable Hold Time                   | t <sub>RDSH</sub>  | 5              | _    | 5                                                                                           | _    | ns    |

| RE "H" Pulse Width                     | t <sub>wreh</sub>  | 5              | _    | 10                                                                                          | _    | ns    |

| RE "L" Pulse Width                     | t <sub>wREL</sub>  | 5              | _    | 10                                                                                          | _    | ns    |

| RSTR Setup Time                        | t <sub>RSTRS</sub> | 0              | _    | 0                                                                                           | —    | ns    |

| RSTR Hold Time                         | t <sub>RSTRH</sub> | 10             | —    | 10                                                                                          | —    | ns    |

| SWCK Cycle Time                        | t <sub>swc</sub>   | 30             | —    | 40                                                                                          | —    | ns    |

| SRCK Cycle Time                        | t <sub>SRC</sub>   | 30             | —    | 40                                                                                          | —    | ns    |

| Transition Time (Rise and Fall)        | t <sub>T</sub>     | 3              | 30   | 3                                                                                           | 30   | ns    |

# $(V_{cc} = 3.3 \text{ V} \pm 0.3 \text{ V}, \text{ Ta} = 0 \text{ to } 70^{\circ}\text{C})$

| OKI | Semiconductor |

|-----|---------------|

|-----|---------------|

- Notes: 1. Input signal reference levels for the parameter measurement are  $V_{IH} = 3.0$  V and  $V_{IL} = 0$  V. The transition time  $t_T$  is defined to be a transition time that signal transfers between  $V_{IH} = 3.0$  V and  $V_{II} = 0$  V.

- 2. AC measurements assume  $t_T = 3$  ns.

- 3. Read address must have more than a 600 address delay than write address in every cycle when asynchronous read/write is performed.

- 4. Read must have more than a 600 address delay than write in order to read the data written in a current series of write cycles which has been started at last write reset cycle: this is called "new data read".

When read has less than a 119 address delay than write, the read data are the data written in a previous series of write cycles which had been written before at last write reset cycle: this is called "old data read".

- 5. When the read address delay is between more than 120 and less than 599, read data will be undetermined. However, normal write is achieved in this address condition.

- 6. Outputs are measured with a load equivalent to 1 TTL load and 30 pF. Output reference levels are  $V_{OH}$  = 2.0 V and  $V_{OL}$  = 0.8 V.

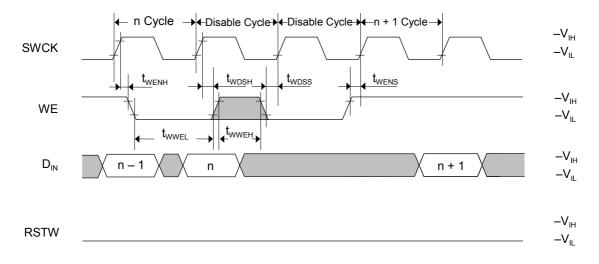

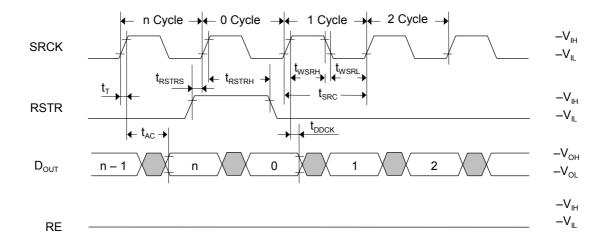

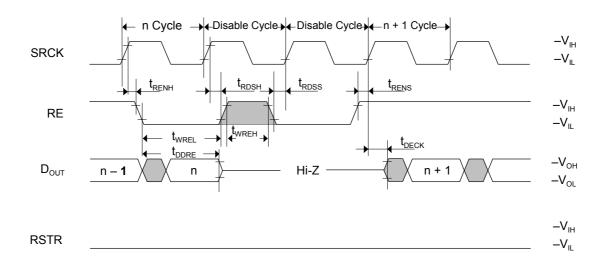

# **TIMING WAVEFORM**

### Write Cycle Timing (Write Reset)

# Write Cycle Timing (Write Enable)

# Read Cycle Timing (Read Reset)

# Read Cycle Timing (Read Enable)

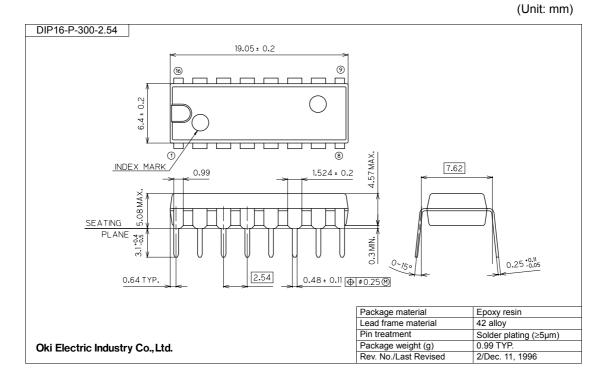

# PACKAGE DIMENSIONS

### **OKI** Semiconductor

# MSM51V4222C

Notes for Mounting the Surface Mount Type Package

The surface mount type packages are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

### FEDS51V4222C-03

### **OKI** Semiconductor

### MSM51V4222C

### NOTICE

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

Copyright 2000 Oki Electric Industry Co., Ltd.