# TMS38010 COMMUNICATIONS PROCESSOR

SEPTEMBER 1985 - REVISED MAY 1986

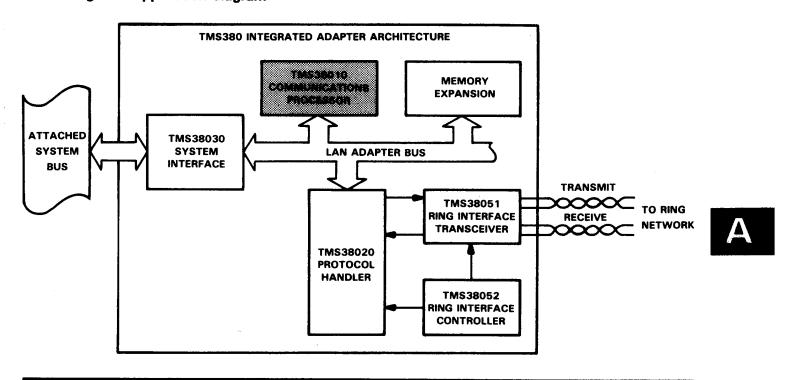

#### token ring LAN application diagram

PRODUCTION DATA documents centain information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1986, Texas Instruments Incorporated

A-1

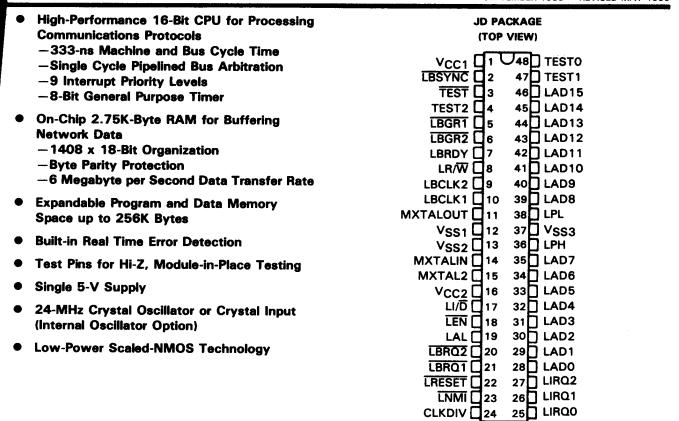

#### pin descriptions

| NAME                | 1/0 | DESCRIPTION                                                                                      |  |  |  |

|---------------------|-----|--------------------------------------------------------------------------------------------------|--|--|--|

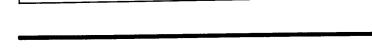

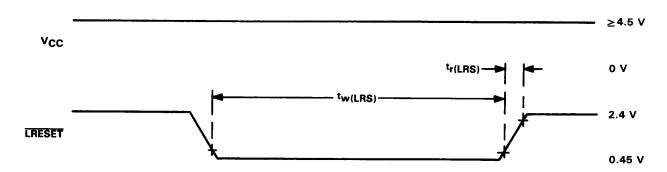

| LRESET              | 1   | TMS38010 Reset                                                                                   |  |  |  |

| LBCLK1, LBCLK2      | 0   | Bus Clocks                                                                                       |  |  |  |

| LBSYNC              | 1   | Bus Synchronization. This pin is reserved and should be left unconnected.                        |  |  |  |

| LAL                 | 1/0 | Address Latch Enable                                                                             |  |  |  |

| LEN                 | 1/0 | Data Enable                                                                                      |  |  |  |

| LBRDY               | 1   | Bus Ready. Used to force wait states on bus read/write cycles.                                   |  |  |  |

| LIRQO, LIRQ1, LIRQ2 | 1   | Interrupt Request Level Request                                                                  |  |  |  |

| LNMI                | 1   | Non-Maskable Interrupt (NMI) Request                                                             |  |  |  |

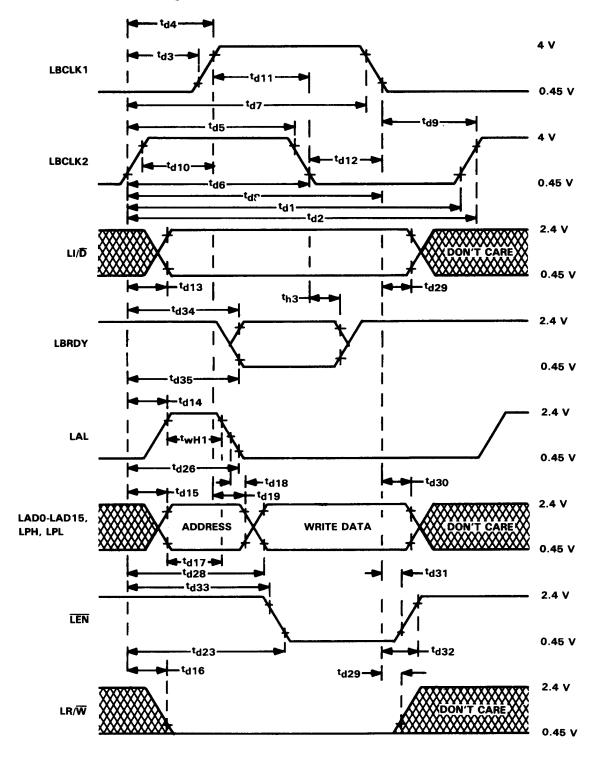

| LBRQ1, LBRQ2        | 1   | Bus Request 1 and 2. Used by bus masters to request control of the bus.                          |  |  |  |

| LBGRI, LBGR2        | 0   | Bus Grant 1 and 2                                                                                |  |  |  |

| LADO - LAD15        | 1/0 | Address/Data bus. LADO is the most-significant bit and LAD15 is the least-significant bit. LAD15 |  |  |  |

|                     |     | erves as a "Page Select" during the address phase of memory cycles.                              |  |  |  |

| LPH, LPL            |     |                                                                                                  |  |  |  |

| LI/D                | 0   | Instruction Fetch/Data Transfer Status Code                                                      |  |  |  |

| LR/W                | 1/0 | Read/Write signal                                                                                |  |  |  |

| CLKDIV              | i   | This pin is reserved and should be tied to VCC.                                                  |  |  |  |

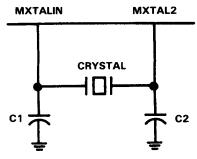

| MXTALIN             | 1   | Input to internal oscillator from crystal or external clock                                      |  |  |  |

| MXTAL2              | 0   | Connection to internal oscillator from crystal                                                   |  |  |  |

| MXTALOUT            | 0   | Crystal Frequency Output. This frequency is MXTALIN/3.                                           |  |  |  |

| TEST, TESTO-TEST2   | 1   | TMS38010 Test Pins. These pins should be left unconnected.                                       |  |  |  |

| Vcc                 |     | 5-V supply pins                                                                                  |  |  |  |

| VSS                 | 1   | Ground pins                                                                                      |  |  |  |

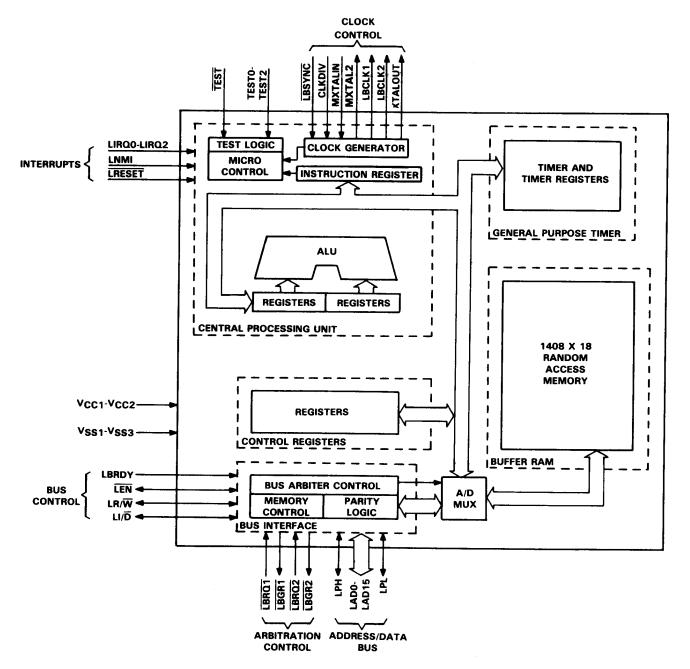

#### functional block diagram

#### description

The TMS38010 Communications Processor is a member of the TMS380 family of VLSI components which form a highly integrated Adapter used for attaching to a token ring local area network (LAN). The TMS38010 provides a high-performance CPU ideal for processing communications protocols. The TMS38010 provides 63 instructions, a 1408 x 18-bit RAM for communications data buffering and CPU workspace, and a general purpose timer for implementing software protocol timers. The TMS38010's architecture features hardware and software interrupts, memory-based registers for fast response to hardware and software interrupts, and a 333-ns machine cycle time. Bus arbitration is provided internal to the TMS38010 Communications Processor.

The TMS38010 Communications Processor, when coupled with the TMS38020 Protocol Handler, the TMS38030 System Interface, and the TMS38051 and TMS38052 Ring Interface Pair, forms a complete, integrated token ring LAN Adapter fully compatible with the IEEE Std 802.5-1985 Token Ring Access Method and Physical Layer Specifications for token ring networks.

#### architecture

The architecture of the TMS38010 Communications Processor consists of a 16-bit CPU, a LAN Adapter bus interface, a general purpose timer, control registers, and a 2.75K-byte buffer RAM.

#### central processing unit

The central processing unit (CPU) of the TMS38010 contains the arithmetic-logic unit (ALU), registers, and control store. This CPU features memory-to-memory architecture which can address up to 256K bytes of memory, logically divided into 128K bytes of data memory and 128K bytes of instruction memory. Using paging techniques, both the instruction and data spaces are paged into two 64K byte regions. This paging is accomplished via a page select output on the LAD15 pin during the address phase of memory cycles. The state of this pin is controlled through the CPU's status register.

#### arithmetic-logic unit (ALU)

The arithmetic-logic unit of the TMS38010 is 16 bits wide. The ALU performs all arithmetic and logical operations required during instruction execution. The ALU is partitioned into two 8-bit halves to accommodate byte operations. The bus interface only performs 16-bit wide transfers on the LAN Adapter bus, thus, the byte being operated upon may be modified while the unaffected byte is passed through unchanged.

#### internal registers

The CPU contains three registers used for programming: the Program Counter (PC), the Status Register (ST), and the Workspace Pointer (WP). The Program Counter contains the memory address of the next instruction word. The Status Register contains bits which signify the results of program comparisons, indicate program status conditions, and supply the interrupt mask to the interrupt priority circuits. The Workspace Pointer contains a memory address which defines the first word of a block of 16 words which define the Workspace Registers. These workspace registers are memory-resident working registers and are used as scratch and index registers similar to the internal registers of register-based architectures. By changing the value of the Workspace Pointer (as may occur when an interrupt occurs), a new set of registers is defined for efficient program context switches.

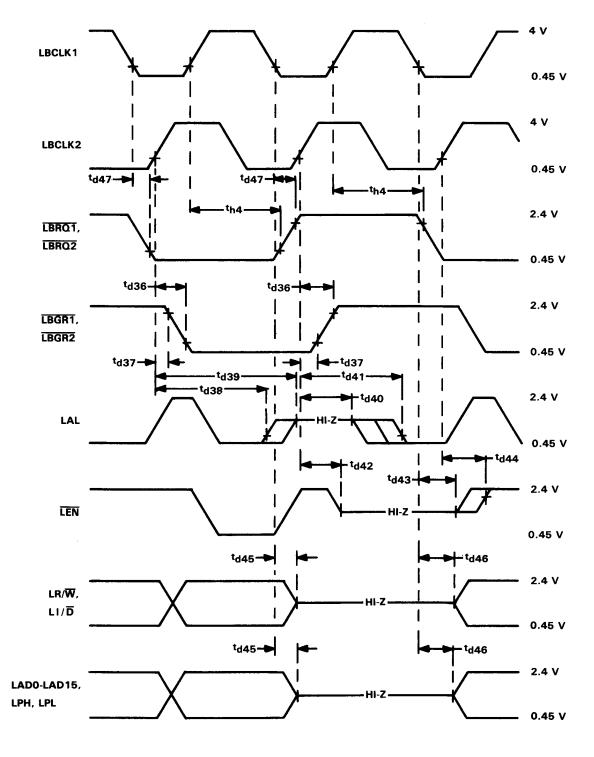

#### interrupts

Interrupts are presented to the TMS38010 via the LIRQ0, LIRQ1, and LIRQ2 interrupt request pins. These pins, when any one is active low for an entire LBCLK cycle, cause an interrupt request to be posted to the TMS38010's CPU. LIRQ0 (the most-significant bit) through LIRQ2 (the least-significant bit) present an interrupt level of one (all low) through level seven. When LIRQ0 through LIRQ2 are all high, no interrupt is requested. The prioritization of interrupts is done external to the TMS38010. In the TMS380 LAN Adapter, this function is performed by the TMS38030 System Interface.

When an interrupt is accepted (by one or more of the LIRQ lines being low for a full LBCLK cycle), the CPU performs a context switch by fetching a new Program Counter value and a new Workspace Pointer value from predefined memory locations in the first 32 bytes of memory. Three interrupt levels are specially defined for the TMS38010. The first is interrupt level 10. This interrupt level is used by the TMS38010's internal general purpose timer when the count has decremented to zero. The level ten interrupt is also used for a special "software interrupt" initiated by a request bit in the CPCTL (CP Control) register. This bit allows higher level software routines to activate lower-level routines such as a task scheduler. The second interrupt level specially defined for the TMS38010 is the level-2 interrupt. The level-2 interrupt is used to report several error conditions of the TMS38010. These include arithmetic fault, illegal opcode, and LAN Adapter bus parity errors. The third interrupt level defined for the TMS38010 is the level-0 interrupt. This interrupt is asserted when the LRESET or the LNMI pin is taken active low.

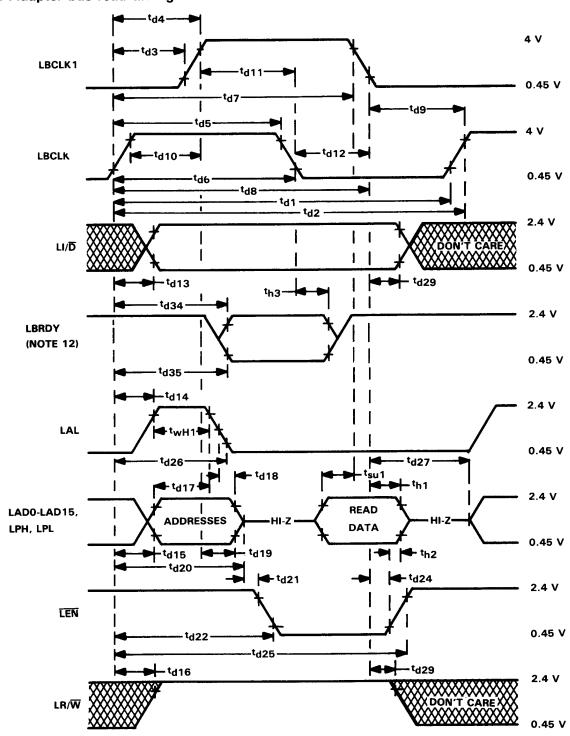

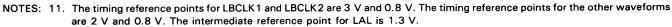

#### LAN adapter bus interface

The TMS38010 provides a high-speed interface to the TMS380 family LAN Adapter bus. This bus interface allows the TMS38010's CPU to communicate to external memory and peripherals and allows external LAN Adapter Bus masters unrestricted access to the internal Buffer RAM of the TMS38010. A full description of the bus cycles and their timing may be found in the electrical specifications.

The LAN Adapter bus is a multiplexed bus with address and data multiplexed on the LADO-LAD15 pins. All transfers on the LAN Adapter bus consist of 16-bit words. Parity is checked and generated on each data byte transfer on the LAN Adapter bus. Detection of a parity error by the TMS38010 causes a level-2 interrupt to occur.

Each cycle on the LAN Adapter bus extends for at least one LBCLK1/LBCLK2 period (333 ns). External devices may extend the bus transfer in increments of one LBCLK1/LBCLK2 period (wait states) by driving LBRDY low before the falling edge of LBCLK2. The bus transfer extends until the bus master samples LBRDY high at the falling edge of LBCLK2. When accessing the internal buffer RAM, neither the CPU nor external bus masters incur wait states.

The  $LI/\overline{D}$  pin is driven high or low at the beginning of each memory cycle to indicate whether data is being accessed or an instruction is being fetched. This information may be used to partition the memory map of the TMS38010 into a data space and an instruction space. Also, LAD15 will display the inverted value of status bit 8 of the Status Register during the address phase of the cycle which may be used to "page" the memory for extended memory applications. Note, however, that the TMS38010 does not decode either the  $LI/\overline{D}$  pin nor the LAD15 (page select) for accesses to internal buffer RAM or registers.

#### general purpose timer

The TMS38010 contains a general purpose timer which can be programmed to provide an interrupt to the TMS38010 CPU at regular intervals. This timer is intended as the hardware base for all protocol timers implemented in software.

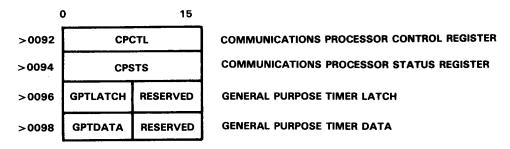

The general purpose timer is controlled by the CPU through two registers: the GPTLATCH register and the GPTDATA register. The GPTLATCH register is an 8-bit register loaded by the CPU as the initial timer value. It is read and written by the CPU as the most-significant byte of the word at address >0096 (">" of the word at address >0096 (">" of the word at address >0098 (" of the word at address of GPTLATCH when either the GPTDATA register is decremented to zero or the timer start bit of CPCNTL is toggled from 0 to 1.

A

The general purpose timer decrements the value in GPTDATA by a signal derived from LBCLK (3 MHz) divided by 512. When GPTDATA decrements to zero, the GPTINT bit of the CPSTS (CP Status) register is set. If the interrupt was enabled by setting the GPTIEN bit of the CPCTL (CP Control) register, a level-10 interrupt will be asserted to the CPU. The decrementer will be reloaded with the value in GPTLATCH on the next LBCLK cycle following the decrement to zero. Hence, the period of timer interrupts is (512)t<sub>C</sub>(GPTLATCH) where t<sub>C</sub> is the machine cycle time (333 ns).

#### control registers

In addition to the GPTLATCH and GPTDATA register, the TMS38010 Communications Processor contains two additional 16-bit registers: the CP Control (CPCTL) register and the CP Status (CPSTS) register. These 16-bit registers are used by the CPU as follows: 1) to control the operation of the general purpose timer, 2) to test the parity of the LAN Adapter bus, and 3) to store status information with respect to the CPU. These registers are shown in Figure 1.

FIGURE 1. TMS38010 CONTROL REGISTERS

#### **CPCTL** register

The CPCTL register controls the general purpose timer and the LAN Adapter bus parity checker/generator. Four bits are defined; the remaining bits are reserved. These bits are defined in Table 1.

**TABLE 1. CONTROL REGISTER BIT FUNCTIONS**

| BI | Т | NAME     | DESCRIPTION                              |

|----|---|----------|------------------------------------------|

| 0  |   | LPIEN    | Local Parity Interrupt Enable            |

| 1  |   | LPTST    | Local Parity Test                        |

| 2  | : | GPTIEN   | General Purpose Timer Interrupt Enable   |

| 3  | 3 | GPTSTART | General Purpose Timer Start              |

| 4  |   | RFLAG    | Reset Flag. Cleared upon hardware reset. |

#### **CPSTS** register

The CPSTS register provides additional status for the CPU, the status of the parity checkers, and the status of the general purpose timer. The bits of the CPSTS register are shown in Table 2.

**TABLE 2. CPSTS REGISTER BIT VALUES**

| BIT  | NAME   | DESCRIPTION                         |

|------|--------|-------------------------------------|

| 0    | ILLOP  | Illegal Operation Interrupt Request |

| 1    | AFI    | Arithmetic Fault Indicator          |

| 2    | LPE    | Local Parity Error                  |

| 3    | GPTINT | General Purpose Timer Interrupt     |

| 4    | SWINT  | Software Interrupt Indicator        |

| 5-11 |        | Reserved                            |

| 12   | TESTO  | Test 0 pin value                    |

| 13   | TEST1  | Test 1 pin value                    |

| 14   | TEST2  | Test 2 pin value                    |

| 15   | CLKDIV | CLKDIV pin value                    |

#### **buffer RAM**

The TMS38010 contains 1408 x 18-bits of random-access memory on chip. The RAM is implemented with a dynamic cell. Refresh is performed transparently to bus operation. The buffer RAM features single cycle access (no wait states) when accessed by either the CPU of the TMS38010 or external bus masters.

The buffer RAM is intended for storage of incoming and outgoing frame data as well as additional CPU software working storage. The RAM occupies addresses >0000 through >007E and >0580 through >0FFE in the memory space of the CPU.

#### test mode

The TMS38010 reatures a module-in-place test mode for board-level testing with the TMS38010 in circuit. This facilitates testing by bed-of-nails testers. This test mode is enabled by tying pins TEST, TESTO, TEST1 and TEST2 to ground and maintaining the clock input on MXTALIN. This has the effect of driving all outputs of the TMS38010 to the high-impendance state except MXTAL2. These pins may also be used to disable the on-chip buffer RAM. Table 3 illustrates the modes selectable through the test pins. All pin state combinations are reserved and should only be configured as shown in Table 3. When not used for these purposes, these pins should be left unconnected. An internal pullup drives these pins high when not externally connected.

**TABLE 3. TEST PIN MODES**

| TEST | TEST0 | TEST1 | TEST2 | MODE SELECTED        |

|------|-------|-------|-------|----------------------|

| NC   | NC    | NC    | NC    | Normal Operation     |

| LOW  | LOW   | LOW   | LOW   | Module-In-Place Test |

| NC   | LOW   | NC    | NC    | On-Chip RAM Disabled |

NC denotes no-connect

#### **CPU** instruction set summary

|          | DUAL-OPERAND INSTRUCTIONS — GENERAL SOURCE AND DESTINATION |                                                       |  |  |  |

|----------|------------------------------------------------------------|-------------------------------------------------------|--|--|--|

| MNEMONIC | MEANING                                                    | DESCRIPTION                                           |  |  |  |

| Α        | Add Words                                                  | (SA)+(DA) → (DA)                                      |  |  |  |

| AB       | Add Bytes                                                  | $(SA) + (DA) \rightarrow (DA)$                        |  |  |  |

| С        | Compare Words                                              | Compare (SA) to (DA) and set appropriate status bits. |  |  |  |

| СВ       | Compare Bytes                                              | Compare (SA) to (DA) and set appropriate status bits. |  |  |  |

| S        | Subtract Word                                              | $(DA) - (SA) \rightarrow (DA)$                        |  |  |  |

| SB       | Subtract Byte                                              | $(DA) - (SA) \rightarrow (DA)$                        |  |  |  |

| soc      | Set Ones Corresponding                                     | (DA) OR (SA) → (DA)                                   |  |  |  |

| SOCB     | Set Ones Corresponding Byte                                | (DA) OR (SA) → (DA)                                   |  |  |  |

| SZC      | Set Zeros Corresponding                                    | (DA) AND (SA) → (DA)                                  |  |  |  |

| SZCB     | Set Zeros Corresponding Byte                               | (DA) AND (SA) → (DA)                                  |  |  |  |

| MOV      | Move Word                                                  | (SA) → (DA)                                           |  |  |  |

| MOVB     | Move Byte                                                  | (SA) → (DA)                                           |  |  |  |

# CPU instruction set summary (continued)

|          | DUAL-OPERAND INSTRUCTIONS — REGISTER DESTINATION |                                                                                                                               |  |  |  |  |

|----------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MNEMONIC | MEANING                                          | DESCRIPTION                                                                                                                   |  |  |  |  |

| COC      | Compare Ones Corresponding                       | Test (D) to determine if 1's are in each bit position where 1's are in (SA).                                                  |  |  |  |  |

|          | •                                                | If so, set appropriate bits in status register.                                                                               |  |  |  |  |

| CZC      | Compare Zeros Corresponding                      | Test (D) to determine if O's are in each bit position where 1's are in (SA). If                                               |  |  |  |  |

|          | ,                                                | so, set appropriate bits in status register.                                                                                  |  |  |  |  |

| XOR      | Exclusive OR                                     | (D) XOR (SA) → (D)                                                                                                            |  |  |  |  |

| MPY      | Multiply                                         | Multiply unsigned (D) by unsigned (SA) and place unsigned 32-bit product in                                                   |  |  |  |  |

|          |                                                  | D (most significant) and D+ 1 (least significant).                                                                            |  |  |  |  |

| DIV      | Divide                                           | If unsigned (SA) is less than or equal to (D), perform no operation and set                                                   |  |  |  |  |

|          |                                                  | status register bit 4. Otherwise, divide unsigned (D) and $(D+1)$ by unsigned                                                 |  |  |  |  |

|          |                                                  | (SA). Quotient $\rightarrow$ (D), remainder $\rightarrow$ (D + 1)                                                             |  |  |  |  |

|          | SIG                                              | NED MULTIPLY AND DIVIDE                                                                                                       |  |  |  |  |

| MNEMONIC | MEANING                                          | DESCRIPTION                                                                                                                   |  |  |  |  |

| MPYS     | Signed Multiply                                  | Multiply signed 2's complement integer in register 0 by signed 2's                                                            |  |  |  |  |

|          |                                                  | complement integer in (SA) and place signed 32-bit product in register 0                                                      |  |  |  |  |

|          |                                                  | (most significant) and register 1 (least significant).                                                                        |  |  |  |  |

| DIVS     | Signed Divide                                    | If the quotient cannot be expressed as a signed 16-bit quantity (hex 8000                                                     |  |  |  |  |

|          |                                                  | is a valid negative number), set the appropriate status register bits,                                                        |  |  |  |  |

|          |                                                  | otherwise, divide the signed 2's complement integer in register 0 and regist                                                  |  |  |  |  |

|          |                                                  | 1 by the signed 2's complement integer at SA and place the signed quotien                                                     |  |  |  |  |

|          |                                                  | in register 0 and the signed remainder in register 1. The sign of the                                                         |  |  |  |  |

|          |                                                  | quotient is determined by algebraic rules. The sign of the remainder is                                                       |  |  |  |  |

|          |                                                  | the same as the sign of the dividend, and  REMAINDER  <  DIV .                                                                |  |  |  |  |

|          |                                                  | EXTENDED OPERATION                                                                                                            |  |  |  |  |

| MNEMONIC | MEANING                                          | DESCRIPTION                                                                                                                   |  |  |  |  |

| ХОР      | Extended Operation                               | Performs a context switch. The address of the trap vector is calculated                                                       |  |  |  |  |

|          |                                                  | by (>0040 + 4 × D).                                                                                                           |  |  |  |  |

|          | SING                                             | I<br>GLE-OPERAND INSTRUCTIONS                                                                                                 |  |  |  |  |

| MNEMONIC | MEANING                                          | DESCRIPTION                                                                                                                   |  |  |  |  |

| В        | Branch                                           | SA → (PC)                                                                                                                     |  |  |  |  |

| BL       | Branch and Link                                  | (PC) → (WR11), SA → (PC)                                                                                                      |  |  |  |  |

| BLWP     | Branch and Load Workspace Pointer                | $(SA) \rightarrow (WP)$ , $(SA + 2) \rightarrow (PC)$ , $(old WP) \rightarrow (new WR13)$ , $(old PC) \rightarrow (new WR13)$ |  |  |  |  |

|          | •                                                | WR14), (old ST) → (new WR15). The LIRQ inputs are not tested upon                                                             |  |  |  |  |

|          |                                                  | completion of the BLWP instruction.                                                                                           |  |  |  |  |

| CLR      | Clear                                            | 0 → (SA)                                                                                                                      |  |  |  |  |

| SETO     | Set to Ones                                      | FFFF → (SA)                                                                                                                   |  |  |  |  |

| INV      | Invert                                           | (SA) inverted → (SA)                                                                                                          |  |  |  |  |

| NEG      | Negate                                           | - (SA) → (SA)                                                                                                                 |  |  |  |  |

| ABS      | Absolute Value                                   | $ (SA)  \rightarrow (SA)$                                                                                                     |  |  |  |  |

| SWPB     | Swap bytes                                       | Bits 0-7 of (SA) $\rightarrow$ bits 8-15 of (SA); bits 8-15 of (SA) $\rightarrow$ bits 0-7 of (SA)                            |  |  |  |  |

| INC      | Increment                                        | (SA) + 1 → (SA)                                                                                                               |  |  |  |  |

| INCT     | Increment by 2                                   | (SA) + 2 → (SA)                                                                                                               |  |  |  |  |

| DEC      | Decrement                                        | (SA) - 1 → (SA)                                                                                                               |  |  |  |  |

| DECT     | Decrement by 2                                   | $(SA) - 2 \rightarrow (SA)$                                                                                                   |  |  |  |  |

|          |                                                  |                                                                                                                               |  |  |  |  |

#### **CPU** instruction set summary (concluded)

| MNEMONIC   MEANING   DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SHIFT INSTRUCTIONS           |                                  |                                                                       |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------------------|-----------------------------------------------------------------------|--|--|

| SRA Shift Right Circular SRC Shift Right Circular SRL Shift Right Circular Shift (W) right. Shift previous LSB into MSB. Shift (W) right. Shift previous LSB into MSB. Shift (W) right. Fill vacated bit positions with original MSB of (W).  Shift (W) right. Fill vacated bit positions with zeros.   JUMP INSTRUCTIONS  MNEMONIC  MEANING  DESCRIPTION  DESCRIPTION  DESCRIPTION  JUMP IF ST0 = 1.  JUMP Jump High Jump if ST0 = 1 and ST2 = 0.  JUMP if ST0 = 0 or ST2 = 1.  JUMP Jump Low or Equal Jump if ST0 = 0 or ST2 = 1.  JUMP Jump Jump Jump Jump if ST1 = 0 and ST2 = 0.  JUMP Jump No Carry Jump if ST3 = 0.  JUMP JUMP Not Equal Jump if ST3 = 0.  JUMP MORE Jump No Overflow Jump if ST3 = 0.  JUMP MORE Jump No Overflow Jump if ST3 = 1.  JUMP GENERAL STA = 0.  JUMP JUMP DUMP Jump if ST3 = 1.  JUMP JUMP ODE PRIVE STA = 1.  JUMP IF ST3 = 1.  JUMP ODE PRIVE STA = 1.  JUMP IF ST3 = 1.  JUMP IF ST4 = 0.  JUMP IF ST3 = 1.  JUMP IF ST4 = 0.  JUMP IF ST3 = 1.  JUMP IF ST3 = 1.  JUMP IF ST4 = 0.  JUMP IF ST4 = 0.  JUMP IF ST3 = 1.  JUMP IF ST3 = 1.  JUMP IF ST4 = 0.  JUMP IF ST4 =  | MNEMONIC                     | MEANING                          | DESCRIPTION                                                           |  |  |

| SRC Shift Right Circular Shift (W) right. Shift previous LSB into MSB. Shift Right Logical Shift (W) right. Fill vacated bit positions with zeros.    WIMP INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SLA                          | Shift Left Arithmetic            | Shift (W) left. Fill vacated bit positions with 0.                    |  |  |

| SRL Shift Right Logical Shift (W) right. Fill vacated bit positions with zeros.    JUMP INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SRA                          | Shift Right Arithmetic           | Shift (W) right. Fill vacated bit positions with original MSB of (W). |  |  |

| MNEMONIC   MEANING   DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SRC                          | Shift Right Circular             | Shift (W) right. Shift previous LSB into MSB.                         |  |  |

| MNEMONIC         MEANING         DESCRIPTION           JEQ         Jump Equal         Jump if ST2 = 1.           JGT         Jump Greater Than         Jump if ST1 = 1.           JH         Jump High         Jump if ST0 = 1 and ST2 = 0.           JHE         Jump High or Equal         Jump if ST0 = 0 and ST2 = 0.           JL         Jump Low         Jump if ST0 = 0 and ST2 = 0.           JLE         Jump Low or Equal         Jump if ST1 = 0 and ST2 = 0.           JLT         Jump Less Than         Jump if ST1 = 0 and ST2 = 0.           JMP         Jump         Jump unconditional.           JNC         Jump No Carry         Jump if ST3 = 0.           JND         Jump No Equal         Jump if ST2 = 0.           JNO         Jump No Overflow         Jump if ST4 = 0.           JOC         Jump Odd Parity         Jump if ST5 = 1.           IMMEDIATE REGISTER INSTRUCTIONS           MNEMONIC         MEANING         DESCRIPTION           AI         Add Immediate         (W) AND IOP → (W)           CI         Compare Immediate         Compare (W) to IOP and set appropriate status bits.           LI         Load Immediate         (W) OR IOP → (W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SRL                          | Shift Right Logical              | Shift (W) right. Fill vacated bit positions with zeros.               |  |  |

| JEQ         Jump Equal         Jump if ST2 = 1.           JGT         Jump Greater Than         Jump if ST0 = 1 and ST2 = 0.           JHE         Jump High or Equal         Jump if ST0 = 1 or ST2 = 1.           JL         Jump Low         Jump if ST0 = 0 and ST2 = 0.           JLE         Jump Low or Equal         Jump if ST0 = 0 or ST2 = 1.           JLT         Jump Less Than         Jump if ST1 = 0 and ST2 = 0.           JMP         Jump         Jump unconditional.           JNC         Jump No Carry         Jump if ST3 = 0.           JNE         Jump No Overflow         Jump if ST2 = 0.           JNO         Jump No Overflow         Jump if ST3 = 1.           JOP         Jump on Carry         Jump if ST3 = 1.           JOP         Jump Odd Parity         Jump if ST5 = 1.           IMMEDIATE REGISTER INSTRUCTIONS           MNEMONIC         MEANING         DESCRIPTION           AI         Add Immediate         (W) + IOP → (W)           CI         Compare Immediate         (W) AND IOP → (W)           CI         Compare Immediate         Compare (W) to IOP and set appropriate status bits.           LI         Load Immediate         (W) OR IOP → (W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                              |                                  | JUMP INSTRUCTIONS                                                     |  |  |

| JGT         Jump Greater Than         Jump if ST1 = 1.           JH         Jump High         Jump if ST0 = 1 and ST2 = 0.           JHE         Jump High or Equal         Jump if ST0 = 1 or ST2 = 1.           JL         Jump Low         Jump if ST0 = 0 and ST2 = 0.           JLE         Jump Low or Equal         Jump if ST1 = 0 and ST2 = 0.           JLT         Jump Less Than         Jump if ST3 = 0.           JMP         Jump No Carry         Jump if ST3 = 0.           JNC         Jump No Equal         Jump if ST2 = 0.           JNO         Jump No Overflow         Jump if ST3 = 1.           JOC         Jump on Carry         Jump if ST3 = 1.           JOP         Jump Odd Parity         Jump if ST5 = 1.           IMMEDIATE REGISTER INSTRUCTIONS           MNEMONIC         MEANING         DESCRIPTION           AI         Add Immediate         (W) + IOP → (W)           ANDI         AND Immediate         (W) AND IOP → (W)           CI         Compare Immediate         Compare (W) to IOP and set appropriate status bits.           LI         Load Immediate         (W) OR IOP → (W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | MNEMONIC                     | MEANING                          | DESCRIPTION                                                           |  |  |

| JH Jump High Jump if ST0 = 1 and ST2 = 0.  JHE Jump High or Equal Jump if ST0 = 1 or ST2 = 1.  JL Jump Low Jump if ST0 = 0 and ST2 = 0.  JLE Jump Low or Equal Jump if ST0 = 0 or ST2 = 1.  JLT Jump Less Than Jump if ST1 = 0 and ST2 = 0.  JMP Jump Jump Jump unconditional.  JNC Jump No Carry Jump if ST3 = 0.  JNE Jump Not Equal Jump if ST2 = 0.  JNO Jump No Overflow Jump if ST4 = 0.  JOC Jump no Carry Jump if ST3 = 1.  JOP Jump Odd Parity Jump if ST5 = 1.   IMMEDIATE REGISTER INSTRUCTIONS  MNEMONIC MEANING DESCRIPTION  AI Add Immediate (W) + IOP → (W)  ANDI AND Immediate (W) AND IOP → (W)  CI Compare Immediate Compare (W) to IOP and set appropriate status bits.  LI Load Immediate (W) OR IOP → (W)  ORI OR Immediate (W) OR IOP → (W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | JEQ                          | Jump Equal                       | Jump if ST2 = 1.                                                      |  |  |

| JHE Jump High or Equal Jump if ST0 = 1 or ST2 = 1.  JLE Jump Low Jump if ST0 = 0 and ST2 = 0.  JUMP Jump Low or Equal Jump if ST0 = 0 or ST2 = 1.  JUMP Jump Low ST1 = 0 and ST2 = 0.  JUMP Jump Jump Jump Jump Low or Equal JUMP if ST3 = 0.  JUMP No Carry Jump if ST3 = 0.  JUMP No Overflow Jump if ST4 = 0.  JUMP No Overflow Jump if ST3 = 1.  JUMP Jump Odd Parity Jump if ST5 = 1.  IMMEDIATE REGISTER INSTRUCTIONS  MNEMONIC MEANING DESCRIPTION  AI Add Immediate (W) + IOP → (W)  ANDI AND Immediate (W) AND IOP → (W)  CI Compare Immediate (W) AND IOP → (W)  CI Compare Immediate (W) OR IOP → (W)  ORI OR Immediate (W) OR IOP → (W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | JGT                          | Jump Greater Than                | Jump if ST1 = 1.                                                      |  |  |

| JL Jump Low Jump if ST0 = 0 and ST2 = 0.  JLE Jump Low or Equal Jump if ST0 = 0 or ST2 = 1.  JLT Jump Less Than Jump if ST1 = 0 and ST2 = 0.  JMP Jump Jump Jump unconditional.  JNC Jump No Carry Jump if ST3 = 0.  JNE Jump Not Equal Jump if ST2 = 0.  JNO Jump No Overflow Jump if ST4 = 0.  JOC Jump on Carry Jump if ST3 = 1.  JOP Jump Odd Parity Jump if ST5 = 1.  IMMEDIATE REGISTER INSTRUCTIONS  MNEMONIC MEANING DESCRIPTION  AI Add Immediate (W) + IOP → (W)  ANDI AND Immediate (W) AND IOP → (W)  CI Compare Immediate Compare (W) to IOP and set appropriate status bits.  LI Load Immediate (W) OR IOP → (W)  ORI OR Immediate (W) OR IOP → (W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | JH                           | Jump High                        | Jump if ST0=1 and ST2=0.                                              |  |  |

| JLE JUMP Low or Equal JUMP if ST0 = 0 or ST2 = 1.  JUMP JUMP JUMP JUMP JUMP JUMP JUMP JUMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | JHE                          | Jump High or Equal               | Jump if $ST0 = 1$ or $ST2 = 1$ .                                      |  |  |

| JLT Jump Less Than Jump if ST1 = 0 and ST2 = 0.  JMP Jump Jump Jump unconditional.  JNC Jump No Carry Jump if ST3 = 0.  JNE Jump Not Equal Jump if ST2 = 0.  JNO Jump No Overflow Jump if ST4 = 0.  JOC Jump on Carry Jump if ST5 = 1.  IMMEDIATE REGISTER INSTRUCTIONS  MNEMONIC MEANING DESCRIPTION  AI Add Immediate (W) + IOP → (W)  ANDI AND Immediate (W) AND IOP → (W)  CI Compare Immediate (W) AND IOP → (W)  CI Compare Immediate (W) OR IOP → (W)  ORI OR Immediate (W) OR IOP → (W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | JL                           | Jump Low                         | Jump if $ST0=0$ and $ST2=0$ .                                         |  |  |

| JMP Jump Jump No Carry Jump if ST3 = 0.  JNE Jump No Overflow Jump if ST4 = 0.  JOC Jump on Carry Jump if ST5 = 1.  JOP Jump Odd Parity  IMMEDIATE REGISTER INSTRUCTIONS  MNEMONIC  MEANING  ME | JLE                          | Jump Low or Equal                | Jump if $ST0=0$ or $ST2=1$ .                                          |  |  |

| JNC JUMP Not Equal JUMP if ST3 = 0.  JUMP if ST2 = 0.  JUMP No Overflow Jump if ST4 = 0.  JUMP if ST3 = 1.  JUMP if ST3 = 0.  JUMP if ST3 = 0.  JUMP if ST4 | JLT                          | Jump Less Than                   | Jump if $ST1 = 0$ and $ST2 = 0$ .                                     |  |  |

| JNE Jump Not Equal Jump if ST2 = 0.  JNO Jump No Overflow Jump if ST4 = 0.  JOC Jump on Carry Jump if ST3 = 1.  JOP Jump Odd Parity Jump if ST5 = 1.  IMMEDIATE REGISTER INSTRUCTIONS  MNEMONIC MEANING DESCRIPTION  AI Add Immediate (W) + IOP → (W)  ANDI AND Immediate (W) AND IOP → (W)  CI Compare Immediate (W) AND IOP → (W)  CI Load Immediate (DP → (W)  ORI OR IMMEdiate (W) OR IOP → (W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | JMP                          | Jump                             | Jump unconditional.                                                   |  |  |

| JNO Jump No Overflow JOC Jump on Carry JOP Jump Odd Parity  IMMEDIATE REGISTER INSTRUCTIONS  MNEMONIC  AI Add Immediate ANDI AND Immediate CI Compare Immediate LI Load Immediate ORI OR Immediate  ORI OR Immediate  (W) Jump if ST4 = 0.  Jump if ST3 = 1.  Jump if ST3 = 1.  Jump if ST5 = 1.  When if ST3 = 1.  Jump if ST4 = 0.  Jump if ST3 = 1.  Jump if ST4 = 0.  Jump if ST3 = 1.  Jump if ST4 = 0.  Jump if ST3 = 1.  Jump if ST4 = 0.  Jump if ST3 = 1.  Jump if ST4 = 0.  Jump if S | JNC                          | Jump No Carry                    | Jump if ST3 = 0.                                                      |  |  |

| JOC<br>JOPJump on Carry<br>Jump Odd ParityJump if ST3 = 1.<br>Jump if ST5 = 1.IMMEDIATE REGISTER INSTRUCTIONSMNEMONICMEANINGDESCRIPTIONAI<br>ANDI<br>ANDI<br>CI<br>Compare Immediate $(W) + IOP \rightarrow (W)$<br>$(W)$ AND $IOP \rightarrow (W)$<br>Compare $(W)$ to $IOP$ and set appropriate status bits.LI<br>ORILoad Immediate<br>OR Immediate $IOP \rightarrow (W)$<br>$(W)$ OR $IOP \rightarrow (W)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | JNE                          | Jump Not Equal                   | Jump if ST2 = 0.                                                      |  |  |

| JOP Jump Odd Parity Jump if ST5 = 1.  IMMEDIATE REGISTER INSTRUCTIONS  MNEMONIC MEANING DESCRIPTION  Al Add Immediate (W) + IOP → (W)  ANDI AND Immediate (W) AND IOP → (W)  CI Compare Immediate (W) AND IOP and set appropriate status bits.  LI Load Immediate IOP → (W)  ORI OR Immediate (W) OR IOP → (W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | JNO                          | Jump No Overflow                 | Jump if ST4=0.                                                        |  |  |

| IMMEDIATE REGISTER INSTRUCTIONS           MNEMONIC         MEANING         DESCRIPTION           AI         Add Immediate         (W) + IOP → (W)           ANDI         AND Immediate         (W) AND IOP → (W)           CI         Compare Immediate         Compare (W) to IOP and set appropriate status bits.           LI         Load Immediate         IOP → (W)           ORI         OR Immediate         (W) OR IOP → (W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | JOC                          | Jump on Carry                    | Jump if ST3 = 1.                                                      |  |  |

| MNEMONIC         MEANING         DESCRIPTION           AI         Add Immediate         (W) + IOP → (W)           ANDI         AND Immediate         (W) AND IOP → (W)           CI         Compare Immediate         Compare (W) to IOP and set appropriate status bits.           LI         Load Immediate         IOP → (W)           ORI         OR Immediate         (W) OR IOP → (W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | JOP                          | Jump Odd Parity                  | Jump if ST5 = 1.                                                      |  |  |

| AI Add Immediate (W) + IOP → (W)  ANDI AND Immediate (W) AND IOP → (W)  CI Compare Immediate Compare (W) to IOP and set appropriate status bits.  LI Load Immediate IOP → (W)  ORI OR Immediate (W) OR IOP → (W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                              | IMMEC                            | DIATE REGISTER INSTRUCTIONS                                           |  |  |

| ANDI AND Immediate (W) AND IOP → (W)  CI Compare Immediate Compare (W) to IOP and set appropriate status bits.  LI Load Immediate IOP → (W)  ORI OR Immediate (W) OR IOP → (W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MNEMONIC MEANING DESCRIPTION |                                  |                                                                       |  |  |

| CI Compare Immediate Compare (W) to IOP and set appropriate status bits.  LI Load Immediate IOP → (W)  ORI OR Immediate (W) OR IOP → (W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Al                           | Add Immediate                    | $(W) + IOP \rightarrow (W)$                                           |  |  |

| LI         Load Immediate         IOP → (W)           ORI         OR Immediate         (W) OR IOP → (W)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ANDI                         | AND Immediate                    | (W) AND IOP → (W)                                                     |  |  |