Datasheet, April 2010

# 2ED020I06-FI Dual IGBT Driver IC

## Power Managment & Drives

Never stop thinking.

#### 2ED020I06-FI Revision History: 2010-04-20 Datasheet

| Previous Version:                            |  |  |  |  |  |  |

|----------------------------------------------|--|--|--|--|--|--|

| Subjects (major changes since last revision) |  |  |  |  |  |  |

|                                              |  |  |  |  |  |  |

|                                              |  |  |  |  |  |  |

|                                              |  |  |  |  |  |  |

|                                              |  |  |  |  |  |  |

For questions on technology, delivery and prices, please contact the Infineon offices in Germany or the Infineon companies and representatives worldwide:

See our webpage at http://www.infineon.com/gatedriver

Edition 2010-04-20

Published by Infineon Technologies AG, Am Campeon 1-12, D-85579 Neubiberg © Infineon 2007.

C Infineon 2007. All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

## Dual IGBT Driver IC 2ED020I06-FI

#### **Product Highlights**

- Fully opera tional to ±650V

- Power supply operating range from 14 to 18 V

- Gate drive currents of +1 A / -2 A

- · Matched propagation delay for both channels

- High dV/dt immunity

- Low power consumption

#### Features

- · Floating high side driver

- Undervoltage lockout for both channels

- 3.3 V and 5 V TTL compatible inputs

- · CMOS Schmitt-triggered inputs with pull-down

- Non-inverting inputs

- · Interlocking inputs

- Dedicated shutdown input with pull-up

- · RoHS compliant

| PG-DSO-18-2 |

|-------------|

| Туре         | Ordering Code | Package     | Packaging |

|--------------|---------------|-------------|-----------|

| 2ED020I06-FI |               | PG-DSO-18-2 | Tape&Reel |

#### Overview

## 1 Overview

The 2ED020I06-FI is a high voltage, high speed power MOSFET and IGBT driver with interlocking high and low side referenced outputs. The floating high side driver may be supplied directly or by means of a bootstrap diode and capacitor. In addition to the logic input of each driver the 2ED020I06-FI is equipped with a dedicated shutdown input. All logic inputs are compatible with 3.3 V and 5 V TTL. The output drivers feature a high pulse current buffer stage designed for minimum driver cross-conduction. Propagation delays are matched to simplify use in high frequency applications. Both drivers are designed to drive an N-channel power MOSFET or IGBT which operate up to 650V.

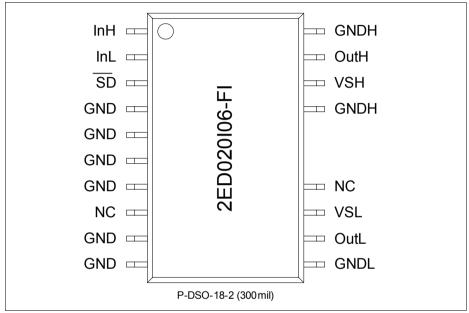

Pin Configuration and Functionality

## 2 Pin Configuration and Functionality

## 2.1 Pin Configuration

Figure 1 Pin Configuration (top view)

## 2.2 Pin Definitions and Functions

| Pin     | Symbol    | Function                                 |

|---------|-----------|------------------------------------------|

| 1       | InH       | Logic input for high side driver         |

| 2       | InL       | Logic input for low side driver          |

| 3       | SD        | Logic input for shutdown of both drivers |

| 4       | GND       | Common ground                            |

| 5       | GND       | Connect to GND                           |

| 6       | GND       | Connect to GND                           |

| 7       | GND       | Connect to GND                           |

| 8       | n.c.      | Do not connect, Pin must stay open       |

| Table 1 | Pin Descr | iption                                   |

#### Pin Configuration and Functionality

| Pin     | Symbol     | Function                            |

|---------|------------|-------------------------------------|

| 9       | GND        | Connect to GND                      |

| 10      | GND        | Connect to GND                      |

| 11      | GNDL       | Low side power ground <sup>1)</sup> |

| 12      | OutL       | Low side gate driver output         |

| 13      | VSL        | Low side supply voltage             |

| 14      | n.c.       | (not connected)                     |

| 15      | n.e.       | (not existing)                      |

| 16      | n.e.       | (not existing)                      |

| 17      | GNDH       | High side (power) ground            |

| 18      | VSH        | High side supply voltage            |

| 19      | OutH       | High side gate driver output        |

| 20      | GNDH       | High side (power) ground            |

| Table 1 | Pin Descri | ption (cont'd)                      |

1) Please note : GNDL has to be connected directly to GND

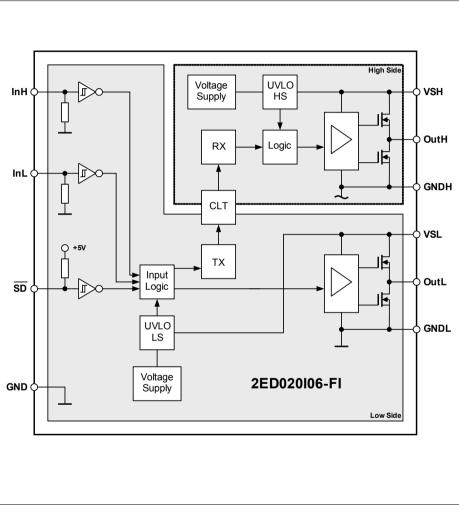

**Block Diagram**

## 3 Block Diagram

Figure 2 Block Diagram

**Functional Description**

## 4 Functional Description

## 4.1 Power Supply

The power supply of both sides, "VSL" and "VSH", is monitored by an undervoltage lockout block (UVLO) which enables operation of the corresponding side when the supply voltage reaches the "on" threshold. Afterwards the internal voltage reference and the biasing circuit are enabled. When the supply voltage (VSL, VSH) drops below the "off" threshold, the circuit is disabled.

## 4.2 Logic Inputs

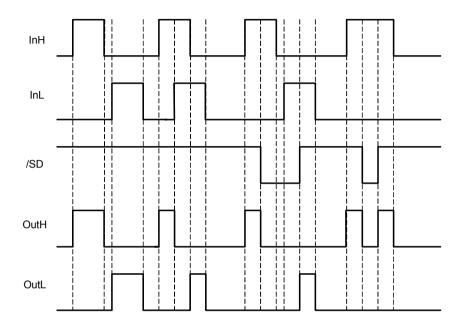

The logic inputs InH, InL and  $\overline{SD}$  are fed into Schmitt-Triggers with thresholds compatible to 3.3V and 5V TTL. When  $\overline{SD}$  is enabled (low), InH and InL are disabled. If InH is high (while InL is low), OutH is enabled and vice versa. However, if both signals are high, they are internally disabled until one of them gets low again. This is due to the interlocking logic of the device. See Figure 3 (section 4.7).

#### 4.3 Gate Driver

2ED020I06-FI features two hard-switching gate drivers with N-channel output stages capable to source 1A and to sink 2A peak current. Both drivers are equipped with active-low-clamping capability. Furthermore, they feature a large ground bounce ruggedness in order to compensate ground bounces caused by a turn-off of the driven IGBT.

## 4.4 Coreless Transformer (CLT)

In order to enable signal transmission across the isolation barrier between low-side and high-side driver, a transformer based on CLT-Technology is employed. Signals, that are to be transmitted, are specially encoded by the transmitter and correspondingly restored by the receiver. In this way EMI due to variations of GNDH ( $dV_{GNDH}/dt$ ) or the magnetic flux density (dH/dt) can be suppresed. To compensate the additional propagation delay of transmitter, level shifter and receiver, a dedicated propagation delay is introduced into the low-side driver.

## High and Low Side Driver 2ED020I06-FI

**Functional Description**

#### 4.5 Diagrams

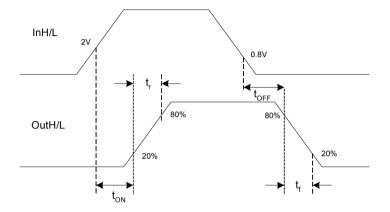

Figure 3 Input/Output Timing Diagram

## 5 Electrical Parameters

#### 5.1 Absolute Maximum Ratings

*Note:* Absolute maximum ratings are defined as ratings, which when being exceeded may lead to destruction of the integrated circuit. Unless otherwise noted all parameters refer to GND.

| Parameter                                                   | Symbol                                    | Limi | t Values  | Unit | Remarks                           |  |

|-------------------------------------------------------------|-------------------------------------------|------|-----------|------|-----------------------------------|--|

|                                                             |                                           | min. | max.      |      |                                   |  |

| High side ground                                            | GNDH                                      | -650 | 650       | V    |                                   |  |

| High side supply voltage                                    | VSH                                       | -0.3 | 20        | V    | 1)                                |  |

| High side gate driver output                                | OutH                                      | -0.3 | VSH + 0.3 | V    | 1)                                |  |

| Low side ground                                             | GNDL                                      | -0.3 | 5.3       | V    |                                   |  |

| Low side supply voltage                                     | VSL                                       | -0.3 | 20        | V    | 2)                                |  |

| Low side gate driver output                                 | OutL                                      | -0.3 | VSL + 0.3 | V    | 3)                                |  |

| Logic input voltages<br>(InH, InL, SD)                      | V <sub>IN</sub>                           | -0.3 | 5.3       | V    |                                   |  |

| High side ground, voltage transient                         | $\mathrm{dV}_{\mathrm{GNDH}}/\mathrm{dt}$ | -50  | 50        | V/ns |                                   |  |

| ESD Capability                                              | V <sub>ESD</sub>                          |      | 2         | kV   | <sup>4)</sup> Human<br>Body Model |  |

| Package power disipation $@T_A = 25^{\circ}C$               | P <sub>D</sub>                            |      | 1.4       | W    | 5)                                |  |

| Thermal resistance (both chips active), junction to ambient | R <sub>THJA</sub>                         |      | 90        | K/W  | 6)                                |  |

| Thermal resistance (high side chip), junction to ambient    | R <sub>THJA(HS)</sub>                     |      | 110       | K/W  | 6)                                |  |

| Thermal resistance (low side chip), junction to ambient     | R <sub>THJA(LS)</sub>                     |      | 110       | K/W  | 6)                                |  |

| Junction temperature                                        | T <sub>J</sub>                            |      | 150       | °C   |                                   |  |

| Storage temperature                                         | Ts                                        | -55  | 150       | °C   |                                   |  |

<sup>1)</sup> With reference to high side ground GNDH.

2) With respect to both GND and GNDL.

<sup>3)</sup> With respect to GNDL.

<sup>4)</sup> According to EIA/JESD22-A114-B (discharging a 100pF capacitor through a 1.5kΩ series resistor).

<sup>5)</sup> Considering Rth(both chips active)=90K/W

<sup>6)</sup> Device soldered to reference PCB without cooling area

#### 5.2 **Operating Range**

Note: Within the operating range the IC operates as described in the functional description. Unless otherwise noted all parameters refer to GND.

| Parameter                              | Symbol          | Li   | nit Values | Unit | Remarks                                                  |  |

|----------------------------------------|-----------------|------|------------|------|----------------------------------------------------------|--|

|                                        |                 | min. | max.       |      |                                                          |  |

| High side ground                       | GNDH            | -650 | 650        | V    |                                                          |  |

| High side supply voltage               | VSH             | 14   | 18         | V    | 1)                                                       |  |

| Low side supply voltage                | VSL             | 14   | 18         | V    | 2)                                                       |  |

| Logic input voltages<br>(InH, InL, SD) | V <sub>IN</sub> | 0    | 5          | V    |                                                          |  |

| Junction temperature                   | TJ              | -40  | 105        | °C   | Industrial<br>applications,<br>useful lifetime<br>87600h |  |

| Junction temperature                   | TJ              | -40  | 125        | °C   | Other<br>applications,<br>useful lifetime<br>15000h      |  |

<sup>1)</sup> With reference to high side ground GNDH.

2) With respect to both GND and GNDL.

#### 5.3 Electrical Characteristics

Note: The electrical characteristics involve the spread of values for the supply voltages, load and junction temperature given below. Typical values represent the median values, which are related to production processes. Unless otherwise noted all voltages are given with respect to ground (GND). VSL = VSH - GNDH = 15V,  $C_L = 1nF$ ,  $T_A = 25$  °C. Positive currents are assumed to be flowing into pins.

#### Voltage Supply

| Parameter                    | Symbol            | Limit Values |     |      | Unit | Test Condition            |

|------------------------------|-------------------|--------------|-----|------|------|---------------------------|

|                              |                   | min.         | typ | max. |      |                           |

| High side<br>leakage current | I <sub>GNDH</sub> | _            | 0   |      | μA   | GNDH = 1.2kV<br>GNDL = 0V |

## Voltage Supply (cont'd)

| Parameter                                       | Symbol           | I    | Limit Values |      |    | <b>Test Condition</b>                       |

|-------------------------------------------------|------------------|------|--------------|------|----|---------------------------------------------|

|                                                 |                  | min. | typ          | max. |    |                                             |

| High side quiescent supply                      | I <sub>VSH</sub> | _    | 2.4          | 3.2  | mA | $VSH = 15V^{1)}$                            |

| current                                         |                  | _    | 2.3          | 3.2  | mA | $VSH = 15 V^{1}$<br>T <sub>J</sub> = 125 °C |

| High side undervoltage lockout, upper threshold | $V_{VSH}^{(1)}$  | 10.9 | 12.2         | 13.5 | V  |                                             |

| High side undervoltage lockout, lower threshold | $V_{VSH}^{(1)}$  | _    | 11.2         | _    | V  |                                             |

| High side undervoltage lockout hysteresis       | $\Delta V_{VSH}$ | 0.7  | 1            | 1.3  | V  |                                             |

| Low side quiescent supply                       | I <sub>VSL</sub> | _    | 3.9          | 5.0  | mA | VSL = 15V                                   |

| current                                         |                  |      | 3.9          | 5.5  | mA | $VSL = 15V$ $T_{J} = 125 \text{ °C}$        |

| Low side undervoltage lockout, upper threshold  | V <sub>VSL</sub> | 10.7 | 12           | 13.3 | V  |                                             |

| Low side undervoltage lockout, lower threshold  | V <sub>VSL</sub> | _    | 11           | _    | V  |                                             |

| Low side undervoltage lockout hysteresis        | $\Delta V_{VSL}$ | 0.7  | 1            | 1.3  | V  |                                             |

<sup>1)</sup> With reference to high side ground GNDH.

#### Logic Inputs

| Parameter                                          | Symbol          | L    | Limit Values |      |    | <b>Test Condition</b> |

|----------------------------------------------------|-----------------|------|--------------|------|----|-----------------------|

|                                                    |                 | min. | typ          | max. |    |                       |

| Logic "1" input voltages<br>(InH, InL, <u>SD</u> ) | V <sub>IN</sub> | 2    |              | _    | V  |                       |

| Logic "0" input voltages<br>(InH, InL, <u>SD</u> ) | V <sub>IN</sub> | -    |              | 0.8  | V  |                       |

| Logic "1" input currents<br>(InH, InL)             | I <sub>IN</sub> | -    | 40           | 55   | μA | $V_{IN} = 5 V$        |

| Logic "0" input currents<br>(InH, InL)             | I <sub>IN</sub> | -    | 0            | _    | μA | $V_{IN} = 0 V$        |

## Logic Inputs (cont'd)

| Parameter                                                        | Symbol Limit Values |      |     | Unit | <b>Test Condition</b> |                |

|------------------------------------------------------------------|---------------------|------|-----|------|-----------------------|----------------|

|                                                                  |                     | min. | typ | max. |                       |                |

| $\frac{\text{Logic "1" input currents}}{(\overline{\text{SD}})}$ | I <sub>IN</sub>     | —    | 0   | _    | μΑ                    | $V_{IN} = 5 V$ |

| $\frac{\text{Logic "0" input currents}}{(\overline{\text{SD}})}$ | I <sub>IN</sub>     | -60  | -40 | _    | μΑ                    | $V_{IN} = 0 V$ |

## **Gate Drivers**

| Parameter                                | Symbol                          | Limit Values |     | Unit | Test Condition |                                                                 |

|------------------------------------------|---------------------------------|--------------|-----|------|----------------|-----------------------------------------------------------------|

|                                          |                                 | min.         | typ | max. |                |                                                                 |

| High side high level output voltage      | $V_{VSH} - V_{OutH}$            | _            | 1.4 | 1.7  | V              | $I_{OutH} = -1mA$ $V_{InH} = 5V$                                |

| High side low level output voltage       | V <sub>OutH</sub> <sup>1)</sup> | —            | _   | 0.1  | V              | $I_{OutH} = 1mA$ $V_{InH} = 0V$                                 |

| Low side high level output voltage       | $V_{VSL} - V_{OutL}$            | _            | 1.4 | 1.7  | V              | $I_{OutL} = -1 mA$ $V_{InL} = 5V$                               |

| Low side low level output voltage        | V <sub>OutL</sub>               | _            | _   | 0.1  | V              | $I_{OutL} = 1mA$ $V_{InL} = 0V$                                 |

| Output high peak current<br>(OutL, OutH) | I <sub>Out</sub>                | —            | —   | -1   | А              | $V_{IN} = 5V$ $V_{Out} = 0V$                                    |

| Output low peak current<br>(OutL, OutH)  | I <sub>Out</sub>                | 2            | _   | -    | А              | $V_{IN} = 0V$ $V_{Out} = 15V$                                   |

| High side active low clamping            | V <sub>OutH</sub> <sup>1)</sup> | _            | 2.6 | 3    | V              | InH =0V, VSH open<br>I <sub>OutH</sub> =200mA                   |

|                                          |                                 |              | 2.7 | 3.2  | V              | InH =0V, VSH open<br>I <sub>OutH</sub> =200mA<br>$T_J$ = 125 °C |

| Low side active low clamping             | V <sub>OutL</sub>               | —            | 2.6 | 3    | V              | InL =0V, VSL open<br>I <sub>OutL</sub> =200mA                   |

|                                          |                                 |              | 2.7 | 3.2  | V              | InL =0V, VSL open<br>$I_{OutL}$ =200mA<br>$T_J$ = 125 °C        |

<sup>1)</sup> With reference to high side ground GNDH.

#### **Dynamic Characteristics**

| Parameter                                        | Symbol            | Limit Values |     |      | Unit | <b>Test Condition</b>                           |

|--------------------------------------------------|-------------------|--------------|-----|------|------|-------------------------------------------------|

|                                                  |                   | min.         | typ | max. |      |                                                 |

| Turn-on propagation delay                        | t <sub>on</sub>   | _            | 85  | 105  | ns   | GNDH = 0V<br>20% V <sub>out</sub>               |

|                                                  |                   | _            | 95  | 120  | ns   | GNDH = 0V<br>$20\% V_{out}$<br>$T_{J} = 125 °C$ |

| Turn-off propagation delay                       | t <sub>OFF</sub>  | _            | 85  | 115  | ns   | 80% V <sub>out</sub>                            |

|                                                  |                   | —            | 100 | 130  | ns   | $80\% V_{out}$ $T_{J} = 125 °C$                 |

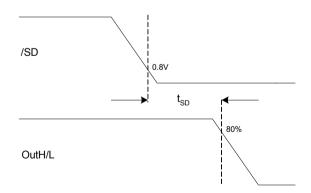

| Shutdown propagation delay                       | t <sub>SD</sub>   | _            | 85  | 115  | ns   | 80% V <sub>out</sub>                            |

|                                                  |                   | _            | 100 | 130  | ns   | $80\% V_{out}$<br>T <sub>J</sub> = 125 °C       |

| Turn-on rise time                                | t <sub>r</sub>    | _            | 20  | 40   | ns   | 20% to 80% $V_{\rm out}$                        |

|                                                  |                   | _            | 30  | 50   | ns   | 20% to 80% $V_{out}$<br>T <sub>J</sub> = 125 °C |

| Turn-off fall time                               | t <sub>f</sub>    | _            | 20  | 35   | ns   | 80% to 20% $\mathrm{V}_{\mathrm{out}}$          |

|                                                  |                   | _            | 25  | 40   | ns   | 80% to 20% $V_{out}$<br>T <sub>J</sub> = 125 °C |

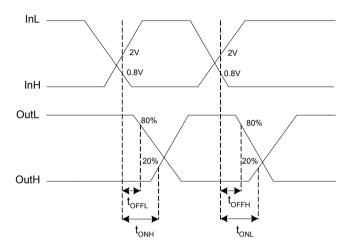

| Delay mismatch (high & low side turn-on/off)     | Δt                | _            | 15  | 25   | ns   | $T_J = 25^{\circ}C$<br>see Figure 6             |

|                                                  |                   | _            | 15  | 30   | ns   | $T_J = 125^{\circ}C$<br>see Figure 6            |

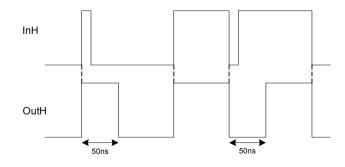

| Minimum turn-on input<br>(InH, InL) pulse width  | t <sub>pON</sub>  | _            | 50  | 75   | ns   | 1)                                              |

|                                                  |                   | _            | 55  | 80   | ns   | <sup>1)</sup> $T_J = 125^{\circ}C$              |

| Minimum turn-off input<br>(InH, InL) pulse width | t <sub>pOFF</sub> | _            | 50  | 75   | ns   | 1)                                              |

|                                                  |                   |              | 55  | 80   | ns   | <sup>1)</sup> $T_J = 125 \ ^{\circ}C$           |

<sup>1)</sup> InH-Pulses shorter than the "minimum turn-on(off) input pulse width" are prolonged to 50ns (See Figure 7). InL-Input doesn't have this feature.

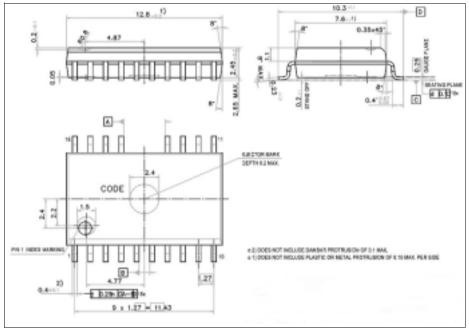

#### Package Outline

## 6 Package Outline

Note: dimensions are given in mm.

#### 6.1 Soldering Profile

The soldering profile qualified for 2ED020I06-FI (according to the standard IPC/JEDEC J-STD-020C) is moisture sensitivity level 3. The peak reflow temperature for its package (volume < 350 mm<sup>3</sup>) is 260 +0/-5 °C.

Diagrams

## 7 Diagrams

#### Figure 4 Switching Time Waveform Definition

Figure 5 Shutdown Waveform Definition

#### Diagrams

$\Delta t = max (|t_{ONH} - t_{OFFL}| , |t_{OFFH} - t_{ONL}|)$

#### Figure 6 Delay Matching Waveform Definitions

Figure 7 Short InH-Pulses Prolongation

**Application Advices**

## 8 Application Advices

## 8.1 Power Supply

a) The connection of a capacitor (>10nF) as close as possible to the supply pins VSH, VSL is recommended for avoiding that possible oscillations in the supply voltage can cause erroneous operation of the output driver stage. Total value of capacitance connected to the supply terminals has to be determined by taking into account gatecharge, peak current, supply voltage and kind of power supply.

b) If a bootstrap power supply for the high side driver is applied, a resistor of  $10\Omega$  minimum in series with the bootstrap diode is required.

## High and Low Side Driver 2ED020I06-FI

**Application Advices**

## Total Quality Management

Qualität hat für uns eine umfassende Bedeutung. Wir wollen allen Ihren Ansprüchen in der bestmöglichen Weise gerecht werden. Es geht uns also nicht nur um die Produktqualität – unsere Anstrengungen gelten gleichermaßen der Lieferqualität und Logistik, dem Service und Support sowie allen sonstigen Beratungs- und Betreuungsleistungen.

Dazu gehört eine bestimmte Geisteshaltung unserer Mitarbeiter. Total Quality im Denken und Handeln gegenüber Kollegen, Lieferanten und Ihnen, unserem Kunden. Unsere Leitlinie ist jede Aufgabe mit "Null Fehlern" zu lösen – in offener Sichtweise auch über den eigenen Arbeitsplatz hinaus – und uns ständig zu verbessern.

Unternehmensweit orientieren wir uns dabei auch an "top" (Time Optimized Processes), um Ihnen durch größere Schnelligkeit den entscheidenden Wettbewerbsvorsprung zu verschaffen.

Geben Sie uns die Chance, hohe Leistung durch umfassende Qualität zu beweisen.

Wir werden Sie überzeugen.

Quality takes on an all encompassing significance at Infineon AG. For us it means living up to each and every one of your demands in the best possible way. So we are not only concerned with product quality. We direct our efforts equally at quality of supply and logistics, service and support, as well as all the other ways in which we advise and attend to you.

Part of this is the very special attitude of our staff. Total Quality in thought and deed, towards co-workers, suppliers and you, our customer. Our guideline is "do everything with zero defects", in an open manner that is demonstrated beyond your immediate workplace, and to constantly improve.

Throughout the corporation we also think in terms of Time Optimized Processes (top), greater speed on our part to give you that decisive competitive edge.

Give us the chance to prove the best of performance through the best of quality – you will be convinced.

http://www.infineon.com