# 6

# P3C218 LATCHED HIGH-SPEED 16Kx16 STATIC RAM

#### **FEATURES**

- **■** Full CMOS Design

- Supports Processor Speeds to 60MHz

- On-Chip Address and Chip Enable Latch

- On-Chip Input Data Latch

- Byte Write Strobe Controls

- Dual Chip Enable for Depth Expansion

- Single 3.3V ±0.3V Power Supply

- **■** Power Down Mode When Deselected

- Output Enable Control

- TTL-Compatible I/O

- Outputs Drive up to 85pF

- 52-Pin PLCC Package

### DESCRIPTION

Z.

24

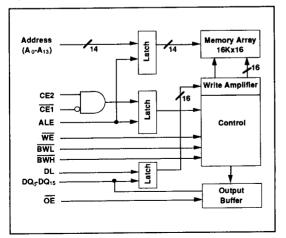

The P3C218 is a 262,144-bit CMOS static RAM organized as 16K words, each 16 bits wide, for cache applications. The SCRAM contains on-chip address and chip enable latches controlled by ALE. A separate control, DL, latches the input data. All latches are transparent when the latch enable controls are HIGH, so the P3C218 can be used as a general-purpose asynchronous 16Kx16 SRAM by connecting ALE and DL to Vcc.

The address and chip enable latches make the P3C218 ideally suited for R3000 cache applications. Four units make up a 64KByte i- (or d-) cache; the two chip enable controls facilitate easy expansion to 128KByte. Individuals byte write operations are possible using  $\overline{BWL}$  and  $\overline{BWH}$  strobes to qualify the  $\overline{WE}$  control, a useful feature for ix86 cache applications.

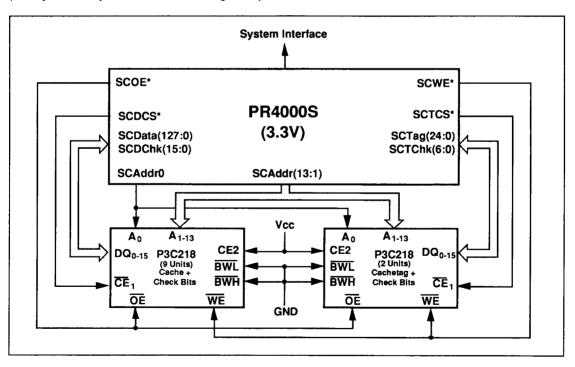

The P3C218 operates from a  $3.3V\pm0.3V$  tolerance power supply. Power dissipation is 1.0W (max.) when active, and only 100mW in standby mode. The P3C218 can be used as the secondary cache for low-cost R4000S workstations; 11 units form a 256KByte cache, expandable to 512KBytes with 22 units.

With access times of 15ns, the P3C218 can support all popular microprocessors to 60MHz while keeping chip count and power dissipation low. Outputs can drive up to 85pF loads, so no external buffers are required.

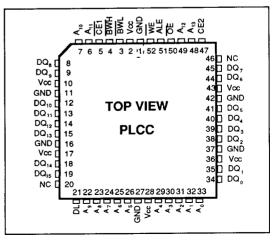

The P3C218 is manufactured using PACE III Technology, and is available in a 52-pin PLCC package, providing excellent board density.

# **FUNCTIONAL DIAGRAM**

### PIN CONFIGURATION

PERFORMANCE

SEMICONDUCTOR CORPORATION

Means Quality, Service and Speed

## **TRUTH TABLE**

|     |                 |     |     |    |    |                 | INPUT/OUTPUT |          |

|-----|-----------------|-----|-----|----|----|-----------------|--------------|----------|

| CE, | CE <sub>2</sub> | BWH | BWL | WE | ŌĒ | MODE            | Bits 15-8    | Bits 7-0 |

| Н   | х               | x   | Х   | x  | х  | Deselected      | High Z       | High Z   |

| x   | L               | x   | x   | x  | x  |                 |              |          |

| L   | Н               | x   | х   | Н  | н  | Output Disabled | High Z       | High Z   |

| L   | Н               | х   | х   | н  | L  | Read Word       | Data Out     | Data Out |

| L   | н               | L   | н   | L  | x  | Write High Byte | Data In      | High Z   |

| L   | н               | н   | L   | L  | x  | Write Low Byte  | High Z       | Data in  |

| L   | н               | L   | L   | L  | x  | Write Word      | Data In      | Data In  |

## **APPLICATION EXAMPLE: 3.3V PR4000 Secondary Cache**

(256KByte cache in joint instruction-data configuration)

4/28/92 6-16