# **TFA9842AJ**

# 7.5 W stereo power amplifier with volume control

Rev. 01 — 28 April 2006

**Preliminary specification**

### 1. General description

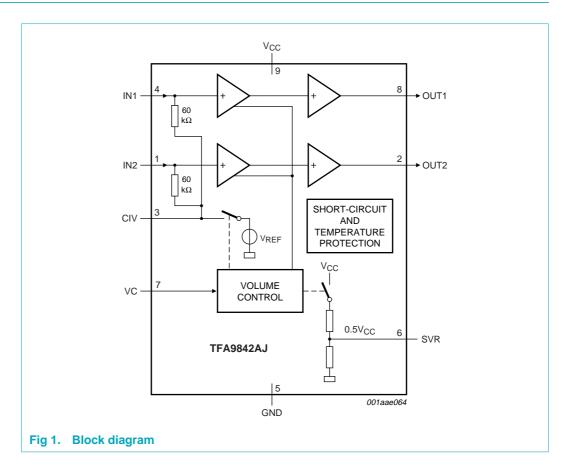

The TFA9842AJ contains two identical audio power amplifiers. The TFA9842AJ can be used as two Single-Ended (SE) channels with a volume control. The maximum gain is 26 dB.

The TFA9842AJ comes in a 9-pin DIL-bent-SIL (DBS9P) power package. The TFA9842AJ is pin compatible with the TFA9843AJ, TFA9843(B)J, TFA9842(B)J and TFA9841J. The difference between the TFA9843AJ and the TFA9843(B)J, TFA9842(B)J, TFA9841J is the functionality of pin 7. The TFA9843AJ has a Volume Control (VC) on pin 7. The TFA9843(B)J, TFA9842(B)J and TFA9841J have a mode select (MODE) on pin 7.

The TFA9842AJ contains a unique protection circuit that is solely based on multiple temperature measurements inside the chip. This gives maximum output power for all supply voltages and load conditions with no unnecessary audio holes. Almost any supply voltage and load impedance combination can be made as long as thermal boundary conditions (number of channels used, external heatsink and ambient temperature) allow it.

#### 2. Features

- 2 channel SE: 1 W to 7.5 W operation possibility

- Soft clipping

- Input clamps

- Volume control

- Standby and Mute mode

- No on or off switching plops

- Low standby current

- High supply voltage ripple rejection

- Outputs short-circuit protected to ground, supply and across the load

- Thermally protected

- Pin compatible with the TFA9843AJ, TFA9843(B)J, TFA9842(B)J and TFA9841J

# 3. Applications

- CRT TV and LCD TV

- Monitors

- PC speakers

- Boom box

- Mini and micro audio receivers

## 4. Quick reference data

Table 1. Quick reference data

| Table 1.            | Quick reference data            |                                                         |              |     |     |      |

|---------------------|---------------------------------|---------------------------------------------------------|--------------|-----|-----|------|

| Symbol              | Parameter                       | Conditions                                              | Min          | Тур | Max | Unit |

| $V_{CC}$            | supply voltage                  | operating                                               | <u>[1]</u> 9 | 17  | 28  | V    |

| $I_q$               | quiescent current               | $V_{CC} = 17 \text{ V};$ $R_L = \infty \Omega$          | -            | 60  | 100 | mA   |

| $I_{CC(stb)}$       | standby supply current          | $V_{CC} = 17 \text{ V};$<br>$V_{I(VC)} < 0.8 \text{ V}$ | -            | -   | 150 | μΑ   |

| P <sub>o</sub>      | output power                    | THD = 10 %;<br>$R_L = 4 \Omega$ ;<br>$V_{CC} = 17 V$    | 7            | 7.5 | -   | W    |

| THD                 | total harmonic distortion       | $P_0 = 1 W$                                             | -            | 0.1 | 0.5 | %    |

| G <sub>v(max)</sub> | maximum voltage gain            | $V_{I(VC)} > 5.0 \text{ V}$                             | 25           | 26  | 27  | dB   |

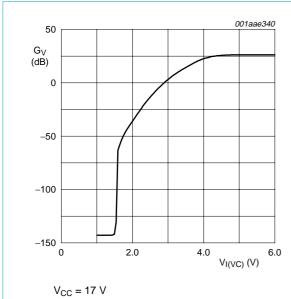

| $\Delta G_{v}$      | voltage gain range              | 1.5 V < V <sub>I(VC)</sub> < 5.0 V                      | -            | 80  | -   | dB   |

| SVRR                | supply voltage ripple rejection | $f_{ripple} = 1 \text{ kHz}$                            | [2] _        | 60  | -   | dB   |

|                     |                                 |                                                         |              |     |     |      |

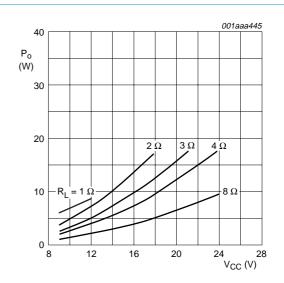

<sup>[1]</sup> A minimum load of 3  $\Omega$  is allowed at supply voltages > 22 V.

# 5. Ordering information

Table 2. Ordering information

| Type number | Package |                                                                                     |           |  |  |  |

|-------------|---------|-------------------------------------------------------------------------------------|-----------|--|--|--|

|             | Name    | Description                                                                         | Version   |  |  |  |

| TFA9842AJ   | DBS9P   | plastic DIL-bent-SIL power package; 9 leads (lead length 12/11 mm); exposed die pad | SOT523 -1 |  |  |  |

<sup>[2]</sup> Supply voltage ripple rejection is measured at the output, with a source impedance  $Z_S = 0~\Omega$  at the input and with a frequency range from 20 Hz to 22 kHz (unweighted). The ripple voltage is a sine wave with a frequency  $f_{ripple}$  and an amplitude of 300 mV (RMS), which is applied to the positive supply rail.

# 6. Block diagram

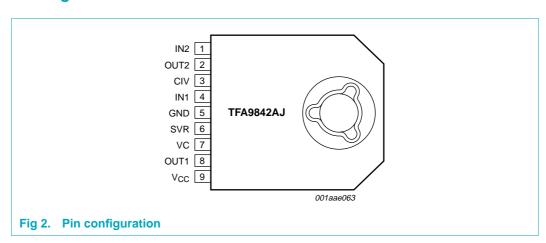

# 7. Pinning information

### 7.1 Pinning

#### 7.2 Pin description

Table 3. Pin description

| Symbol   | Pin | Description                                             |

|----------|-----|---------------------------------------------------------|

| IN2      | 1   | input 2                                                 |

| OUT2     | 2   | loudspeaker terminal 2                                  |

| CIV      | 3   | common input voltage decoupling                         |

| IN1      | 4   | input 1                                                 |

| GND      | 5   | ground                                                  |

| SVR      | 6   | half supply voltage decoupling (ripple rejection)       |

| VC       | 7   | volume control input (standby, mute and volume control) |

| OUT1     | 8   | loudspeaker terminal 1                                  |

| $V_{CC}$ | 9   | supply voltage                                          |

## 8. Functional description

### 8.1 Input configuration

The input cut-off frequency is:

$$f_{i(-3dB)} = \frac{1}{2\pi(R_i \times C_i)} \tag{1}$$

Single-ended application:  $R_i = 60 \text{ k}\Omega$  and  $C_i = 220 \text{ nF}$ :

$$f_{i(-3dB)} = \frac{1}{2\pi(60 \times 10^3 \times 220 \times 10^{-9})} = 12 \text{ Hz}$$

(2)

As shown in <u>Equation 2</u>, large capacitor values for the inputs are not necessary; therefore switch-on delay during charging of the input capacitors can be minimized. This results in a good low frequency response and good switch-on behavior.

The TFA9842AJ has clamps on the inputs. In Standby mode the voltage on the input pins is clamped for voltages lower than -0.1 V. When the TFA9842AJ is in Mute, Volume control or Operating mode (maximum gain) the input clamp voltage is 1 V (RMS).

#### 8.2 Power amplifier

The power amplifier is a single-ended amplifier with an all NPN output stage, capable of delivering a peak output current of 3 A.

### 8.2.1 Output power measurement

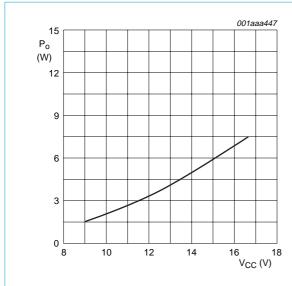

The output power as a function of the supply voltage is measured on the output pins at THD = 10 %; see <u>Figure 7</u>. The maximum output power is limited by the supply voltage of 26 V and the maximum available output current is 3 A repetitive peak current. A minimum load of 3  $\Omega$  is required for supply voltages > 22 V; see <u>Figure 4</u>. The output power is measured with one channel driven.

#### 8.2.2 Headroom

Typical CD music requires at least 12 dB (factor 15.85) dynamic headroom, compared to the average power output, for transferring the loudest parts without distortion. At  $V_{CC}$  = 17 V and  $P_o$  = 5 W (SE with  $R_L$  = 4  $\Omega$ ) at THD < 0.5 % (see <u>Figure 5</u>), the Average Listening Level (ALL) music power without any distortion yields:

$$P_{o(ALL)} = \frac{5}{15.85} = 315 \text{ mW}$$

(3)

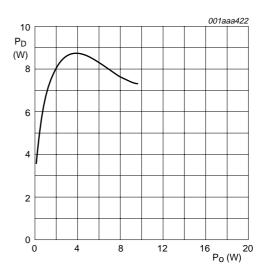

The power dissipation can be derived from <u>Figure 8</u> (SE) for 0 dB respectively 12 dB headroom (see <u>Table 4</u>).

For the average listening level a power dissipation of 4.2 W can be used for a heatsink calculation.

Table 4. Power rating as function of headroom

| Headroom | Power output SE<br>(THD < 0.5 %) | Power dissipation (P); both channels driven |

|----------|----------------------------------|---------------------------------------------|

| 0 dB     | $P_0 = 5 W$                      | 8.4 W                                       |

| 12 dB    | $P_{o(ALL)} = 315 \text{ mW}$    | 4.2 W                                       |

#### 8.3 Mode selection

The TFA9842AJ has four functional modes, which can be selected by applying the proper DC voltage to pin VC (see <u>Table 5</u>).

Table 5. Mode selection

| V <sub>I(VC)</sub>       | Status            | Definition                                                                                                                                                                                                                      |

|--------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 V to 0.8 V             | Standby           | in this mode the current consumption is very low and the outputs are floating; the device is in Standby mode when $V_{I(VC)}$ < 0.8 V.                                                                                          |

| 1.2 V to 1.5 V           | Mute              | in this mode the amplifier is DC-biased but not operational (no audio output); this allows the input coupling capacitors to be charged to avoid pop-noise; the device is in Mute mode when $1.2~\rm V < V_{I(VC)} < 1.5~\rm V.$ |

| 1.5 V to 5.0 V           | Volume control    | in this mode the volume of the amplifier can be controlled; the gain can be adjusted between the range of 1.5 V $<$ V <sub>I(VC)</sub> $<$ 5.0 V.                                                                               |

| 5.0 V to V <sub>CC</sub> | On (maximum gain) | in this mode the amplifier has its maximum gain; the Operating mode is activated at $V_{I(VC)} > 5.0 \text{ V}$ .                                                                                                               |

#### 8.4 Supply voltage ripple rejection

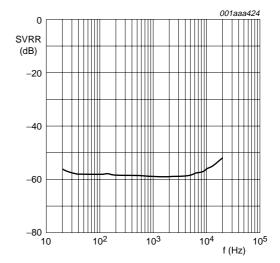

The supply voltage ripple rejection (SVRR) is measured with an electrolytic capacitor of 150  $\mu$ F connected to pin SVR with a bandwidth of 20 Hz to 22 kHz. The SVRR as a function of the frequency is illustrated in Figure 10. A larger capacitor value on pin SVR improves the ripple rejection behavior at the lower frequencies.

### 8.5 Built-in protection circuits

The TFA9842AJ contains two types of temperature sensors; one measures the local temperatures of the power stages and one measures the global chip temperature. At a local temperature of the power stage of approximately 185 °C or a global temperature of approximately 150 °C this detection circuit switches off the power stages for 2 ms. When the outputs are switched off the voltage is measured on the outputs. In the event of a short-circuit to ground or to  $V_{CC}$  the device will remain in Protection mode. In all other cases the power stages switch-on automatically and the detection will take place again; however a too high temperature will switch-off the power stages immediately. This can result in repetitive switching during too high junction temperature. This protects the TFA9842AJ against short-circuits to ground, to the supply voltage, across the load and too high chip temperatures.

The protection will only be activated when necessary, so even during a short-circuit condition, a certain amount of (pulsed) current will still flow through the short-circuit (as much as the power stage can handle without exceeding the critical temperature level).

## 9. Limiting values

Table 6. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol               | Parameter                               | Conditions    | Min  | Max            | Unit |

|----------------------|-----------------------------------------|---------------|------|----------------|------|

| $V_{CC}$             | supply voltage                          | operating     | -0.3 | +28            | V    |

| V <sub>I</sub>       | input voltage                           |               | -0.3 | $V_{CC} + 0.3$ | V    |

| I <sub>ORM</sub>     | repetitive peak output current          |               | -    | 3              | Α    |

| T <sub>stg</sub>     | storage temperature                     | non-operating | -55  | +150           | °C   |

| T <sub>amb</sub>     | ambient temperature                     | operating     | -40  | +85            | °C   |

| P <sub>tot</sub>     | total power dissipation                 |               | -    | 35             | W    |

| V <sub>CC(scp)</sub> | short-circuit protection supply voltage |               | -    | 26             | V    |

### 10. Thermal characteristics

Table 7. Thermal characteristics

| Symbol               | Parameter                                   | Conditions           | Тур | Unit |

|----------------------|---------------------------------------------|----------------------|-----|------|

| $R_{th(j-a)}$        | thermal resistance from junction to ambient | in free air          | 40  | K/W  |

| $R_{\text{th(j-c)}}$ | thermal resistance from junction to case    | both channels driven | 2.0 | K/W  |

### 11. Static characteristics

Table 8. Static characteristics

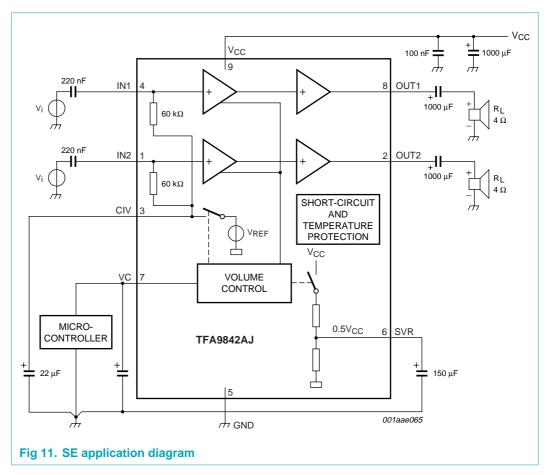

$V_{CC}$  = 17 V;  $T_{amb}$  = 25 °C;  $R_L$  = 4  $\Omega$ ;  $V_{I(VC)}$  =  $V_{CC}$ ;  $V_i$  = 0 V; measured in test circuit of <u>Figure 11</u>; unless otherwise specified.

| Symbol           | Parameter               | Conditions                   |            | Min | Тур | Max      | Unit |

|------------------|-------------------------|------------------------------|------------|-----|-----|----------|------|

| $V_{CC}$         | supply voltage          | operating                    | <u>[1]</u> | 9   | 17  | 28       | V    |

| Iq               | quiescent current       | $R_L = \infty \Omega$        |            | -   | 60  | 100      | mA   |

| I <sub>stb</sub> | standby current         | $V_{I(VC)} = 0 V$            |            | -   | -   | 150      | μΑ   |

| $V_{O}$          | output voltage          |                              | [2]        | -   | 9   | -        | V    |

| $V_{I(VC)}$      | input voltage on pin VC | On mode (maximum gain)       |            | 5.0 | -   | $V_{CC}$ | V    |

|                  |                         | Volume control mode          |            | 1.5 | -   | 5.0      | V    |

|                  |                         | Mute mode                    |            | 1.2 | -   | 1.5      | V    |

|                  |                         | Standby mode                 |            | 0   | -   | 8.0      | V    |

| $I_{I(VC)}$      | input current on pin VC | $0 \ V < V_{I(VC)} < V_{CC}$ |            | -   | -   | 20       | μΑ   |

<sup>[1]</sup> A minimum load of 3  $\Omega$  is allowed at supply voltages > 22 V.

# 12. Dynamic characteristics

Table 9. Dynamic characteristics

$V_{CC}$  = 17 V;  $T_{amb}$  = 25 °C;  $R_L$  = 4  $\Omega$ ; f = 1 kHz;  $V_{I(VC)}$  =  $V_{CC}$ ; measured in test circuit Figure 11; unless otherwise specified.

| Symbol                | Parameter                       | Conditions                                  |            | Min | Тур | Max | Unit      |

|-----------------------|---------------------------------|---------------------------------------------|------------|-----|-----|-----|-----------|

| Po                    | output power                    | THD = 10 %; $R_L$ = 4 $\Omega$              |            | 7   | 7.5 | -   | W         |

|                       |                                 | THD = 0.5 %; $R_L$ = 4 $\Omega$             |            | -   | 6.1 | -   | W         |

| THD                   | total harmonic distortion       | $P_0 = 1 W$                                 |            | -   | 0.1 | 0.5 | %         |

| G <sub>v(max)</sub>   | maximum voltage gain            | $V_{I(VC)} > 5.0 \text{ V}$                 |            | 25  | 26  | 27  | dB        |

| $\Delta G_{v}$        | voltage gain range              | $1.5 \text{ V} < V_{I(VC)} < 5.0 \text{ V}$ |            | -   | 80  | -   | dB        |

| V <sub>i</sub>        | input voltage                   | Gain = 0 dB;<br>THD < 1 %                   |            | 1.0 | -   | -   | V         |

| $Z_{i}$               | input impedance                 |                                             |            | 40  | 60  | -   | $k\Omega$ |

| $V_{n(o)}$            | noise output voltage            |                                             | <u>[1]</u> | -   | 150 | -   | μV        |

| SVRR                  | supply voltage ripple           | f <sub>ripple</sub> = 1 kHz                 | [2]        | -   | 60  | -   | dB        |

|                       | rejection                       | $f_{ripple} = 100 \text{ Hz to}$<br>20 kHz  | [2]        | -   | 60  | -   | dB        |

| V <sub>o(mute)</sub>  | mute output voltage             |                                             | [3]        | -   | -   | 150 | μV        |

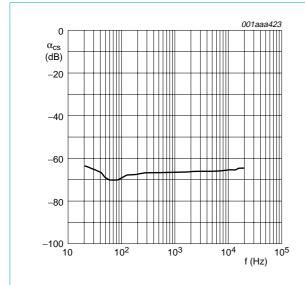

| $\alpha_{\text{cs}}$  | channel separation              | $Z_S = 0 \Omega$                            |            | 50  | 60  | -   | dB        |

| $ \Delta G_{v(max)} $ | maximum voltage gain difference |                                             |            | -   | -   | 1   | dB        |

|                       |                                 |                                             |            |     |     |     |           |

<sup>[1]</sup> The noise output voltage is measured at the output in a frequency range from 20 Hz to 22 kHz (unweighted), with a source impedance  $Z_S = 0~\Omega$  at the input.

TFA9842AJ\_1

<sup>[2]</sup> The DC output voltage with respect to ground is approximately 0.5V<sub>CC</sub>.

- [2] Supply voltage ripple rejection is measured at the output, with a source impedance  $Z_S = 0~\Omega$  at the input and with a frequency range from 20 Hz to 22 kHz (unweighted). The ripple voltage is a sine wave with a frequency  $f_{\text{ripple}}$  and an amplitude of 300 mV (RMS), which is applied to the positive supply rail.

- [3] Output voltage in Mute mode (V<sub>I(VC)</sub> = 1.35 V) and an input voltage of 1 V (RMS) in a bandwidth from 20 Hz to 22 kHz, so including noise.

Fig 3. Voltage gain as a function of volume control voltage

THD = 10 %

Fig 4. Output power (one channel) as a function of supply voltage for various SE loads

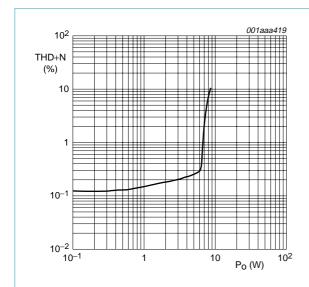

Fig 5. Total harmonic distortion-plus-noise as a function of output power

$V_{CC}$  = 17 V; SE; f = 1 kHz;  $R_L$  = 4  $\Omega$

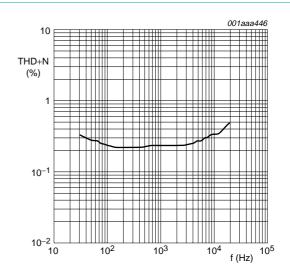

$V_{CC}$  = 17 V; SE;  $P_o$  = 1 W;  $R_L$  = 4  $\Omega$

Fig 6. Total harmonic distortion-plus-noise as a function of frequency

THD = 10 %; SE;  $R_L$  = 4  $\Omega$ ; f = 1 kHz

Fig 7. Output power as a function of supply voltage

$V_{CC}$  = 17 V; SE;  $R_L$  = 4  $\Omega$

Fig 8. Total power dissipation as a function of channel output power per channel (worst case, both channels driven)

$V_{CC}$  = 17 V; SE;  $R_L$  = 4  $\Omega$

Fig 9. Channel separation as a function of frequency (no bandpass filter applied)

$V_{CC}$  = 17 V; SE;  $Z_S$  = 0  $\Omega;$   $V_{ripple}$  = 300 mV (RMS); a bandpass filter of 20 Hz to 22 kHz has been applied; inputs short-circuited.

Fig 10. Supply voltage ripple rejection as a function of frequency

# 13. Application information

### 13.1 Application diagrams

### 13.1.1 Single-ended Application

**Remark:** Switching inductive loads, the output voltage can rise beyond the maximum supply voltage of 28 V. At high supply voltage it is recommended to use (Schottky) diodes to the supply voltage and ground.

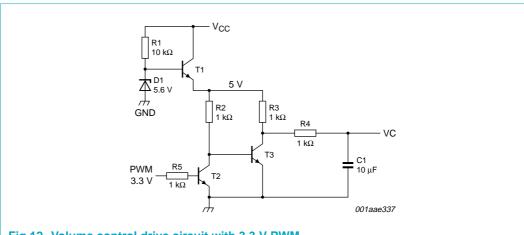

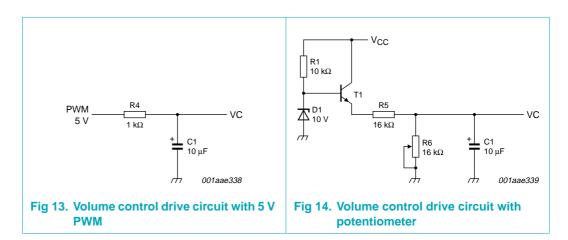

### 13.1.2 Volume control drive options

Fig 12. Volume control drive circuit with 3.3 V PWM

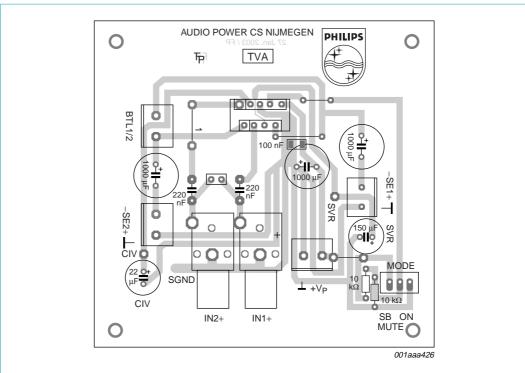

#### 13.2 Printed-circuit board

#### 13.2.1 Layout and grounding

To obtain a high-level system performance, certain grounding techniques are essential. The input reference grounds have to be tied with their respective source grounds and must have separate tracks from the power ground tracks; this will prevent the large output signal currents from interfering with the small AC input signals. The small-signal ground tracks should be physically located as far as possible from the power ground tracks. Supply and output tracks should be as wide as possible for delivering maximum output power.

Fig 15. Printed-circuit board layout (single-sided); components view

#### 13.2.2 Power supply decoupling

Proper supply bypassing is critical for low-noise performance and high supply voltage ripple rejection. The respective capacitor location should be as close as possible to the device and grounded to the power ground. Proper power supply decoupling also prevents oscillations.

For suppressing higher frequency transients (spikes) on the supply line a capacitor with low ESR, typical 100 nF, has to be placed as close as possible to the device. For suppressing lower frequency noise and ripple signals, a large electrolytic capacitor, e.g.  $1000~\mu F$  or greater, must be placed close to the device.

The bypass capacitor connected to pin SVR reduces the noise and ripple on the mid rail voltage. For good THD and noise performance a low ESR capacitor is recommended.

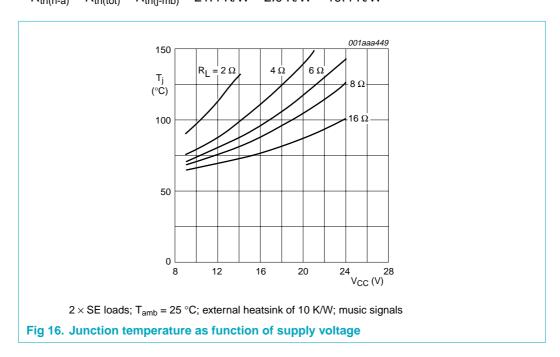

### 13.3 Thermal behavior and heatsink calculation

The measured maximum thermal resistance of the IC package,  $R_{th(j-mb)}$ , is 2.0 K/W. A calculation for the heatsink can be made, with the following parameters:

$$T_{amb(max)}$$

= 60 °C (example)

$V_{CC}$  = 17 V and  $R_L$  = 4  $\Omega$  (SE)

$T_{j(max)}$  = 150 °C (specification)

$R_{th(tot)}$  is the total thermal resistance between the junction and the ambient including the heatsink. This can be calculated using the maximum temperature increase divided by the power dissipation:

$$R_{th(tot)} = (T_{j(max)} - T_{amb(max)})/P$$

At  $V_{CC}$  = 17 V and  $R_L$  = 4  $\Omega$  (2 × SE) the measured worst-case sine-wave dissipation is 8.4 W; see <u>Figure 8</u>. For  $T_{j(max)}$  = 150 °C the temperature raise, caused by the power dissipation, is: 150 °C – 60 °C = 90 °C:

$$P \times R_{th(tot)} = 90 \text{ }^{\circ}C$$

$R_{th(tot)} = 90/8.4 \text{ K/W} = 10.7 \text{ K/W}$

$R_{th(h-a)} = R_{th(tot)} - R_{th(j-mb)} = 10.7 \text{ K/W} - 2.0 \text{ K/W} = 8.7 \text{ K/W}$

This calculation is for an application at worst-case (stereo) sine-wave output signals. In practice music signals will be applied, which decreases the maximum power dissipation to approximately half of the sine-wave power dissipation (see <u>Section 8.2.2</u>). This allows for the use of a smaller heatsink:

$$\begin{split} P \times R_{th(tot)} &= 90 \text{ °C} \\ R_{th(tot)} &= 90/4.2 \text{ K/W} = 21.4 \text{ K/W} \\ R_{th(h-a)} &= R_{th(tot)} - R_{th(j-mb)} = 21.4 \text{ K/W} - 2.0 \text{ K/W} = 19.4 \text{ K/W} \end{split}$$

### 14. Test information

### 14.1 Quality information

The General Quality Specification for Integrated Circuits, SNW-FQ-611 is applicable.

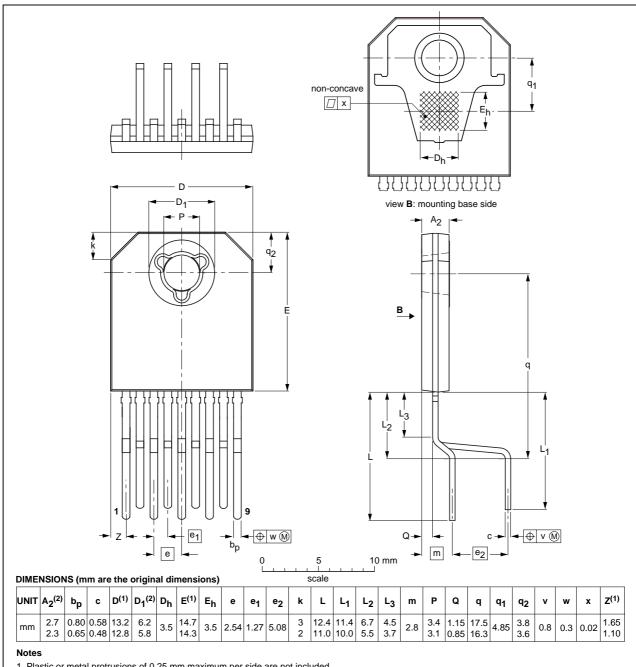

# 15. Package outline

DBS9P: plastic DIL-bent-SIL power package; 9 leads (lead length 12/11 mm); exposed die pad SOT523-1

- 1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

- 2. Plastic surface within circle area  $\mathsf{D}_1$  may protrude 0.04 mm maximum.

|     | REFER | ENCES |                            | EUROPEAN   | ISSUE DATE                       |  |

|-----|-------|-------|----------------------------|------------|----------------------------------|--|

| IEC | JEDEC | JEITA |                            | PROJECTION | ISSUE DATE                       |  |

|     |       |       |                            |            | <del>-00-07-03</del><br>03-03-12 |  |

|     | IEC   |       | REFERENCES IEC JEDEC JEITA |            | IEC JEDEC JEITA PROJECTION       |  |

Fig 17. Package outline SOT523-1 (DBS9P)

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

### 16. Soldering

#### 16.1 Introduction to soldering through-hole mount packages

This text gives a brief insight to wave, dip and manual soldering. A more in-depth account of soldering ICs can be found in our *Data Handbook IC26; Integrated Circuit Packages* (document order number 9398 652 90011).

Wave soldering is the preferred method for mounting of through-hole mount IC packages on a printed-circuit board.

#### 16.2 Soldering by dipping or by solder wave

Driven by legislation and environmental forces the worldwide use of lead-free solder pastes is increasing. Typical dwell time of the leads in the wave ranges from 3 seconds to 4 seconds at 250 °C or 265 °C, depending on solder material applied, SnPb or Pb-free respectively.

The total contact time of successive solder waves must not exceed 5 seconds.

The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified maximum storage temperature  $(T_{stg(max)})$ . If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit.

#### 16.3 Manual soldering

Apply the soldering iron (24 V or less) to the lead(s) of the package, either below the seating plane or not more than 2 mm above it. If the temperature of the soldering iron bit is less than 300  $^{\circ}$ C it may remain in contact for up to 10 seconds. If the bit temperature is between 300  $^{\circ}$ C and 400  $^{\circ}$ C, contact may be up to 5 seconds.

#### 16.4 Package related soldering information

Table 10. Suitability of through-hole mount IC packages for dipping and wave soldering methods

| Package                         | Soldering method |              |  |  |

|---------------------------------|------------------|--------------|--|--|

|                                 | Dipping          | Wave         |  |  |

| CPGA, HCPGA                     | -                | suitable     |  |  |

| DBS, DIP, HDIP, RDBS, SDIP, SIL | suitable         | suitable[1]  |  |  |

| PMFP[2]                         | -                | not suitable |  |  |

<sup>[1]</sup> For SDIP packages, the longitudinal axis must be parallel to the transport direction of the printed-circuit board.

<sup>[2]</sup> For PMFP packages hot bar soldering or manual soldering is suitable.

# 17. Revision history

### Table 11. Revision history

| Document ID | Release date | Data sheet status      | Change notice | Supersedes |

|-------------|--------------|------------------------|---------------|------------|

| TFA9842AJ_1 | 20060428     | Preliminary data sheet | -             | -          |

16 of 18

## 18. Legal information

#### 18.1 Data sheet status

| Document status[1][2]          | Product status[3] | Definition                                                                            |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development       | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification     | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production        | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions"

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.semiconductors.philips.com.

#### 18.2 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Philips Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local Philips Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

#### 18.3 Disclaimers

**General** — Information in this document is believed to be accurate and reliable. However, Philips Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

Right to make changes — Philips Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Suitability for use** — Philips Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or

malfunction of a Philips Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Philips Semiconductors accepts no liability for inclusion and/or use of Philips Semiconductors products in such equipment or applications and therefore such inclusion and/or use is for the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.

Terms and conditions of sale — Philips Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.semiconductors.philips.com/profile/terms">http://www.semiconductors.philips.com/profile/terms</a>, including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by Philips Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

#### 18.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

#### 19. Contact information

For additional information, please visit: http://www.semiconductors.philips.com

For sales office addresses, send an email to: sales.addresses@www.semiconductors.philips.com

Contact information

17

Contents

18

### 20. Contents

| 1                 |                                           | 19 |

|-------------------|-------------------------------------------|----|

| 2                 | Features                                  | 20 |

| 3                 | Applications                              |    |

| 4                 | Quick reference data 2                    |    |

| 5                 | Ordering information 2                    |    |

| 6                 | Block diagram 3                           |    |

| 7                 | Pinning information                       |    |

| 7.1               | Pinning                                   |    |

| 7.2               | Pin description 4                         |    |

| 8                 | Functional description 4                  |    |

| 8.1               | Input configuration 4                     |    |

| 8.2               | Power amplifier 4                         |    |

| 8.2.1             | Output power measurement 4                |    |

| 8.2.2             | Headroom5                                 |    |

| 8.3               | Mode selection                            |    |

| 8.4               | Supply voltage ripple rejection           |    |

| 8.5               | Built-in protection circuits 6            |    |

| 9                 | Limiting values                           |    |

| 10                | Thermal characteristics 6                 |    |

| 11                | Static characteristics 7                  |    |

| 12                | Dynamic characteristics 7                 |    |

| 13                | Application information 10                |    |

| 13.1              | Application diagrams 10                   |    |

| 13.1.1            | Single-ended Application                  |    |

| 13.1.2            | Volume control drive options              |    |

| 13.2              | Printed-circuit board                     |    |

| 13.2.1<br>13.2.2  | Layout and grounding                      |    |

| 13.2.2            | Power supply decoupling                   |    |

| 14                | Test information                          |    |

| 14.1              | Quality information                       |    |

| 15                | Package outline                           |    |

|                   | _                                         |    |

| <b>16</b><br>16.1 | Soldering                                 |    |

| 16.1              | packages                                  |    |

| 16.2              | Soldering by dipping or by solder wave 15 |    |

| 16.3              | Manual soldering                          |    |

| 16.4              | Package related soldering information 15  |    |

| 17                | Revision history                          |    |

| 18                | Legal information                         |    |

| 18.1              | Data sheet status                         |    |

| 18.2              | Definitions                               |    |

| 18.3              | Disclaimers                               |    |

| 18.4              | Trademarks                                |    |

| Please be aware tha                                                  | t important notices | s concerning this | s document | and the | product(s) |  |  |  |

|----------------------------------------------------------------------|---------------------|-------------------|------------|---------|------------|--|--|--|

| described herein, have been included in section 'Legal information'. |                     |                   |            |         |            |  |  |  |

For more information, please visit: http://www.semiconductors.philips.com.

For sales office addresses, email to: sales.addresses@www.semiconductors.philips.com.

Date of release: 28 April 2006

Document identifier: TFA9842AJ\_1