## PRELIMINARY PRODUCT INFORMATION

# MOS INTEGRATED CIRCUIT $\mu$ PD780921, 780922, 780923, 780924

## 8-BIT SINGLE-CHIP MICROCONTROLLER

The µPD780921, 780922, 780923, and 780924, which are members of the µPD780924 subseries of the 78K/0 series, are suited to control general-purpose inverters.

Compared to the conventional µPD78014 subseries or µPD78018F subseries products, EMI (Electro Magnetic Interface) noise is reduced for the µPD780924 subseries products.

A flash memory version, the µPD78F0924, that can operate within the same power supply voltage range as the mask ROM version, and various development tools are also provided.

## The details of functions are described in the following user's manuals. Be sure to read them before designing. μPD780924 Subseries User's Manual : Planned 78K/0 Series User's Manual Instructions : IEU-1372

#### FEATURES

Internal ROM and RAM

EL

| Item<br>Part Number | Program memory<br>(ROM) | Data memory<br>(internal high-capacity RAM) | Package                                             |

|---------------------|-------------------------|---------------------------------------------|-----------------------------------------------------|

| μPD780921           | 8 Kbytes                | 512 bytes                                   | 64-pin plastic shrink DIP (750 mil)                 |

| μPD780922           | 16 Kbytes               |                                             | <ul> <li>64-pin plastic QFP (14 x 14 mm)</li> </ul> |

| µPD780923           | 24 Kbytes               | 1024 bytes                                  |                                                     |

| μPD780924           | 32 Kbytes               |                                             |                                                     |

- External memory expansion space: 48 Kbytes

- Minimum instruction execution time: 0.24 μs (@ fx = 8.38-MHz operation)

- I/O ports: 47

- 8-bit resolution A/D converter: eight channels

- Serial interface: two channels

- Timer: Five channels

- Power supply voltage: VDD = 2.7 to 5.5 V

#### **APPLICATIONS**

Motor control for inverter-type air conditioners, washing machines, etc.

The information in this document contains applications using a device in advance of the production cycle. The parameters for the device may change before final production or NEC Corporation, at its own discretion, may withdraw the device prior to its production.

Document No. U11804EJ1V0PM00 (1st edition)

Date Published November 1996 N

Printed in Japan

© NEC Corporation 1996

\_

2

\_ . \_ \_ \_ \_

ſ

## ORDERING INFORMATION

| Part Number         | Package                             |

|---------------------|-------------------------------------|

| μPD780921CW-xxx     | 64-pin plastic shrink DIP (750 mil) |

| μPD780922CW-xxx     | 64-pin plastic shrink DIP (750 mil) |

| μPD780923CW-xxx     | 64-pin plastic shrink DIP (750 mil) |

| μPD780924CW-xxx     | 64-pin plastic shrink DIP (750 mil) |

| μPD780921GC-xxx-AB8 | 64-pin plastic QFP (14 x 14 mm)     |

| μPD780922GC-×××-AB8 | 64-pin plastic QFP (14 x 14 mm)     |

| µPD780923GC-×××-AB8 | 64-pin plastic QFP (14 x 14 mm)     |

| μPD780924GC-xxx-AB8 | 64-pin plastic QFP (14 x 14 mm)     |

Remark xxx indicates the ROM code suffix.

🖬 6427525 009940l ll7 🛤

\_\_\_\_

3

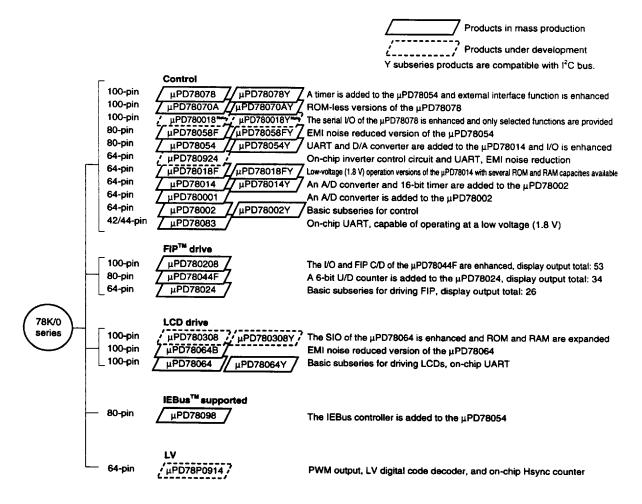

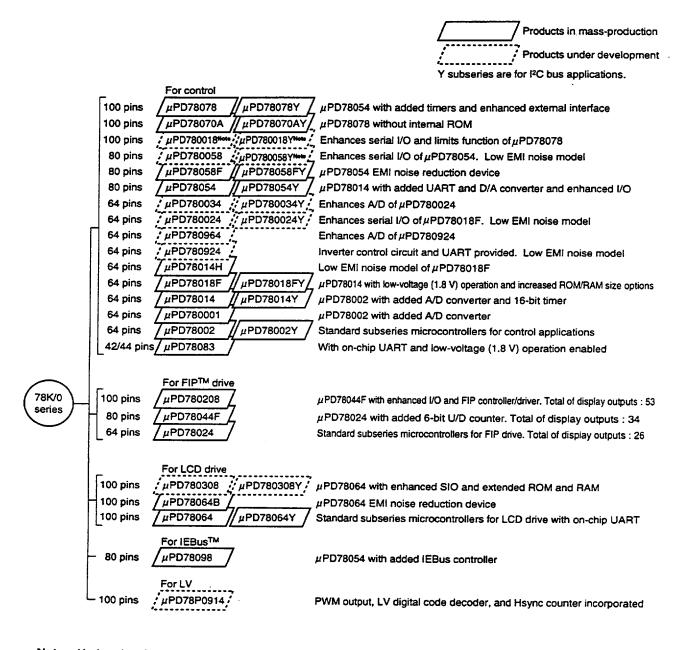

## **78K/0 SERIES DEVELOPMENT**

The 78K/0 series product line-up is shown below. Subseries names are shown inside frames.

Note Under planning

**6**427525 0099402 053 **III**

\_\_\_\_\_

|                  | Functions  | ROM          |       | Tir    | ner   |     | 8-bit | 8-bit | Serial           | 1/0 | Vod<br>MIN. | External  |

|------------------|------------|--------------|-------|--------|-------|-----|-------|-------|------------------|-----|-------------|-----------|

| Subseries        |            | Capacity     | 8-bit | 16-bit | Watch | WDT | A/D   | D/A   | Interface        | 1/0 | Value       | Expansion |

| For Control      | µPD78078   | 32 K to 60 K | 4ch   | 1ch    | 1ch   | 1ch | 8ch   | 2ch   | 3ch (UART: 1ch)  | 88  | 1.8 V       | Available |

|                  | µPD78070A  | —            |       |        |       |     |       |       |                  | 61  | 2.7 V       | 1         |

|                  | µPD780018  | 48 K to 60 K |       | 1      |       |     |       |       | 2ch              | 88  |             |           |

|                  | µPD78058F  |              | 2ch   | 1      |       |     | ł     | 2ch   | 3ch (UART : 1ch) | 69  |             |           |

|                  | µPD78054   | 16 K to 60 K |       |        |       |     |       |       |                  |     | 2.0 V       | 1         |

|                  | µPD780924  | 8 K to 32K   | 3ch   | Note   | —     |     |       | _     | 2ch (UART : 2ch) | 47  | 2.7ch       |           |

|                  | µPD78018F  | 8 K to 60 K  | 2ch   | 1ch    | 1ch   |     |       |       | 2ch              | 53  | 1.8 V       | 1         |

|                  | µPD78014   | 8 K to 32 K  |       |        |       |     |       |       |                  |     | 2.7 V       | -<br>     |

|                  | µPD780001  | 8 K          |       | _      | -     |     |       |       | 1ch              | 39  |             | _         |

|                  | µPD78002   | 8 K to 16 K  |       |        | 1ch   |     |       |       |                  | 53  |             | Available |

|                  | µPD78083   | 8 K to 16 K  |       |        | -     |     | Bch   | 1     | 1ch (UART : 1ch) | 33  | 1.8 V       | - 1       |

| For FIP          | µPD780208  | 32 K to 60 K | 2ch   | 1ch    | 1ch   | 1ch | 8ch   |       | 2ch              | 74  | 2.7 V       | _         |

| drive            | µPD78044F  | 16 K to 40 K |       |        |       |     |       |       |                  | 68  |             |           |

|                  | µPD78024   | 24 K to 32 K |       |        |       |     |       |       |                  | 54  |             |           |

| For LCD          | µPD780308  | 48 K to 60 K | 2ch   | 1ch    | 1ch   | 1ch | 8ch   |       | 3ch (UART: 1ch)  | 57  | 1.8 V       | -         |

| drive            | µPD78064B  | 32 K         |       |        |       |     |       |       | 2ch (UART : 1ch) | 1   | 2.0 V       | 1         |

|                  | µPD78064   | 16 K to 32 K |       |        |       |     |       |       |                  |     |             |           |

| IEBus<br>Support | µPD78098   | 32 K to 60 K | 2ch   | 1ch    | 1ch   | 1ch | 8ch   | 2ch   | 3ch (UART: 1ch)  | 69  | 2.7 V       | Available |

| For LV           | µPD78P0914 | 32K          | 6ch   | -      | _     | 1ch | 8ch   | _     | 2ch              | 54  | 4.5 V       | Available |

The table below shows the main differences between subseries.

Note 10-bit timer: one channel

4

## 64275250099403 T9T 🖿

Powered by ICminer.com Electronic-Library Service CopyRight 2003

- .....

## **FUNCTION OVERVIEW**

|                      | Product Name               |                                                                         |                           |                          |                              |  |  |  |

|----------------------|----------------------------|-------------------------------------------------------------------------|---------------------------|--------------------------|------------------------------|--|--|--|

| Item                 |                            | μPD780921                                                               | μPD780922                 | µPD780923                | μPD780924                    |  |  |  |

| internal             | ROM                        | 8 Kbytes                                                                | 16 Kbytes                 | 24 Kbytes                | 32 Kbytes                    |  |  |  |

| memory               | Internal<br>high-speed RAM | 512 bytes                                                               |                           | 1024 bytes               |                              |  |  |  |

| Memory sp            | ace                        | 64 Kbytes                                                               |                           |                          |                              |  |  |  |

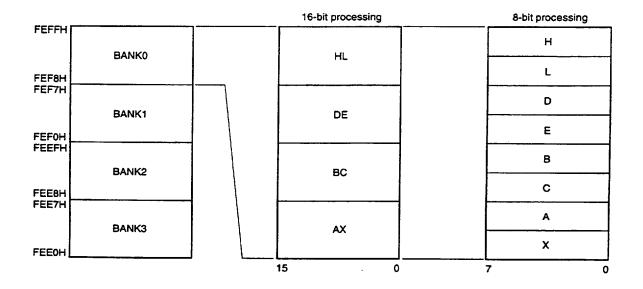

| General-pu           | rpose register             | 8 bits x 32 registers (8                                                | bits x 8 registers x 4 ba | nks)                     |                              |  |  |  |

| Instruction          | cycle                      | On-chip instruction exc                                                 | ecution time variable fun | ction                    | a <u>1995 - 19</u> 11 - 1911 |  |  |  |

| Instruction          |                            |                                                                         | us/1.9 μs/3.8 μs (@ 8.38- | MHz operation with syste | m clock)                     |  |  |  |

| instruction          | set                        | 16-bit operation                                                        |                           |                          |                              |  |  |  |

|                      |                            | <ul> <li>Multiply/divide (8 bits x 8 bits, 16 bits + 8 bits)</li> </ul> |                           |                          |                              |  |  |  |

|                      |                            | Bit manipulate (set, reset, test, Boolean operation)                    |                           |                          |                              |  |  |  |

|                      |                            | BCD adjust, etc.                                                        |                           |                          |                              |  |  |  |

| I/O ports            |                            | Total : 47                                                              |                           |                          |                              |  |  |  |

|                      |                            | CMOS inputs : 8                                                         |                           |                          |                              |  |  |  |

|                      |                            | CMOS I/Os : 39                                                          |                           |                          |                              |  |  |  |

|                      | output ports               | 8 bits x 1 or 4 bits x 2                                                |                           |                          |                              |  |  |  |

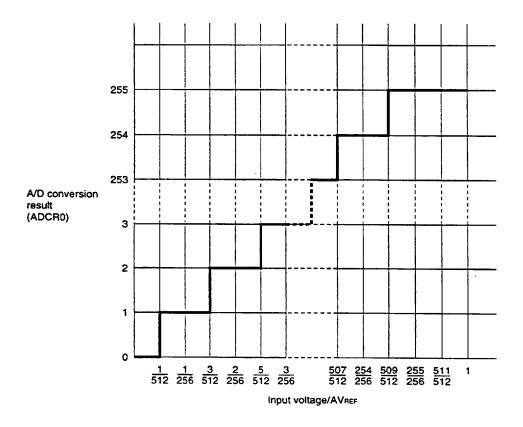

| A/D conver           | ter                        | B-bit resolution x 8 channels                                           |                           |                          |                              |  |  |  |

|                      |                            | Power supply voltage: AVob = 2.7 to 5.5 V                               |                           |                          |                              |  |  |  |

| Serial inter         | face                       | UART x 2 channels                                                       |                           |                          |                              |  |  |  |

| Timer                |                            | 8-bit timer/event counter : 3 channels                                  |                           |                          |                              |  |  |  |

|                      |                            | • 10-bit timer : 1 channel                                              |                           |                          |                              |  |  |  |

|                      |                            | Watchdog timer : 1 channel                                              |                           |                          |                              |  |  |  |

| Timer outp           |                            | 9 (8-bit PWM output x 3, and inverter control output x 6)               |                           |                          |                              |  |  |  |

| Vectored             | Maskable interrupts        | Internal: 12, external: 4                                               |                           |                          |                              |  |  |  |

| interrupt            | Non-maskable interrupt     | Internal: 1                                                             |                           |                          |                              |  |  |  |

| Software interrupt   |                            | 1                                                                       |                           |                          |                              |  |  |  |

| Power supply voltage |                            | Voo = 2.7 to 5.5 V                                                      |                           |                          |                              |  |  |  |

|                      | mbient temperature         | T <sub>A</sub> = -40 to +85 °C                                          |                           |                          |                              |  |  |  |

| Package              |                            | <ul> <li>64-pin plastic shrink</li> </ul>                               | DIP (750 mil)             |                          |                              |  |  |  |

|                      |                            | • 64-pin plastic QFP (14 x 14 mm)                                       |                           |                          |                              |  |  |  |

## ■ 6427525 0099404 926 **■**

\_

NEC

## CONTENTS

| 1.  | PIN CONFIGURATION (TOP VIEW)              | 7  |

|-----|-------------------------------------------|----|

| 2.  | BLOCK DIAGRAM                             | 10 |

| 3.  | PIN FUNCTION LIST                         |    |

|     | 3.1 PORT PINS                             |    |

|     | 3.2 NON PORT PINS                         | 12 |

|     | 3.3 RECOMMENDED CONNECTION OF UNUSED PINS | 13 |

| 4.  | MEMORY SPACE                              | 14 |

| 5.  | PERIPHERAL HARDWARE FUNCTION FEATURES     | 15 |

|     | 5.1 PORTS                                 |    |

|     | 5.2 CLOCK GENERATOR                       |    |

|     | 5.3 TIMER/EVENT COUNTERS                  | 17 |

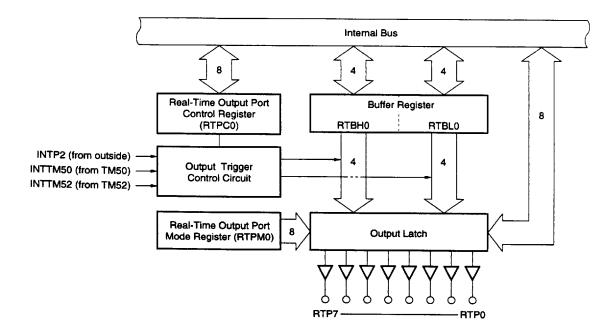

|     | 5.4 REAL-TIME OUTPUT PORT                 | 19 |

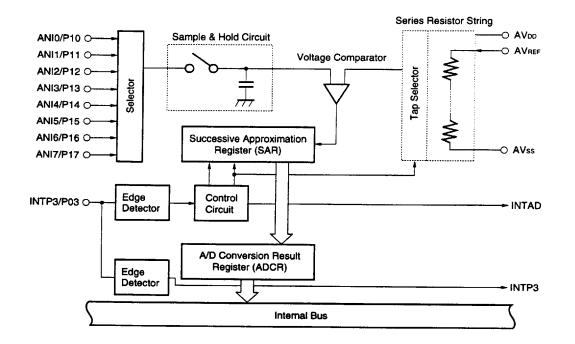

|     | 5.5 A/D CONVERTER                         | 20 |

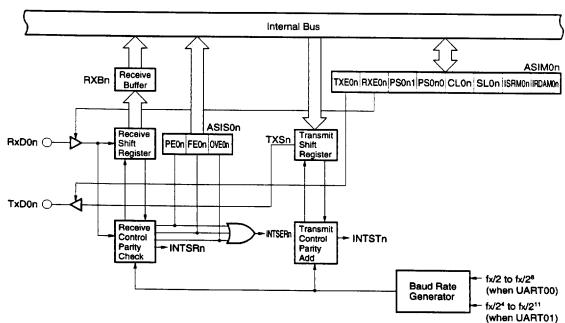

|     | 5.6 SERIAL INTERFACE                      | 21 |

| 6.  | INTERRUPT FUNCTIONS                       | 22 |

| 7.  | EXTERNAL DEVICE EXPANSION FUNCTION        | 25 |

| 8.  | STANDBY FUNCTIONS                         | 25 |

| 9.  | RESET FUNCTIONS                           | 25 |

| 10. |                                           | 26 |

| 11. | PACKAGE DRAWINGS                          | 29 |

| AP  | PENDIX A. DEVELOPMENT TOOLS               | 31 |

| AP  | PENDIX B. RELATED DOCUMENTS               | 33 |

6

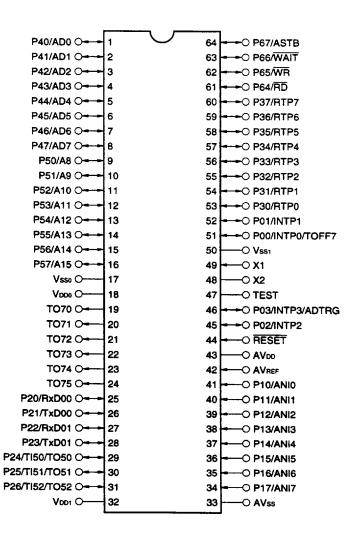

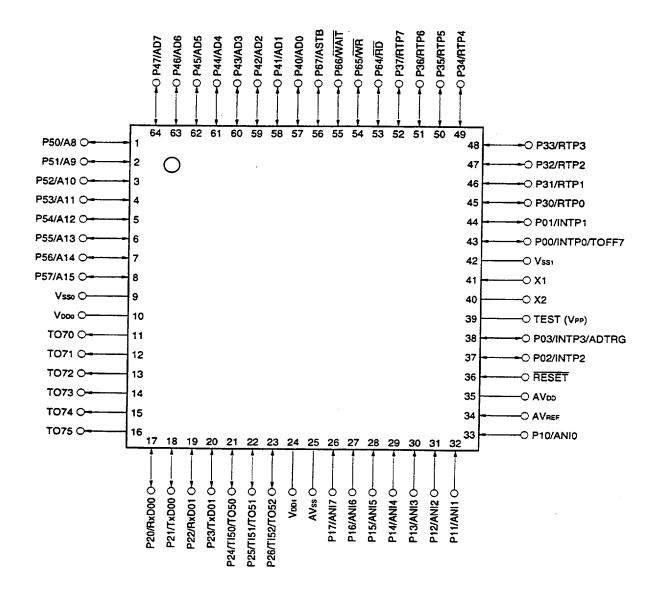

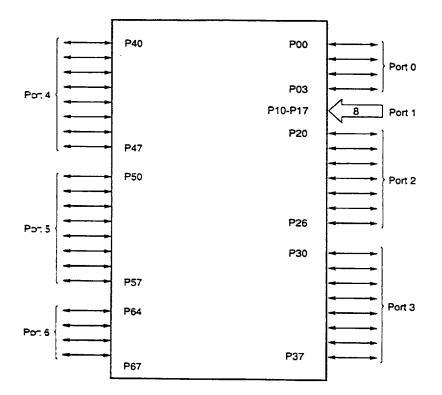

## 1. PIN CONFIGURATION (Top View)

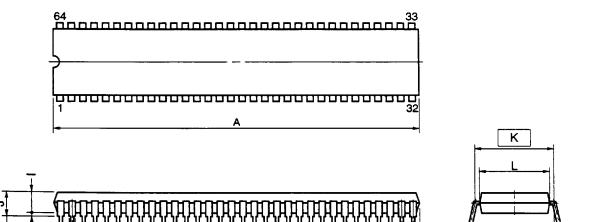

• 64-Pin Plastic Shrink DIP (750 mil) μPD780921CW-xxx, 780922CW-xxx, 780923CW-xxx, 780924CW-xxx

## Cautions 1. Connect the TEST pin to Vsso directly.

- 2. Connect the AVpp pin to Vppo.

- 3. Connect the AVss pin to Vsso.

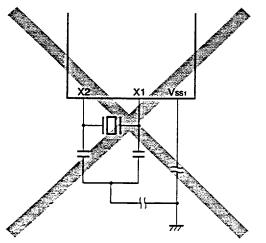

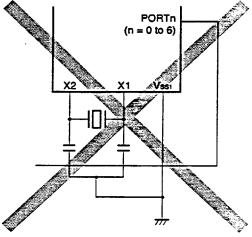

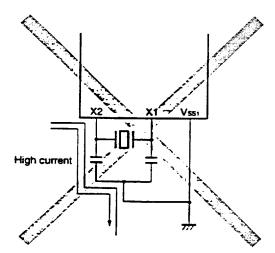

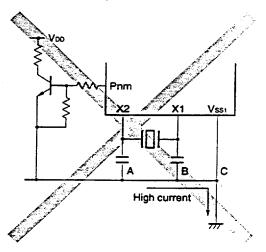

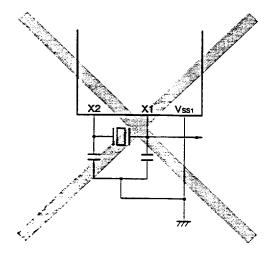

- Remark When the μPD780921, 780922, 780923, or 780924 is used in application fields that require reduction of the noise generated from inside the microcontroller, the implementation of noise reduction measures, such as supplying voltage to Vodo and Vss1 individually and connecting Vsso and Vss1 to different ground lines, is recommended.

#### 🖬 6427525 0099406 7T9 📰

NEC

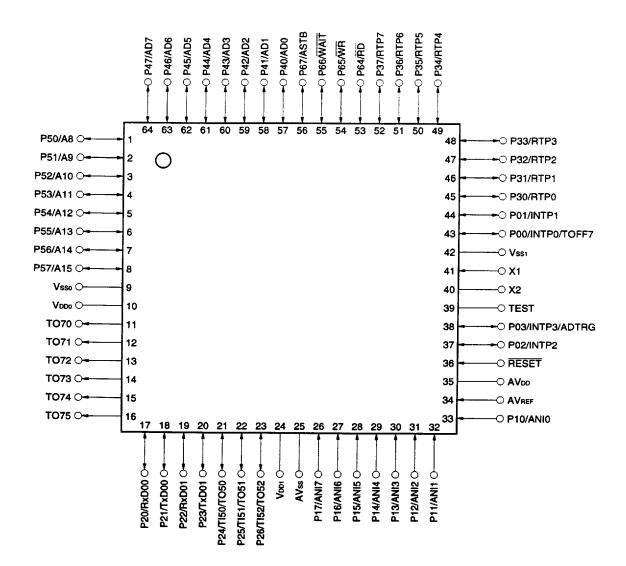

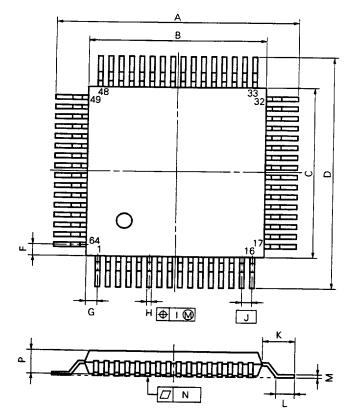

## • 64-Pin Plastic QFP (14 x 14 mm) μPD780921GC-xxx-AB8, 780922GC-xxx-AB8, 780923GC-xxx-AB8, 780924GC-xxx-AB8

#### Cautions 1. Connect the TEST pin to Vsso directly.

- 2. Connect the AVDD pin to VDDO.

- 3. Connect the AVss pin to Vsso.

8

Remark When the μPD780921, 780922, 780923, or 780924 is used in application fields that require reduction of the noise generated from inside the microcontroller, the implementation of noise reduction measures, such as supplying voltage to Vodo and Vss1 individually and connecting Vsso and Vss1 to different ground lines, is recommended.

## | 6427525 0099407 635 🖿

9

| P00 to P03<br>P10 to P17<br>P20 to P26<br>P30 to P37<br>P40 to P47<br>P50 to P57 | <ul> <li>Address Bus</li> <li>Address/Data Bus</li> <li>AD Trigger Input</li> <li>Analog Input</li> <li>Address Strobe</li> <li>Analog Power Supply</li> <li>Analog Reference Voltage</li> <li>Analog Ground</li> <li>Interrupt From Peripherals</li> <li>Port 0</li> <li>Port 1</li> <li>Port 2</li> <li>Port 3</li> <li>Port 4</li> <li>Port 5</li> <li>Port 6</li> </ul> | RD           RESET           RTP0 to RTP7           RxD00, RxD01           TEST           T150 to T152           TO50 to T052,           TO70 to T075           TOFF7           TxD00, TxD01           Vsso, Vss1           WAIT           WR           X1, X2 |  | Read Strobe<br>Reset<br>Real-time Port<br>Receive Data<br>Test<br>Timer Input<br>Timer Output<br>Timer Output Off<br>Transmit Data<br>Power Supply<br>Ground<br>Wait<br>Write Strobe<br>Crystal |  |

|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

🔲 6427525 0099408 571 🔜

NEC

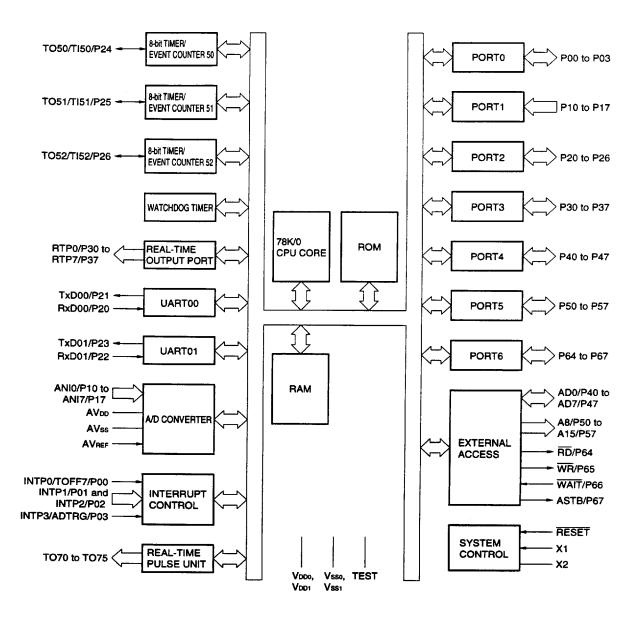

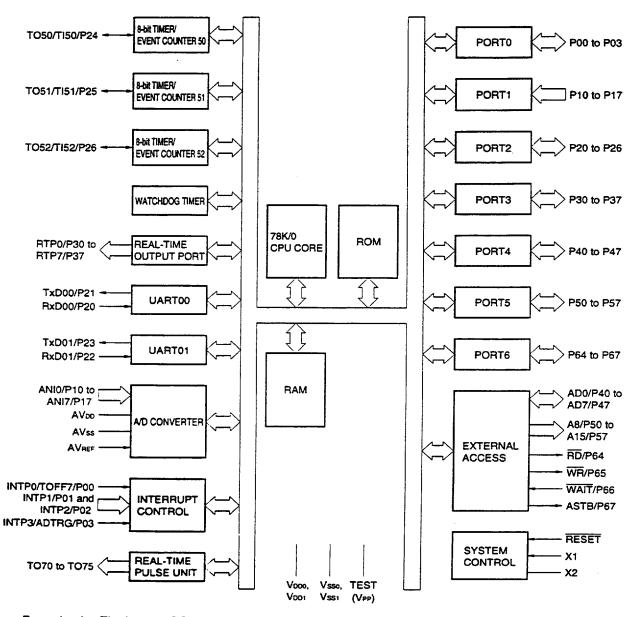

## 2. BLOCK DIAGRAM

6427525 0099409 408 🔳

Remark Internal ROM and RAM capacity varies depending on the product.

10

## 3. PIN FUNCTION LIST

## 3.1 PORT PINS

| Pin Name   | 1/0   | Function                                                       | After Reset | Alternate<br>Function |

|------------|-------|----------------------------------------------------------------|-------------|-----------------------|

| P00        | 1/0   | Port 0.                                                        | Input       | INTP0/TOFF7           |

| P01        |       | 4-bit I/O port.                                                |             | INTP1                 |

| P02        |       | Input/output can be specified bit-wise.                        |             | INTP2                 |

| P03        | 7     | When used as an input port, an on-chip pull-up resistor can be |             | INTP3/ADTRG           |

|            |       | connected by software.                                         |             |                       |

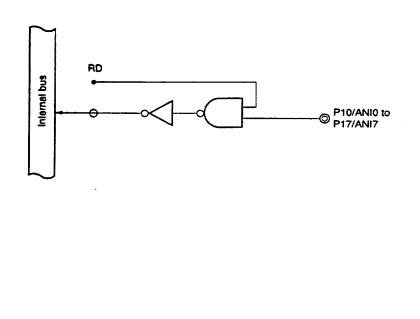

| P10 to P17 | Input | Port 1.                                                        | Input       | ANI0 to ANI7          |

|            |       | 8-bit input only port.                                         |             |                       |

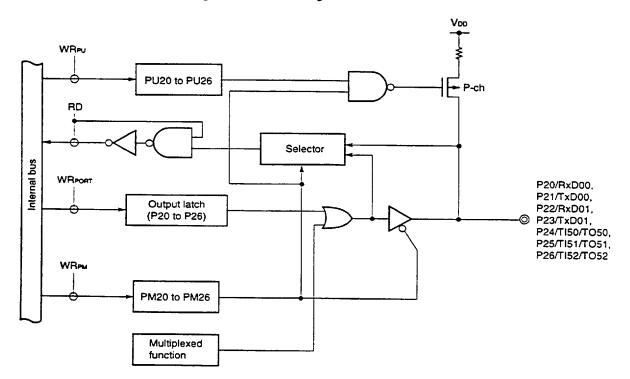

| P20        | 1/0   | Port 2.                                                        | Input       | RxD00                 |

| P21        |       | 7-bit I/O port.                                                |             | TxD00                 |

| P22        |       | Input/output can be specified bit-wise.                        |             | RxD01                 |

| P23        |       | When used as an input port, an on-chip pull-up resistor can be |             | TxD01                 |

| P24        |       | connected by software.                                         |             | TI50/TO50             |

| P25        | _     |                                                                |             | TI51/TO51             |

| P26        |       |                                                                |             | TI52/TO52             |

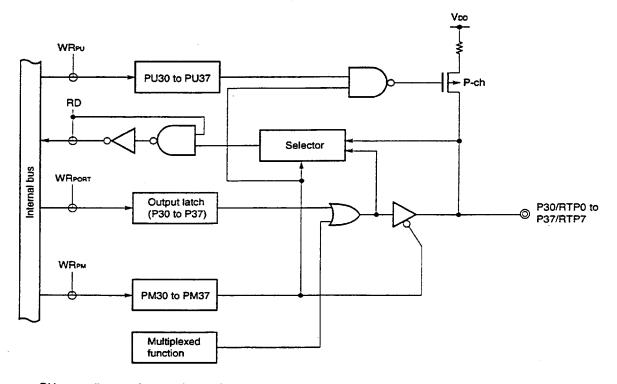

| P30 to P37 | 1/0   | Port 3.                                                        | Input       | RTP0 to RTP7          |

|            |       | 8-bit I/O port.                                                |             |                       |

|            |       | Input/output can be specified bit-wise.                        |             |                       |

|            |       | When used as an input port, an on-chip pull-up resistor can be |             |                       |

|            |       | connected by software.                                         |             |                       |

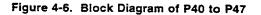

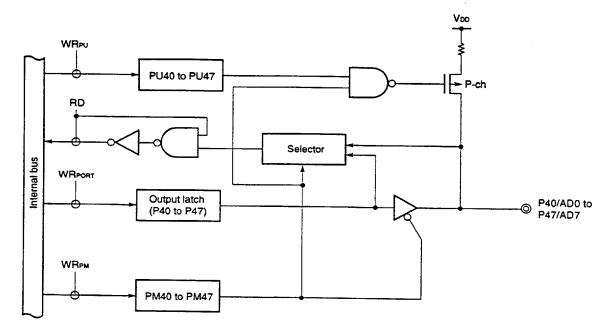

| P40 to P47 | 1/0   | Port 4.                                                        | Input       | AD0 to AD7            |

|            |       | 8-bit I/O port.                                                |             |                       |

|            |       | Input/output can be specified bit-wise.                        |             |                       |

|            |       | When used as an input port, an on-chip pull-up resistor can be |             |                       |

|            |       | connected by software.                                         |             |                       |

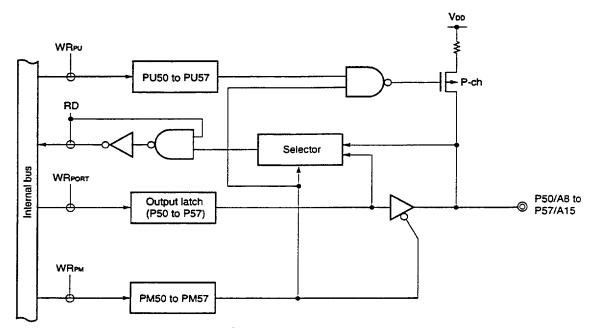

| P50 to P57 | 1/0   | Port 5.                                                        | Input       | A8 to A15             |

|            |       | 8-bit I/O port.                                                |             |                       |

|            |       | Input/output can be specified bit-wise.                        |             |                       |

|            |       | LEDs can be driven directly.                                   |             |                       |

|            |       | When used as an input port, an on-chip pull-up resistor can be |             |                       |

|            |       | connected by software                                          |             |                       |

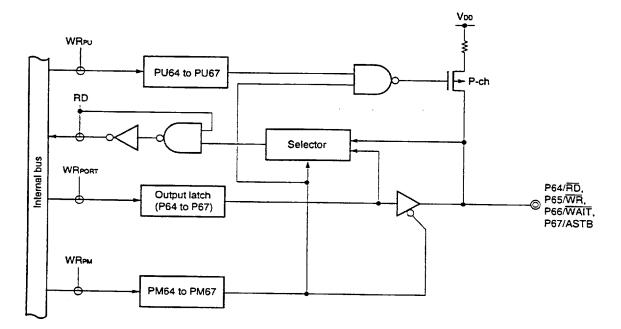

| P64        | 1/0   | Port 6.                                                        | Input       | RD                    |

| P65        | ]     | 4-bit I/O port.                                                |             | WB                    |

| P66        | ]     | Input/output can be specified bit-wise.                        |             | WAIT                  |

| P67        |       | When used as an input port, an on-chip pull-up resistor can be |             | ASTB                  |

|            |       | connected by software.                                         |             |                       |

📟 6427525 009941012T 📟

-

-----

#### 3.2 NON PORT PINS

| Pin Name     | 1/0    | Function                                                             | After Reset | Alternate<br>Function |

|--------------|--------|----------------------------------------------------------------------|-------------|-----------------------|

| INTPO        | Input  | External interrupt input that can specify the effective edge         | Input       | P00/TOFF7             |

| INTP1        | ]      | (rising edge, falling edge, or both rising and falling edges) can be | Input       | P01                   |

| INTP2        | ]      | specified.                                                           | Input       | P02                   |

| INTP3        | ]      |                                                                      | Input       | P03/ADTRG             |

| TI50         | Input  | External count clock input to timer (TM50).                          | Input       | P24/TO50              |

| TI51         | ]      | External count clock input to timer (TM51).                          | Input       | P25/TO51              |

| TI52         |        | External count clock input to timer (TM52).                          | Input       | P26/T052              |

| TO50         | Output | Timer (TM50) output.                                                 | Input       | P24/TI50              |

| TO51         |        | Timer (TM51) output.                                                 | Input       | P25/TI51              |

| TO52         | 1      | Timer (TM52) output.                                                 | Input       | P26/T152              |

| RTP0 to RTP7 | Output | Real-time output port that outputs pulses in synchronization with    | Input       | P30 to P37            |

|              |        | trigger signals outputs from the real-time pulse unit.               |             |                       |

| TxD00        | Output | Asynchronous serial interface serial data output.                    | Input       | P21                   |

| TxD01        | ]      |                                                                      | Input       | P23                   |

| RxD00        | Input  | Asynchronous serial interface serial data input.                     | Input       | P20                   |

| RxD01        |        |                                                                      | Input       | P22                   |

| ANI0 to ANI7 | Input  | A/D converter analog input.                                          | Input       | P10 to P17            |

| ADTRG        | Input  | External trigger signal input to the A/D converter.                  | Input       | P03/INTP3             |

| TO70 to TO75 | Output | Timer output for the 3-phase PWM inverter control.                   | Hi-Z        | _                     |

| TOFF7        | Input  | Timer output (TO70 to TO75) stop interrupt input.                    | Input       | P00/INTP0             |

| AD0 to AD7   | I/O    | Lower address/data bus when memory is expanded externally.           | Input       | P40 to P47            |

| A8 to A15    | Output | Upper address bus when memory is expanded externally.                | Input       | P50 to P57            |

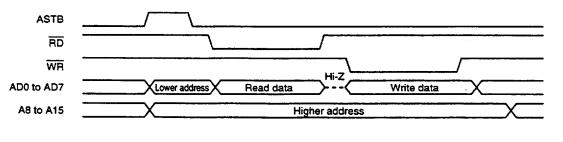

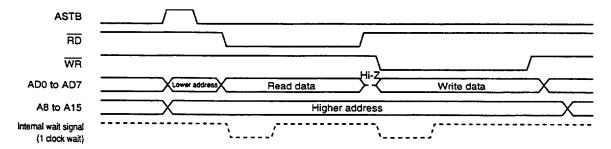

| RD           | Output | Strobe signal output for external memory read operation.             | Input       | P64                   |

| WR           |        | Strobe signal output for external memory write operation.            | Input       | P65                   |

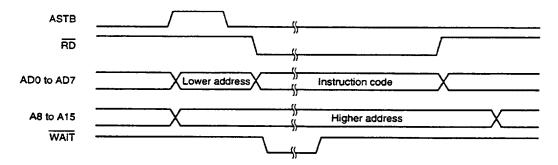

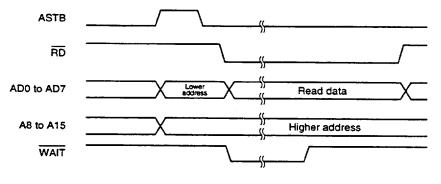

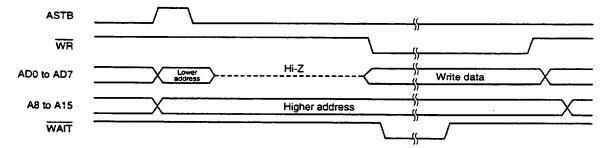

| WAIT         | Input  | Wait insertion when accessing external memory.                       | Input       | P66                   |

| ASTB         | Output | Strobe output that externally latches address information output     | Input       | P67                   |

|              |        | to ports 4 and 5 to access external memory.                          |             |                       |

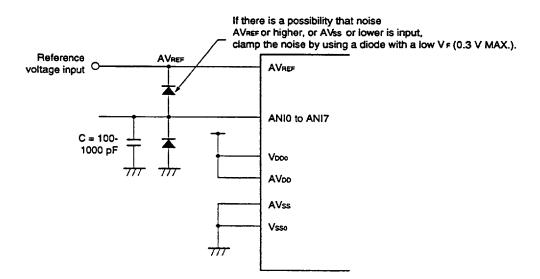

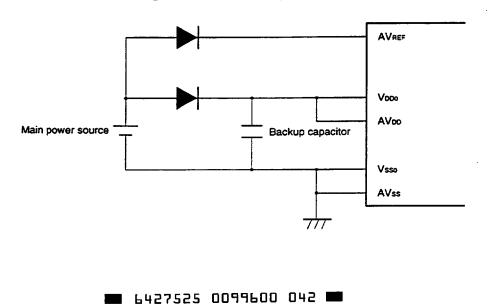

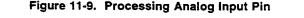

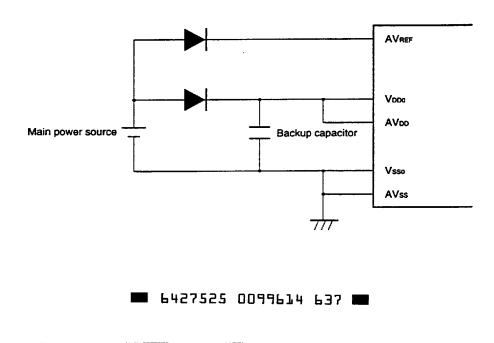

| AVREF        | Input  | A/D converter reference voltage input.                               | -           | _                     |

| AVdd         | -      | A/D converter analog power supply. Connect to VDDO.                  | _           | _                     |

| AVss         | -      | A/D converter ground potential. Connect to Vsso.                     |             | _                     |

| RESET        | Input  | System reset input.                                                  | _           | _                     |

| X1           | Input  | Crystal connection for system clock oscillation.                     |             |                       |

| X2           | _      |                                                                      | -           |                       |

| VDDo         | -      | Positive power supply for ports.                                     | _           | _                     |

| Vsso         | -      | Ground potential for ports.                                          |             | _                     |

| VDD1         | -      | Positive power supply except for ports.                              | -           |                       |

| Vss1         | _      | Ground potential except for ports.                                   | _           |                       |

| TEST         | _      | Test mode set pin. Connect to Vsso directly.                         |             | _                     |

12

🔲 6427525 0099411 O66 페

## 3.3 RECOMMENDED CONNECTION OF UNUSED PINS

The recommended connections of unused pins are shown in Table 3-1.

| Pin Name             | I/O    | Recommended Connection of Unused Pins                |

|----------------------|--------|------------------------------------------------------|

| P00/INTP0/TOFF7      | 1/0    | Individually connect to Vsso via a resistor.         |

| P01/INTP1            |        |                                                      |

| P02/INTP2            |        |                                                      |

| P03/INTP3/ADTRG      |        |                                                      |

| P10/ANI0 to P17/ANI7 | Input  | Individually connect to VDD0 or Vss0 via a resistor. |

| P20/RxD00            | I/O    |                                                      |

| P21/TxD00            |        |                                                      |

| P22/RxD01            |        |                                                      |

| P23/TxD01            |        |                                                      |

| P24/TI50/TO50        |        |                                                      |

| P25/TI51/TO51        |        |                                                      |

| P26/TI52/TO52        |        |                                                      |

| P30/RTP0 to P37/RTP7 |        |                                                      |

| P40/AD0 to P47/AD7   |        |                                                      |

| P50/A8 to P57/A15    |        |                                                      |

| P64/RD               |        |                                                      |

| P65/WR               |        |                                                      |

| P66/WAIT             |        |                                                      |

| P67/ASTB             |        |                                                      |

| TO70 to TO75         | Output | Open                                                 |

| AVDD                 | _      | Connect to VDDo.                                     |

| AVREF                |        | Connect to Vsso.                                     |

| AVss                 |        |                                                      |

| TEST                 |        | Connect to Vsso directly.                            |

Table 3-1. Recommended Connection of Unused Pins

## 🖿 6427525 0099412 TT2 📰

-----

\_ .

\_\_\_\_

\_\_\_\_\_

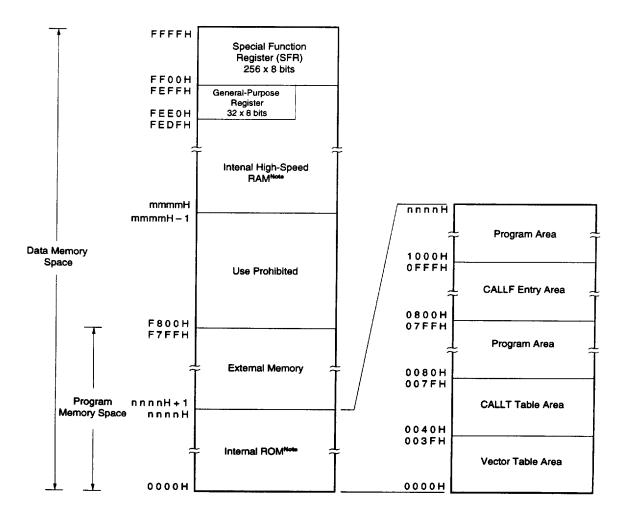

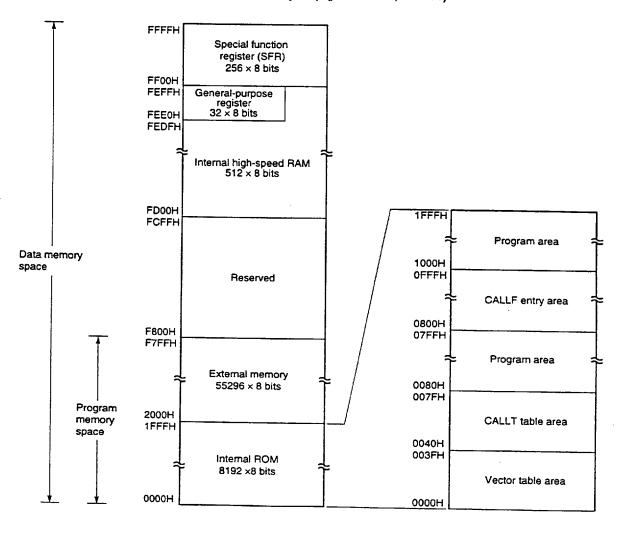

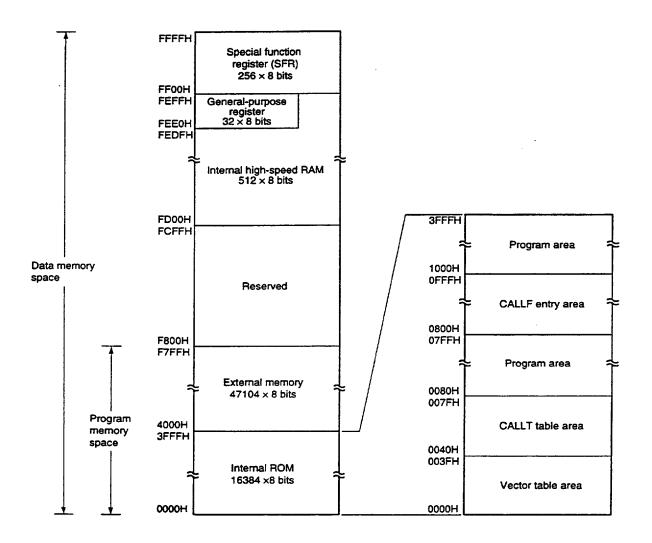

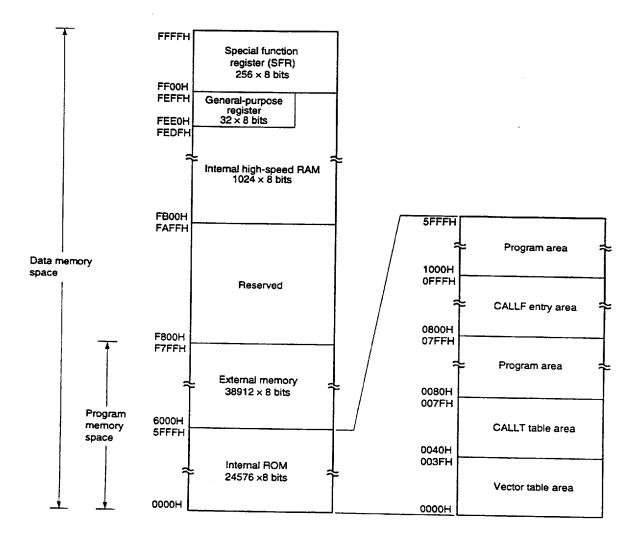

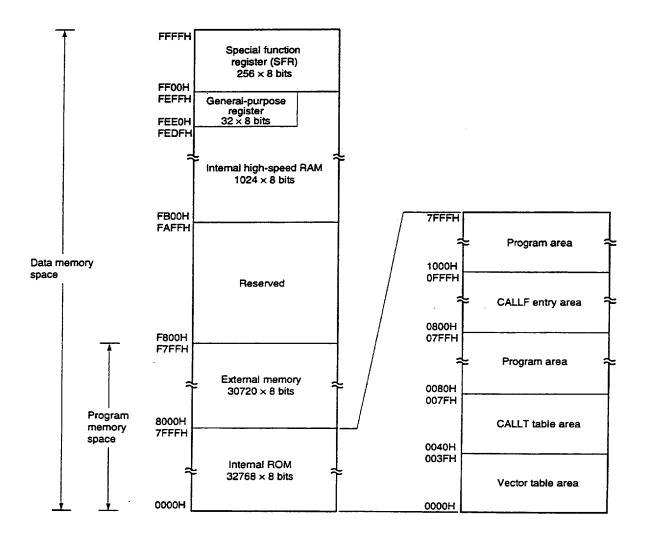

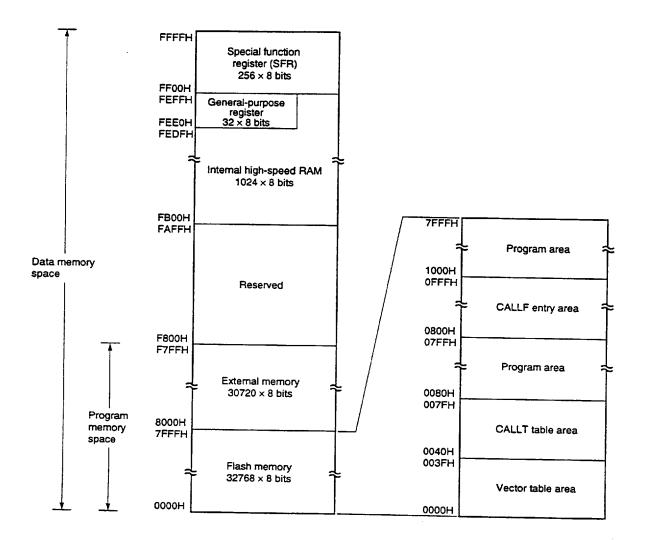

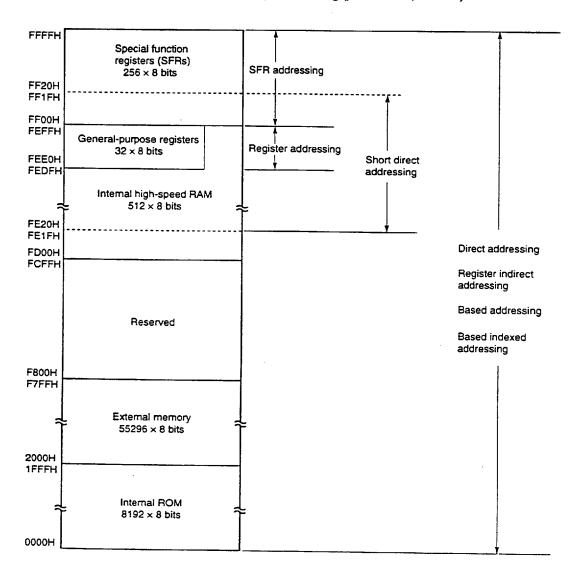

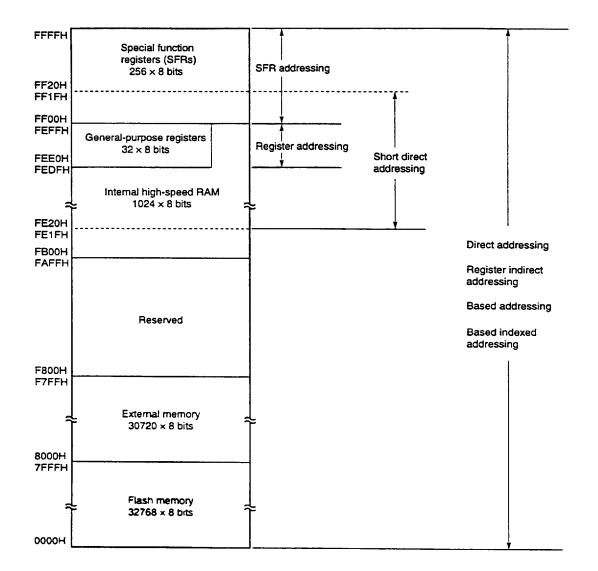

#### 4. MEMORY SPACE

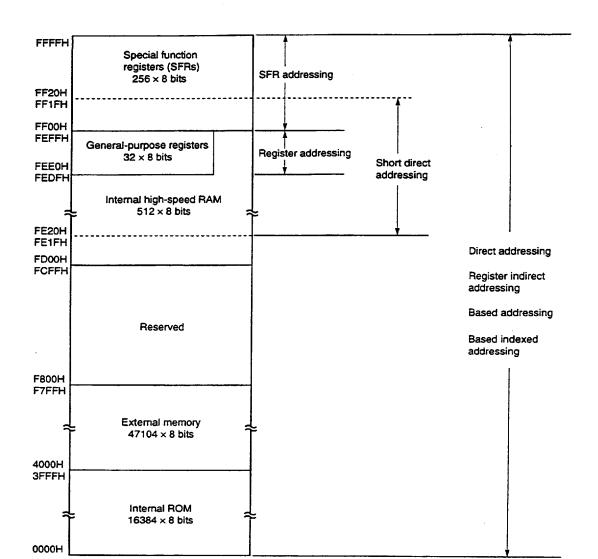

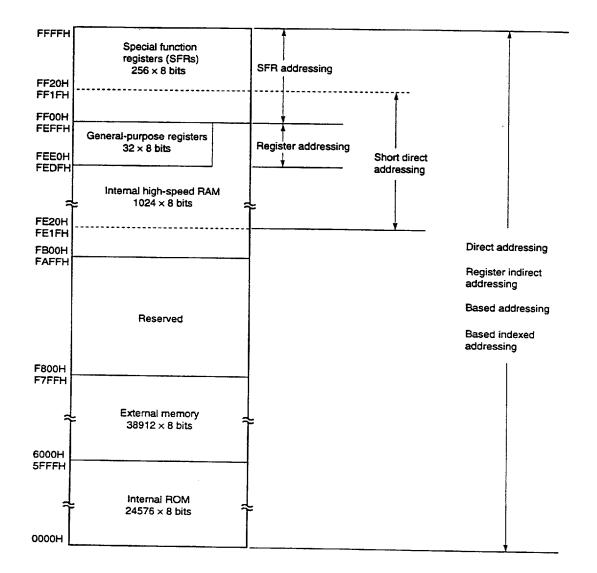

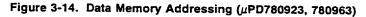

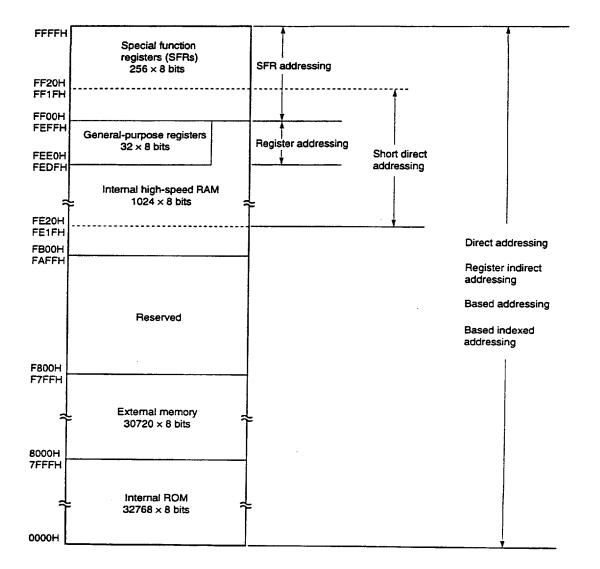

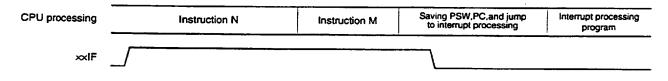

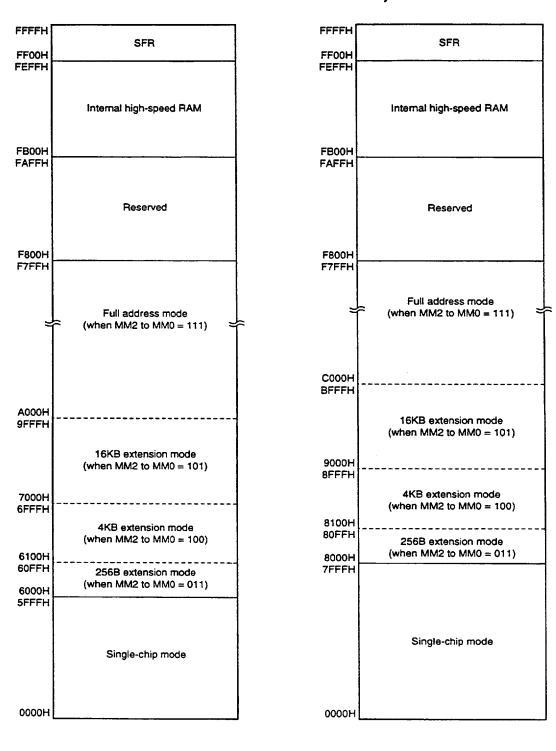

The memory map of the  $\mu$ PD780921, 780922, 780923, and 780924 is shown in Figure 4-1.

Note The internal ROM and internal high-speed RAM capacity differ depending on the product (see the table below).

| Product Name | Intenal ROM End Address | Internal High-Speed RAM<br>Start Address<br>mmmmH |

|--------------|-------------------------|---------------------------------------------------|

| μPD780921    | 1FFFH                   | FD00H                                             |

| μPD780922    | 3FFFH                   |                                                   |

| μPD780923    | 5FFFH                   | FB00H                                             |

| μPD780924    | 7FFFH                   |                                                   |

6427525 0099413 939 🖿

14

## 5. PERIPHERAL HARDWARE FUNCTION FEATURES

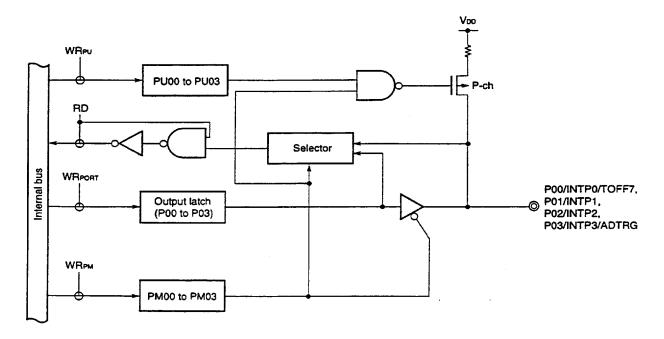

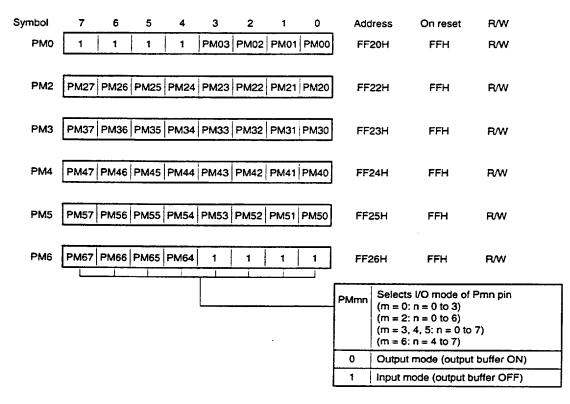

## 5.1 PORTS

Two kinds of I/O ports are provided.

| ÷ | 39 | '           |

|---|----|-------------|

|   |    | : 8<br>: 39 |

## Table 5-1. Functions of Ports

----

| Port Name | Pin Name   | Function                                                                                                                                                                   |

|-----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port 0    | P01 to P03 | I/O port. Input/output can be specified bit-wise.<br>When used as an input port, an on-chip pull-up resistor can be connected by software.                                 |

| Port 1    | P10 to P17 | Input only port.                                                                                                                                                           |

| Port 2    | P20 to P26 | I/O port. Input/output can be specified bit-wise.<br>When used as an input port, an on-chip pull-up resistor can be connected by software.                                 |

| Port 3    | P30 to P37 | I/O port. Input/output can be specified bit-wise.<br>When used as an input port, an on-chip pull-up resistor can be connected by software.                                 |

| Port 4    | P40 to P47 | I/O port. Input/output can be specified bit-wise.<br>When used as an input port, an on-chip pull-up resistor can be connected by software.                                 |

| Port 5    | P50 to P57 | I/O port. Input/output can be specified bit-wise.<br>When used as an input port, an on-chip pull-up resistor can be connected by software.<br>LEDs can be driven directly. |

| Port 6    | P64 to P67 | I/O port. Input/output can be specified bit-wise.<br>When used as an input port, an on-chip pull-up resistor can be connected by software.                                 |

## 📟 6427525 00994<u>1</u>4 875 📟

\_\_\_\_\_

------

15

## NEC

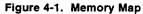

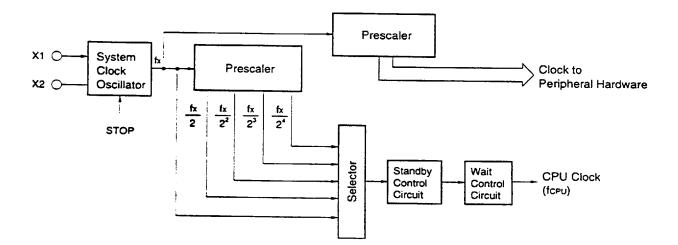

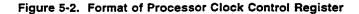

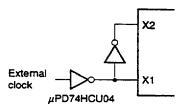

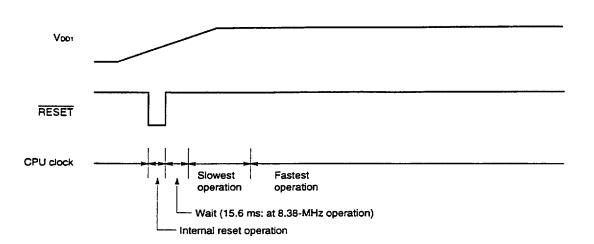

#### 5.2 CLOCK GENERATOR

A system clock generator is incorporated. The instruction exection time can be changed.

• 0.24 μs/0.48 μs/0.96 μs/1.9 μs/3.8 μs (@ 8.38-MHz operation with system clock)

16

17

## NEC

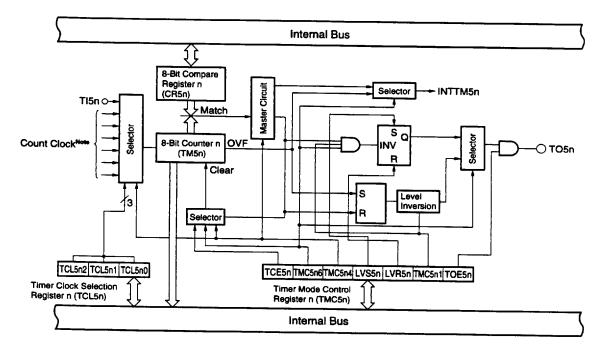

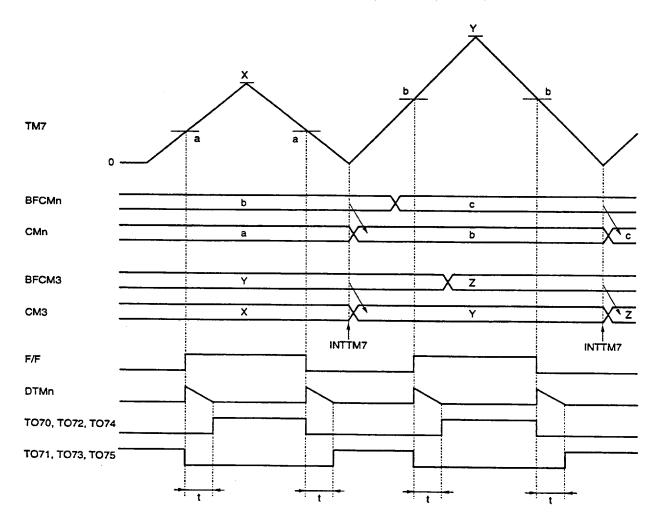

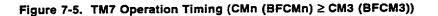

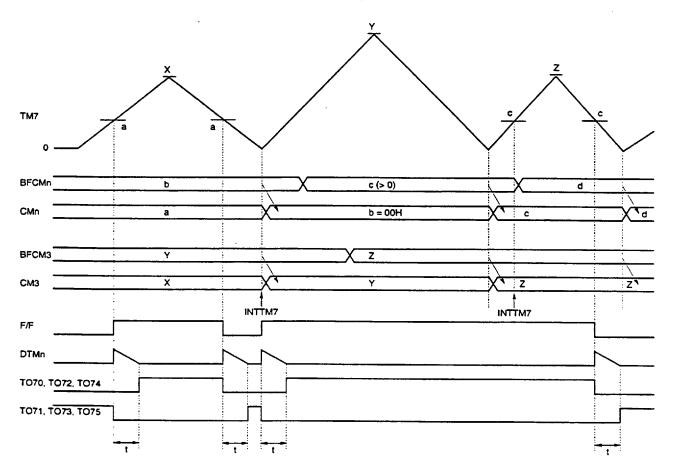

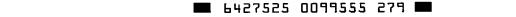

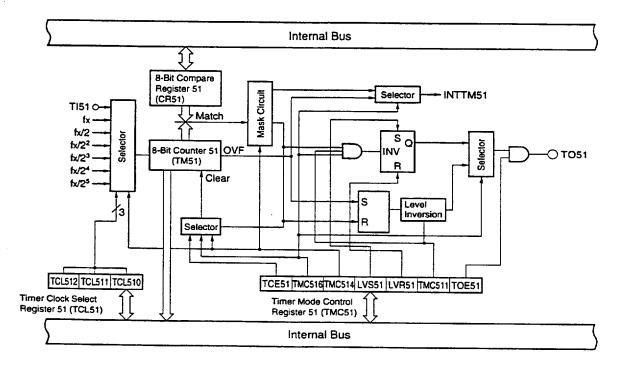

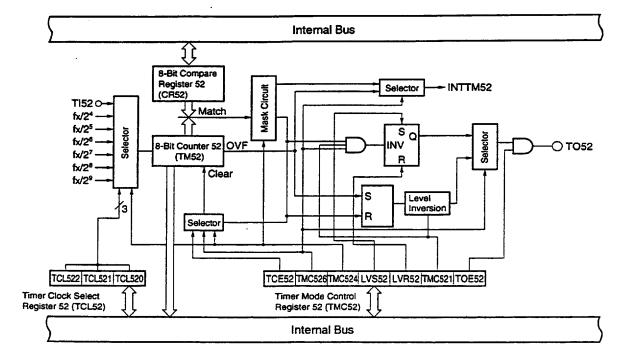

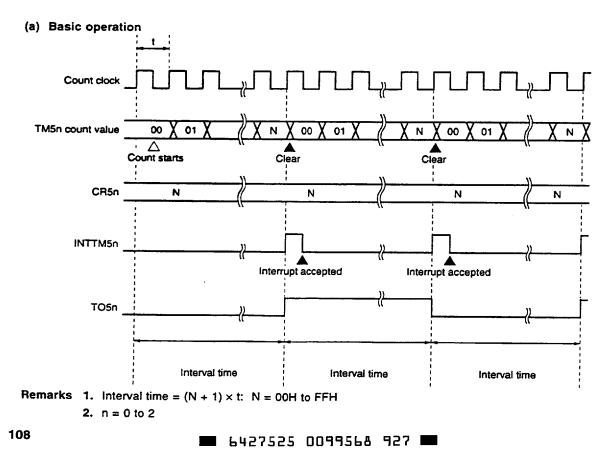

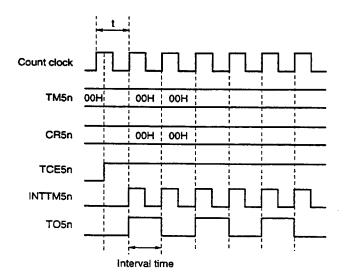

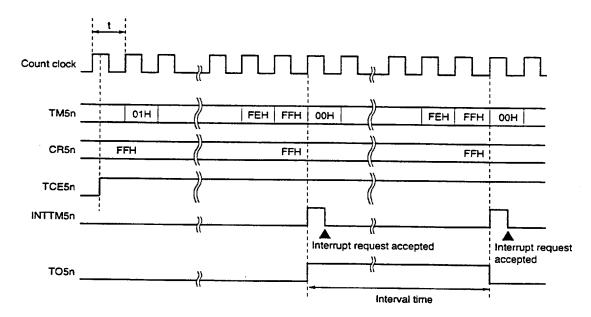

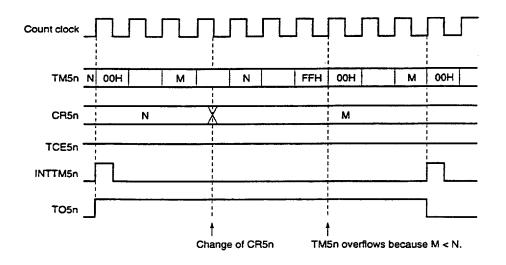

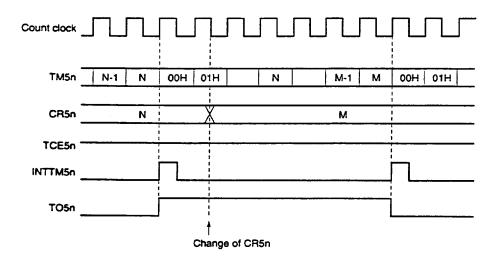

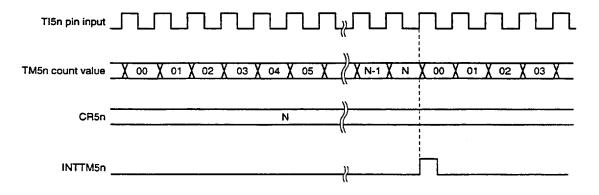

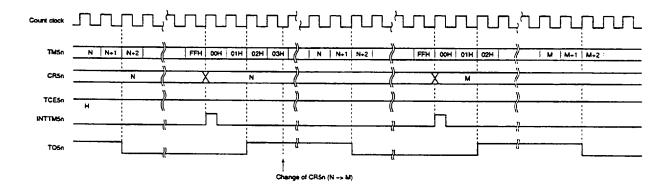

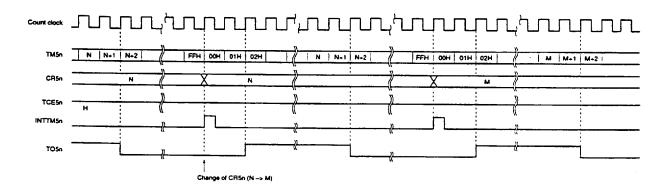

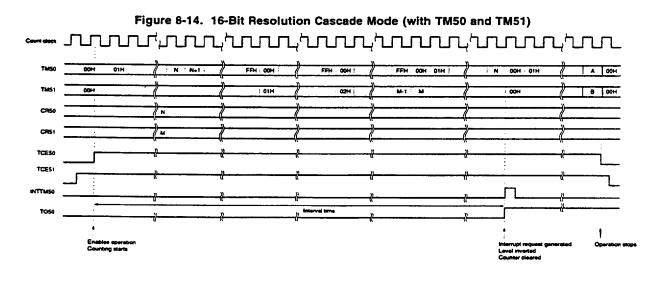

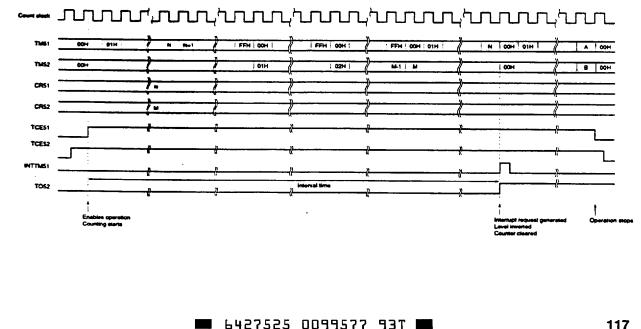

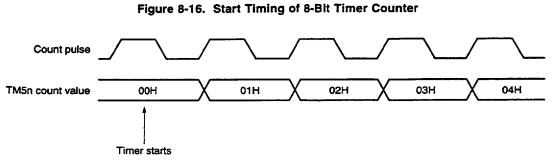

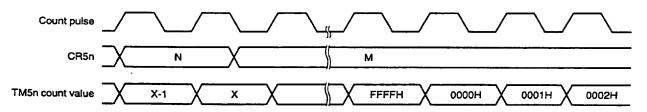

## 5.3 TIMER/EVENT COUNTERS

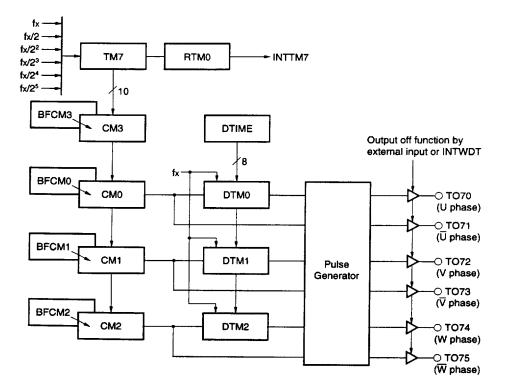

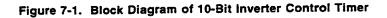

Five timer/event counter channels are incorporated.

- 8-bit timer/event counter : 3 channels

- 10-bit timer : 1 channel

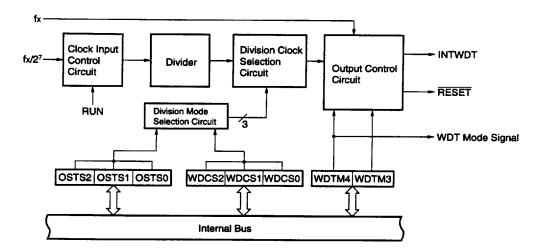

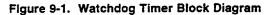

- Watchdog timer : 1 channel

## Table 5-2. Types and Functions of Timer/Event Counters

|           |                        | 8-bit Timer/Event<br>Counter | 10-bit Timer | Watchdog Timer |

|-----------|------------------------|------------------------------|--------------|----------------|

| Туре      | Interval timer         | 3 channels                   | 1 channel    | 1 channel      |

|           | External event counter | 3 channels                   |              |                |

| Functions | Timer output           | 3 outputs                    | 6 outputs    |                |

|           | PWM output             | 3 outputs                    |              |                |

|           | Square wave output     | 3 outputs                    | _            |                |

|           | Interrupt request      | 3                            | 1            | 1              |

Note Count clock differs depending on the timer TM50 : fx/2, fx2<sup>3</sup>, fx2<sup>5</sup>, fx2<sup>7</sup>, fx2<sup>9</sup>, fx<sup>11</sup> TM51 : fx, fx/2, fx2<sup>2</sup>, fx2<sup>3</sup>, fx2<sup>4</sup>, fx2<sup>5</sup> TM52 : fx2<sup>4</sup>, fx2<sup>5</sup>, fx2<sup>6</sup>, fx2<sup>7</sup>, fx2<sup>8</sup>, fx2<sup>9</sup>

\_\_\_\_\_

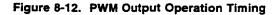

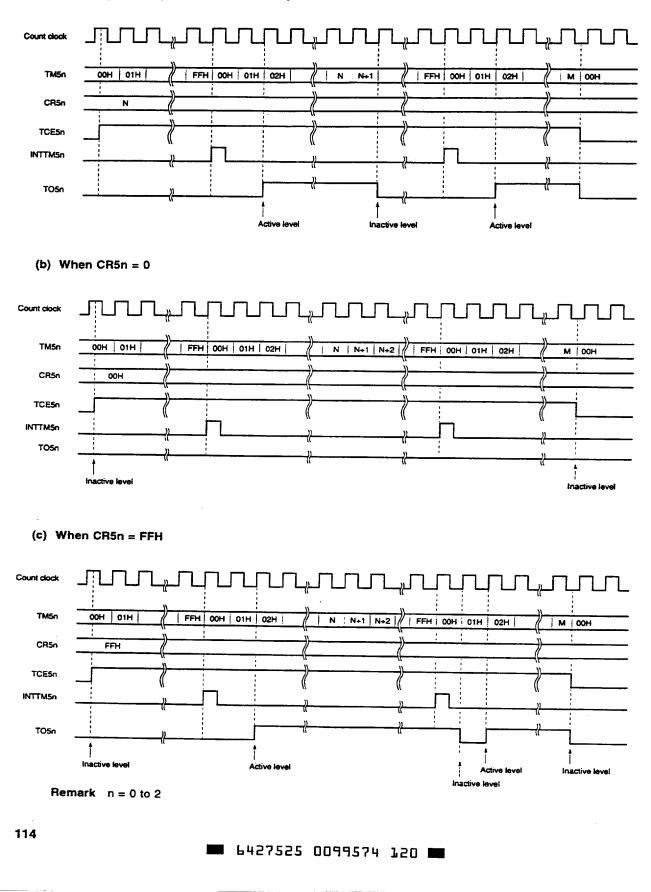

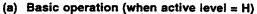

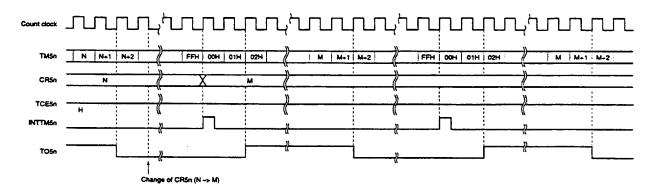

Remark n = 0 to 2

■ 6427525 00994<u>16</u> 648 ■

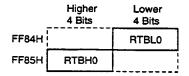

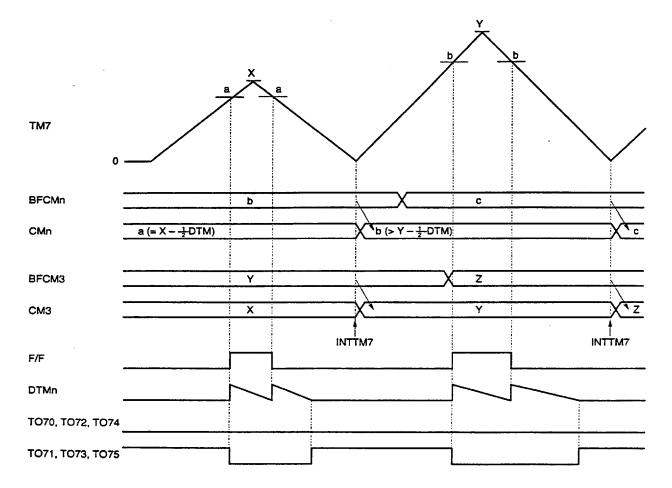

Figure 5-3. 10-bit Timer Block Diagram

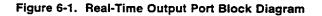

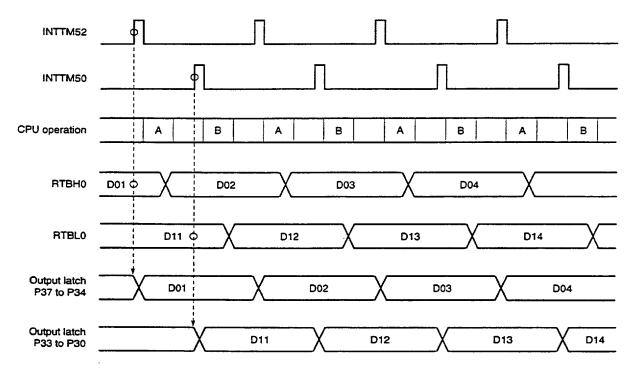

## 5.4 REAL-TIME OUTPUT PORT

The real-time output port outputs data stored in buffers in synchronization with match interrupts of 8-bit timer/event counters (TM50 and TM52) or external interrupts, enabling to output pulses without jitter.

Therefore, the real-time output method is suited for applications which output given patterns at set intervals.

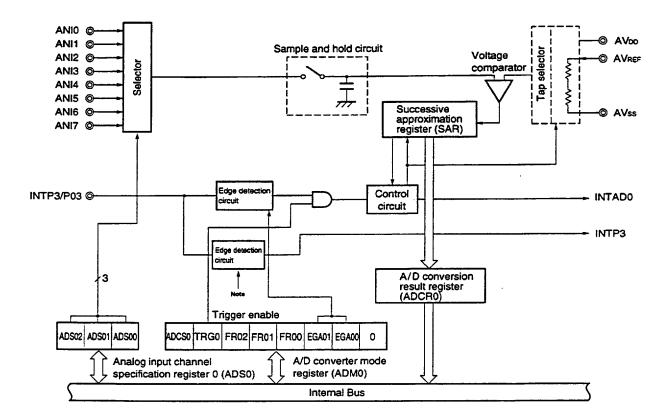

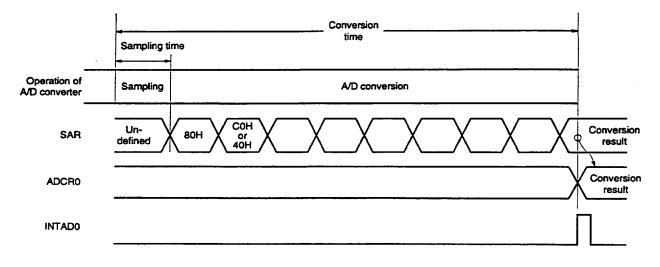

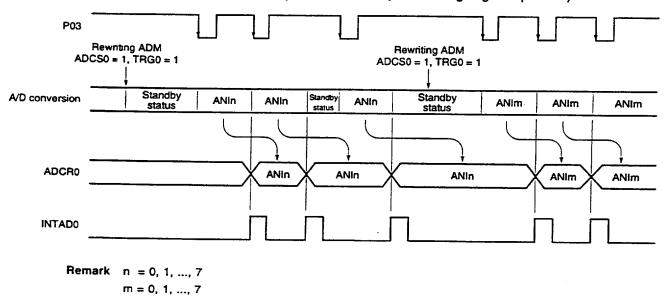

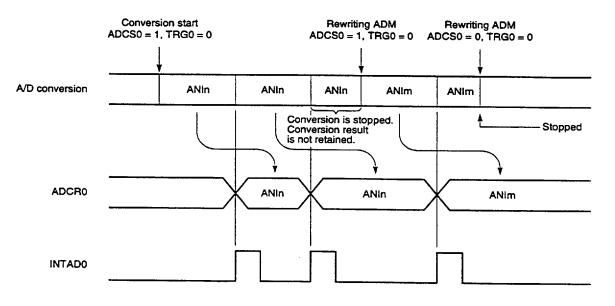

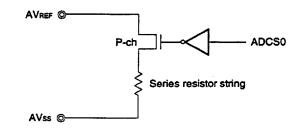

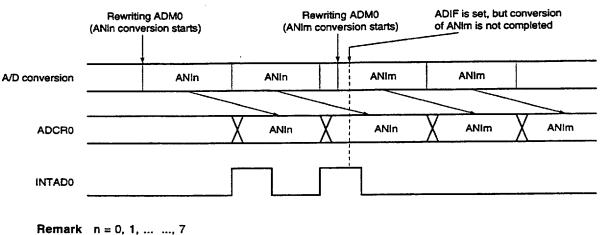

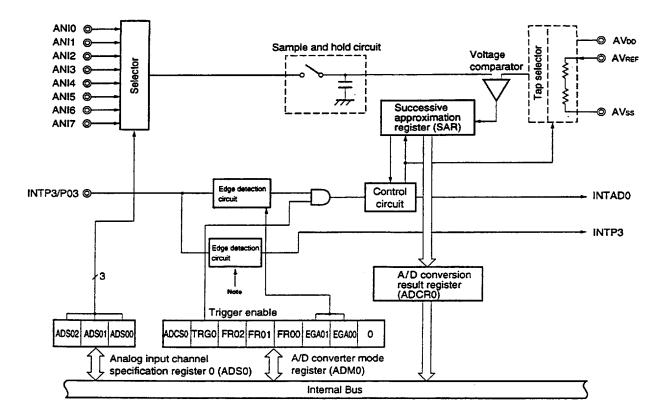

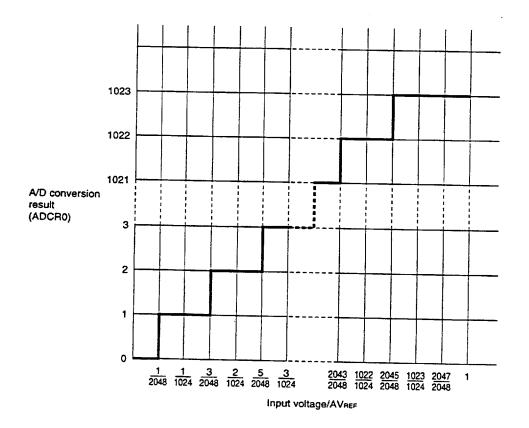

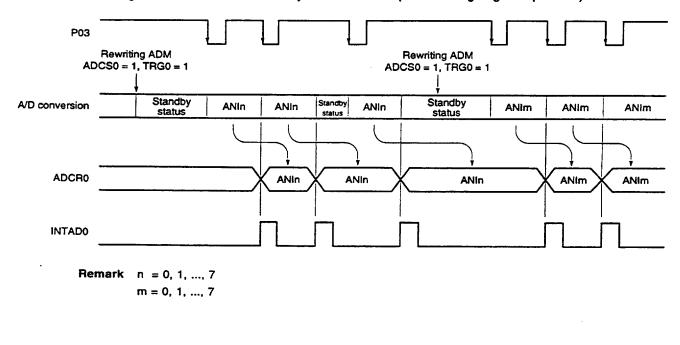

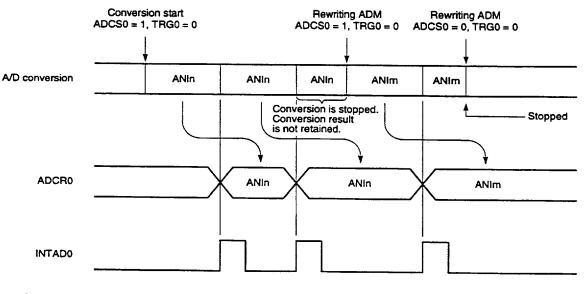

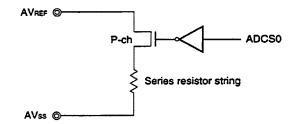

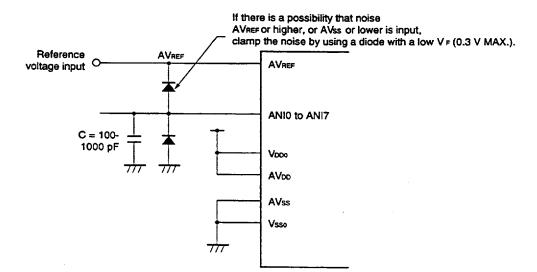

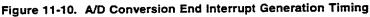

#### 5.5 A/D CONVERTER

NEC

Eight 8-bit resolution A/D converter channels are incorporated. A/D conversion by the following two methods.

- · Hardware start

- Software start

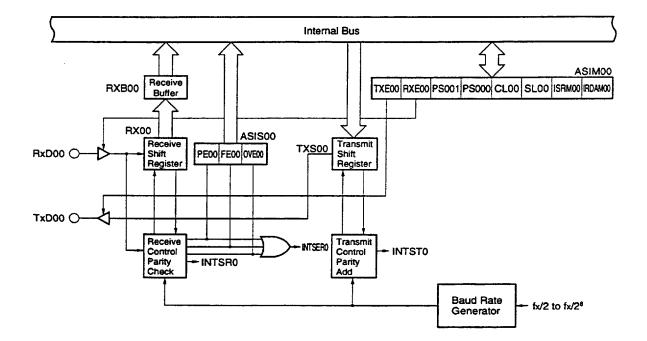

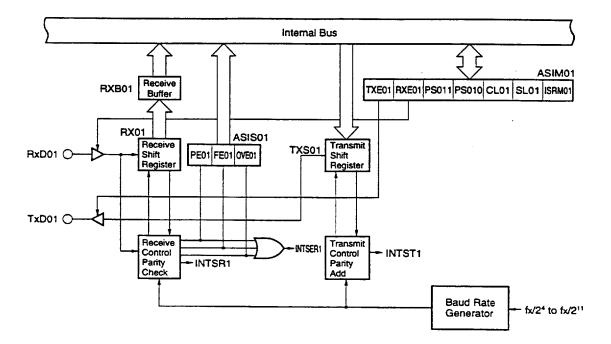

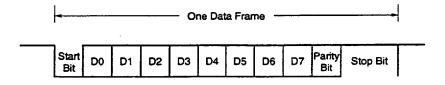

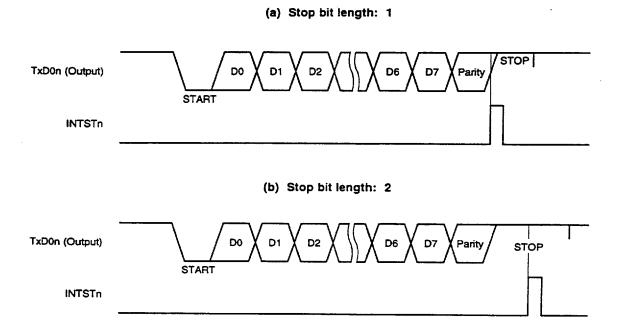

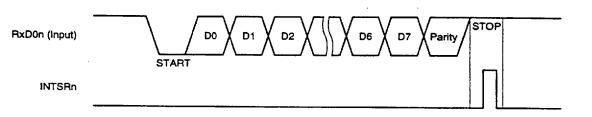

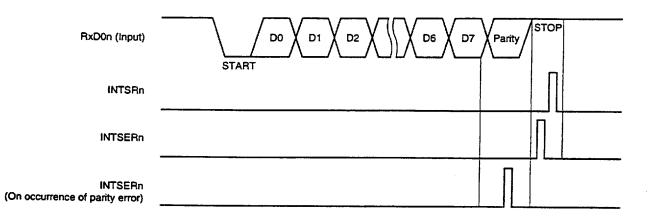

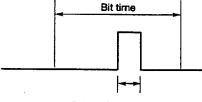

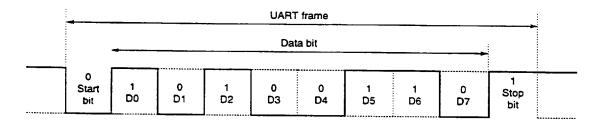

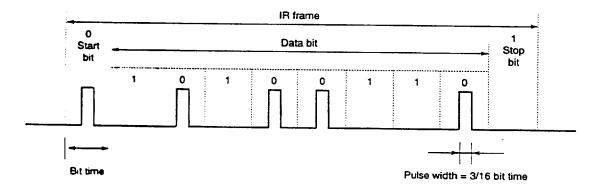

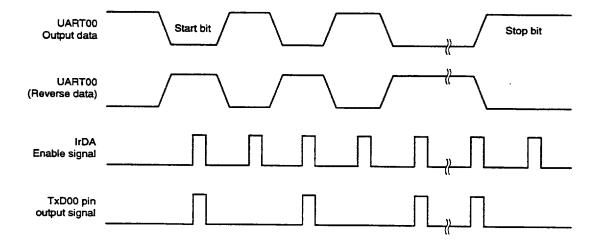

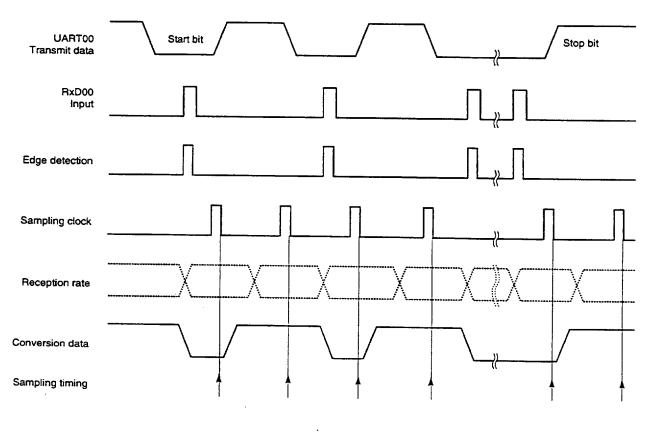

#### 5.6 SERIAL INTERFACE

Two independent serial interface channels (UART00 and UART01) are incorporated.

Each serial interface incorporates a baud-rate generator. Therefore, it is possible to set a serial transfer rate that is independent of the operating clock frequency.

The serial transfer rate can be set from 75 to 76800 bps (@ fx = 8.38-MHz operation) by setting the mode register.

#### Table 5-7. Serial Interface Block Diagram

**Remark** n = 0, 1

#### 6427525 0099420 079 🎟

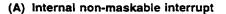

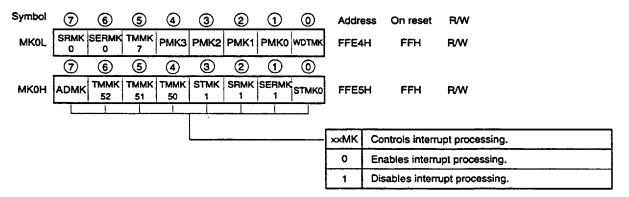

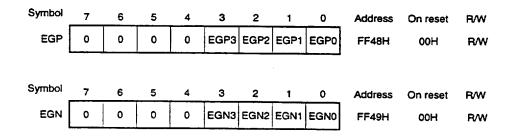

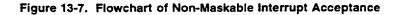

## 6. INTERRUPT FUNCTIONS

NEC

There are 18 interrupt functions of three different kinds as shown below.

Non-maskable interrupt : 1

Maskable interrupt : 16

Software interrupt : 1

|                | Default         |         | Interrupt Source                          | Internal/ | Vector Table | Basic                                  |  |

|----------------|-----------------|---------|-------------------------------------------|-----------|--------------|----------------------------------------|--|

| Interrupt Type | Priority Note 1 | Name    | Trigger                                   | External  | Address      | Configuratin<br>Type <sup>Note 2</sup> |  |

| Non-maskable   | _               | INTWDT  | Watchdog timer overflow                   | Internal  | 0004H        | (A)                                    |  |

|                |                 |         | (when non-maskable interrupt is selected) |           |              |                                        |  |

| Maskable       | 0               | INTWDT  | Watchdog timer overflow                   |           |              | (B)                                    |  |

| Ĺ              |                 |         | (when interval timer is selected)         |           |              |                                        |  |

|                | 1               | INTP0   | Pin input edge detection                  | External  | 0006H        | (C)                                    |  |

|                | 2               | INTP1   |                                           |           | 0008H        |                                        |  |

|                | 3               | INTP2   |                                           |           | 000AH        |                                        |  |

|                | 4               | INTP3   |                                           |           | 000CH        |                                        |  |

| L              | 5               | INTTM7  | TM7 under flow                            | Internal  | 000EH        | (B)                                    |  |

|                | 6               | INTSERO | UART00 receive error generation           |           | 0010H        |                                        |  |

|                | 7               | INTSR0  | UART00 receive termination                |           | 0012H        |                                        |  |

|                | 8               | INTSTO  | UART00 transmit termination               |           | 0014H        |                                        |  |

|                | 9               | INTSER1 | UART01 receive error generation           |           | 0016H        |                                        |  |

|                | 10              | INTSR1  | UART01 receive termination                |           | 0018H        |                                        |  |

|                | 11              | INTST1  | UART01 transmit termination               |           | 001AH        | `                                      |  |

|                | 12              | INTTM50 | TM50 and CR50 match signal generation     |           | 001CH        |                                        |  |

|                | 13              | INTTM51 | TM51 and CR51 match signal generation     |           | 001EH        |                                        |  |

|                | 14              | INTTM52 | TM52 and CR52 match signal generation     |           | 0020H        |                                        |  |

|                | 15              | INTAD0  | A/D conversion termination                |           | 0022H        |                                        |  |

| Software       | _               | BRK     | BRK instruction execution                 | _         | 003EH        | (D)                                    |  |

Notes 1. The default priority is the priority applicable when more than one maskable interrupt is generated. 0 is the highest priority and 15, the lowest.

🖿 6427525 0099421 TO5 🛲

2. Basic configuration types (A) to (D) correspond to (A) to (D) on the next page.

22

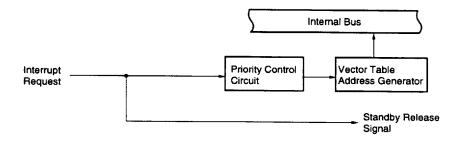

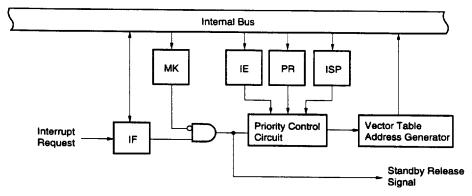

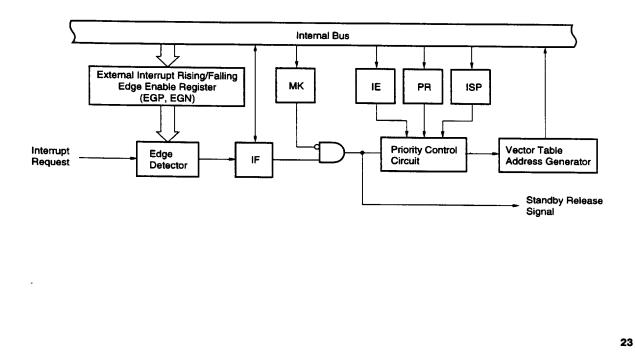

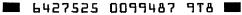

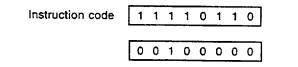

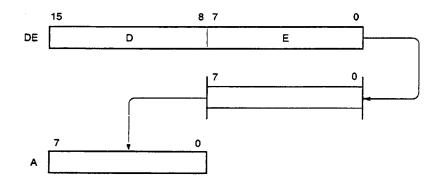

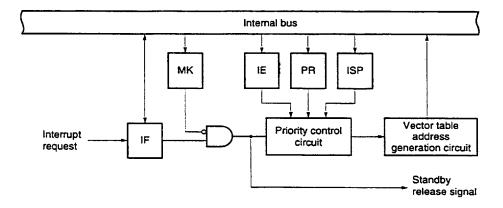

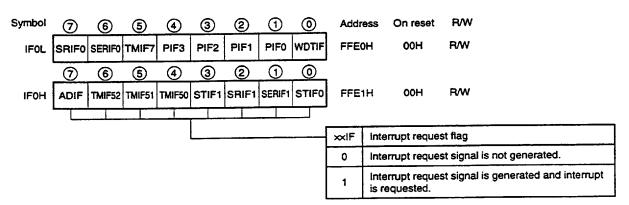

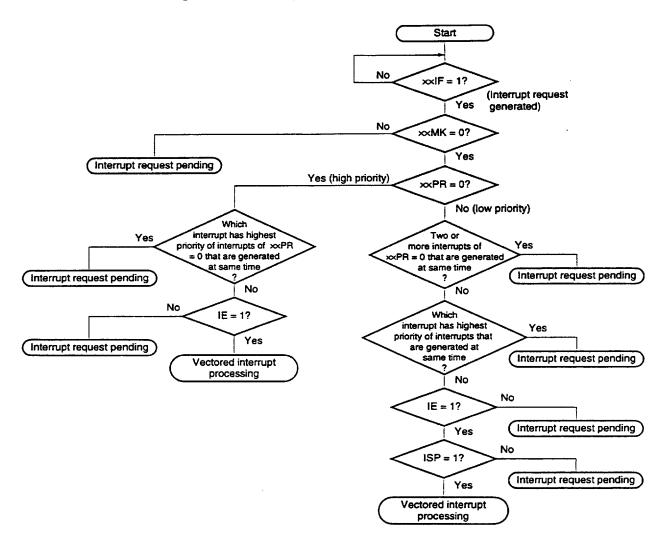

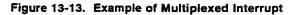

#### Figure 6-1. Basic Interrupt Function Configuration (1/2)

#### (A) Internal non-maskable interrupt

## (B) Internal maskable interrupt

#### (C) External Maskable Interrupt

#### 💻 6427525 0099422 94**] 📖**

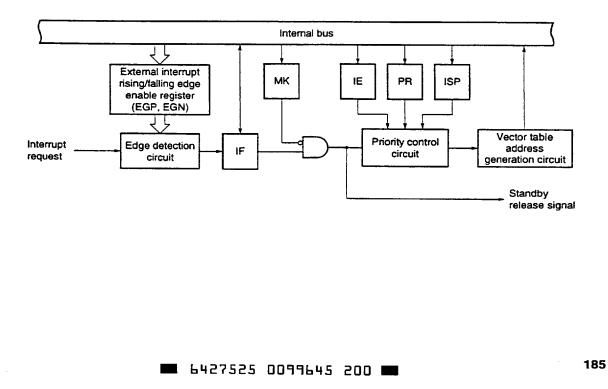

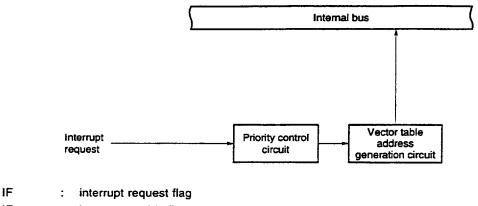

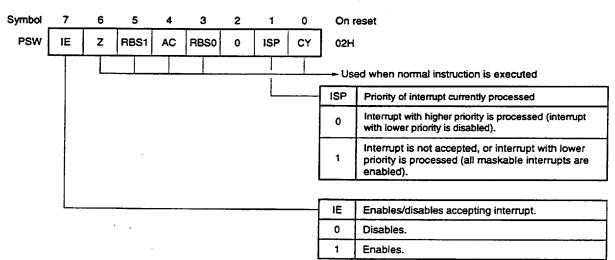

## Figure 6-1. Basic Interrupt Function Configuration (2/2)

## (D) Software Interrupt

- IF : Interrupt request flag

- IE : Interrupt enable flag

- ISP : In-service priority flag

- MK : Interrupt mask flag

- PR : Priority specification flag

## 🖬 6427525 0099423 888 🎟

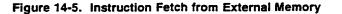

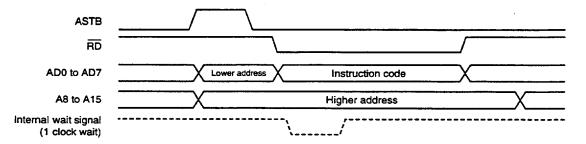

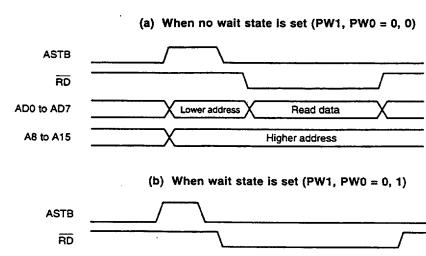

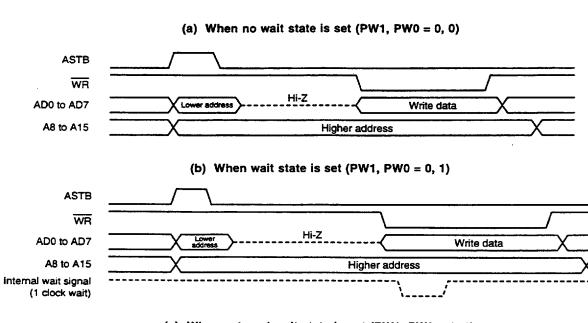

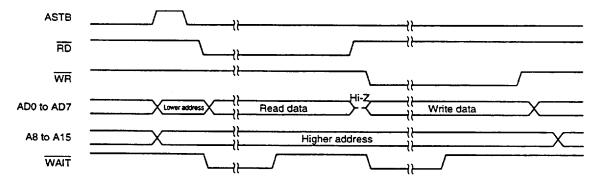

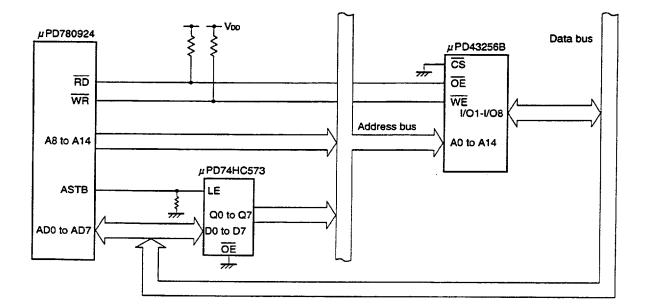

## 7. EXTERNAL DEVICE EXPANSION FUNCTION

The external device expansion function is used to connect external devices to areas other than the internal ROM, RAM and SFR.

Ports 4 to 6 are used for connection with external devices.

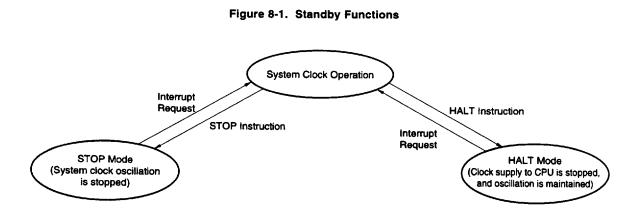

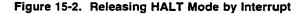

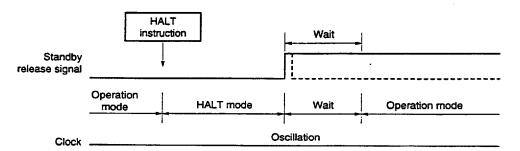

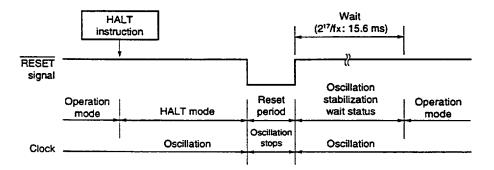

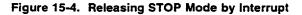

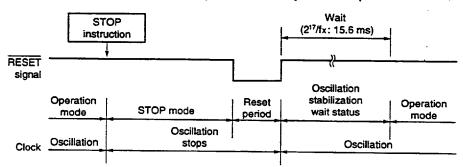

## 8. STANDBY FUNCTIONS

There are the following two standby functions to reduce the current consumption.

- HALT mode : The CPU operating clock is stopped. The average current consumption can be reduced by intermittent operation in combination with the normal operating mode.

- STOP mode : The system clock oscillation is stopped. The whole operation by the system clock is stopped, so that the system operates with ultra-low power dissipation.

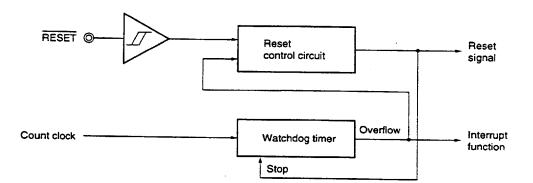

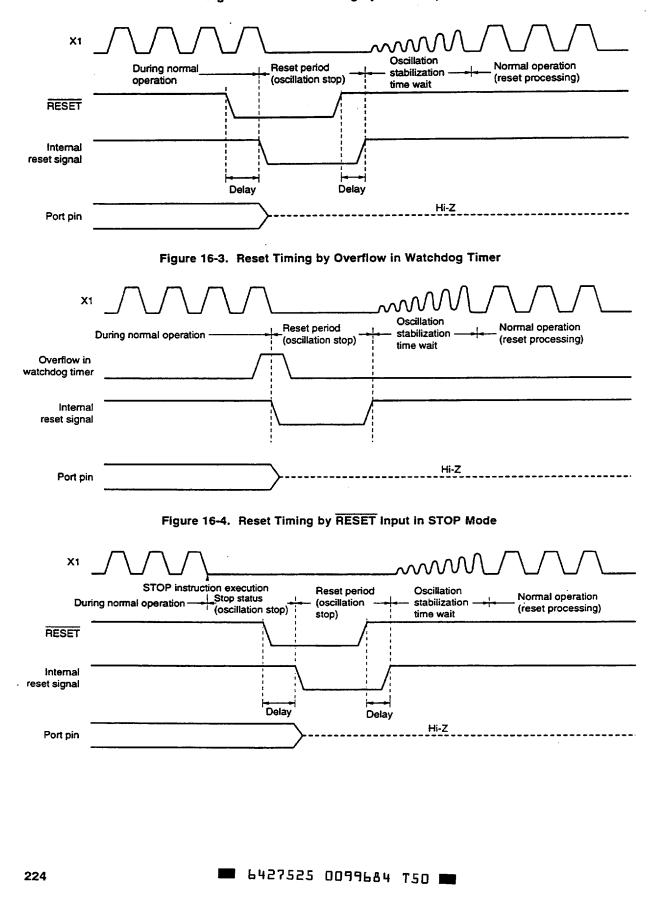

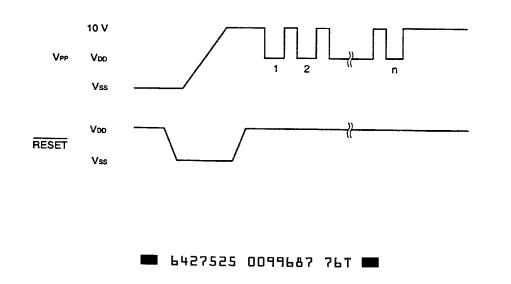

#### 9. RESET FUNCTIONS

There are the following two reset methods.

- External reset by RESET input.

- Internal reset by watchdog timer runaway time detection

| 6427525 | 0099424 | 714 🔳 |

|---------|---------|-------|

|---------|---------|-------|

25

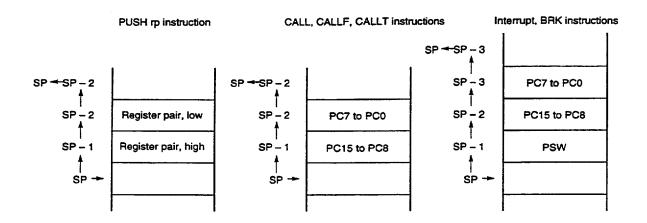

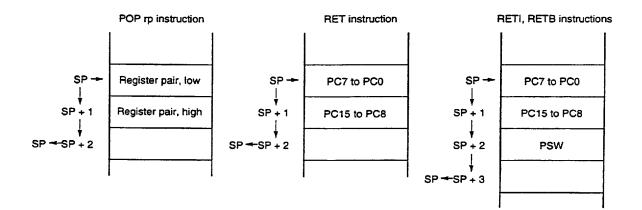

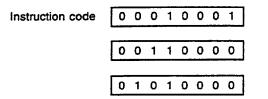

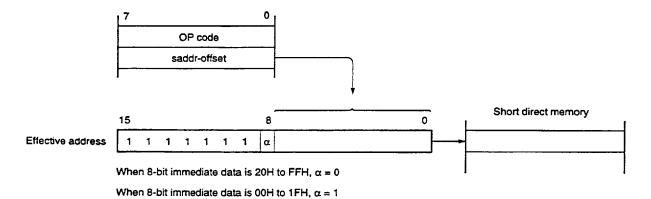

## **10. INSTRUCTION SET**

#### (1) 8-bit instructions

MOV, XCH, ADD, ADDC, SUB, SUBC, AND, OR, XOR, CMP, MULU, DIVUW, INC, DEC, ROR, ROL, RORC, ROLC, ROR4, ROL4, PUSH, POP, DBNZ

|                            |              | T    | 1      | T   | 1     | T          | 1   | T      | <b></b>    | 1                   | T    |      |       |

|----------------------------|--------------|------|--------|-----|-------|------------|-----|--------|------------|---------------------|------|------|-------|

| 2nd Operand<br>1st Operand | \ #byte      | A    | r Note | sfr | saddr | laddr16    | PSW | [DE]   | (HL)       | [HL+byte]<br>[HL+B] |      | 1    | None  |

|                            |              |      |        |     |       |            |     |        | ļ          | [HL+C]              |      |      |       |

| A                          | ADD          | }    | MOV    | MOV | MOV   | MOV        | MOV | MOV    | MOV        | MOV                 |      | ROR  |       |

|                            | ADDC         |      | хсн    | ХСН | хсн   | хсн        | 1   | ХСН    | ХСН        | ХСН                 |      | ROL  |       |

|                            | SUB          |      | ADD    |     | ADD   | ADD        |     |        | ADD        | ADD                 |      | RORC |       |

|                            | SUBC         |      | ADDC   |     | ADDC  | ADDC       |     |        | ADDC       | ADDC                |      | ROLC |       |

|                            | AND          | 1    | SUB    |     | SUB   | SUB        |     | -      | SUB        | SUB                 |      |      |       |

|                            | OR           |      | SUBC   |     | SUBC  | SUBC       |     | 1      | SUBC       | SUBC                |      |      |       |

|                            | XOR          | 1    | AND    |     | AND   | AND        |     |        | AND        | AND                 |      | 1    |       |

|                            | CMP          |      | OR     |     | OR    | OR         |     |        | OR         | OR                  |      |      |       |

|                            |              |      | XOR    |     | XOR   | 1          |     |        | 1          |                     |      |      |       |

|                            |              |      | CMP    |     | CMP   | XOR<br>CMP |     |        | XOR<br>CMP | XOR<br>CMP          |      |      |       |

| r                          | MOV          | MOV  |        |     |       |            |     |        | CIVIF      |                     |      |      | +     |

| -                          |              | ADD  |        |     |       |            |     |        |            |                     |      |      | INC   |

|                            |              |      |        |     |       |            |     |        |            |                     |      |      | DEC   |

|                            |              | ADDC |        |     |       |            |     |        |            |                     |      |      |       |

|                            |              | SUB  |        | i   |       |            |     |        |            |                     |      |      |       |

|                            |              | SUBC |        |     |       |            |     |        |            |                     |      |      |       |

|                            |              | AND  |        |     |       |            |     |        |            |                     |      |      |       |

|                            |              | OR   |        |     |       |            |     |        |            |                     |      |      |       |

|                            |              | XOR  |        |     |       |            |     |        |            |                     |      |      |       |

|                            |              | CMP  |        |     |       |            |     |        |            |                     |      |      |       |

| B, C                       |              |      |        |     |       |            |     |        |            |                     | DBNZ |      |       |

| str                        | MOV          | MOV  |        |     |       |            |     |        |            |                     |      |      |       |

| saddr                      | MOV          | MOV  |        |     |       |            |     |        |            |                     | DBNZ |      | INC   |

|                            | ADD          |      |        |     |       |            |     |        |            |                     |      |      | DEC   |

|                            | ADDC         |      |        |     |       |            | 1   |        |            |                     |      |      |       |

|                            | SUB          |      |        |     |       |            |     |        |            |                     |      |      |       |

|                            | SUBC         |      |        |     |       |            |     |        | ĺ          |                     |      |      |       |

|                            | AND          |      |        |     |       | 1          |     |        | [          |                     |      |      |       |

|                            | OR           |      |        |     |       | l l        |     |        |            |                     |      |      |       |

|                            | XOR          |      |        |     |       |            |     |        |            |                     |      |      |       |

|                            | CMP          |      | [      |     |       |            |     |        |            |                     |      |      |       |

| laddr16                    |              | MOV  |        |     |       |            |     |        |            |                     |      |      |       |

| PSW                        | MOV          | MOV  |        |     |       |            |     |        |            |                     |      |      | PUSH  |

|                            |              |      |        |     |       |            |     | i<br>I |            |                     | -    |      | POP   |

| [DE]                       |              | MOV  |        |     |       |            |     |        |            |                     |      |      |       |

| [HL]                       |              | MOV  |        |     |       |            |     |        |            |                     |      |      | ROR4  |

| [HL+byte]                  | ├── ┤        | MOV  |        |     |       |            |     |        |            |                     |      |      | ROL4  |

| [HL+B]                     |              |      | [      |     |       |            | i i |        |            |                     |      |      |       |

| [HL+C]                     |              |      | 1      |     |       |            |     |        |            |                     |      |      |       |

| X                          | <u>├</u> ─── | -    |        |     |       |            |     |        |            | — <del> </del>      |      |      |       |

| <u>с</u>                   | ┟╼╴╶┧        |      |        |     |       |            |     |        |            |                     |      |      | MULU  |

|                            | r=A          |      |        |     |       |            |     |        |            |                     |      |      | DIVUW |

Note Except r=A

26

🖬 6427525 0099425 650 🔳

-----

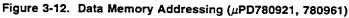

#### (2) 16-bit instructions

MOVW, XCHW, ADDW, SUBW, CMPW, PUSH, POP, INCW, DECW

| 2nd Operand<br>1st Operand | #byte | AX                   | rp <sup>Note</sup> | strp | saddrp | laddr16                                | SP   | None                    |

|----------------------------|-------|----------------------|--------------------|------|--------|----------------------------------------|------|-------------------------|

| AX                         | ADDW  |                      | MOVW               | MOVW | MOVW   | MOVW                                   | MOVW |                         |

|                            | SUBW  |                      | хснw               |      |        |                                        |      |                         |

|                            | CMPW  |                      |                    |      |        |                                        |      |                         |

| rp                         | MOVW  | MOVW <sup>Note</sup> |                    |      |        |                                        |      | INCW, DECW<br>PUSH, POP |

| strp                       | MOVW  | MOVW                 |                    |      |        |                                        |      |                         |

| saddrp                     | MOVW  | MOVW                 |                    |      |        |                                        |      |                         |

| laddr16                    |       | MOVW                 |                    |      |        |                                        | 1    |                         |

| SP                         | MOVW  | MOVW                 |                    |      |        | ······································ | 1    |                         |

Note Only when rp = BC, DE, HL.

## (3) Bit manipulation instructions

MOV1, AND1, OR1, XOR1, SET1, CLR1, NOT1, BT, BF, BTCLR

| 2nd Operand | A L 1                       |                             |                             |                             |                             |      |                   |                      |

|-------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|------|-------------------|----------------------|

| 1st Operand | A.bit                       | sfr.bit                     | saddr.bit                   | PWS.bit                     | [HL].bit                    | CY   | \$addr16          | None                 |

| A.bit       |                             |                             |                             |                             |                             | MOV1 | BT<br>BF<br>BTCLR | SET1<br>CLR1         |

| sfr.bit     |                             |                             |                             |                             |                             | MOV1 | BT<br>BF<br>BTCLR | SET1<br>CLR1         |

| saddr.bit   |                             |                             |                             |                             |                             | MOV1 | BT<br>BF<br>BTCLR | SET1<br>CLR1         |

| PSW.bit     |                             |                             |                             |                             |                             | MOV1 | BT<br>BF<br>BTCLR | SET1<br>CLR1         |

| [HL].bit    |                             |                             |                             |                             |                             | MOV1 | BT<br>BF<br>BTCLR | SET1<br>CLR1         |

| CY          | MOV1<br>AND1<br>OR1<br>XOR1 | MOV1<br>AND1<br>OR1<br>XOR1 | MOV1<br>AND1<br>OR1<br>XOR1 | MOV1<br>AND1<br>OR1<br>XOR1 | MOV1<br>AND1<br>OR1<br>XOR1 |      |                   | SET1<br>CLR1<br>NOT1 |

## 🖬 6427525 0099426 597 🛤

Powered by ICminer.com Electronic-Library Service CopyRight 2003

\_\_\_\_\_

## (4) Call instruction/branch instructions

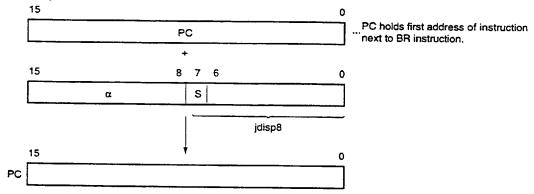

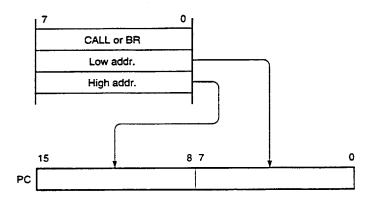

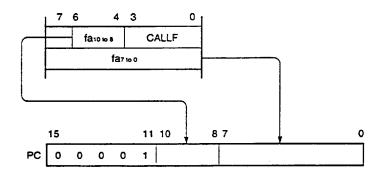

CALL, CALLF, CALLT, BR, BC, BNC, BZ, BNZ, BT, BF, BTCLR, DBNZ

| 2nd Operand<br>1st Operand | AX | laddr16  | laddr11 | [addr5] | \$addr16                |

|----------------------------|----|----------|---------|---------|-------------------------|

| Basic instruction          | BR | CALL, BR | CALLF   | CALLT   | BR, BC, BNC,<br>BZ, BNZ |

| Compound instruction       |    |          |         |         | BT,BF,BTCLR,<br>DBNZ    |

## (5) Other Instructions

ADJBA, ADJBS, BRK, RET, RETI, RETB, SEL, NOP, EI, DI, HALT, STOP

28

\_ \_ \_ \_

## **11. PACKAGE DRAWINGS**

NEC

## 64 PIN PLASTIC SHRINK DIP (750 mil)

σΙ

1) Each lead centerline is located within 0.17 mm (0.007 inch) of its true position (T.P.) at maximum material condition.

2) item "K" to center of leads when formed parallel.

NM

$\oplus$

D

| ITEM | MILLIMETERS  | INCHES       |

|------|--------------|--------------|

| Α    | 58.68 MAX.   | 2.311 MAX.   |

| В    | 1.78 MAX.    | 0.070 MAX.   |

| С    | 1.778 (T.P.) | 0.070 (T.P.) |

| D    | 0.50±0.10    | 0.020+0.004  |

| F    | 0.9 MIN.     | 0.035 MIN.   |

| G    | 3.2±0.3      | 0.126±0.012  |

| H    | 0.51 MIN.    | 0.020 MIN.   |

| 1    | 4.31 MAX.    | 0.170 MAX.   |

| J    | 5.08 MAX.    | 0.200 MAX.   |

| К    | 19.05 (T.P.) | 0.750 (T.P.) |

| L    | 17.0         | 0.669        |

| м    | 0.25+0.10    | 0.010+0.004  |

| N    | 0.17         | 0.007        |

| R    | 0~15°        | 0~15°        |

М

СВ

P64C-70-750A,C-1

## 🖬 6427525 0099428 36T 🎟

## 64 PIN PLASTIC QFP (□14)

detail of lead end

#### NOTE

Each lead centerline is located within 0.15 mm (0.006 inch) of its true position (T.P.) at maximum material condition.

| ITEM |             | P64GC-80-AB8-3 |

|------|-------------|----------------|

| 1151 | MILLIMETERS | INCHES         |

| A    | 17.6±0.4    | 0.693±0.016    |

| В    | 14.0±0.2    | 0.551+0.009    |

| С    | 14.0±0.2    | 0.551+0.009    |

| D    | 17.6±0.4    | 0.693±0.016    |

| F    | 1.0         | 0.039          |

| G    | 1.0         | 0.039          |

| н    | 0.35±0.10   | 0.014+0.004    |

| 1    | 0.15        | 0.006          |

| J    | 0.8 (T.P.)  | 0.031 (T.P.)   |

| κ    | 1.8±0.2     | 0.071±0.008    |

| L    | 0.8±0.2     | 0.031+0.009    |

| м    | 0.15+0.10   | 0.006+0.004    |

| N    | 0.10        | 0.004          |

| Р    | 2.55        | 0.100          |

| ۵    | 0.1±0.1     | 0.004±0.004    |

| S    | 2.85 MAX.   | 0.112 MAX.     |

#### 30

🛚 6427525 0099429 2T6 🖿

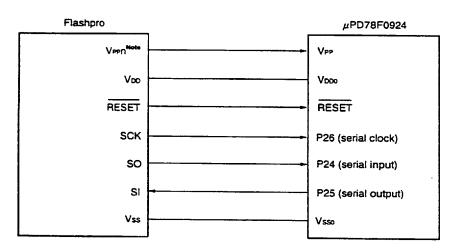

## **APPENDIX A. DEVELOPMENT TOOLS**

The following development tools are available for system development using the  $\mu$ PD780924 subseries.

## Language Processing Software

| RA78K/0 Notes 1, 2, 3, 4     | 78K/0 series common assembler package              | ····· |

|------------------------------|----------------------------------------------------|-------|

| CC78K/0 Notes 1, 2, 3, 4     | 78K/0 series common C compiler package             |       |

| DF780964 Notes 1, 2, 3, 4, 8 | μPD780924 subseries common device file             | ·     |

| CC78K/0-L Notes 1, 2, 3, 4   | 78K/0 series common C compiler library source file |       |

## Flash Memory Writing Tools

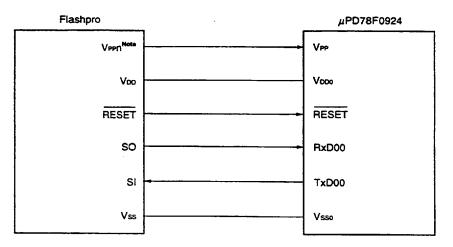

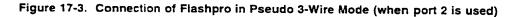

| Flashpro                                                                                                 | Dedicated flash memory writer. The Flashpro is a product of Naitou Densei Machida Seisakusho Co., Ltd. |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| PA-FLASH64CW<br>(temporary name) <sup>Note 8</sup><br>PA-FLASH64GC<br>(temporary name) <sup>Note 8</sup> | Adapter to write data to the flash memory                                                              |

## **Debugging Tools**

| IE-780000-SL                 | 75XL, 78K/0S, 78K/0, and 78K/IV series common in-circuit emulator                            |

|------------------------------|----------------------------------------------------------------------------------------------|

| (temporary name) Note 8      |                                                                                              |

| IE-78K0-SL-EM                | 78K/0 series common CPU core board                                                           |

| (temporary name) Note 8      |                                                                                              |

| IE-780964-SL-EM1             | Probe board to emulate µPD780924 subseries products                                          |

| (temporary name) Note 8      |                                                                                              |

| EP-64CW-SL                   | Emulation probe for 64-pin plastic shrink DIP (CW type)                                      |

| (temporary name) Note 8      |                                                                                              |

| EP-64GC-SL                   | Emulation probe for 64-pin plastic QFP (GC-AB8 type)                                         |

| (temporary name) Note 8      |                                                                                              |

| EV-9200GC-64                 | Socket to be mounted on target system board created for the 64-pin plastic QFP (GC-AB8 type) |

| SM78K0 Notes 5, 6, 7         | 78K/0 series common system simulator                                                         |

| 1D78K0 Notes 4, 5, 6, 7      | IE-780000-SL integrated debugger                                                             |

| DF780964 Notes 4, 5, 6, 7, 8 | Device file common to µPD780924 subseries                                                    |

#### Real-Time OSs

| RX78K/0 Notes 1, 2, 3, 4 | 78K/0 series real-time OS |

|--------------------------|---------------------------|

| MX78K0 Notes 1, 2, 3, 4  | 78K/0 series OS           |

## Fuzzy Inference Development Support Systems

| FE9000 Note 1/FE9200 Note 5 | Fuzzy knowledge data creation tool |

|-----------------------------|------------------------------------|

| FT9080 Note 1/FT9085 Note 2 | Translator                         |

| FI78K0 Notes 1, 2           | Fuzzy inference module             |

| FD78K0 Notes 1, 2           | Fuzzy inference debugger           |

Notes 1. PC-9800 series (MS-DOS<sup>™</sup>) based

- 2. IBM PC/AT<sup>™</sup> and compatibles (PC DOS<sup>™</sup>/IBM DOS<sup>™</sup>/MS-DOS) based

- 3. HP9000 series 300<sup>™</sup> (HP-UX<sup>™</sup>) based

- 4. HP9000 series 700<sup>™</sup> (HP-UX) based, SPARCstation<sup>™</sup> (SunOS<sup>™</sup>) based, EWS4800 series (EWS-UX/V) based

- 5. PC-9800 series (MS-DOS + Windows™) based

- 6. IBM PC/AT and compatibles (PC DOS/IBM DOS/MS-DOS + Windows) based

- 7. NEWS<sup>™</sup> (NEWS-OS<sup>™</sup>) based

- 8. Under development

Remark RA78K/0, CC78K/0, SM78K0, ID78K0, and RX78K/0 are used in combination with DF780964.

#### 🖬 6427525 0099431 954 📰

## APPENDIX B. RELATED DOCUMENTS

#### **Device Related Documents**

| Document Name                                                     | Docume<br>English<br>Planned<br>This manual<br>Planned<br>—<br>IEU-1372<br>— | nt No.   |

|-------------------------------------------------------------------|------------------------------------------------------------------------------|----------|

|                                                                   | English                                                                      | Japanese |

| μPD780924 Subseries User's Manual                                 | Planned                                                                      | Planned  |

| μPD780921, 780922, 780923, 780924 Preliminary Product Information | This manual                                                                  | U11804J  |

| µPD78F0924 Preliminary Product Information                        | Planned                                                                      | Planned  |

| µPD780924 Subseries Special Function Register Table               | _                                                                            | Planned  |

| 78K/0 Series User's Manual Instructions                           | IEU-1372                                                                     | IEU-849  |

| 78K/0 Series Instruction Table                                    | _                                                                            | U10903J  |

| 78K/0 Series Instruction Set                                      |                                                                              | U10904J  |

## **Development Tool Documents (User's Manuals)**

| Document Name                                |                                                     | Document No. |          |

|----------------------------------------------|-----------------------------------------------------|--------------|----------|

|                                              |                                                     | English      | Japanese |

| RA78K Series Assembler Package               | Operation                                           | EEU-1399     | EEU-809  |

|                                              | Language                                            | EEU-1404     | EEU-815  |

| RA78K Series Structured Assembler Preprocess | sor                                                 | EEU-1402     | EEU-817  |

| CC78K Series C Compiler                      | Operation                                           | EEU-1280     | EEU-656  |

|                                              | Language                                            | EEU-1284     | EEU-655  |

| CC 78K0 C Compiler                           | Operation                                           | U11517E      | U11517J  |

|                                              | Language                                            | U11518E      | U11518J  |

| CC78K/0 C Compiler Application Note          | Programming Know-how                                | EEA-1208     | EEA-618  |

| CC78K Series Library Source File             |                                                     | _            | EEU-777  |

| IE-780000-SL                                 |                                                     | Planned      | Planned  |

| IE-78K0-SL-EM                                |                                                     | Planned      | Planned  |

| IE-780924-SL-EM1                             |                                                     | Planned      | Planned  |

| EP-64CW-SL                                   |                                                     | Planned      | Planned  |

| EP-64GC-SL                                   |                                                     | Planned      | Planned  |

| SM78K0 System Simulator Windows-based        | Reference                                           | U10181E      | U10181J  |

| SM78K Series System Simulator                | External parts user open<br>interface specification | U10092E      | U10092J  |

| ID78K0 Integrated Debugger EWS-based         | Reference                                           | U11151E      | U11151J  |

| ID78K0 Integrated Debugger PC-based          | Reference                                           | U11539E      | U11539J  |

| ID78K0 Integrated Debugger Windows-based     | Guide                                               | U11649E      | U11649J  |

Caution The above related documents are subject to change without notice. Be sure to use the latest documents when starting design.

- ---- -- --

Powered by ICminer.com Electronic-Library Service CopyRight 2003

\_\_\_\_\_

## Embedded Software Documents (User's Manuals)

| Document Name                                          |                    | Document No. |          |

|--------------------------------------------------------|--------------------|--------------|----------|

|                                                        | nthame             | English      | Japanese |

| 78K/0 Series Real-Time OS                              | Basics             | _            | U11537J  |

|                                                        | Installation       | -            | U11536J  |

|                                                        | Technical          | -            | U11538J  |

| 78K/0 Series OS MX78K0                                 | Basics             | EEU-1532     | EEU-5010 |

| Fuzzy Knowledge Data Creation Tool                     |                    | EEU-1438     | EEU-829  |

| 78K/0, 78K/II, 87AD Series                             |                    | EEU-1444     | EEU-862  |

| Fuzzy Inference Development Support S                  | System Translator  |              |          |

| 78K/0 Series Fuzzy Inference Development Suport System |                    | EEU-1441     | EEU-858  |

| Fuzzy Inference Module                                 |                    |              |          |

| 78K/0 Series Fuzzy Inference Developm                  | ent Support System | EEU-1458     | EEU-921  |

| Fuzzy Inference Debugger                               |                    |              |          |

#### Other Documents

| Document Name                                               | Docum    | ent No.  |

|-------------------------------------------------------------|----------|----------|

|                                                             | English  | Japanese |

| IC Package Manual                                           | C10943X  |          |

| Semiconductor Device Mounting Technology Manual             | C10535E  | C10535J  |

| Quality Grades on NEC Semiconductor Devices                 | C11531E  | C11531J  |

| NEC Semiconductor Device Reliability/Quality Control System | C10983E  | C10983J  |

| Electrostatic Discharge (ESD) Test                          | IEI-1201 | MEM-539  |

| Guide to Quality Assurance for Semiconductor Devices        | MEI-1202 | MEI-603  |

| Microcomputer Product Series Guide                          | _        | MEI-604  |

Caution The above related documents are subject to change without notice. Be sure to use the latest documents when starting design.

34

6427525 0099433 727 🖿

[MEMO]

## PAGE(S) INTENTIONALLY BLANK

🖬 6427525 0099434 663 **5**

35

Powered by ICminer.com Electronic-Library Service CopyRight 2003

\_\_\_\_

[MEMO]

## PAGE(S) INTENTIONALLY BLANK

🔲 6427525 0099435 STT 페

#### [MEMO]

The following supersedes any statement which may be found elsewhere in this document purporting to address the subjects of quality, reliability or suitability of any devices listed in this document for applications other than as noted.

No part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC Electronics Inc. (NECEL). The information in this document is subject to change without notice. ALL DEVICES SOLD BY NECEL ARE COVERED BY THE PROVISIONS APPEARING IN NECEL TERMS AND CONDITIONS OF SALE ONLY, INCLUDING THE LIMITATION OF LIABILITY, WARRANTY, AND PATENT PROVISIONS. NECEL makes no warranty, express, statutory, implied or by description, regarding information set forth herein or regarding the freedom of the described devices from patent infringement. NECEL assumes no responsibility for any errors that may appear in this document. NECEL makes no commitments to update or to keep current information contained in this document. The devices listed in this document are not suitable for use in applications such as, but not limited to, aircraft control systems, aerospace equipment, submarine cables, nuclear reactor control systems and life support systems. "Standard" quality grade devices are recommended for computers, office equipment, communication equipment, test and measurement equipment, traffic control systems, anti-disaster and anti-systems, it is recommended that the customer contact the responsible NECEL salesperson to determine the reliability requirements is such application and any cost adder. NECEL does not recommend or approve use of any of its products in life support devices or sys, or in any application where failure could result in injury or death. If customers wish to use NECEL devices in applications not intendeo NECEL, customer must contact the responsible NECEL sales people to determine the reliability requirements is or in any application where failure could result is injury or death. If customers wish to use NECEL devices in applications not intendeo

For literature, call toll-free 7 a.m. to 6 p.m. Pacific time: 1-800-366-9782 or FAX your request to: 1-800-729-9288

🛲 6427525 0099436 436 🎟

### -NOTES FOR CMOS DEVICES-

# **① PRECAUTION AGAINST ESD FOR SEMICONDUCTORS**

Note: Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

### ② HANDLING OF UNUSED INPUT PINS FOR CMOS

Note: No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS device behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

# **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note: Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

38

NEC

🖿 6427525 0099437 372 📰

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- Device availability

- Ordering information

- Product release schedule

- Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

NEC Electronics Inc. (U.S.) Mountain View, California Tel: 800-366-9782 Fax: 800-729-9288

NEC Electronics (Germany) GmbH Duesseldorf, Germany Tel: 0211-65 03 02 Fax: 0211-65 03 490

NEC Electronics (UK) Ltd. Milton Keynes, UK

Tel: 01908-691-133 Fax: 01908-670-290

NEC Electronics Italiana s.r.1. Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99 NEC Electronics (Germany) GmbH Benelux Office Eindhoven, The Netherlands Tel: 040-2445845 Fax: 040-2444580

**NEC Electronics (France) S.A.** France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

NEC Electronics (France) S.A. Spain Office Madrid, Spain Tel: 01-504-2787 Fax: 01-504-2860

NEC Electronics (Germany) GmbH Scandinavia Office Taeby Sweden Tel: 8-63 80 820 Fax: 8-63 80 388 NEC Electronics Hong Kong Ltd. Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

NEC Electronics Hong Kong Ltd. Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

NEC Electronics Singapore Pte. Ltd. United Square, Singapore 1130 Tel: 253-8311 Fax: 250-3583

NEC Electronics Taiwan Ltd. Taipei, Taiwan Tel: 02-719-2377 Fax: 02-719-5951

NEC do Brasil S.A.

Sao Paulo-SP, Brasil Tel: 011-889-1680 Fax: 011-889-1689

**J96.** 3

•••• 6427525 0099438 209 **•••**