November 1991

### DESCRIPTION

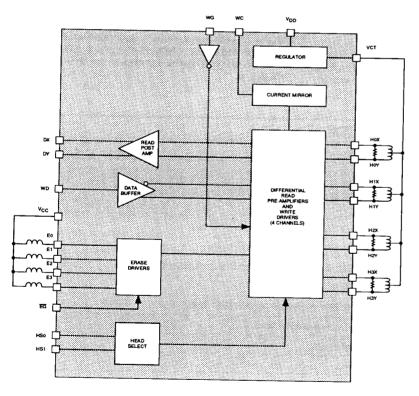

The SSI 34R575 device is a bipolar monolithic integrated circuit used in floppy disk systems for head control and write, erase, and read select functions. The device has either two or four discrete read, write, and erase channels. Channel select inputs are TTL compatible. The SSI 34R575 device requires +5 V and +12 V power supplies and is available in 18-pin (2-channel version) or 24-pin (4-channel version) dual inline packages.

### **FEATURES**

- Operates on +5 V, +12 V power supplies

- Two or four channel capability

- TTL compatible control inputs

- Read/Write functions on one-chip

- Internal center tap voltage source

- Supports all disk sizes

- Applicable to tape systems

## **PIN DIAGRAM**

|                   |    |    | _     |

|-------------------|----|----|-------|

| E2 [              | 1  | 24 | be₁   |

| E3 [              | 2  | 23 | DE⊙   |

| v <sub>DD</sub> [ | 3  | 22 | ∃но×  |

| GND [             | 4  | 21 | ] ноч |

| EG [              | 5  | 20 | ] нтх |

| HS1 [             | 6  | 19 | H1Y   |

| HSO [             | 7  | 18 | ] H2X |

| DY [              | 8  | 17 | ] H2Y |

| Dx [              | 9  | 16 | Нэх   |

| wc □              | 10 | 15 | НЗҮ   |

| vсс Д             | 11 | 14 | VCT   |

| w¤ [              | 12 | 13 | ] wc  |

|                   |    |    |       |

CAUTION: Use handling procedures necessary for a static sensitive component.

1191 - rev.

9-25

### **FUNCTIONAL DESCRIPTION**

The SSI 34R575 functions as a write and erase driver or as a read amplifier for the selected head. Two TTL compatible inputs are decoded to select the desired read/write and erase heads. Head select logic is indicated in Table 1. Both the erase gate  $(\overline{EG})$  and write gate  $(\overline{WG})$  lines have internal pull up resistors to prevent an accidental write or erase condition.

#### MODE SELECTION

The read or write mode is determined by the write gate  $(\overline{WG})$  line. The input is open collector TTL compatible. With the input low, the circuit is in the write mode. With the input high (open), the circuit is in the read mode. In the read mode, or with the +5 V supply off, the circuit will not pass write current.

#### **ERASE**

The erase operation is controlled by an open collector TTL compatible input. With erase gate  $(\overline{EG})$  input high

(open) or the +5 V supply off, the circuit will not pass erase current. With  $\overline{\rm EG}$  low, the selected open collector erase output will be low and current will be pulled through the erase heads.

#### **READ MODE**

With the WG line high, the read mode is enabled. In the read mode the circuit functions as a differential amplifier. The state of the head select input determines which amplifier is active. When the mode or head is switched, the read output will have a voltage level shift. External reactive elements must be allowed to recover before proper reading can commence. A current diverting circuit prevents any possible write current from appearing on a head line.

#### WRITE MODE

With the WG line low, externally generated write current is mirrored to the selected head and is switched between head windings by the state of the write data (WD) signal.

### PIN DESCRIPTION

| NAME               | TYPE | DESCRIPTION                                                   |

|--------------------|------|---------------------------------------------------------------|

| Vcc                |      | +5 V                                                          |

| Vod                |      | +12 V                                                         |

| H0X-H3X<br>H0Y-H3X |      | X, Y head connections                                         |

| DX, DY             |      | X, Y Read Data: Differential read signal out                  |

| WG                 | * ** | Write gate: sets write mode of operation                      |

| wc                 |      | Write current: current mirror used to drive floppy disk heads |

| WD                 |      | Write data line                                               |

| EG                 |      | Erase gate: allows erasure by selected head                   |

| E0-E3              |      | Erase head driver connections                                 |

| HS0-HS1            |      | Head select inputs                                            |

| GND                |      | Ground                                                        |

| VCT                |      | Center Tap Voltage Source                                     |

9-26 1191 - rev.

**TABLE 1: HEAD SELECT LOGIC**

| 4 - CHANNELS |     |      |  |  |

|--------------|-----|------|--|--|

| HS1          | HS0 | HEAD |  |  |

| 0            | 0   | 0    |  |  |

| 0            | 1   | 1    |  |  |

| 1            | 0   | 2    |  |  |

| 1            | 1   | 3    |  |  |

| 2 - CHANNELS |      |  |  |

|--------------|------|--|--|

| HS1          | HEAD |  |  |

| 0            | 0    |  |  |

| 1            | 1    |  |  |

### **ELECTRICAL SPECIFICATIONS**

# **ABSOLUTE MAXIMUM RATINGS**

(Operating above absolute maximum ratings may damage the device.)

| PARAMETER               |                      | RATING                        | UNIT |  |

|-------------------------|----------------------|-------------------------------|------|--|

| DC Supply Voltage:      | Vcc                  | 6.0                           | V    |  |

|                         | Vdd                  | 14.0                          | V    |  |

| Write Current           |                      | 10                            | mA   |  |

| Head Port Voltage       |                      | 18.0                          | V    |  |

| Digital Input Voltages: | DX, DY, HS0, HS1, WD | -0.3 to + 10                  | V    |  |

|                         | EG, WG               | -0.3 to V <sub>cc</sub> + 0.3 | V    |  |

| DX, DY Output Current   |                      | -5                            | mA   |  |

| VCT Output Current      |                      | -10                           | mA   |  |

| Storage Temperature R   | ange                 | -65 to + 150                  | °C   |  |

| Junction Temperature    |                      | 125                           | °C   |  |

| Lead Temperature (Solo  | dering, 10 sec.)     | 260                           | °C   |  |

1191 - rev.

# RECOMMENDED OPERATING CONDITIONS (0°C<Ta<50°C, 4.7 V<Vcc<5.3 V, 11 V<Vdc<13 V)

| PARAMETER          | CONDITIONS | MIN | МОМ     | MAX | UNIT |

|--------------------|------------|-----|---------|-----|------|

| Vcc Supply Current |            |     |         |     |      |

| Read mode          | Vcc MAX    |     |         | 15  | mA   |

| Write mode         | Vcc MAX    |     | <u></u> | 35  | mA   |

| VDD Supply Current |            |     |         |     |      |

| Read mode          | VDD MAX    |     |         | 25  | mA   |

| Write mode         | VDD MAX    |     |         | 15  | mA   |

| Write Current      |            |     | 5.5     |     | mA   |

### **ERASE OUTPUT**

| PARAMETER         | CONDITIONS | MIN | МОМ | MAX | UNIT |

|-------------------|------------|-----|-----|-----|------|

| Erase On Voltage  | IE = 80 mA | 0.7 |     | 1.3 | VDC  |

| Erase Off Leakage |            |     |     | 100 | μΑ   |

### **LOGIC SIGNALS**

| PARAMETER                    | CONDITIONS      | MIN  | ном | MAX  | UNIT |

|------------------------------|-----------------|------|-----|------|------|

| Head Select (HS0, HS1) and W | ite Data (WD)   |      |     |      |      |

| Low Level Voltage            |                 | -0.3 |     | 0.8  | VDC  |

| High Level Voltage           |                 | 2.0  |     | 6.0  | VDC  |

| Low Level Current            | Vin = 0 volts   | -1.6 |     |      | mA   |

| High Level Current           | Vin = 2.7 volts |      |     | 40   | μΑ   |

| WRITE GATE (WG) and ERAS     | E GATE (EG)     |      |     |      |      |

| Low Level Voltage            |                 | -0.3 |     | 0.81 | VDC  |

| High Level Input Current     |                 | -300 |     |      | μА   |

| Low Level Current            | Vin = 0 volts   | -2.0 |     |      | mA   |

9-28 1191 - rev.

### **READ MODE**

| PARAMETER                                | CONDITIONS                                       | MIN | мом | MAX | UNIT   |

|------------------------------------------|--------------------------------------------------|-----|-----|-----|--------|

| Differential Gain                        | $f$ = 100 kHz, Vin = 5 mV Rms RL = 10 k $\Omega$ | 80  | 100 | 120 | V/V    |

| Bandwidth                                | Vin = 5 mVRms<br>RL = 10 K CL = 15pF             | 9   |     |     | MHz    |

| Input Voltage Range for 95%<br>Linearity | f = 100 kHz, RL = 10 K                           | 25  |     |     | m∨pp   |

| Differential Input Resistance            | f = 1 MHz                                        | 100 |     |     | kΩ     |

| Differential Input Capacitance           | f = 1 MHz                                        |     |     | 10  | рF     |

| Input Bias Current                       |                                                  |     |     | 25  | μА     |

| Input Offset Voltage                     |                                                  |     |     | 12  | mV     |

| Output Voltage, Common Mode              |                                                  |     | 8   |     | VDC    |

| Output Resistance                        |                                                  |     |     | 35  | Ω      |

| Output Current Sink                      |                                                  | 2   |     |     | mA     |

| Output Current Source                    |                                                  | 3   |     |     | mA     |

| Common Mode Rejection Ratio              | f = 1 MHz (input referred)                       | 50  |     |     | dB     |

| Power Supply Rejection Ratio             | f = 1 MHz (input referred)                       | 50  |     |     | dB     |

| Channel Separation                       | f = 1 MHz (input referred)                       | 50  |     |     | dB     |

| Input Noise                              | BW = 100 Hz to 1 MHz,<br>Z Source = 0            |     | 7   |     | μV RMS |

### WRITE MODE

| PARAMETER                   | CONDITIONS                  | MIN  | NOM  | MAX  | UNIT |

|-----------------------------|-----------------------------|------|------|------|------|

| Write Current Gain          | IW = 5.5 mA                 | .97  |      | 1.05 | A/A  |

| Write Current Voltage Level | IW = 5.5 mA                 | 1.2  |      | 2.1  | VDC  |

| Differential Head Voltage   | IW = 5.5 mA                 | 12.5 |      |      | VDC  |

| Unselected Head Current     | IW = 5.5 mA<br>DC Condition |      |      | 0.1  | mA   |

| Write Current Unbalance     | IW = 5.5 mA                 |      |      | 1    | %    |

| Write Current Time Symmetry | IW = 5.5 mA                 |      |      | ±10  | ns   |

| Read Amplifier Output Level |                             |      | 10.5 |      | VDC  |

| Center Tap Voltage          | (Read and Write Modes)      |      | 8.5  |      | VDC  |

1191 - rev. 9-29

### **SWITCHING CHARACTERISTICS**

| PARAMETER                               | CONDITIONS                    | MIN | NOM | MAX | UNIT |

|-----------------------------------------|-------------------------------|-----|-----|-----|------|

| Write and Erase<br>Gate Switching Delay | Delay to 90% of Write Current |     |     | 1   | μѕес |

| Head Select Switching Delay             |                               |     |     | 1   | μѕес |

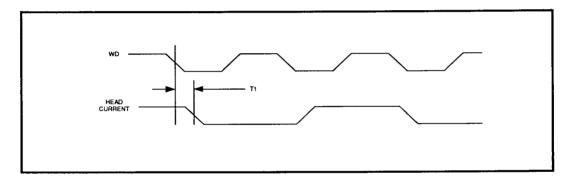

| Head Current Switching Delay            | T1 in Fig. 1                  |     | 10  |     | nsec |

| Head Current Switching Time             | IW = 5.5 mA Shorted Head      |     | 10  | 30  | nsec |

| Write to Read Recovery Time             |                               |     |     | 2   | μѕес |

FIGURE 1: Head Current Switching Delay

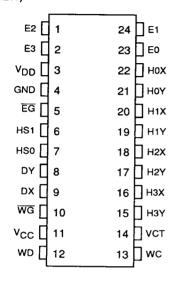

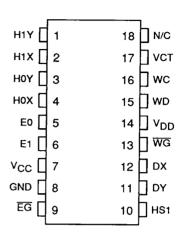

# PACKAGE PIN DESIGNATIONS (TOP VIEW)

24-Pin DIP

18-Pin DIP

### ORDERING INFORMATION

| PART DESCRIPTION      | ORDER NO.  | PKG. MARK  |

|-----------------------|------------|------------|

| SSI 34R575 24-Pin DIP | 34R575-4CP | 34R575-4CP |

| SSI 34R575 18-Pin DIP | 34R575-2CP | 34R575-2CP |

No responsibility is assumed by Silicon Systems for use of this product nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights or trademarks of Silicon Systems. Silicon Systems reserves the right to make changes in specifications at any time without notice. Accordingly, the reader is cautioned to verify that the data sheet is current before placing orders.

Silicon Systems, Inc., 14351 Myford Road, Tustin, CA 92680, (714) 731-7110, FAX: (714) 573-6914

1191 - rev.

@1989 Silicon Systems, Inc.