# **Preliminary Data**

July 1992

#### DESCRIPTION

The F687 is a high performance MSIC® (Mixed Signal Integrated Circuit) designed to work with a microprocessor in an engine management system. Using two sensor inputs (crank and cam), the F687 tracks engine position through one or two complete revolutions with a resolution of 0.25 degrees. Designed to be flexible, the F687 will accept a variety of sensor types and pulse patterns. It generates ignition and injection output pulses based on position and time parameters supplied by the host microprocessor, relieving it of many of the real time interrupt routines associated with these tasks. These outputs can directly drive power devices to actuate automotive ignition coils and fuel injectors. A sense input from each output device allows individual diagnostics, short circuit protection and ignition coil current limit. A timer, which measures coil charge time at the ignition sense inputs, enhances closed loop dwell control. Communication with a host microprocessor is through a parallel data and address bus. A general purpose parallel I/O port offers level sensitive input and output capability, in addition to edge detect inputs and PWM outputs.

#### **FEATURES**

- Engine control applications

- 2 or 4 cycle engines

- Parallel microprocessor bus for control

- Configurable for a variety of sensor patterns

- Variable Reluctance or Hall Effect sensor inputs

- Engine position angle counter

- 4 Ignition outputs (8 Individual spark advance values)

- 8 injection outputs

- Dwell timer

- Ignition coil current limit (for use with external power transistors)

- Injector driver short circuit protection

- Diagnostics

- 8 programmable I/O lines

- PMW outputs

- Edge detect inputs

- On chip oscillator with buffered 8 MHz/31.25 KHz output

- +5V operation

- CMOS technology for low power consumption

- Operating temperature range -40 to +125°C

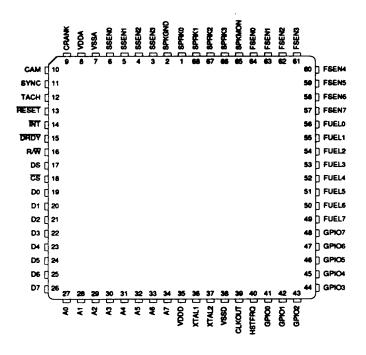

- 68-pin PLCC

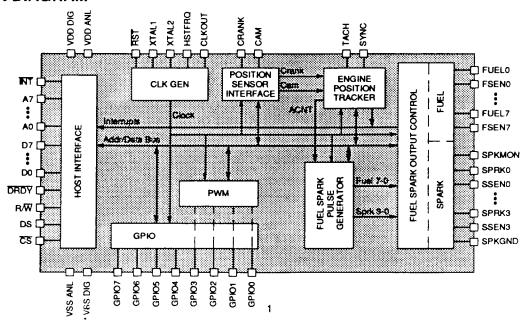

#### **BLOCK DIAGRAM**

0792 - rev.

#### **FUNCTIONAL DESCRIPTION**

The 67F687 Engine Interface Peripheral (EIP), is designed to track engine position from crank and cam sensor inputs and generate output pulses for up to eight fuel injectors and eight ignition spark plugs (multiplexed to four output pins). It is intended to be used with a host microprocessor which defines the engine configuration and calculates the position and time dependent parameters needed to generate fuel and spark pulses. The EIP acts as a memory at the host interface and outputs a single interrupt to the host.

The EIP is divided into modular blocks. There are two analog blocks (PSI and FSOC) and six digital blocks (CLKGEN, EPT, FSPG, PWM, GPIO and HOSTINT). The analog blocks provide the digital blocks with an interface to the engine sensors and ignition/injector drivers. The digital blocks perform engine position tracking, output pulse generation, pulse width modulation, general purpose I/O, clock generation and the host interface.

The Position Sensor Interface (PSI) converts crank and cam sensor inputs to digital signals for use by the EPT. Programmable registers control the input threshold levels, hysteresis amount and allows the use of time (frequency) dependent hysteresis. This allows the PSI to be tailored to the particular type of sensor being used, whether variable reluctance or Hall effect type.

The Engine Position Tracker (EPT) can be configured through internal RAM to track a large number of crank and cam sensor configurations. Once the EPT has attained synchronization with the engine, it maintains a monotonic angle count with a resolution of 0.25 degrees. The angle count and tracking status are available to the host through memory mapped registers. The EPT generates interrupts to the host when it attains or loses synchronization. Digital TACH and SYNC outputs also provide engine speed and position clocks.

The Fuel Spark Pulse Generator (FSPG) generates digital pulses that control fuel and ignition. The host controls the mode used to generate these pulses. In the normal mode, spark is controlled by writing the angle at which charging of the coil is to begin and the angle at which the spark is to occur. Fuel is controlled by writing the angle at which the fuel injector is to turn on and the

time duration of the fuel pulse. In direct mode, the host can generate the output pulses through writes to memory mapped registers. The host can also execute a hard shutdown of all pulses by writing to a control register.

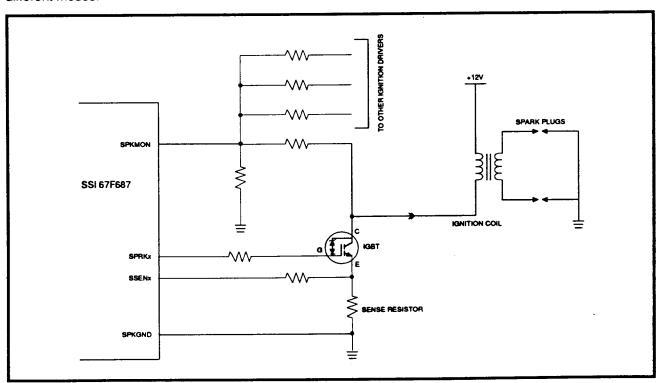

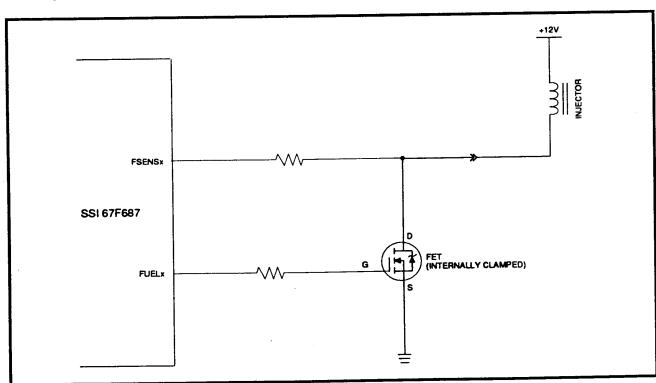

The Fuel Spark Output Controller (FSOC) converts the digital pulses generated by the FSPG into analog outputs. It performs a current limit function for external ignition drivers and contains an ignition dwell timer. The FSOC can also be configured to end a spark pulse when the coil current reaches a predetermined threshold. It monitors the external injector drivers for faults and can turn off pulses to protect these drivers. The FSOC also performs diagnostic tests on both fuel and spark outputs and generates interrupts to the host when a fault condition is indicated.

The General Purpose I/O (GPIO) provides eight user configurable I/O pins. As inputs, four are configurable as either level or edge sensitive and four are level sensitive only. As outputs, four are configurable as pulse width modulated or direct write outputs and four are direct write outputs only.

The Pulse Width Modulator (PWM) provides four pulse width modulated outputs for the GPIO. The outputs are grouped in two pairs. Each pair shares a common output frequency with individual duty cycle control. There are eight programmable output frequencies from 20 Hz to 651 Hz.

The Host Interface (HOSTINT) acts as a buffer between the asynchronous external memory bus and the internal bus. It also provides the interrupt output, interrupt register and interrupt control.

The Clock Generator (CLKGEN) contains the crystal oscillator circuit. It supplies all the necessary internal clocks as well as an external clock at the CLKOUT pin.

#### INTERNAL REGISTERS AND RAM

The 67F687 uses both static RAM and registers to store data. Memory on the EIP falls into one of two categories:

(1) memory that must be accessable during normal operation and (2) EPT configuration memory that is loaded only once during power up.

To allow more than 256 memory locations using eight address pins, memory is divided into two pages. Memory locations 00 through BF HEX can be mapped to two different locations depending on the value of bit 0 in the

Global Configuration Register (GCR) - location F6 HEX. This allows a maximum of 448 locations. When GCR bit 0=0, the memory necessary for normal operation (FSPG RAM) is accessed. When GCR bit 0=1, the EPT configuration memory is accessed. These registers configure the F687 for the particular engine and sensors, and must be initialized by the host microprocessor before engine position tracking can begin. In normal operation, the EPT configuration registers are only written to once on power up, and should not be modified after initialization without first disabling the outputs.

Whenever GCR bit 0 = 1, the EPT is inhibited from attaining sync and will be forced out of sync if it attained it previously.

To differentiate the two pages of memory, addresses of locations on page 1 described in this document will be preceded by a "1" (1xx for page 1 locations and xx for page 0 locations).

Memory locations C0 through FF HEX access only one set of registers and are unaffected by the value of GCR bit 0. During reset GCR bit 0 is set to "1".

#### RESET

An external logic level low at the RST pin places the 67F687 in a defined initial state. All registers are set to known values. RAM values are unknown and should not be used until initialized. All output pulses are turned off. All GPIO pins are configured as level sensitive inputs. The PWM is configured to output no pulses. All interrupts are off and masked. The memory page bit of the GCR (location F6) is set to "1".

After reset the 67F687 internal RAM and registers cannot be accessed for 2  $\mu s$  (sixteen 8 MHz clock pulses).

#### **CLOCK GENERATOR (CLKGEN)**

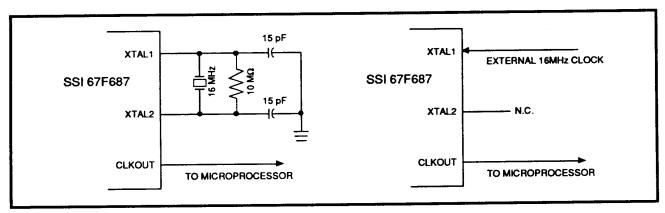

The CLKGEN uses a 16 MHz crystal at the XTAL1 and XTAL2 pins to generate the required internal clocks for the F687. Alternatively, XTAL1 can be driven by an external 16 MHz clock. If this is done XTAL2 should be left open. The CLKOUT pin provides a buffered output clock whose frequency depends upon the logic level at the HSTFRQ pin. If HSTFRQ=0, CLKOUT is 8 MHz; if HSTFRQ=1, CLKOUT is 31.25 KHz.

A reset will inhibit the internal clocks, but has no effect on the external clock at the CLKOUT pin. Figure 4 shows some typical external circuits for the Clock Generator.

#### HOST MICROPROCESSOR INTERFACE (HOSTINT)

The HOSTINT makes the 67F687 look like external memory to a host microprocessor. It supports non-multiplexed address and data buses. Both address and data are eight bits wide. Chip select bar  $(\overline{CS})$ , data strobe (DS) and read/write bar  $(R/\overline{W})$  inputs are used to control the bus interface.

The DS pin can either be data strobe (DS) or data strobe bar  $(\overline{DS})$  dependent on the logic level at the HSTFRQ pin. If HSTFRQ=0, DS is inverted internally. For the remainder of this description it is assumed that HSTFRQ=1. If HSTFRQ=0 replace "DS=0" with "DS=1" and vice-versa and replace "rising edge of DS" with "falling edge of DS" and vice-versa.

A data ready bar (DRDY) output is available for use with hosts that can support extended bus cycles. A single interrupt bar (INT) pin is also provided to the host.Both of these are open drain outputs.

The data bus pins (D0-D7) are outputs when R/W=1 AND DS=0 AND CS=0. They are inputs otherwise.

During a read cycle, the output data will be valid 500 nsec after DS=0. When DS=0 for less than this time and the host cannot use  $\overline{DRDY}$  to extend its memory cycle, the host must execute multiple read cycles to interface with the EIP. For this condition, a host must read a location once to start the EIP internal read cycle. The same location must then be read a second time. There must be at least 500 nsec between the falling edge of DS during the first read and the rising edge of DS during the second read to get valid data. There can be no other reads or writes to the F687 between the double read.

If the host can use  $\overline{DRDY}$ , the R/W input must be valid for the entire duration of  $\overline{CS}$ =0. For a read,  $\overline{DRDY}$ =0 as soon as the data is valid and remains low until DS=1.

During a write cycle, the address inputs are latched by the falling edge of  $\overline{CS}$  and DS. External data is latched by the rising edge of DS. Writes can occur no less than 500 nsec apart. For a write,  $\overline{DRDY}$  goes low as soon as  $\overline{CS}$ =0 and and stays low until the rising edge of DS.

#### PIN DESCRIPTION

#### **GENERAL**

| NAME  | TYPE | DESCRIPTION                                                                                |

|-------|------|--------------------------------------------------------------------------------------------|

| VddD  | PWR  | +5V Power supply for digital circuits.                                                     |

| VddA  | PWR  | +5V Power supply for analog circuits.                                                      |

| VssD  | PWR  | GROUND reference for digital circuits.                                                     |

| VssA  | PWR  | GROUND reference for analog circuits.                                                      |

| RESET | ı    | RESET. Active low input turns off all outputs and initializes the 67F687 to a known state. |

#### **CLOCK GENERATOR**

| XTAL1, XTAL2 | I | These pins are for the external 16 MHz crystal to generate the internal 8 MHz clock. An external clock (16 MHz) can also be input at XTAL1 with XTAL2 open. |

|--------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKOUT       | 0 | Buffered clock signal to microprocessor. Either 8 MHz or 31.25 KHz depending on state of HSTFRQ input.                                                      |

| HSTFRQ       | 1 | Level at this pin determines the clock frequency at CLKOUT and the sense of DS.                                                                             |

#### **HOST INTERFACE**

| A0:7 | i   | HOST ADDRESS LINES. These are used to address the internal registers of the 67F687.                                                                       |

|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS   | Į.  | CHIP SELECT. Active low signal, allows the internal registers of the 67F687 to be accessed.                                                               |

| D0:7 | 1/0 | HOST DATA LINES. These are used to read and write to the 67F687 internal RAM and registers.                                                               |

| DS   | 1   | DATA STROBE. Active low or high depending on state of HSTFRQ input. Indicates valid data on D0:7.                                                         |

| R/W  | ı   | READ/WRITE. Determines direction of data flow on D0:7.                                                                                                    |

| DRDY | 0   | DATA READY. Active low signal used with certain microprocessors that support extended bus cycles to indicate that data requested is available to be read. |

| INT  | 0   | INTERRUPT. Active low output, indicates interrupt request to microprocessor.                                                                              |

#### **PSI**

| NAME  | TYPE | DESCRIPTION                                                                                                                 |

|-------|------|-----------------------------------------------------------------------------------------------------------------------------|

| CRANK | ı    | Crankshaft sensor input.                                                                                                    |

| CAM   | ı    | Camshaft sensor input.                                                                                                      |

| TACH  | 0    | Output at this pin is either TACH or the conditioned CRANK sensor signal, depending on the contents of the EPTRST register. |

| SYNC  | 0    | Output at this pin is either SYNC or the conditioned CAM sensor signal, depending on the contents of the EPTRST register.   |

#### **FSOC**

| SPRK0:4 | 0 | Spark outputs to ignition coil drivers.                                                                                                                                         |

|---------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSEN0:4 | I | Spark sense inputs used to detect current through ignition coil by measuring voltage across current sense resistor. Used for current limit, autofire and dwell timer threshold. |

| SPKGND  | l | Ground reference for SSEN0:4. Should be connected directly to low side of current sense resistors.                                                                              |

| SPKMON  | 1 | Input pin to detect voltage spike generated when ignition coil is turned off (for diagnostics).                                                                                 |

| FUEL0:7 | 0 | Fuel outputs to fuel injector drivers.                                                                                                                                          |

| FSEN0:7 | ı | Fuel sense inputs from injector driver, used for short circuit protection and diagnostics on FUEL outputs.                                                                      |

#### **GPIO**

|         | · · · |                                                                           |

|---------|-------|---------------------------------------------------------------------------|

| GPIO0:7 | 1/0   | General purpose input or output pins. Four pins can also be configured as |

|         |       | PWM outputs and the other four can be edge detect inputs.                 |

#### **ELECTRICAL SPECIFICATIONS**

#### **ABSOLUTE MAXIMUM RATINGS**

Operation beyond absolute maximum ratings may permanently damage the device. All voltages are referenced to logic ground unless otherwise specified. Current flowing into the integrated circuit is positive.

| PARAMETER             |               | CONDITIONS                                                 | MIN  | NOM | MAX       | UNIT |

|-----------------------|---------------|------------------------------------------------------------|------|-----|-----------|------|

| Supply Voltage        | -digital VddD | Referenced to VssD                                         | -0.5 |     | 7.0       | V    |

| ,                     | -analog VddA  | Referenced to VssA                                         | -0.5 |     | 7.0       | V    |

| Input Current         | lin           | All I/O Pins                                               | -10  |     | +10       | mA   |

| Input Voltage         | Vin           | All Inputs, referenced to VssD or VssA except FSEN, SPKMON | 05   |     | Vdd = +.5 | ٧    |

| Operating Temporating | erature To    | Ambient                                                    | -40  |     | +125      | °C   |

| Storage Tempera       |               | Ambient                                                    | -55  |     | +150      | ô    |

#### **RECOMMENDED OPERATING CONDITIONS**

Unless otherwise specified, VddD = VddA = 5.0V, T(ambient) = 25 °C.

#### **POWER SUPPLY**

| Supply Voltage -digital VddD         | Referenced to VssD | 4.5 | 5.0  | 5.5  | V   |

|--------------------------------------|--------------------|-----|------|------|-----|

| -analog VddA                         | Referenced to VssA | 4.5 | 5.0  | 5.5  | V   |

| Delta Supply Voltage                 | VddD - VddA        | 3   | 0.0  | .3   | V   |

| Supply Current Idd                   |                    |     | 18.0 | 25.0 | mA  |

| Clock Frequency                      |                    |     | 16.0 |      | MHz |

| Bypass Capacitor Both power supplies |                    |     | 0.1  |      | μF  |

## HOST INTERFACE - INPUTS (DS, CS, R/W, A(7:0), RESET, D(7:0))

| Input Voltage Range | Vin |                    | -0.5   |    | Vdd    | V  |

|---------------------|-----|--------------------|--------|----|--------|----|

| Input Current       | lin | 0V < Vin < Vdd     |        | 25 | 100    | μΑ |

| Input Low Voltage   | Vil | Referenced to VddD | 0      |    | .2xVdd |    |

| Input High Voltage  | Vih | Referenced to VddD | .7xVdd |    | Vdd    | V  |

## **HOST INTERFACE - OUTPUTS** (D(7:0))

| PARAMETER             |     | CONDITIONS  | MIN  | NOM | MAX | UNIT |

|-----------------------|-----|-------------|------|-----|-----|------|

| Output Voltage - High | Voh | lo = -2.0mA | Vdd4 |     |     | ٧    |

| Output Voltage - Low  | Vol | lo = +2.0mA |      |     | 0.4 | ٧    |

## CLOCK FREQUENCY - OUTPUTS (CLKOUT, SYNC, TACH)

| 1 | Clkout Frequency - 1 | Fo1 | HSTFRQ(Pin 26) = Vdd | 31.25 | kHz |

|---|----------------------|-----|----------------------|-------|-----|

|   | Clkout Frequency - 2 | Fo2 | HSTFRQ(Pin 26) = 0   | 8.0   | MHz |

## CONTROL TIMING - CLOCK/RESET (XTAL1, XTAL2, HSTFRQ, RESET)

| Frequency of Operation             | Fosc | Clock at Pin 26                    | 16.0 |    | MHz |

|------------------------------------|------|------------------------------------|------|----|-----|

| External Clock Option              | Fc   | Crystal oscillator at Xtal1, Xtal2 | 16.0 |    | MHz |

| Crystal Oscillator<br>Startup Time | Tst  |                                    |      | 10 | ms  |

## GENERAL PURPOSE I/O (GPIO(7:0), DRDY, INT)

| Input Low Voltage                   | Vil  | Referenced to VddD                                 | 0      | .2xVdd | ٧  |

|-------------------------------------|------|----------------------------------------------------|--------|--------|----|

| Input High Voltage                  | Vih  | Referenced to VddD                                 | .7xVdd | Vdd    | ٧  |

| PWM output frequency                | Fpwm | Programmable                                       | 20     | 651    | Hz |

| Output voltage - low DRDY, INT pins | Vol  | Referenced to VddD Open Drain Outputs Io = +2.0 mA | 0      | .1xVdd | ٧  |

#### **ELECTRICAL SPECIFICATIONS** (continued)

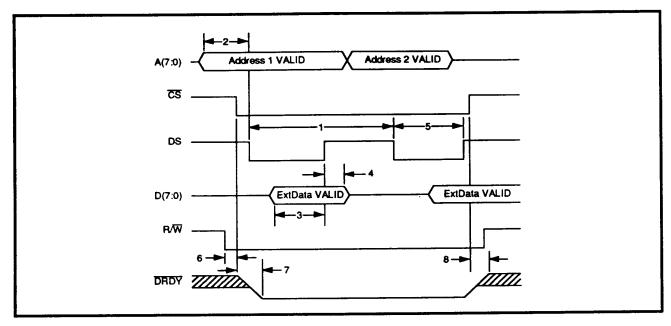

FIGURE 1: Write Cycle

## CONTROL TIMING - WRITE ( $\overline{CS}$ , DS, A(7:0), D(7:0), R/ $\overline{W}$ ), (HSTFRQ = 1)

| (1) Data Strobe Period | Tdsb | Between falling edges                 | 500 |    | ns |

|------------------------|------|---------------------------------------|-----|----|----|

| (2) Address setup time | Tas  | Before $\overline{CS} = 0$ AND DS = 0 | 5   |    | ns |

| (3) Data valid setup   | Tdvs | DATA valid to DS = 1 OR CS = 1        | 10  |    | ns |

| (4) DATA hold time     | Tdh  | From CS or DS = 1                     | 5   |    | ns |

| (5) DS pulse width     | Tdsp | Minimum width                         | 200 |    | ns |

| (6) R/W setup time     | Trds | Before CS falling edge                | 5   |    | ns |

| (7) DRDY active time   | Twra | From CS falling edge                  |     | 10 | ns |

| (8) DRDY inactive      | Tri  | From CS rising edge                   |     | 10 | ns |

If HSTFRQ = 0, DS is inverted.

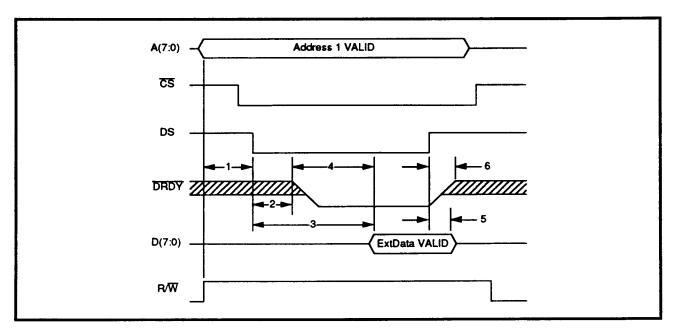

FIGURE 2: Read Cycle Applying DRDY Output

CONTROL TIMING - READ W/ $\overline{DRDY}$  (CS, DS, A(7:0), D(7:0), R/ $\overline{W}$ ,  $\overline{DRDY}$ ), (HSTFRQ = 1)

| PARAMETER              |      | CONDITIONS                                                                   | MIN | NOM | MAX | UNIT |

|------------------------|------|------------------------------------------------------------------------------|-----|-----|-----|------|

| (1) Address setup time | Tas  | Before DS = 0                                                                | 5   |     |     | ns   |

| (2) DRDY active delay  | Trra | DS = 0 and $\overline{\text{CS}}$ = 0 to time $\overline{\text{DRDY}}$ valid | 320 |     | 445 | ns   |

| (3) DATA valid delay   | Tvd  | DS = 0 and <del>CS</del> = 0 to time DATA valid                              | 320 |     | 450 | ns   |

| (4) DRDYb to DATA      | Tde  |                                                                              |     |     | 5   | ns   |

| (5) DATA inactive      | Trdi | From DS = 1                                                                  |     |     | 5   | ns   |

| (6) DRDY inactive      | Tri  | From DS = 1                                                                  |     |     | 5   | ns   |

If HSTFRQ = 0, DS is inverted.

### **ELECTRICAL SPECIFICATIONS** (continued)

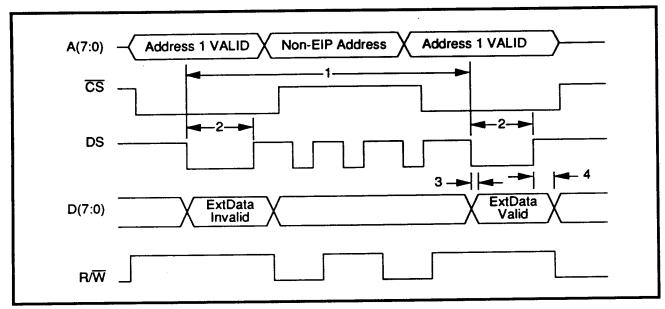

FIGURE 3: Multiple Reads

## CONTROL TIMING - MULTIPLE READS (CS. DS. A(7:0), D(7:0)), (HSTFRQ = 1)

| (1) DS Period                     | Tds  | Between falling edges               | 500 |   | ns |

|-----------------------------------|------|-------------------------------------|-----|---|----|

| (2) DS pulse width -multiple read | Tdsp | From DS falling edge to rising edge | 200 |   | ns |

| (3) DATA active time              | Tda  | From DS falling edge                | 5   |   | ns |

| (4) DATA inactive                 | Tdi  | From DS rising edge                 |     | 5 | ns |

If HSTFRQ = 0, DS is inverted.

#### **INPUTS - CRANK AND CAM**

| DC Voltage Range VinDC            | Steady state range                | -0.5   |         | Vdd+.3 | ٧  |

|-----------------------------------|-----------------------------------|--------|---------|--------|----|

| Input Voltage Range VinAC         |                                   | -1     |         | Vdd+1  | ٧  |

| Input Current lin                 | Gnd < Vin < Vdd                   |        | 25      | 100    | μА |

| Time Decreasing:                  |                                   |        |         |        |    |

| Input Threshold -low rising Vtlr  | Ctrl bit $6 = 1$ bits $2,1,0 = 0$ |        | 0.15    |        | V  |

| Input Threshold -high rising Vthr | Ctrl bit $6 = 1$ bits $2,1,0 = 0$ |        | 2.65    |        | V  |

| Input Threshold -low rising VtIr  | Ctrl bit $6 = 1$ bits $2,1,0 = 1$ |        | 0.25    |        | ٧  |

| Input Threshold -high rising Vthr | Ctrl bit 6 = 1 bits 2,1,0 = 1     | .7xVdd | .75xVdd |        | ٧  |

| Input Threshold falling Vtf       | Ctrl bit 6 = 1                    |        | 0.0     |        | V  |

| PARAMETER                                      |      | CONDITIONS     | MIN      | NOM | MAX           | UNIT                              |

|------------------------------------------------|------|----------------|----------|-----|---------------|-----------------------------------|

| Threshold decay time<br>Programmable value     | Vtd  | Ctrl bit 6 = 1 | 1.024    |     | 8.192         | ms                                |

| Constant value:                                |      |                |          |     |               | • · <del>-</del> · · <del>-</del> |

| Input Threshold -rising<br>Programmable value  | Vptr | Ctrl bit 6 = 0 | .125xVdd |     | Vdd           | ٧                                 |

| Input Threshold -falling<br>Programmable value | Vptf | Ctrl bit 6 = 0 | 0.0      |     | .875 x<br>Vdd | ٧                                 |

# FUEL OUTPUTS/SENSE (FUEL(7:0), FSEN(7:0))

| Input Threshold - High | Vfh | Vdd = 5.0V     |      | 3.33 | 3.5 | V |

|------------------------|-----|----------------|------|------|-----|---|

| Input Threshold - Low  | VfI | Vdd = 5.0V     | 1.5  | 1.66 |     | V |

| Output Voltage - High  |     | lload < 200 μA | Vdd5 |      |     | V |

| Output Voltage - Low   |     | lload < 100 μA |      |      | 0.5 | V |

## SPARK OUTPUT/SENSE (SPRK(3:0), SSEN(3:0), SPKMON, SPKGND)

| Dwell current Threshold  | Vdw | Vdd=5.0V           | 270   | 300 | 330  | m∨     |

|--------------------------|-----|--------------------|-------|-----|------|--------|

| Current limit Threshold  | VcI | Vdd=5.0V           | 320   | 350 | 380  | mV     |

| Autofire Threshold       | Vaf | Vdd=5.0V           | 460   | 500 | 540  | mV_    |

| SPKGND Current           | Isg | Current out of Pin |       | 270 | 400  | μА     |

| SPKMON Threshold         |     | Vdd=5.0V           |       | 3.4 |      | V      |

| Power Supply sensitivity |     | All Thresholds     |       | 20  |      | %/V    |

| Temperature sensitivity  |     | All Thresholds     | -200  |     | +200 | ppm/°C |

| Output Voltage - High    |     | Iload = 2.0 mA     | Vdd-1 |     |      | V      |

| Output Voltage - Low     |     | lload < 100 μA     |       |     | 0.5  | V      |

#### REGISTER DESCRIPTION

#### **POSITION SENSOR INTERFACE (PSI)**

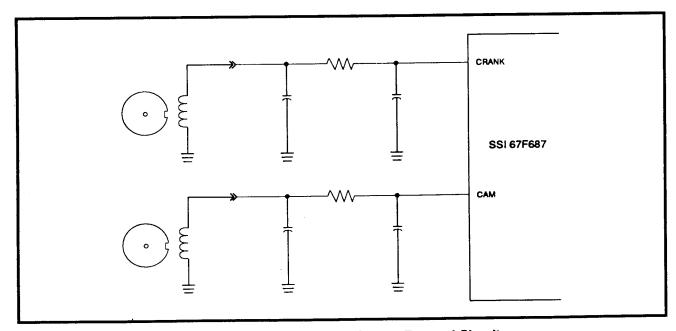

The Position Sensor Interface (PSI) accepts 2 sensor inputs which are used to determine the operating position of an engine. One can indicate crankshaft angle position, and the other camshaft position. These sensors can typically be either Variable Reluctance (VR) or Hall Effect type. Figure 5 shows a typical VR sensor external input circuit. These are conditioned in the 67F687 to provide clean digital pulses to the Engine Position Tracker (EPT).

The circuits for crank and cam sensor conditioning are identical comparators with variable positive and negative switch points. They can be individually configured to optimize the signal processing for the particular type of sensor. The switch points can either be fixed levels (for Hall Effect sensors) or time decreasing (for VR sensors). They are controlled by configuration registers CRKCFG (crank) and CAMCFG (cam)at locations 16C and 16D HEX, respectively. These registers can only be read or written when bit 0 of the GCR (location F6) is a "1". Under normal operation, they would only be configured at power up, along with the EPT registers. The two registers have the same format, shown below.

FIGURE 4: Typical Clock Generator Circuits

FIGURE 5: Typical EIP VR Sensor External Circuit

#### **CRKCFG AND CAMCFG FORMAT**

#### **CRKCFG**

Location 16C

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0 |

|-------|-------|-------|-------|-------|-------|--------|-------|

| INV   | DEC   |       | VTLOW |       |       | VTHIGH |       |

#### **CAMCFG**

Location 16D

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0 |

|-------|-------|-------|-------|-------|-------|--------|-------|

| INV   | DEC   |       | VTLOW |       |       | VTHIGH |       |

| D2.7    | INV: Inverts the output of the PSI before it is input to the EPT. 0 = NOT INVERTED, 1 = INVERTED                                                        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 7   | INV: Invens the output of the PSI before it is input to the EP1. 0 = NOT INVENTED, 1 = INVENTED                                                         |

| Bit 6   | DEC: Determines whether the positive switch point is fixed or time decreasing. 0 = FIXED SWITCH POINTS, 1 = TIME DECREASING                             |

| Bit 5-3 | VTLOW: If DEC (bit 6) = 1, this controls the time dependency of the positive switch point. If DEC (bit 6) = 0, this controls the negative switch point. |

| Bit 2-0 | VTHIGH: Controls the level of the positive switch point.                                                                                                |

If INV = 0, the PSI signal path is non-inverting from the sensor inputs to the PSI output (EPT input). The EPT acts on rising edges. If INV = 1, the sensor signal will be inverted in the PSI. A falling edge at the sensor inputs will generate a rising edge at the EPT input.

The DEC bit selects either fixed or time decreasing switch points. If fixed switch points are selected (DEC = 0), the remaining bits (VTLOW and VTHIGH) set the negative and positive switch points as shown below.

| For DEC = 0 | _     | VTLOW |       | Negative Switch Point |

|-------------|-------|-------|-------|-----------------------|

|             | Bit 5 | Bit 4 | Bit 3 |                       |

|             | 0     | 0     | 0     | 0 volts               |

|             | 0     | 0     | 1     | 1/8 Vdd               |

|             | 0     | 1     | 0     | 1/4 Vdd               |

|             | 0     | 1     | 1     | 3/8 Vdd               |

|             | 1     | 0     | 0     | 1/2 Vdd               |

|             | 1     | 0     | 1     | 5/8 Vdd               |

|             | 1     | 1     | 0     | 3/4 Vdd               |

|             | 1     | 1     | 1     | 7/8 Vdd               |

#### REGISTER DESCRIPTION (continued)

CRKCFG AND CAMCFG FORMAT (continued)

| For DEC = 0 |       | VTHIGH |       | Positive Switch Point |

|-------------|-------|--------|-------|-----------------------|

|             | Bit 2 | Bit 1  | Bit 0 |                       |

|             | 0     | 0      | 0     | 1/8 Vdd               |

|             | 0     | 0      | 1     | 1/4 Vdd               |

|             | 0     | 1      | 0     | 3/8 Vdd               |

|             | 0     | 1      | 1     | 1/2 Vdd               |

|             | 1     | 0      | 0     | 5/8 Vdd               |

|             | 1     | 0      | 1     | 3/4 Vdd               |

|             | 1     | 1      | 0     | 7/8 Vdd               |

|             | 1     | 1      | 1     | Vdd                   |

NOTE: To insure proper operation, the positive switch point must be at least 1/8 Vdd above the negative switch point.

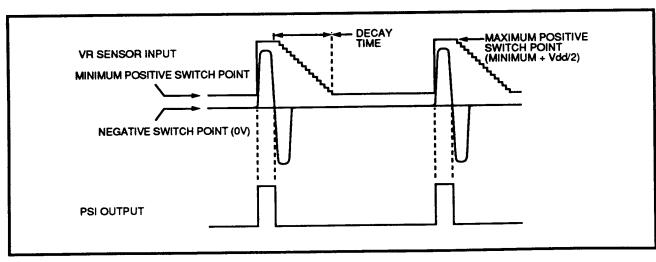

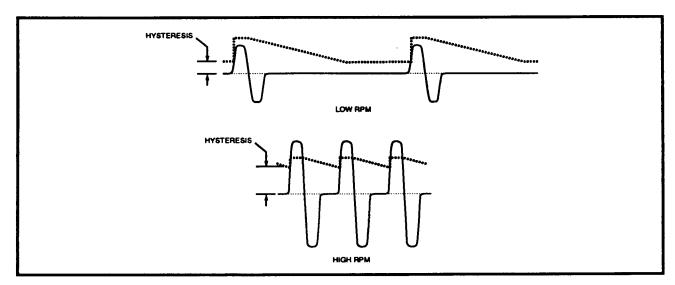

If time decreasing hysteresis is selected (DEC = 1), the positive switch point is a function of time. The negative switch point is always set to 0 volts. Initially, the positive threshold is set to its maximum value. After a high to low transition on the sensor input (falling edge passing through 0 volts), the positive threshold decays linearly in 16 steps to its minimum value. After a low to high transition (rising edge passes through positive threshold), the positive threshold is again set to its maximum and held there until a high to low transition. Figure 6 shows the time decreasing threshold with a sensor input and PSI digital output. Figure 7 shows how this can be used to increase noise immunity at higher speeds.

The maximum positive threshold is always set to 1/2 Vdd above the minimum. The VTLOW and VTHIGH bits are used to select the minimum switch point and the decay rate from maximum to minimum positive switch point.

FIGURE 6: EIP VR Sensor Input, Threshold Levels and PSI Output

FIGURE 7: EIP Time Decreasing Hysteresis

| For DEC = 1 |       | VTLOW  |       | Decay Time (Maximum to minimum threshold) |

|-------------|-------|--------|-------|-------------------------------------------|

|             | Bit 5 | Bit 4  | Bit 3 |                                           |

|             | 0     | 0      | 0     | 8.192 msec                                |

|             | 0     | 0      | 1     | 1.024                                     |

|             | 0     | 1      | 0     | 2.048                                     |

|             | 0     | 1      | 1     | 3.072                                     |

|             | 1     | 0      | 0     | 4.096                                     |

|             | 1     | 0      | 1     | 5.120                                     |

|             | 1     | 1      | 0     | 6.114                                     |

|             | 1     | 1      | 1     | 7.168                                     |

| For DEC = 1 |       | VTHIGH |       | Minimum Positive Switch Point             |

|             | Bit 2 | Bit 1  | Bit 0 |                                           |

|             | 0     | 0      | 0     | 1/32 Vdd                                  |

|             | 0     | 0      | 1     | 1/16 Vdd                                  |

| ]           | 0     | 1      | 0     | 3/32 Vdd                                  |

|             | 0     | 1      | 1     | 1/8 Vdd                                   |

|             | 1     | 0      | 0     | 5/32 Vdd                                  |

| ]           | 1     | 0      | 1     | 3/16 Vdd                                  |

| ;           | 1     | 1      | 0     | 7/32 Vdd                                  |

|             | 1     | 1      | 1     | 1/4 Vdd                                   |

#### REGISTER DESCRIPTION (continued)

#### **ENGINE POSITION TRACKER (EPT)**

The Engine Position Tracker (EPT) is the heart of the 67F687. It uses the conditioned crank and cam sensor signals from the PSI in conjunction with data stored in the EPT configuration RAM to determine engine angular position. This position is stored in the Angle Counter, a monotonic counter which tracks engine position with 0.25 degree resolution and is used to control the spark. fuel, tach and sync outputs.

#### **EPT Page 0 Registers**

Most of the memory used by the EPT is on page 1 because it will not be accessed by the host after initialization. The locations which the host needs to access during normal operation are located on page 0. These contain the angle count, interrupt status, reset, TACH and SYNC setup and test registers (used for factory testing).

NOTE: Accessing page 1 (setting GCR bit 0 = 1) inhibits the EPT from attaining sync, and will cause it to exit the sync mode if it had previously attained sync.

#### **Angle Counter (ACNT)**

The angle counter (ACNT) is a 12 bit representation of engine angular position stored in two 8 bit registers. The upper four bits (ac15-ac12) have no meaning and always return a 0 when read. The lower 11 bits (ac10ac0) represent 0 to 359.75 degrees of engine rotation in 0.25 degree increments. It counts from 0 to 59F HEX (359.75 X 4) and then rolls over to 0 again. The MSB (ac11) is toggled every time this counter rolls over and is used to specify which half of a 720 degree cycle the engine is on (a four cycle engine requires 720 degrees to specify a unique position).

#### **ACNT**

| 0000 | ac11 | ac10 | ac9 | ac8 | ac7 | ac6     | ac5    | ac4 | ac3 | ac2 | ac1 | ac0 |

|------|------|------|-----|-----|-----|---------|--------|-----|-----|-----|-----|-----|

|      | MSB  |      |     |     | ENC | SINE PC | SITION |     |     |     |     |     |

MSB (ac11): 0 = first half of cycle (0 to 359.75 deg.)

1 = second half of cycle (360 to 719.75 deg.)

ENGINE POSITION: Engines degrees X 4 (in 0.25 degree increments) 0 to 359.75 degrees (0 to 59F)

(ac10 - ac2): degrees in integer units

(ac1 - ac0): fraction of a degree

00 = 0

01 = .25

10 = .50

11 = .75

The EPT uses the crank input to determine engine position and engine speed to generate an interpolated count every 0.25 degrees. The interpolated count is corrected to the true count at each crank pulse input.

The angle counter (ACNT) is updated at a maximum rate of once every 2 µs. If the engine is in the steady state condition (no angular acceleration), the angle count is accurate to 0.25 degrees. Under positive or negative acceleration, the angle count interpolation between teeth will not exactly match true engine position. This error is dependent on the magnitude of the acceleration and the spacing between crank pulses (more pulses allow more frequent correction). The angle count is corrected at each crank pulse if the interpolated engine position does not match the true position for that pulse stored in EPT configuration RAM. If the interpolated value is too low (increase in engine speed) the angle count will be updated every 2 usec until it reaches the true position. If the angle count reaches the angular position of the next pulse before that pulse occurs (decrease in engine speed), the angle count will stop incrementing. When the pulse occurs, the angle count will be at the correct value and will begin counting again (at a new interpolation rate based on the spacing and time between the last two pulses). Notice that there are no missing angles in the angle count (monotonic) and once a new crank edge is received the angle count (ACNT) is immediately corrected.

Following a reset, ACNT is set to 07FF. This is not a valid angle count and inhibits any spark or fuel output pulses from occurring. ACNT remains at 07FF until synchronization with the engine is attained, at which time ACNT is initialized to the actual engine position.

ACNT cannot be read directly by the host. To read the angle count, the host must first write to location C0. This latches the present contents of ACNT into the 16 bit Angle Count Register (location C0 and C1). The Angle Count Register can then be read at any time, and will not change until another write to C0 occurs.

#### **Synchronization**

Synchronization (sync) is defined as the condition where the angle count (ACNT) reflects the actual engine position. For a four cycle engine, there can be two types or stages of sync. This is due to the fact that it takes two crankshaft revolutions (720 degrees) to complete one engine cycle.

Since the crankshaft rotates once every 360 degrees, the crank sensor pattern repeats this often. If the angle count attains sync to the crank (360 degree sync), the least significant 11 bits of ACNT accurately reflect the crankshaft position (0 to 360 degrees). This is sufficient for some engine control functions and in many cases can be attained sooner than 720 degree sync.

For other engine control functions (sequential injection, coil per cylinder DIS), crankshaft sync is not sufficient. Camshaft position is also required to indicate where in the engine cycle the crankshaft is. This is called cam or 720 degree sync. The MSB of ACNT (ac11) is used to indicate a unique angular position between 0 and 720 degrees. Some engines (such as 2 cycle) do not require 720 degree sync.

The 67F687 allows both types of sync to be used. Initially 360 degree sync can be attained and used to trigger the outputs and later, when 720 degree sync is attained, the EIP can be switched to that mode.

The mechanism by which either type of sync is attained is the detection of a unique pattern of crank and/or cam pulses, which corresponds to a particular crank or cam position. This unique pattern is then compared to patterns in the EPT configuration memory and if a match is found, the engine position corresponding to that pattern is loaded into ACNT. The EIP allows 8 unique patterns and each one can initiate either 360 or 720 degree sync.

Once sync is attained, the patterns are continuously detected and compared with the configuration memory. If ACNT does not match the expected value, the F687 sets an interrupt flag. Actions taken in this instance are determined by the initial setup by the host.

#### REGISTER DESCRIPTION (continued)

#### **EPT Interrupts**

Three interrupts can be generated by the EPT: attained 360 degree sync, attained 720 degree sync and lost either type of sync. These will set the appropriate bits in the Interrupt Register (location F3) and can generate an external interrupt to the host, depending on the value of the appropriate bit in the MASK Register (location F0).

If synchronization is lost, the cause is identified by a bit in the Sync Interrupt Status Register (SISR) at location C2. Normal operation is designated by a logic "0". A "1" indicates the reason that the EPT lost synchronization. Once set (to "1"), bits in SISR can only be cleared (reset to "0") by a read of the SISR register. This clears all the bits in the register.

#### SISR Location C2

| Γ | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

| ľ | 0     | ТО    | IP    | AP    | ACLSB | ST360 | ST720 | ACMSB |

| Bit 7 | NOT USED.                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| то    | Timer Overflow: This is the timer that measures the time between crank pulses and is used to generate the interpolated 0.25 degree pulses. An overflow here means that there was too much time between pulses (crank sensor signal lost or engine cranking stopped or is too slow). The maximum time between two pulses is:  Max time = 65535 • (degrees between pulses • 4 / 8,000,000) sec. |

| IP    | Invalid pattern received: The pattern acquired does not match any of the patterns stored in PSREG.                                                                                                                                                                                                                                                                                            |

| AP    | Address pointer error: The address stored in PRRAM for the acquired pattern does not match the address of the next expected tooth (CWRAM address).                                                                                                                                                                                                                                            |

| ACLSB | Angle count error: Expected ACNT (bits 10-0) associated with the acquired pattern does not match true ACNT.                                                                                                                                                                                                                                                                                   |

| ST360 | 360 degree information stop: No 360 degree patterns were matched in two complete revolutions (720 degrees of ACNT).                                                                                                                                                                                                                                                                           |

| ST720 | 720 degree information stop: No 720 degree patterns were matched in two complete revolutions (720 degrees of ACNT).                                                                                                                                                                                                                                                                           |

| ACMSB | MSB error: Expected ACNT MSB (bit 11) associated with the acquired pattern does not match true ACNT MSB.                                                                                                                                                                                                                                                                                      |

If the EPT is not reset (either automatically or by the host) after generating an out of sync interrupt, it will assume it is still in sync. In this case, if the condition that caused the interrupt reoccurs, another interrupt will be generated.

#### **TACH and SYNC Outputs**

A bit in EPTRST determines which signals are output to these pins. Either the conditioned CRANK and CAM (the output of the PSI) or the TACH and SYNC can be selected.

TACH and SYNC are one bit outputs used to relay specific engine positions to the host processor. These are both low frequency signals whose rising and falling edges indicate a particular engine position.

The SYNC signal output depends on the type of synchronization attained by the EPT. In 720 degree mode, it mirrors the MSB (bit 11) of the angle count (ACNT). The falling edge indicates a position of 0 (or 720) degrees. The rising edge indicates 360 degrees. The exception to this is the first rising edge after a reset. During reset the SYNC will go low (MSB of ACNT = 0) and a rising edge could occur anywhere between 360 and 720 degrees if the EPT attains 720 degree sync in this region. In 360 degree synchronization mode SYNC

outputs a single low pulse per revolution with the falling edge at 0 degrees and a duration equal to the TACH pulsewidth.

The TACH output allows the host a finer resolution of angular position. It changes states every (TANG X 15) degrees. TANG is a number from 0 to 7 specified at location C3 (EPTRST) bits 4-2 (if TANG = 0 the multiplier is 8). In this way the host can receive angular position updates at angles of 15 to 120 degrees apart in multiples of 15 degrees. The TACH is reset to a low at 0 and 360 degrees. This means that after reset the TACH signal edges may not occur on 15 degree multiples of ACNT until ACNT reaches 0 or 360 degrees.

#### **EPT Reset Register (EPTRST)**

The EPTRST register (location C3) contains the bit to select the signals output on the TACH and SYNC pins, the TANG multiplier and the 720 and 360 degree reset bits. These enable the host to reset the EPT externally.

EPTRST Location C3

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | 0     | TSSEL |       | TANG  |       | RST7  | RST3  |

| Bit 7 | NOT USED. Always reads "0".                                                                                                                                                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 6 | NOT USED. Always reads "0".                                                                                                                                                 |

| TSSEL | TACH and SYNC select bits. Determines signal which is output on TACH and SYNC pins.  TSSEL = 0 - TACH and SYNC are output. TSSEL = 1 - Conditioned CRANK and CAM are output |

| TANG  | Multiplier used to specify TACH output. TACH is reset to 0 on the rising or falling edge of SYNC and changes states every TANG X 15 degrees.                                |

| RST7  | Writing a "1" to this bit will reset the ACNT 720 degree bit (bit 11). This must be followed by a "0" to this location to enable normal operation again.                    |

| RST3  | Writing a "1" to this bit will reset ACNT to "7FF" (360 degree reset). This must be followed by a "0" to this location to enable normal operation again.                    |

#### REGISTER DESCRIPTION (continued)

#### Test Registers (TMUX, TREG1, TREG2)

These registers are located at locations C4 through C6 and are used for factory testing. They should not be accessed during normal operation.

#### **EPT Configuration (Page 1 Memory)**

The EPT configuration memory is used by the host processor to configure the EPT for a specific sensor pattern. It specifies the crank sensor pulses and spacings (used to update ACNT) and the unique patterns and angular positions for attaining sync. The EPT cannot interpret position until the configuration memory is written to from the host processor. Because the data is supplied by the host, the host has no need to access this data after initialization, and should not do so without disabling the outputs. This memory is located on Page 1 of the memory map and to access it, a "1" must be written to the page select bit (bit0) of the GCR (location F6). This bit is set to a "1" by a reset.

The EPT configuration memory is divided into five sections: Crank Wheel RAM, Pattern Recognition RAM, Pattern Storage registers, Pattern Configuration registers and Pattern Acquisition registers. Each section is described in detail below.

#### Crank Wheel RAM (CWRAM)

CWRAM is 64 bytes located from 100 to 13F HEX. This RAM is used to define the crank wheel tooth (crank sensor pulse) spacing. The method chosen requires minimal RAM space for a large variety of wheel configurations.

To determine the proper data to load into CWRAM for a given wheel type, divide the wheel into sections of evenly spaced teeth. Arbitrarily choose one section and label the last tooth in this section as "00" HEX. Number the previous tooth "01", the one before it "02" and so on until all teeth are numbered. The tooth numbers should DECREASE as the engine rotates.

For a given section, the last tooth is defined as the one which precedes a change in tooth spacing. The last section is defined as the last section occurring in time as the engine rotates. The last tooth in the last section is the one numbered "00" (this is also the lead tooth in the first section).

The CWRAM consists of 32 pairs of 8 bit locations, each used to describe one section on the wheel. This means that the crank wheel can have up to 32 sections with each section having a unique tooth spacing. The information loaded for each section follows the format below.

CWSPxx spacing between teeth (degrees X 4 or degrees depending on PMREG1 bit 7)

CWTHxx number of next to last tooth in section

The information describing the last section is loaded into the first pair of locations (00 and 01), the next to last section is loaded into 02 and 03 and so forth until data for all sections of the wheel is loaded. If a particular wheel has N sections, then 2N locations will be loaded.

#### **CWRAM Format**

| NAME   | LOC | CONTENTS                               |

|--------|-----|----------------------------------------|

| CWSP00 | 100 | spacing in section N                   |

| CWTH00 | 101 | # of next to last tooth in section N   |

| CWSP01 | 102 | spacing in section N-1                 |

| CWTH01 | 103 | # of next to last tooth in section N-1 |

| CWSP (N-1) | 1 (2N-3) | spacing in section 2                 |

|------------|----------|--------------------------------------|

| CWTH (N-1) | 1 (2N-2) | # of next to last tooth in section 2 |

| CWSP (N)   | 1 (2N-1) | spacing in section 1                 |

| CWTH (N)   | 1 (2N)   | # of next to last tooth in section 1 |

#### Pattern Recognition RAM (PRRAM)

The Pattern Recognition RAM consists of 32 bytes starting at 140 HEX and containing information associated with each unique pattern used for sync. There are eight groups of four locations to correspond to the eight unique patterns specified in PSREG. The PRRAM contains the angle count for a particular crank pulse, the number of that pulse (tooth) and the address of CWRAM

where the section of the wheel that contains that pulse is specified (the location where the next to last tooth in the section is specified). That address (minus the page bit) is divided by two and stored in PRRAM. There is a one to one correspondence of PRRAM to the patterns specified in PSREG (i.e. locations 140 - 143 refer to pattern 1 at location 160, locations 144 - 147 refer to pattern 2 at location 161, etc.).

#### **PRRAM Format**

| NAME   | LOC | CONTENTS                         |

|--------|-----|----------------------------------|

| PRACH1 | 140 | Pattern 1 angle count High       |

| PRACL1 | 141 | Pattern 1 angle count Low        |

| PRTN01 | 142 | Tooth number at that angle count |

| PRADD1 | 143 | CWRAM address of section / 2     |

| PRACH8 | 15C | Pattern 8 angle count High       |

|--------|-----|----------------------------------|

| PRACL8 | 15D | Pattern 8 angle count Low        |

| PRTN08 | 15E | Tooth number at that angle count |

| PRADD8 | 15F | CWRAM address of section / 2     |

#### REGISTER DESCRIPTION (continued)

#### Pattern Storage Registers (PSREG)

The pattern storage registers are eight single byte registers located at 160 HEX to 167 HEX. The lower seven bits of each byte contain a sync pattern as it would be received by the Pattern Acquisition section of the EPT (specified by the Pattern Aquisition Registers-PAREG). The MSB is used to identify the pattern as occurring every 360 or every 720 degrees.

MSB = 0 Pattern occurs every 360 degrees MSB = 1 Pattern occurs every 720 degrees

This bit is used by the EPT to determine which type of sync (360 or 720 degree) to enter when this pattern is matched.

CBIT (bit 6) is a special bit in the pattern which corresponds to bit 6 of the acquired pattern (as specified by the PAREG registers). This bit will be set by the Cam

signal or a derivative of it as specified by bits 6 and 7 in the PAREG3 register. This feature allows differentiation of identical crank patterns if one is accompanied by a carn pulse and one is not.

CBIT = 0 If bit 6 of acquired pattern will not be set CBIT = 1 If bit 6 of acquired pattern will be set

The lower 6 bits are the decoded pattern of the crank and carn sensors as defined by the Pattern Acquisition Registers.

There is a one to one correspondence between the patterns stored here and the data stored in PRRAM. If a pattern occurs every 360 degrees (MSB = 0), then the corresponding angle count in PRRAM should also have a "0" in the MSB (bit 11). If less than eight patterns are used, the data in the unused patterns is not critical; however, each location must have a unique 8 bit value (unused pattern locations cannot all have the same contents).

#### **PSREG Format**

| NAME   | LOC | CONTENTS |      |                    |  |  |

|--------|-----|----------|------|--------------------|--|--|

| PATRN1 | 160 | MSB      | CBIT | Pattern 1 (6 bits) |  |  |

| PATRN2 | 161 | MSB      | CBIT | Pattern 2          |  |  |

| PATRN3 | 162 | MSB      | CBIT | Pattern 3          |  |  |

| PATRN4 | 163 | MSB      | CBIT | Pattern 4          |  |  |

| PATRN5 | 164 | MSB      | CBIT | Pattern 5          |  |  |

| PATRN6 | 165 | MSB      | CBIT | Pattern 6          |  |  |

| PATRN7 | 166 | MSB      | CBIT | Pattern 7          |  |  |

| PATRN8 | 167 | MSB      | CBIT | Pattern 8          |  |  |

#### Pattern Acquisition Registers (PAREG)

The Pattern Acquisition section of the EPT contains four registers which define the format of the synchronization patterns and conditions (or "windows") underwhich they will be accepted as valid.

All patterns, to be recognized by the EPT, must have some common characteristics. Every pattern is preceded by a specified number of crank pulses. A start of pattern (SOP) pulse defines the beginning of the pattern and a specified number of end of pattern (EOP) pulses define its end. The pattern (as stored in the Pattern Storage Registers) is defined as beginning at the start of pattern pulse and ending on the last EOP pulse.

Synchronization patterns can be divided into two general groups: counted and decoded. Counted patterns are those where some specified pulses are counted as they are received. Decoded patterns are those where one signal is the data and is clocked into a shift register by another signal which is the clock. The 67F687 supports both types of patterns.

In addition to the conditioned crank and cam signals available from the PSI, other signals are generated by the EPT and can be used to either specify a pattern window or the pattern itself. These are generated in the EPT even if they are not used. Whether they are utilized depends on the individual application. A definition of these signals derived from the crank and cam pulses would be appropriate here.

Missing and extra crank pulses are detected by circuits in the EPT. These continuously monitor the time between successive crank input pulses. If this time increases or decreases drastically (taster than would be possible under normal acceleration or deceleration of the engine), then a missing or extra pulse detect signal is generated.

Crank - The conditioned crank signal which

is generated by the PSI.

Cam - The conditioned cam signal gener-

ated by the PSI.

Missing Crank - Pulse generated by the missing crank

pulse detection circuit.

Extra Crank - Pulse generated by the extra crank

pulse detection circuit.

Qualified Crank - Crank signal with the extra pulses

removed.

Crank Data - Signal generated by extra and miss-

ing pulses: rising edge on extra crank pulse, toggles on every crank pulse after that, and goes low (and stays low) when a missing pulse is encountered. This signal can be used for a coded pattern, when the data and the clock are both crank pulses.

Slow Cam - Rising edge on campulse and falling

edge on next end of pattern.

Two additional signals are available but should not be used in normal operation. These are for factory testing only:

Crank Pin - Input directly from the CRANK pin

(bypasses the PSI).

Cam Pin - Input directly from the CAM pin (by-

passes the PSI).

### REGISTER DESCRIPTION (continued)

#### Pattern Acquisition Registers (PAREG) (continued)

PAREG1 and PAREG4 (loc. 168 and 16B) define the window in which the pattern occurs. PAREG1 specifies the number of crank pulses before the EPT begins looking for a SOP pulse to begin the pattern and the number of EOP pulses to end the pattern.

#### PAREG1

Location 168

| Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|--------|-------|-------|-------|-------|-------|-------|

|       | EOPNUM |       |       |       | CRK   | NUM   |       |

| EOPNUM | The number of EOP pulses to end the pattern. Must be a number from 1 (0001) to 15 (1111) - 0000 is not valid.               |

|--------|-----------------------------------------------------------------------------------------------------------------------------|

| CRKNUM | The number of crank pulses before looking for a SOP pulse. Must be a number from 1 (0001) to 15 (1111) - 0000 is not valid. |

PAREG4 specifies the type or types of pulses used for SOP or EOP. They can be one or a combination of the allowable pulses.

#### PAREG4

Location 16B

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       | SO    | TYP   |       |       | EO    | TYP   |       |

| SOPTYP | Any or all of the following types of signals can be an SOP pulse, enabled by setting the appropriate bit in SOPTYP: |

|--------|---------------------------------------------------------------------------------------------------------------------|

|        | Bit 7 - Crank Bit 6 - Cam Bit 5 - Extra Crank Bit 4 - Missing Crank                                                 |

| EOPTYP | Any or all of the following types of signals can be an EOP pulse, enabled by setting the appropriate bit in EOPTYP: |

|        | Bit 3 - Extra Crank Bit 2 - Missing Crank Bit 1 - Qualified Crank Bit 0 - Crank                                     |

PAREG2 and PAREG3 determine the type of pattern (counted or coded) and the signals used to generate the pattern. PAREG2 defines the type of pattern and the signal used for data if the pattern is a coded type. If the pattern is a counted type, then bits 5-0 have no meaning.

#### PAREG2

Location 169

| Bit 7 | Bit 6          | Bit 5                           | Bit 4 | Bit 3 | Bit 2          | Bit 1             | Bit 0         |

|-------|----------------|---------------------------------|-------|-------|----------------|-------------------|---------------|

| PBE   | PBE TYP CDEDAT |                                 |       |       |                |                   |               |

| PBE   |                | 6 enable. This<br>ined in PATBT |       |       | acquired patte | ern will be set t | oy one of the |

| PBE    | Pattern bit 6 enable. This bit determines if bit 6 in the acquired pattern will be set by one of the signals defined in PATBT6 (PAREG3 bits 7 and 6).  PBE = 0 - Pattern bit 6 set based on PATBT6.  PBE = 1 - Pattern bit 6 always "0".             |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TYP    | Specifies the type of pattern:  TYP = 0 - Pattern is coded  TYP = 1 - Pattern is counted                                                                                                                                                             |

| CDEDAT | Defines the signal or signals uses as data for a coded pattern. Not used (and contents have no effect) if data is counted (TYP = 1). The data can be any or all of the following types of signals, enabled by setting the appropriate bit in CDEDAT: |

|        | Bit 5 - Crank Data Bit 4 - Always "0" Bit 3 - Cam Bit 2 - Missing Crank Bit 1 - Extra Crank Bit 0 - Cam Pin (FOR TEST ONLY)                                                                                                                          |

#### REGISTER DESCRIPTION (continued)

#### Pattern Acquisition Registers (PAREG) (continued)

PAREG3 defines the clock for coded data (if PAREG2 bit 6 = 0) or the signal that is counted (if PAREG2 bit 6 = 1).

#### PAREG3

Location 16A

| Bit 7  | Bit 6                    | Bit 5                        | Bit 4                                                                          | Br 3                                 | Bit 2           | DIL I           | DIL U        |  |  |

|--------|--------------------------|------------------------------|--------------------------------------------------------------------------------|--------------------------------------|-----------------|-----------------|--------------|--|--|

| PAT    | ГВТ6                     | CNTCLK                       |                                                                                |                                      |                 |                 |              |  |  |

| PATBT6 | pattern. Th              | is correspor<br>PSREG. O     | it 7 = "0", PATB<br>nds to CBIT (bit<br>ne of the following                    | 6) of the speci                      | fied patterns s | stored in PATF  | N1 through   |  |  |

|        | Bit7<br>0<br>0<br>1<br>1 | 0 (<br>1 h                   | Signal Cam Not Used Slow Cam Cam Pin (TEST                                     | ONLY)                                |                 |                 |              |  |  |

| CNTCLK | Defines the              | e signal or signal or signal | oit 6 of the acquir<br>gnals that are co<br>TYP = 0). The p<br>appropriate bit | unted if the patt<br>oulses can be a | em type is cou  | inted (TYP = 1) | or the clock |  |  |

|        |                          | n                            |                                                                                |                                      |                 |                 |              |  |  |

#### **Test Registers**

Special test registers are located at locations 16E and 16F. These are used for factory testing of the part and should not be accessed during normal operation.

Bit 0 - Crank Pin (FOR TEST ONLY)

#### Pattern Match Registers (PMREG)

Bit 2

The Pattern Match registers are seven miscellaneous registers in the EPT, which contain crank wheel information, default information and EPT reset control.

Bit 0

#### PMREG1

Location 170

| Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

|-------|-------|-------|--------|-------|-------|-------|-------|--|--|

| RES   | 0     |       | NUMSEC |       |       |       |       |  |  |

| RES    | Resolution of tooth spacing in CWSPxx.  RES = 0 - CWSPxx is 0.25 degrees per bit (maximum 63.75 deg.)  RES = 1 - CWSPXX is 1 degree per bit (maximum 255 deg.) |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMSEC | Number of sections on crank wheel - 1 (as described in CWRAM. Must be a number from 0 through 31 (1 through 32 sections)                                       |

#### PMREG2

Location 171

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | IAE3  | IAE7  |       |       | 0     |       |       |

| IAE3 | Enables automatic reset of ACNT (locations C0 and C1) upon a 360 degree type out-of-sync error. ACNT is reset to 07FF.  IAE3 = 1 - Automatic reset of ACNT IAE3 = 0 - Manual reset by host required. |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IAE7 | Enables automatic reset of MSB (720 degree bit) in ACNT (location C0) upon a 720 degree type out-of-sync error.  IAE7 = 1 - Automatic reset of ACNT MSB IAE7 = 0 - Manual reset by host required.    |

#### PMREG3

Location 172

| Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

|--------|-------|-------|-------|-------|-------|-------|-------|--|--|

| PULNUM |       |       |       |       |       |       |       |  |  |

| PULNUM     | Number of pulses (teeth) on crank wheel - | 1 (number from 0 to 255 ( | 00 to FF HEX)) |

|------------|-------------------------------------------|---------------------------|----------------|

| 1 02110111 | Transcr or puises (teetin) on crank wheer |                           |                |

#### REGISTER DESCRIPTION (continued)

#### Pattern Match Registers (PMREG) (continued)

PMREG5 contains a default tooth spacing (in degrees X 4) which is used before sync is attained. The value loaded here depends on the particular pattern and can affect how fast the EPT will attain sync with that particular pattern. PMREG5 is accessed at either location 174 or 175 (a write to either location will change PMREG5).

#### PMREG5

Location 174 or 175

| Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |  |

|--------|-------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| SPSDFT |       |       |       |       |       |       |       |  |  |  |  |

|   | SPSDFT | Spacing between crank teeth used as a default before sync is attained. Units are consistent with CWSPxx (0.25 deg/bit if PMREG1 bit $7 = 0$ and 1 deg/bit if PMREG1 bit $7 = 1$ ). Number from 01 to FF HEX. |

|---|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 |        | (0.11.1.12.11                                                                                                                                                                                                |

PMREG4, PMREG6 and PMREG7 (locations 173, 176 and 177) are used for testing only and should not be written to during normal operation.

#### **FUEL SPARK PULSE GENERATOR (FSPG)**

The FSPG generates the digital pulses that are used by the Fuel Spark Output Controller (FSOC) to create the fuel and ignition output signals.

Eight spark pulses, each with a start and stop angle, can be programmed. These are mapped to the four ignition outputs. This allows an individual spark advance for up to eight cylinders when the ignition outputs control dual ended ignition coils (one coil for two cylinders).

Eight fuel pulses, each with a start angle and pulsewidth time, can also be programmed.

The FSPG uses the angle count (ACNT) from the EPT and an internal timer to generate these digital pulses at the correct engine positions. These pulses can also be initiated or terminated directly by the host.

#### **Direct Output Control**

The GCR (location F6) allows the host to choose either direct control or programmed control of the spark and fuel outputs. After reset, the GCR is configured for direct control.

If GCR bit 4 = 1, the spark pulses are generated under direct control by the host. Each spark pulse mirrors the associated bit in the Spark Pulse Register (location F1);

bit 0 of the Spark Pulse Register (SPRK) corresponds to spark pulse 0, bit 7 corresponds to spark pulse 7. A "1" in each bit location will turn on the pulse and a "0" will turn it off. If GCR bit 4=0, the SPRK register has no effect on the outputs. Upon reset SPRK is set to "00", turning off all spark pulses.

If GCR bit 7 = 1, the fuel pulses are under direct host control. Each fuel pulse is initiated by a writing a "1" to the corresponding bit in the Fuel Pulse Register (location F2) followed by writing a "0" to that bit. Bit 0 of the Fuel Pulse Register (FUEL) corresponds to fuel pulse 0, bit 7 corresponds to fuel pulse 7. The duration of the pulse is determined by the programmed pulsewidth stored in Fuel RAM (FRAM), and cannot be turned on indefinitely (but if the bit in the Fuel Pulse Register is still set to a "1" when the pulse times out, it will be immediately turned on again). In this way the fuel pulses differ from the spark pulses. If GCR bit 7 = 0, the FUEL register has no effect on the outputs. Upon reset FUEL is set to "00", turning off all fuel pulses.

The FSPG also allows a hard shutdown of all spark and fuel pulses by the host. If bit 5 of the GCR is a "1", all eight spark and all eight fuel pulses will be turned off immediately and will stay off until that bit is changed to a "0". Upon reset bit 5 of the GCR is set to a "0", enabling the outputs.

#### GCR Location F6

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| FDC   | 0     | SHTDN | SDC   | TST3  | TST2  | TST1  | PG    |

| FDC   | Fuel Direct Control bit  FDC = 0 - Programmed control of fuel outputs  FDC = 1 - Direct control of fuel using FUEL register  |

|-------|------------------------------------------------------------------------------------------------------------------------------|

| Bit 6 | NOT USED (always returns a "0" when read)                                                                                    |

| SHTDN | Hard Shutdown bit SHTDN = 0 - Normal operation SHTDN = 1 - All fuel and spark outputs are turned off                         |

| SDC   | Spark Direct Control bit SDC = 0 - Programmed control of spark outputs SDC = 1 - Direct control of spark using SPRK register |

| TST3  | Test bit (factory testing only - should always be a "0").                                                                    |

| TST2  | Test bit (factory testing only - should always be a "0").                                                                    |

| TST1  | Test bit (factory testing only - should always be a "0").                                                                    |

| PG    | Page bit for addressing page 1 memory PG = 0 - Page 0 addressed PG = 1 - Page 1 addressed                                    |

At reset, the GCR is initialized to "91". This enables fuel and spark direct control and sets up page 1 addressing.

#### SPRK Location F1

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SPK7  | SPK6  | SPK5  | SPK4  | SPK3  | SPK2  | SPK1  | SPK0  |

If SDC = 1:

SPKx = 0 SPARKx pulse is off SPKx = 1 SPARKx pulse is on

If SDC=0: SPKx has no effect

#### REGISTER DESCRIPTION (continued)

#### **FUEL**

#### Location F2

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| FUEL7 | FUEL6 | FUEL5 | FUEL4 | FUEL3 | FUEL2 | FUEL1 | FUEL0 |

If FDC = 1:

FUELx = 0 no effect

FUELx = 1 FUELx output pulse is initiated

If FDC = 0:

FUELx has no effect

At reset SPRK and FUEL are both initialized to "00", turning off all outputs.

#### **Programmed Output Control**

#### Spark pulses

When GCR bit 4 (SDC) = 0, spark pulses are generated from a start angle to a stop angle. These start and stop angles are stored in Spark RAM (SRAM) at locations 00 through 1F HEX as 16 bit numbers. Start angles are stored in SSTRHx and SSTRLx and stop angles are stored in SSTPHx and SSTPLx. They have the same format as ACNT (0 to 359.75 degrees in 0.25 degree increments with bit 11 indicating an angle count between 360 and 720 degrees). In addition, the angles are concatenated with a bit in the most significant location (bit 15) that tells the FSPG if the angle is used every 720 or 360 degrees.

When ACNT is equal to the start or stop angle programmed, the spark pulse will either begin or end. If bit 15 is a "1", all twelve bits of ACNT are compared to SSTRHx, SSTRLx (SSTPHx, SSTPLx) to initiate (end) a pulse. This generates a pulse every 720 degrees. If

this bit is a "0", bit 11 (MSB) of ACNT is ignored and only bits 10-0 are compared to SSTRHx, SSTRLx (SSTPHx, SSTPLx). This generates a pulse every 360 degrees.

NOTE: Care should be exercised to only set this bit if the EPT is in the 720 degree sync mode. If it is set, and the EPT is tracking in 360 degree mode, any angles with a "1" in bit 11 will not be recognized.

Two byte writes are required to update an angle. The most significant byte (MSB) must be written first, followed by the LSB. This is because the MSB is stored in a latch until the LSB is received, and both bytes of the angle value are updated simultaneously. Angles can be read in any order.

There are eight digital spark pulses in the FSPG. After the angle count (ACNT) changes, all the values in SRAM are compared to the current angle count. If a match(s) is found, the related pulse(s) will start or end 2  $\mu$ s after the angle changed (at 10,000 RPM, 2  $\mu$ s is equal to 0.125 crankshaft degrees).

|                                                                                                   |  |     | SS                 | STRHx                  | SSTRLx                                                                                             |  |

|---------------------------------------------------------------------------------------------------|--|-----|--------------------|------------------------|----------------------------------------------------------------------------------------------------|--|