# Fairchild Imaging Sensors CC

# **PRELIMINARY**

# CCD192 6000 Element Linear Image Sensor

#### **FEATURES**

- 6000 × 1 photosite array

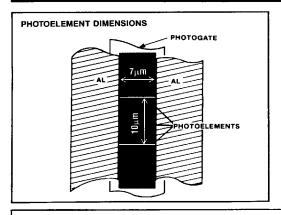

- $10\mu m \times 7\mu m$  photosites on  $10\mu m$  pitch

- Anti-blooming and integration control

- Enhanced resolution in the red region

- Excellent low-light-level performance

- Low dark signal

- High-speed operation

- Dynamic range typical: 11000:1

- Over 2V peak-to-peak outputs

- Special selection available consult factory

- AR coated window

#### **GENERAL DESCRIPTION**

The CCD192 is a 6000 element line image sensor designed for scanning applications which require very high resolution, high sensitivity and wide dynamic range. Incorporation of on-chip anti-blooming and integration controls allow the CCD192 to be extremely useful in industrial measurement and control environments or environments where lighting conditions are difficult to control.

The CCD192 is a third generation device having an overall improved performance compared with first and second generation devices, including excellent low light level performance. The photoelement size is  $10\mu m$  (0.39 mils)  $\times$   $7\mu m$  (0.28 mils) on  $10\mu m$  (0.39 mils) centers. The device is manufactured using Loral Fairchild's advanced charge-coupled device n-channel Isoplanar buried-channel technology.

Loral Fairchild Imaging Sensors 1801 McCarthy Blvd., Milpitas, CA 95035 1 800 325-6975, TWX 910-373-2110, (408) 433-2500

© 1994 Loral Fairchild reserves the right to make changes in the circuitry or specifications at any time without notice.

#### **FUNCTIONAL DESCRIPTION**

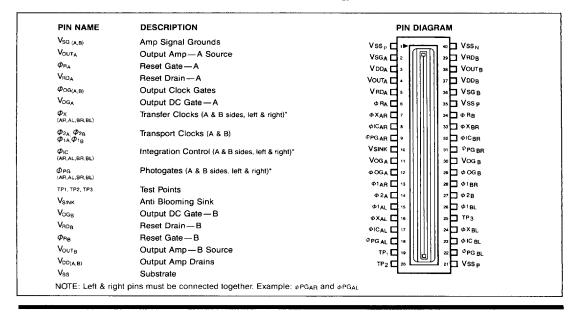

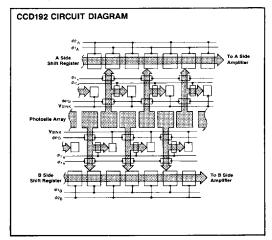

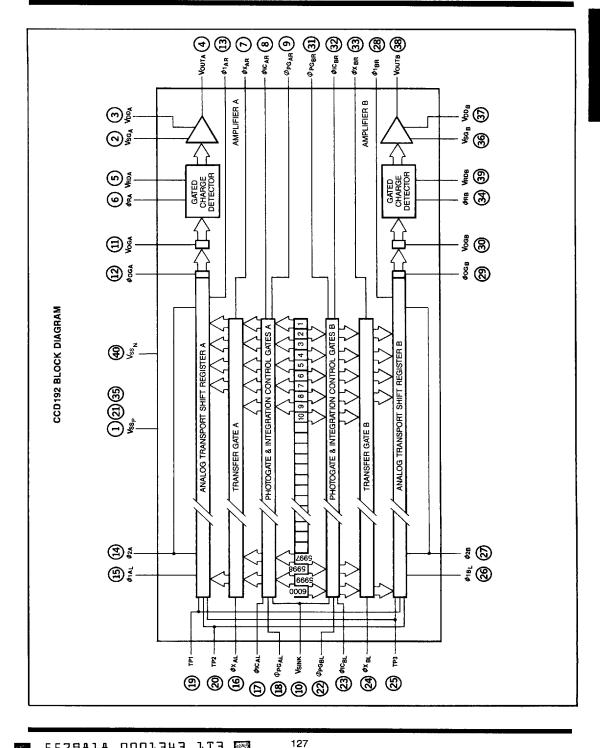

The CCD192 consists of the following functional elements illustrated in the block diagram and circuit diagram.

Photosites — A row of 6000 image sensor elements separated by a diffused channel stop and covered by a silicon dioxide surface passivation layer. Image photons pass through the transparent silicon dioxide layer creating hole-electron pairs. The photon generated electrons are accumulated in the photosites. The amount of charge accumulated in each photosite is a linear function of the incident illumination intensity and the integration period. The output signal will vary in an analog manner from a thermally generated background level at zero illumination to a maximum at saturation under bright illumination.

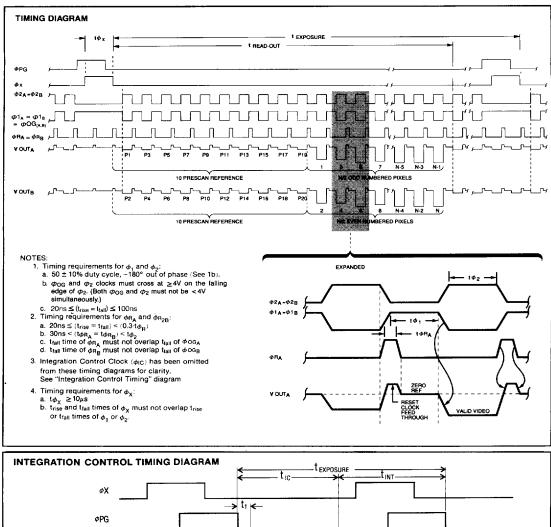

**Two Transfer Gates**—Gate structures adjacent to the row of image sensor elements. The charge packets accumulated in the photosites are transferred in parallel via the transfer gates  $(\phi X)$  to the transpositif registers whenever the transfer gate voltages go high. Alternate charge packets are transferred to the A and B transport registers.

**Two Analog Transport Shift Registers** — The transport shift registers are used to move the light generated charge packets delivered by the transfer gates  $(\phi_{1A}, \phi_{1B}, \phi_{2A}, \phi_{2B})$  serially to the charge detector/amplifier. The parallel layout of the last elements of the two transport registers provides for simultaneous delivery of charge packets at the output amplifiers.

A Gated Charge Detector/Amplifier—Charge packets are transported to a precharged capacitor whose potential changes linearly in response to the quantity of the signal charge delivered. This potential is applied to the input gate of the two-stage NMOS amplifiers producing a signal at the output "Vour" pin. Before each charge packet is sensed, a reset clock ( $\phi_{RA}$ ,  $\phi_{RB}$ ) recharges the input node capacitor to a fixed voltage ( $V_{RDA}$ ,  $V_{RDB}$ ).

Integration and Anti-Blooming Controls—In many applications the dynamic range in parts of the image is larger than the dynamic range of the CCD, which may cause more electrons to be generated in the photosite area than can be stored in the CCD shift register. This is particularly common in industrial inspection and satellite applications. The excess electrons generated by bright illumination tend to "bloom" or "spill over" to neighboring pixels along the shift register, thus "smearing" the information. This smearing can be eliminated using two methods:

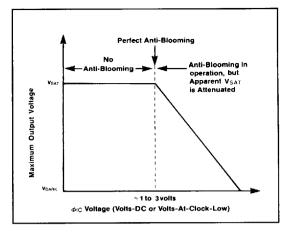

#### **Anti-Blooming Operation:**

A DC voltage applied to the integration control gate (approximately 1 to 3 volts) will cause excess charge generated in the photosites to be diverted to the anti-blooming sink ( $V_{\rm SINK}$ ) instead of to the shift registers. This acts as a ''clipping circuit'' for the CCD output.

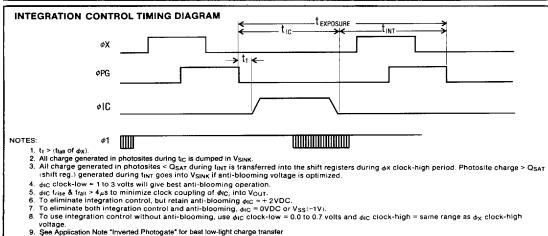

## Integration Control Operation:

Variable integration times which are less than the CCD exposure time may be attained by supplying a clock to the integration control gate. Clocking  $\phi_{\rm IC}$  reduces the integration time from  $t_{\rm EXPOSURE}$  to  $t_{\rm INT}$ . Greater than 10:1 reduction in average photosite signal can be achieved with integration control.

The integration-control and anti-blooming features can be implemented simultaneously. This is done by setting the  $\phi_{IC}$ , clock-low level to approximately 1 to 3 volts.

#### **DEFINITION OF TERMS**

Charge-Coupled Device — A charge-coupled device is a semiconductor device in which finite isolated charge packets are transported from one position in the semiconductor to an adjacent position by sequential clocking of an array of gates. The charge packets are minority carriers with respect to the semiconductor substrate.

Prescan Reference — Video output level generated from shift register cells which provides a reference voltage equivalent to device operation in the dark. This permits use of external DC restoration circuitry.

Dynamic Range — The saturation exposure divided by the RMS temporal noise equivalent exposure. Dynamic range is sometimes defined in terms of peak-to-peak noise. To compare the two definitions a factor of four to six is generally appropriate in that peak-to-peak noise is approximately equal to four to six times RMS noise.

RMS Noise Equivalent Exposure — The exposure level that gives an output signal equal to the RMS noise level at the output in the dark.

**Saturation Exposure**—The minimum exposure level that will provide a saturation output signal. Exposure is equal to the light intensity times the photosite integration time.

Charge Transfer Efficiency — Percentage of valid charge information that is transferred between each successive stage of the transport registers.

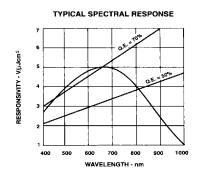

Responsivity — The output signal voltage per unit exposure for a specified spectral type of radiation. Responsivity equals output voltage divided by exposure.

Total Photoresponse Non-Uniformity—The difference of the response levels of the most and the least sensitive element undre uniform illumination. Measurements of PRNU excludes first and last elements

**Dark Signal** — The output in the dark caused by thermally generated electrons that is a linear function of the integration time and is highly sensitive to temperature.

Saturation Output Voltage — The maximum useable signal output voltage. Charge transfer efficiency decreases sharply when the saturation output voltage is exceeded.

Integration Time — The time interval between the falling edge of the integration clock and the falling edge of the transfer clock. The integration time in which charge is accumulated in the photosites.

**Exposure Time**—The time interval between the falling edge of the two transfer pulses ( $\phi X$ ) shown in the timing diagram. The exposure time is the time between transfers of signal charge from the photosites into the transport registers.

Pixel - A picture element (photosite).

126

5579818 0001343 1T3 🖼

| (above which useful life may be        | impaired)         |

|----------------------------------------|-------------------|

| Storage Temperature                    | -25° C to +125° C |

| Operating Temperature                  | -25° C to +70° C  |

| CCD 191: Pins 2, 36 (V <sub>SG</sub> ) | ov                |

| Pins 1, 21, 35 (V <sub>SSP</sub> )     | -3.0V to 0V       |

| Pins 4, 38 (V <sub>OUT</sub> )         | See Caution Note  |

| Pin 40 (V <sub>SSN</sub> )             | 0V to +5V         |

| All other pins                         | -3.0V to +18V     |

#### **CAUTION NOTE:**

These devices have limited built-in gate protection. It is recommended that static discharge be controlled and minimized. Care must be taken to avoid shorting pins  $V_{OUTA+B}$  to  $V_{SS}$  or  $V_{DD}$  during operation of the devices. Shorting these pins temporarily to  $V_{SS}$  or  $V_{DD}$  may destroy the output amplifiers.

# DC CHARACTERISTICS: Tp = 25° C (Note 1)

| SYMBOL                           | CHARACTERISTIC                        |      | RANGE           |      |    | CONDITIONS |

|----------------------------------|---------------------------------------|------|-----------------|------|----|------------|

|                                  |                                       | MIN  | TYP             | MAX  |    |            |

| $V_{DD}$                         | Output Amplifier Drain Supply Voltage | 16.0 | 17.0            | 18.0 | ٧  |            |

| V <sub>RD (A+B)</sub>            | Output Reset Drain Supply Voltages    | 16.5 | 17.0            | 17.5 | V  |            |

| V <sub>SINK</sub>                | Anti-Blooming Sink Voltage            | 16.0 | 17.0            | 18.0 | ٧  |            |

| V <sub>OG (A+B)</sub>            | Output DC Gate Voltages               | 5.5  | 6.0             | 6.5  | V  |            |

| TP <sub>1</sub> ,TP <sub>2</sub> |                                       | 0.0  | 0.0             | 0.5  | ٧  |            |

| TP <sub>3</sub>                  |                                       | 16.0 | 17.0            | 18.0 | ٧  |            |

| V <sub>SG</sub>                  | Amplifier Signal Ground               | 0.0  | 0.0             | 0.5  | ٧  |            |

| V <sub>SS</sub>                  | Substrate Bias                        | -2.0 | -1.0            | -0.0 | ٧  | Note 2     |

| V <sub>SSN</sub>                 |                                       | 0.0  | V <sub>SG</sub> | 5.0  | ٧  | Note 14    |

| V <sub>SSP</sub>                 |                                       | -3.0 | -1.0            | 0.0  | ٧  |            |

| l <sub>DD</sub>                  | Output Amplifier Drain Supply Current | 6.0  | 10.0            | 15.0 | mA |            |

# CLOCK CHARACTERISTICS: Tp = 25° C

| SYMBOL                           | CHARACTERISTIC                 | RANGE |      |      | UNIT | CONDITIONS     |

|----------------------------------|--------------------------------|-------|------|------|------|----------------|

|                                  |                                | MIN   | TYP  | MAX  |      |                |

| V <sub>e</sub> x High            | Transfer Clock HIGH            | 14.5  | 15.0 | 15.5 | ٧    | Note 3         |

| Vø1 HIGH (A+B)<br>Vø2 HIGH (A+B) | Transport Clock HIGH           | 7.5   | 8.0  | 8.5  | ٧    | Note 3         |

| V <sub>PG</sub> HIGH (A+B)       | Photogate Clock HIGH           | 8.0   | 10.0 | 12.0 | ٧    | Note 3, 11     |

| V <sub>PPG</sub> LOW (A+B)       | Photogate Clock LOW            | 0.0   | 2.0  | 2.5  | ٧    | Note 3         |

| V <sub>Ø</sub> OG HIGH (A+B)     | Output Clock Gate HIGH         | 7.5   | 8.0  | 8.5  | ٧    | Note 3         |

| V <sub>PR</sub> HIGH (A+B)       | Reset Clock HIGH               | 14.5  | 15.0 | 15.5 | ٧    | Note 3         |

| V <sub>Ø</sub> IC HIGH           | Integration Control Clock HIGH | 14.5  | 15.0 | 15.5 | ٧    | Note 3         |

| V <sub>Ø</sub> IC LOW            | Integration Control Clock LOW  | 0.0   | 0.3  | 0.7  | ٧    | Notes 2, 3, 13 |

| V <sub>ØX LOW</sub>              | Transfer Clock LOW             | 0.0   | 0.3  | 0.7  | ٧    | Notes 2, 3     |

| V <sub>Ø1 LOW (A+B)</sub>        | Transport Clock LOW            | 0.0   | 0.3  | 0.7  | ٧    | Notes 2, 3     |

| V <sub>02</sub> LOW (A+B)        | Transport Clock LOW            | 0.0   | 0.3  | 0.7  | ٧    | Notes 2, 3     |

| VøR LOW (A+B)                    | Reset Clock LOW                | 0.0   | 0.3  | 0.7  | V    | Notes 2, 3     |

| V <sub>Ø</sub> OG LOW (A+B)      | Output Clock Gate LOW          | 0.0   | 0.3  | 0.7  | ٧    | Notes 2, 3     |

| f <sub>data</sub> max            | Maximum Output Data Rate       | 2.0   | 5.0  | 10.0 | MHz  |                |

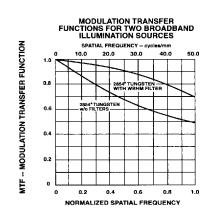

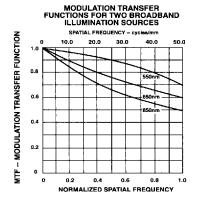

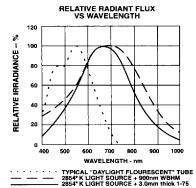

AC CHARACTERISTICS: Tp = 25° C (Note 1), fdata=2.0 MHz, tint=1ms, Light Source = 2854° K + 2.0mm thick Schott BG-38 and OCLI WBHM Filters (Note 4).

| SYMBOL | CHARACTERISTIC                                                     | RANGE  |                        |      | UNIT     | CONDITIONS |

|--------|--------------------------------------------------------------------|--------|------------------------|------|----------|------------|

|        |                                                                    | MIN    | TYP                    | MAX  |          |            |

| DR     | Dynamic Range Relative to peak-to-peak noise Relative to rms noise |        | 2000:1<br>11000:1      |      |          |            |

| NEE    | RMS Noise<br>Equivalent exposure                                   |        | 3.0 x 10 <sup>-6</sup> |      | μJ/cm²   |            |

| CTE    | Charge Transfer Efficiency                                         | .99999 | .99999                 |      |          | Note 6     |

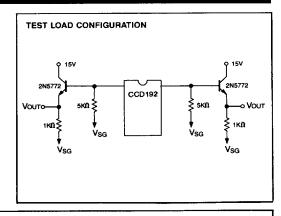

| Vo     | Output DC Level                                                    | 6.0    | 8.0                    | 12.0 | V        |            |

| z      | Output Impedance                                                   |        | 1                      |      | kΩ       |            |

| P<br>N | On-Chip Amplifier Power Dissipation<br>Peak-to-Peak Temporal Noise |        | 150<br>1.0             | 300  | mW<br>mV |            |

Tp = 25° C (Note 1),  $f_{data}$ =2.0 MHz,  $t_{int}$ =1 ms, Light Source = 2854° K + 2.0 mm thick PERFORMANCE CHARACTERISTICS: Schott BG-38 and OCLI WBHM Filters (Note 4).

| SYMBOL           | CHARACTERISTIC                                                              | RANGE |          |            | UNIT     | CONDITIONS  |

|------------------|-----------------------------------------------------------------------------|-------|----------|------------|----------|-------------|

|                  |                                                                             | MIN   | TYP      | MAX        |          |             |

| PRNU*            | Photoresponse Non-uniformity Peak-to-peak Peak-to-peak Positive or Impulses |       | 90<br>55 | 240<br>110 | mV<br>mV |             |

| M Video          | Video Mismatch                                                              |       | 75       | 225        | m∨       | Note 7      |

| M DC             | DC Mismatch                                                                 |       | 0.5      | 2.0        | ٧        | Note 8      |

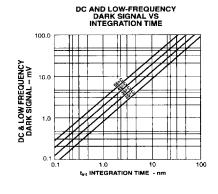

| DS               | Dark Signal DC Component Low Frequency Component                            |       | 5<br>5   | 15<br>15   | mV<br>mV | Notes 9, 10 |

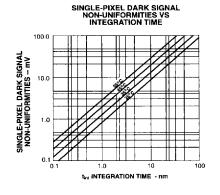

| SPDSNU           | Single Pixel DS Non-Uniformity                                              |       | 5        | 15         | mV       | Note 10     |

| R                | Responsivity                                                                | 2.5   | 5.0      | 9.0        | V/µJcm²  |             |

| V <sub>SAT</sub> | Saturation Output Voltage                                                   | 1.5   | 2.5      | 4.5        | ٧        |             |

\* All PRNU measurements are taken at approximately 80% of V<sub>SAT</sub> using an f/5.0 lens and exclude the outputs from the first and last elements of the array. The "f" number is defined as the distance from the lens to the array divided by the diameter of the lens aperture. As the "f" number increases, the resulting more highly collimated light causes the package window imperfections to dominate and increase PRNU. A lower "f" number results in less collimated light causing device photosite blemishes to dominate the PRNU. The above characteristics are based on a 1200mV output (approximately 80% of the minimum V<sub>SAT</sub>).

#### NOTES:

- 1. To is defined as the package temperature measured on a copper block in good thermal contact with the entire backside of the device

- Negative transients on any clock pin going below 0.0 volts may cause charge injection, which results in an increase in apparent DS. Adjusting V<sub>SSN</sub> to a more negative voltage than the clock low voltages will reduce charge injection, if present.

Cφχα = Cφχα = Cφια = Cφια = Cφια = Cφια = Cφη = Cφη

- 5. The minimum clock frequency is limited by increases in dark signal.

- CTE is the measurement for a one-stage transfer.

- 7. Video mismatch is the difference in AC amplitudes between V<sub>OUT</sub> A and V<sub>OUT</sub> B under uniform illumination. It can be eliminated by attenuation/ amplification of one of the video inputs.

- 8. DC mismatch is the difference in DC output level Vo) between Vout A and Vout B.

- Dark signal component approximately doubles for every 5° to 15° increase in T 10. Each SPDSNU is measured from the DS level adjacent to the base of the SPDSNU. The SPDSNU approximately doubles for every 5° to 15° increase

- in Tp.

11. The HIGH level of the Photogate Clock can actually be as high as 18V. However, increasing the high level of this clock may also increase the photosite

- 12. Metal back plate electrically tied to VSSN.

- 13. See "Anti-Blooming" and "Integration Control" under "Functional Description" for additional information; also see Application Note.

- 14. V<sub>SSN</sub> is normally tied to V<sub>SG</sub>.

## **TYPICAL PERFORMANCE CURVES**

#### **DEVICE CARE AND OPERATION**

Glass may be cleaned by saturating a cotton swab in alcohol and lightly wiping the surface. Rinse off the alcohol with de-ionized water. Allow the glass to dry preferably by blowing with filtered dry  $N_2$  or air.

It is important to note in design and applications considerations that the devices are very sensitive to thermal conditions. The dark signal DC and low frequency components approximately double for every 5° C temperature increase and single-pixel dark signal non-uniformities approximately double for every 12° C temperature increase. The devices may be cooled to achieve very long integration times and very low light level capability.

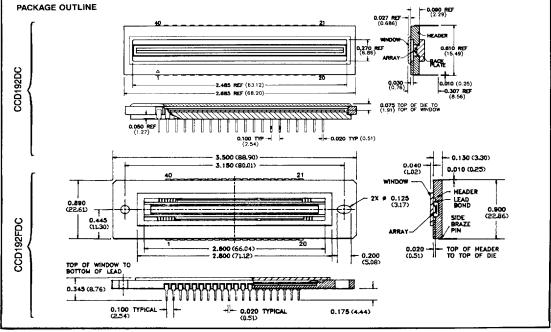

#### ORDER INFORMATION

Order CCD192FDC where "F" stands for special flatness, "D" stands for ceramic package and "C" stands for commercial temperature range. Order CCD192DC for the standard package.

Loral Fairchild cannot assume responsibility for use of any circuitry described other than circuitry embodied in a Loral Fairchild product. No other circuit patent licenses are implied.

5579818 0001348 785

132