# Preliminary Data Sheet July 1995

# DSP1605 Digital Signal Processor

# **1** Features

- For 5 V operation:

- 25 ns instruction cycle time (40 MIPS)

30 ns instruction cycle time (33 MIPS)

- For 3.3 V operation:

31.25 ns instruction cycle time (32 MIPS)

- Power-savings features:

Low-power 0.6 μm CMOS technology; fully static

- design — Active power: 9.5 mW/MIPS at 5.0 V

- 3.8 mW/MIPS at 3.3 V

- Low-power standby: 3.0 mW at 5.0 V

- 0.4 mW at 3.3 V

- 16 Kwords internal ROM

- 1 Kword internal RAM

- 16 x 16-bit multiplication and 36-bit accumulation in one instruction cycle

- Two 36-bit accumulators

- Instruction cache for high-speed, program-efficient, zero-overhead looping

- One external vectored interrupt

- Two 64 Kword address spaces with software waitstates for external accesses

- Single- or dual-channel 20 Mbits/s serial I/O port;

8-bit, 16-bit, 32-bit, and 48-bit data channel

- One 8-bit I/O port for flexible status or control pins

- External DRAM interface

- Two interrupt timers

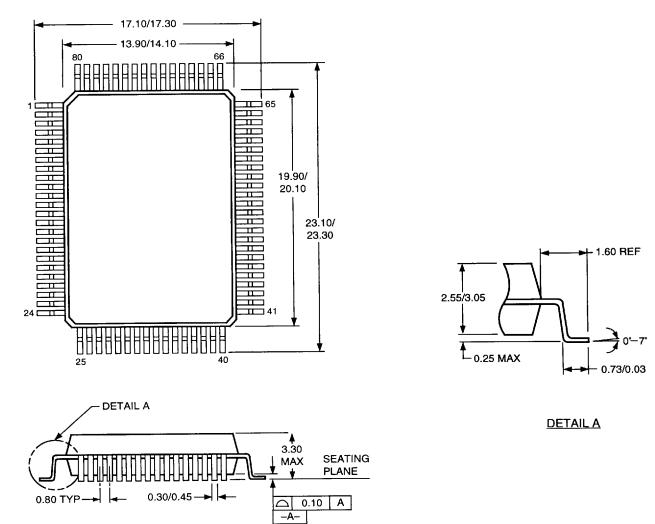

- 68-pin PLCC or 80-pin MQFP package

- High- and low-frequency clock inputs

- Parallel host interface for rapid transfer of data with external devices

- Internal power-loss detection unit

- Object code upward compatible with DSP1600 Digital Signal Processor family

- Supported by DSP160X-ST Support Tools

- Full-speed in-circuit emulation HDS (HD-supported) Flash ROM device

# **2 Description**

The DSP1605 is a 16-bit fixed-point digital signal processor (DSP) based on the DSP1600 core. It is programmable to perform a wide variety of fixed-point signal processing functions. A member of the DSP160X family, the DSP1605 includes a mix of peripherals specifically intended to support processing-intensive but cost-sensitive applications. In addition to the core, the DSP1605 consists of the following peripheral blocks: external memory interface unit (EMI), serial I/O unit (SIO), an 8-bit I/O port (IOP), two timer units, a parallel host interface (PHIF), and a JTAG interface; as well as one Kword of RAM and 16 Kwords of ROM. The DSP1605 is part of a low-cost, high-performance solution for consumer product applications.

The DSP1605 is available in the following packages:

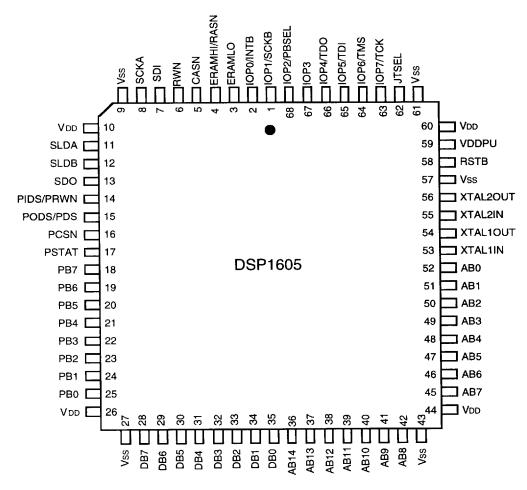

- 68-pin PLCC (See Figure 1 on page 9.)

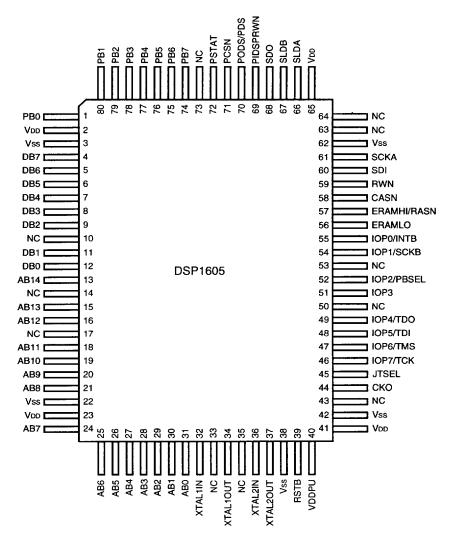

- 80-pin MQFP (See Figure 2 on page 10.)

The DSP achieves high throughput without programming restrictions or latencies due to its parallel pipelined architecture. The processor has an arithmetic unit capable of a 16 x 16 multiplication and 36-bit accumulation, or a 32-bit ALU operation in one instruction cycle. Data is accessed from memory via two independent addressing units.

A fully static, low-power,  $0.6 \,\mu m$  CMOS design and a low-power standby mode support power-sensitive equipment applications. Two sets of pins allow the use of high-frequency and low-frequency clocks. Under program control, the DSP1605 can be switched between the high-frequency and low-frequency clock inputs. When switched to the low-frequency clock, the power is reduced.

The *FlashDSP*  $^{\text{TM}}$  device is the development platform for the DSP1605. To support full-speed in-circuit emulation, the *FlashDSP* device includes an internal HDS module.

🔲 0050026 0016535 050 📟

# **Table of Contents**

| Contents Pa                        | age  |

|------------------------------------|------|

| 1 Features                         | . 1  |

| 2 Description.                     | . 1  |

| 3 Pin Information                  |      |

| 3.1 System Interface               | 14   |

| 3.1.1 XTAL1IN, XTAL1OUT            | 14   |

| 3.1.2 XTAL2IN, XTAL2OUT            | 14   |

| 3.1.3 CKO                          | 14   |

| 3.1.4 RSTB                         | 14   |

| 3.1.5 INTB                         | 14   |

| 3.1.6 VDDPU                        | 14   |

| 3.2 External Memory Interface      | 15   |

| 3.2.1 AB[14:0]                     | 15   |

| 3.2.2 DB[7:0]                      | 15   |

| 3.2.3 ERAMLO                       | 15   |

| 3.2.4 ERAMHI/RASN                  | 15   |

| 3.2.5 CASN                         | 15   |

| 3.2.6 RWN                          | 15   |

| 3.3 Serial Interface (SIO)         | 15   |

| 3.3.1 SDI in Single-Channel Mode   | 15   |

| 3.3.2 SDI in Dual-Channel Mode     | 15   |

| 3.3.3 SCKB Multiplexed             | 15   |

| 3.3.4 SCKB in Single-Channel Mode  | 15   |

| 3.3.5 SCKB in Dual-Channel Mode    | 15   |

| 3.3.6 SLDB in Single-Channel Mode  | 16   |

| 3.3.7 SLDB in Dual-Channel Mode    | 16   |

| 3.3.8 SDO in Single-Channel Mode   | . 16 |

| 3.3.9 SDO in Dual-Channel Mode     | 16   |

| 3.3.10 SCKA in Single-Channel Mode | 16   |

| 3.3.11 SCKA in Dual-Channel Mode   | . 16 |

| 3.3.12 SLDA in Single-Channel Mode | . 16 |

| 3.3.13 SLDA in Dual-Channel Mode   | . 16 |

| 3.4 I/O Port (IOP[7:0])            | . 16 |

| 3.5 PHIF                           | . 17 |

| 3.5.1 PCSN                         | . 17 |

| 3.5.2 PODS/PDS                     | . 17 |

| 3.5.3 PIDS/PRWN                    | . 17 |

| 3.5.4 PSTAT                        |      |

| 3.5.5 PBSEL                        | . 17 |

| 3.5.6 PB[7:0]                      | . 17 |

| 3.6 JTAG Test Mode Interface       | . 18 |

| 3.6.1 JTSEL                        | . 18 |

| 3.6.2 TCK                          | . 18 |

| 3.6.3 TMS.                         | . 18 |

| 3.6.4 TDI                          | . 18 |

| 3.6.5 TDO.                         | . 18 |

| 3.7 PWB/GND                        | . 18 |

| 3.7.1 Vss                          | . 18 |

| 3.7.2 VDD                          | . 18 |

**AT&T Microelectronics**

#### 🗰 0050026 0016536 T97 酬

2

\_

# Table of Contents (continued)

| Contents                                         | Page |

|--------------------------------------------------|------|

| 4 Hardware Architecture                          | 19   |

| 4.1 DSP1605 Architectural Overview.              |      |

| 4.1.1 DSP1600 Core                               |      |

| 4.1.2 Dual-Port RAM (DPRAM)                      | 22   |

| 4.1.3 Read-Only Memory (ROM)                     |      |

| 4.1.4 External Memory Interface (EMI)            | 22   |

| 4.1.5 Timers                                     |      |

| 4.1.6 Input/Output Port (IOP)                    | 22   |

| 4.1.7 JTAG                                       |      |

| 4.1.8 Serial Input/Output Unit (SIO)             |      |

| 4.1.9 Power-Loss Detect Circuit                  |      |

| 4.1.10 Oscillator and Clock Control.             |      |

| 4.1.11 Parallel Host Interface (PHIF)            |      |

| 4.2 DSP1600 Core Architectural Overview          |      |

| 4.2.1 System Cache and Control Section (SYS)     |      |

| 4.2.2 Data Arithmetic Unit (DAU)                 |      |

| 4.2.3 Y Space Address Arithmetic Unit (YAAU).    |      |

| 4.2.4 X Space Address Arithmetic Unit (XAAU)     |      |

| 4.3 Interrupts, Trap, and Low-Power Standby Mode |      |

| 4.3.1 Interruptibility                           |      |

| 4.3.2 Vectored Interrupts.                       |      |

| 4.3.3 External Interrupt Pin (INTB)              |      |

| 4.3.4 Clearing Interrupts                        |      |

| 4.3.5 Low-Power Standby Mode (AWAIT)             |      |

| 4.4 Memory Maps and Wait-States                  |      |

| 4.4.2 Data Memory Map Selection                  |      |

| 4.4.2 Data Memory Map Selection                  |      |

| 4.5.1 Memory Segment Enables                     |      |

| 4.5.2 DRAM Support.                              |      |

| 4.6 Serial I/O Unit (SIO)                        |      |

| 4.6.1 Single-Channel SIO                         |      |

| 4.6.2 Dual-Channel SIO                           |      |

| 4.7 I/O Port (IOP)                               |      |

| 4.8 Timers                                       |      |

| 4.9 Parallel Host Interface (PHIF)               | 39   |

| 5 Software Architecture                          |      |

| 5.1 Instruction Set                              | 41   |

| 5.1.1 F1 Multiply/ALU Instructions               | 42   |

| 5.1.2 F2 Special Function Instructions           | 44   |

| 5.1.3 Control Instructions                       |      |

| 5.1.4 Conditional Mnemonics (Flags)              | 46   |

| 5.1.5 F3 ALU Instructions                        |      |

| 5.1.6 Cache Instructions                         |      |

| 5.1.7 Data Move Instructions                     |      |

| 5.2 Register Settings                            |      |

| 5.3 Reset States                                 | 62   |

**AT&T** Microelectronics

📟 0050026 0016537 923 📟

# Table of Contents (continued)

## Contents

## Page

\_ - \_

| 5.4 Instruction Set Formats                                                      | 60    |

|----------------------------------------------------------------------------------|-------|

| 5.4.1 Multiply/ALU Instructions.                                                 |       |

| 5.4.2 Special Function Instructions                                              |       |

| 5.4.2 Special Function Instructions                                              | 63    |

| 5.4.4 Data Move Instructions                                                     |       |

| 5.4.5 Cache Instructions                                                         |       |

| 5.4.6 Field Descriptions                                                         | . 65  |

| 6 Device Requirements and Characteristics                                        | . 69  |

| 6.1 Absolute Maximum Ratings.                                                    | . 69  |

| 6.2 Handling Precautions                                                         | . 69  |

| 6.3 Recommended Operating Conditions                                             |       |

| 6.4 Decoupling Requirements.                                                     |       |

| 6.5 Package Thermal Considerations                                               |       |

| 7 Electrical Requirements and Characteristics.                                   |       |

| 7.1 Typical Power Dissipation                                                    |       |

| 7.2 Input and I/O Buffer Power Dissipation                                       | 74    |

| 8 Timing Requirements and Characteristics.                                       | 75    |

| 8.1 Input Clock Options                                                          | 75    |

| 8.2 DSP Clock Generation                                                         | 76    |

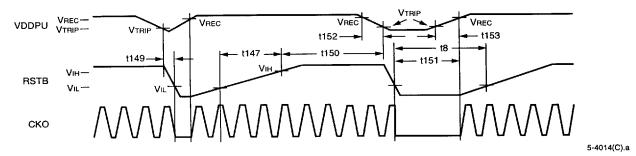

| 8.3 Powerup Reset (Assuming VDDPU Is Disabled)                                   |       |

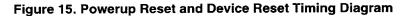

| 8.4 Reset Synchronization                                                        |       |

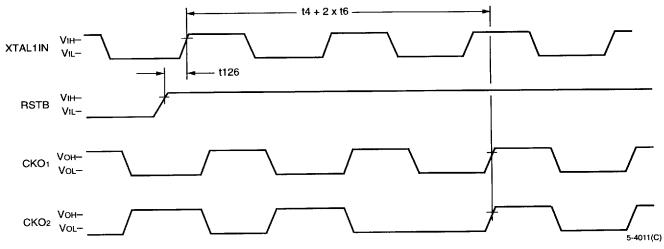

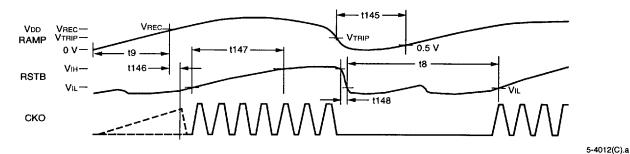

| 8.5 Powerup and Power-Loss Detect Circuit Reset                                  | 79    |

| 8.5.1 Powerup Reset Specifications (VDDPU Connected to VDD)                      |       |

| 8.5.2 Power-Loss Detect Specifications (VDDPU Not Connected to VDD)              | 81    |

| 8.6 JTAG I/O Specifications                                                      | 83    |

| 8.7 Interrupt                                                                    | 84    |

| 8.8 Input/Output Ports (IOP)                                                     | 85    |

| 8.9 External Memory Interface                                                    | 86    |

| 8.10 External DRAM Interface                                                     | 91    |

| 8.11 Serial I/O Specifications                                                   | 97    |

| 8.12 PHIF Specifications                                                         | . 102 |

| 9 Crystal Oscillator Electrical Requirements and Characteristics.                | . 108 |

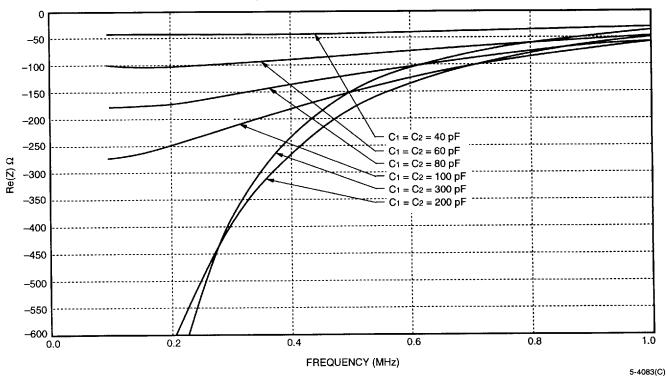

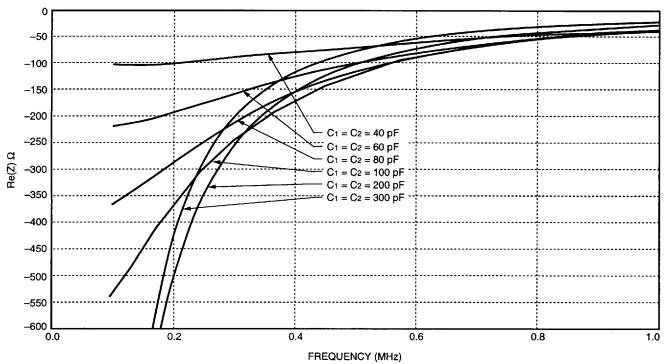

| 9.1 High-Frequency Crystal Oscillator.                                           | . 108 |

| 9.1.1 High-Frequency Crystal Oscillator Power Dissipation.                       | . 108 |

| 9.1.2 High-Frequency Crystal Oscillator External Components.                     | . 108 |

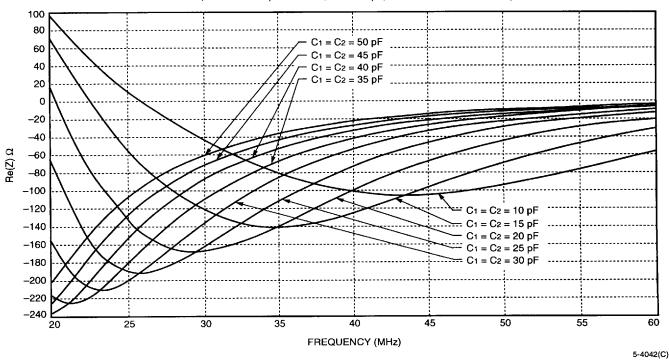

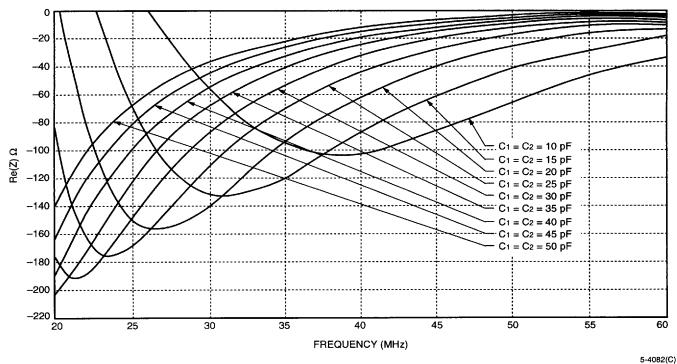

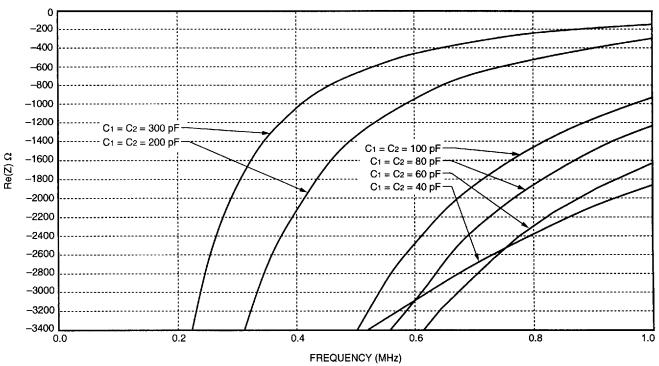

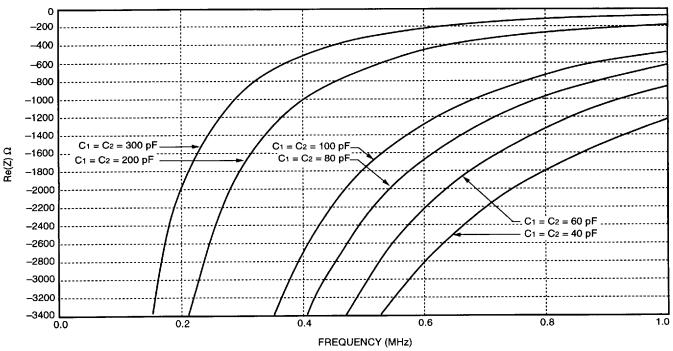

| 9.1.3 High-Frequency Crystal Oscillator Negative Resistance Curves               | . 109 |

| 9.1.4 LC Network Design for Third Overtone Crystal Circuits                      | 111   |

| 9.2 Low-Frequency Crystal Oscillator or Resonator                                | . 112 |

| 9.2.1 Low-Frequency Crystal Oscillator or Resonator Power Dissipation            | 112   |

| 9.2.2 External Components for the Low-Frequency Crystal Oscillator or Resonator. | 112   |

| 9.2.3 Low-Frequency Crystal Oscillator Negative Resistance Curves.               | 113   |

| 9.2.4 Low-Frequency Crystal Resonator Negative Resistance Curves                 | 115   |

| 9.3 Frequency Accuracy Considerations                                            | . 117 |

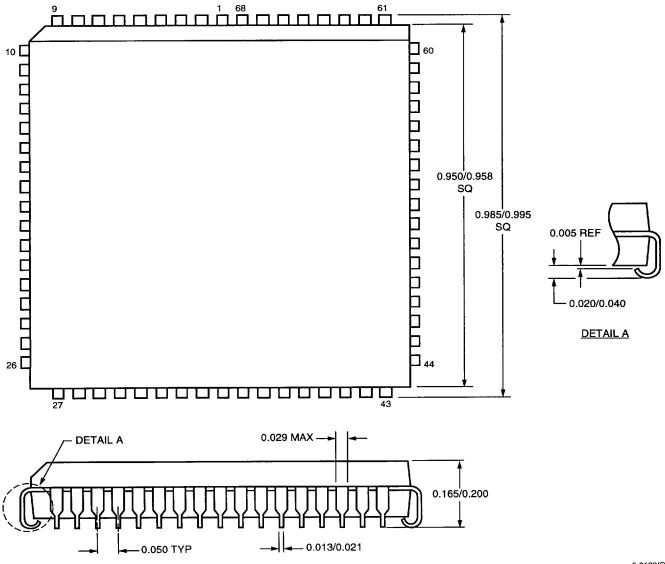

| 10 Outline Diagrams                                                              | . 120 |

| 10.1 68-Pin PLCC Outline Diagram                                                 |       |

| 10.2 80-Pin MQFP Outline Diagram                                                 |       |

| 11 Ordering Information                                                          | . 122 |

| 11.1 Device Coding                                                               |       |

| 11.2 Mask-Programmable Options                                                   | . 122 |

**AT&T Microelectronics**

#### 🛲 0050026 0016538 86T 📰

-----

\_\_\_\_

.

# List of Figures

## Page

|                                                                                           | Ŭ    |         |

|-------------------------------------------------------------------------------------------|------|---------|

| Figure 1. DSP1605 68-Pin PLCC Pin Diagram                                                 |      | Э       |

| Figure 2. DSP1605 80-Pin MQFP Diagram.                                                    |      |         |

| Figure 3. DSP1605 Pinout by Group                                                         |      |         |

| Figure 4. DSP1605 Block Diagram                                                           |      |         |

| Figure 5. DSP1600 Core Block Diagram.                                                     |      |         |

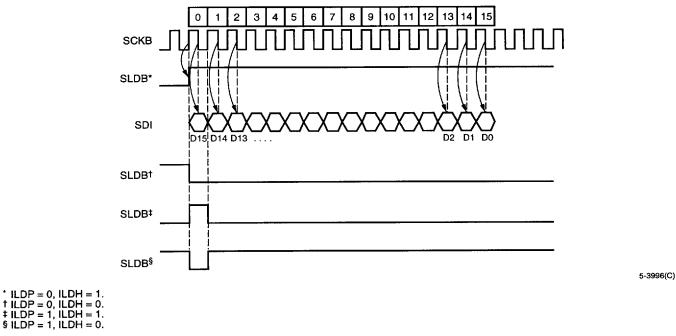

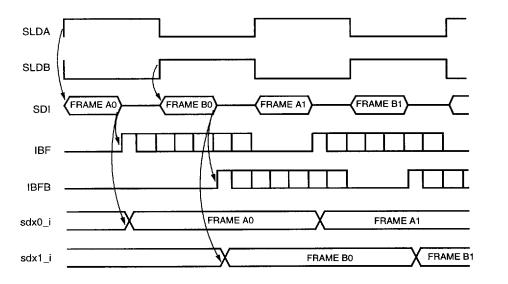

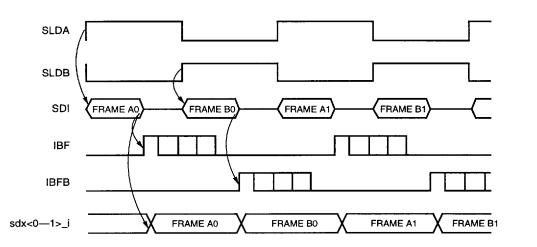

| Figure 6. Serial Input with Delayed Active Load (LDD = 1)                                 |      |         |

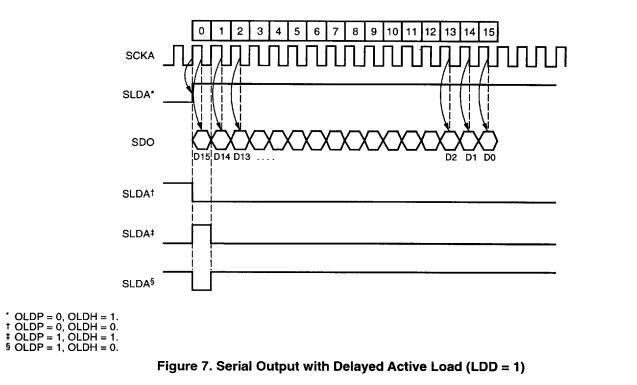

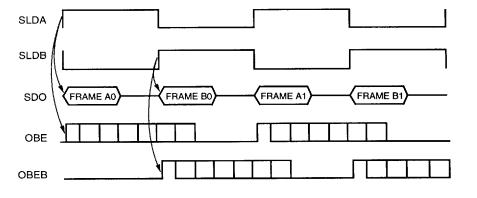

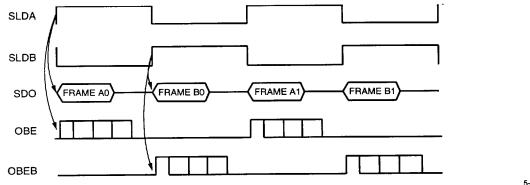

| Figure 7. Serial Output with Delayed Active Load (LDD = 1)                                |      |         |

| Figure 8. Dual-Channel SIO 8-Bit or 16-Bit Data Input                                     |      |         |

| Figure 9. Dual-Channel SIO 8-Bit or 16-Bit Data Output                                    |      |         |

| Figure 11. Dual-Channel SIO 32-Bit or 48-Bit Data Output (Load Offset Selected (D50 = 1)) |      |         |

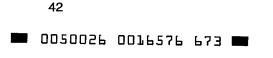

| Figure 12. Plot of Von vs. Ion Under Typical Operating Conditions.                        |      |         |

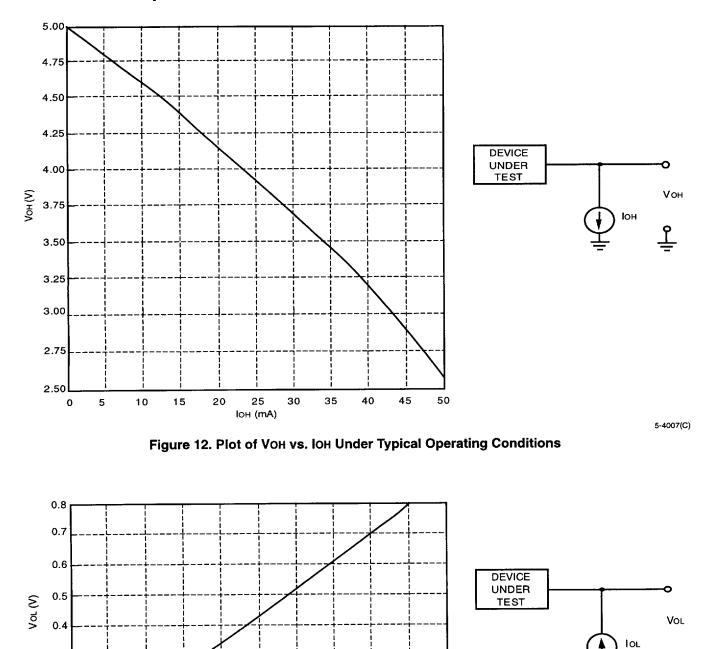

| Figure 13. Plot of Vol. vs. loL Under Typical Operating Conditions                        |      |         |

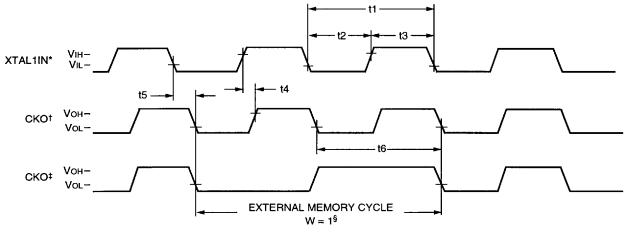

| Figure 14. I/O Clock Timing Diagram                                                       |      |         |

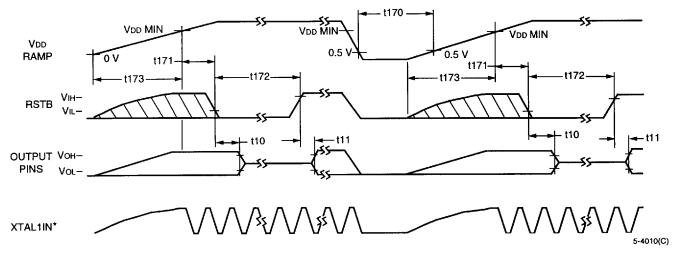

| Figure 15. Powerup Reset and Device Reset Timing Diagram.                                 |      |         |

| Figure 16. Reset Synchronization Timing                                                   |      |         |

| Figure 17. Powerup Reset.                                                                 |      |         |

| Figure 18. Example of Power-Loss Detect External Component Configuration                  | . 8  | 1       |

| Figure 19. Power-Loss Detect Reset.                                                       |      |         |

| Figure 20. JTAG Timing Diagram                                                            |      |         |

| Figure 21. Interrupt Timing Diagram                                                       |      |         |

| Figure 22. Write Outputs Followed by Read Inputs (cbit = Immediate; a1 = sbit)            | . 8  | 5       |

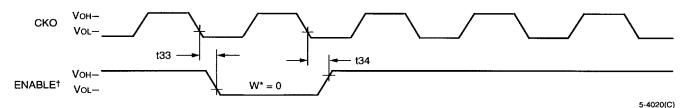

| Figure 23. Enable Transition Timing                                                       | . 8  | 6       |

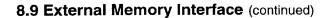

| Figure 24. External Memory Data Read Timing Diagram                                       | . 8  | 7       |

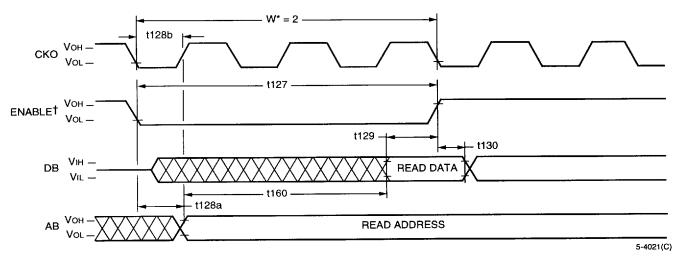

| Figure 25. External Memory Data Write, Read Timing Diagram                                | . 8  | 8       |

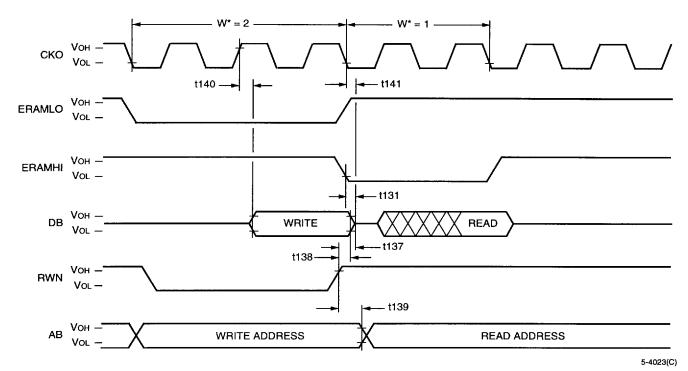

| Figure 26. Write Cycle Followed by Read Cycle                                             | . 9  | 0       |

| Figure 27. Read Cycle Timing (Relative) Diagram                                           |      |         |

| Figure 28. Early Write Cycle Timing (Relative) Diagram                                    | . 9  | 3       |

| Figure 29. Synchronous Delay DRAM Interface Timing Diagram                                |      |         |

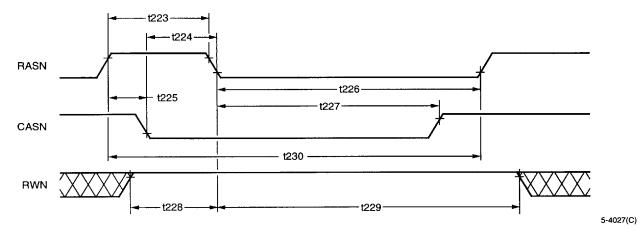

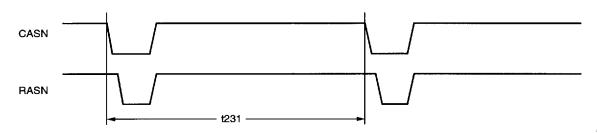

| Figure 30. CASN Before RASN Refresh Cycle Timing Diagram                                  |      |         |

| Figure 31. Refresh Interval Timing with XTAL1 Clocking                                    |      |         |

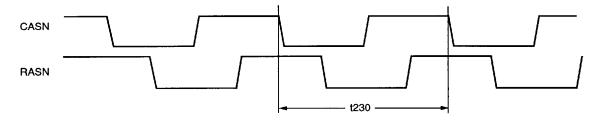

| Figure 32. Refresh Interval Timing with XTAL2 Clocking                                    | . 9  | 6       |

| Figure 33. SIO Active Output Timing Diagram                                               | . 9  | 7       |

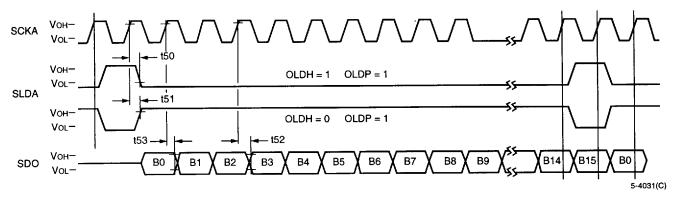

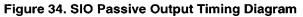

| Figure 34. SIO Passive Output Timing Diagram                                              |      |         |

| Figure 35. SIO Active Input Timing Diagram                                                |      |         |

| Figure 36. SIO Passive Input Timing Diagram                                               |      |         |

| Figure 37. Serial I/O Active Clocks Timing Diagram                                        | 10   | 1<br>12 |

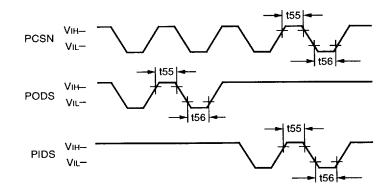

| Figure 39. PHIF Intel Mode Signaling Pulse Period Timing Diagram                          | 10   | 2       |

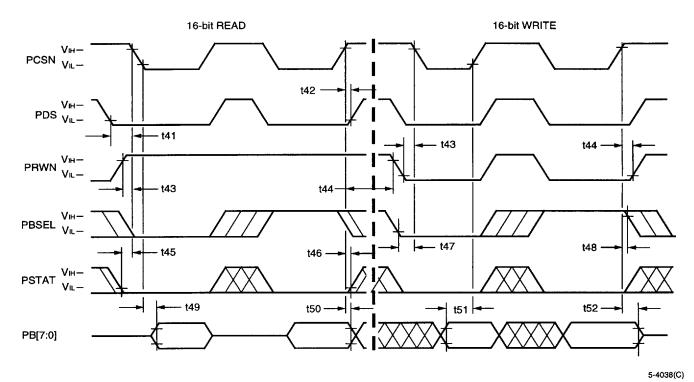

| Figure 40. PHIF <i>Motorola</i> Mode Signaling (Read and Write) Timing Diagram            |      |         |

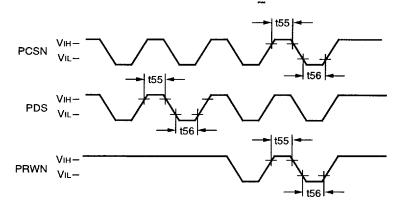

| Figure 40. PHIL Motorola Mode Signaling Pulse Period Timing Diagram.                      |      |         |

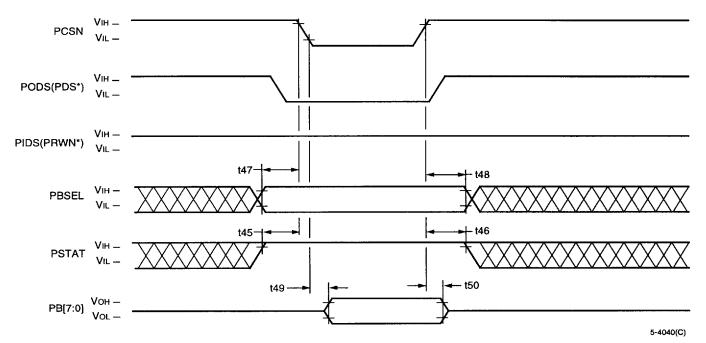

| Figure 42. PHIF Intel or Motorola Mode Signaling (Status Register Read) Timing Diagram    |      |         |

| Figure 43. Fundamental Crystal Configuration                                              | 10   | .8      |

| Figure 44. 5 V High-Frequency Crystal Oscillator Negative Resistance Curves.              | 10   | 9       |

| Figure 45. 3.3 V High-Frequency Crystal Oscillator Negative Resistance Curves             |      |         |

| Figure 46. Third Overtone Crystal Configuration.                                          |      |         |

| Figure 47. Fundamental Crystal/Resonator Configuration                                    | . 11 | 2       |

| Figure 48. 5 V Low-Frequency Crystal Oscillator Negative Resistance Curves                |      |         |

| Figure 49. 3.3 V Low-Frequency Crystal Oscillator Negative Resistance Curves.             |      |         |

| Figure 50. 5 V Low-Frequency Crystal Resonator Negative Resistance Curves                 | . 11 | 5       |

| Figure 51, 3.3 V Low-Frequency Crystal Resonator Negative Resistance Curves               | . 11 | 6       |

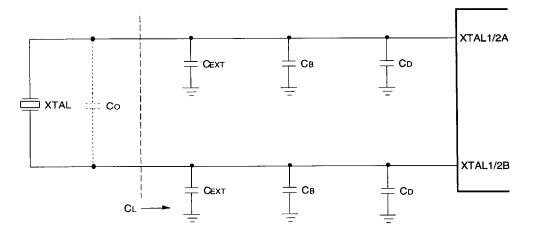

| Figure 52. Components of Load Capacitance for Crystal Oscillator                          | . 11 | 7       |

|                                                                                           |      |         |

**AT&T** Microelectronics

🔲 0050026 0016539 7T6 🔜

# **List of Tables**

# Page

| Table 1. DSP1605 Pinout.         1                                       |    |

|--------------------------------------------------------------------------|----|

| Table 2. DSP1605 Power Supply, Ground, and Unconnected Pins.       1     |    |

| Table 3. DSP1605 Block Diagram Legend.    2                              |    |

| Table 4. CKO Pin Output Functions    2                                   | :3 |

| Table 5. DSP1600 Core Block Diagram Legend    2                          |    |

| Table 6. Interrupt Vectors.   2                                          |    |

| Table 7. DSP1605 Instruction/Coefficient Memory Map.         2           |    |

| Table 8. DSP1605 Data Memory Map         2                               |    |

| Table 9. Pin Functions in Single-Channel Mode    3                       |    |

| Table 10. Pin Functions in Dual-Channel Mode.    3                       |    |

| Table 11. IOP Operations.   3                                            | 8  |

| Table 12. PHIF Function (8-Bit and 16-Bit Modes).    3                   |    |

| Table 13. Instruction Set Operators    4                                 |    |

| Table 14. F1 Multiply/ALU Instructions.    4                             |    |

| Table 15. Replacement Table for F1 Multiply/ALU Instructions         4   |    |

| Table 16. F2 Special Function Instructions    4                          |    |

| Table 17. Replacement Table for F2 Special Function Instructions       4 |    |

| Table 18. Control Instructions.    4                                     |    |

| Table 19. Replacement Table for Control Instructions         4           |    |

| Table 20. DSP1605 Conditional Mnemonics       4                          |    |

| Table 21. F3 ALU Instructions    4                                       |    |

| Table 22. Replacement Table for F3 ALU Instructions.         4           |    |

| Table 23. Cache Instructions    4                                        |    |

| Table 24. Replacement Table for Cache Instructions         4             |    |

| Table 25. Data Move Instructions.    4                                   |    |

| Table 26. Replacement Table for Data Move Instructions       4           | 19 |

| Table 27. alf (Standby and Memory Map) Register    5                     |    |

| Table 28. auc (Arithmetic Unit Control) Register 5                       | 50 |

| Table 29. cbit (IOP Control Bit) and sbit (IOP Status Bit) Registers     | j1 |

| Table 30. drc (DRAM Control) Register 5                                  |    |

| Table 31. inc (Interrupt Control) Register 5                             |    |

| Table 32. ins (Interrupt Status) Register 5                              | 53 |

| Table 33. ioc (I/O Configuration) Register 5                             | 54 |

| Table 34. JTAG ID Register (32-Bit)                                      |    |

| Table 35. JTAG ROMCODE Letter Values                                     | 55 |

| Table 36. mwait (External Memory Wait-States Control) Register           | 55 |

| Table 37. phifc (Parallel Host Interface Control) Register 5             | ;6 |

| Table 38. phifc Register PHIF Function (8-Bit and 16-Bit Modes) 5        | 56 |

| Table 39. pgreg (Page) Register                                          | 57 |

| Table 40. PSTAT (PHIF Status) Register 5                                 | 57 |

| Table 41. psw (Processor Status Word) Register 5                         | 57 |

| Table 42. sbit (IOP Status Bit) and cbit (IOP Control Bit) Registers     | 58 |

| Table 43. sioc (Serial I/O Control) Register    5                        | 59 |

|                                                                          | 50 |

| Table 45. timerc (Timer Control) Register 6                              | 31 |

| Table 46. timerc Register PRESCALE Field 6                               |    |

| Table 47. Register States After Reset    6                               | 32 |

| Table 48. Format 1: Multiply/ALU Read/Write Group                        | 33 |

| Table 49. Format 1a: Multiply ALU Read/Write Group                       | 33 |

| Table 50. Format 2: Multiply/ALU Read/Write Group                        |    |

| Table 51. Format 2a: Multiply/ALU Read/Write Group6                      |    |

|                                                                          |    |

6

AT&T Microelectronics

#### 🔲 0050026 0016540 418 🖿

- ---

# List of Tables (continued)

## Page

|                                                                                                                                                       | -          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Table 52. Format 3: F2 ALU Special Functions.                                                                                                         | 63         |

| Table 53. Format 3a: F3 ALU Operations                                                                                                                | 63         |

| Table 54. Format 4: Branch Direct Group                                                                                                               | 63         |

| Table 55. Format 5: Branch Indirect Group                                                                                                             | 64         |

| Table 56. Format 6: Conditional Branch Qualifier                                                                                                      | 64         |

| Table 57. Format 7: Data Move Group                                                                                                                   | 64         |

| Table 58. Format 8: Data Move (16-Bit Immediate Operand—2 Words)                                                                                      | 64         |

| Table 59. Format 9: Short Immediate Group.                                                                                                            | 64         |

| Table 60. Format 9a: Direct Addressing                                                                                                                | 64         |

| Table 61. Format 10: Do/Redo                                                                                                                          | 64         |

| Table 62. T Field                                                                                                                                     | 65         |

| Table 63. aT Field                                                                                                                                    | 65         |

| Table 64. B Field                                                                                                                                     | 65         |

| Table 65. CON Field                                                                                                                                   | 65         |

| Table 66. D Field                                                                                                                                     | 65         |

| Table 67. DR Field.                                                                                                                                   | 66         |

| Table 68. F1 Field                                                                                                                                    |            |

| Table 69. F2 Field                                                                                                                                    | 66         |

| Table 70. F3 Field                                                                                                                                    | 66         |

| Table 70. I Stried                                                                                                                                    | 66         |

| Table 72. R Field.                                                                                                                                    | . 67       |

| Table 73. S Field                                                                                                                                     | . 67       |

| Table 74. SI Field                                                                                                                                    | 67         |

| Table 75. SRC2 Field                                                                                                                                  | . 67       |

| Table 76. X Field                                                                                                                                     |            |

| Table 77. Y Field                                                                                                                                     | 68         |

| Table 78. Z Field                                                                                                                                     | 68         |

| Table 78. 2 Field       Table 79. Maximum Package Rating Parameters and Values                                                                        | 69         |

| Table 80. Recommended Voltage and Temperature                                                                                                         | 70         |

| Table 80. Recommended voltage and remperature         Table 81. Electrical Requirements.                                                              | 71         |

| Table 81. Electrical Requirements.         Table 82. Electrical Characteristics                                                                       | 71         |

| Table 82. Electrical Characteristics       Table 83. Electrical Requirements for Clocks                                                               | 73         |

| Table 83. Electrical Requirements for Clocks                                                                                                          | 71         |

| Table 84. Internal Power Dissipation.                                                                                                                 | . 74<br>74 |

| Table 85. Input Buffer Maximum Power Dissipation                                                                                                      | - 74<br>7/ |

| Table 86. Schmitt Trigger Input Buffer Maximum Power Dissipation                                                                                      | . /4       |

| Table 87. Test Conditions                                                                                                                             | . 75       |

| Table 88. Timing Requirements for Input Clock                                                                                                         | . 70       |

| Table 89. Timing Requirements for Input Clock and Output Clock                                                                                        | . 70       |

| Table 90. Timing Requirements for Powerup Reset and Device Reset                                                                                      | . 70       |

| Table 91. Timing Characteristics for Powerup Reset and Device Reset.                                                                                  | . 70       |

| Table 92. Timing Requirements and Characteristics for Reset Synchronization Timing.                                                                   | . /9       |

| Table 93. Timing Requirements for Powerup Reset with VDDPU Enabled                                                                                    | . 00       |

| Table 94. Timing Characteristics for Powerup Reset with VDDPU Enabled.                                                                                | . 00       |

| Table 95. Power-Loss Detect Voltage Levels                                                                                                            | . 01       |

| Table 96. Timing Requirements for Powerup Reset with VDDPU Enabled                                                                                    | . 02       |

| Table 97. Timing Characteristics for Powerup Reset with VDDPU Enabled.         Table 97. Timing Characteristics for Powerup Reset with VDDPU Enabled. | . 02       |

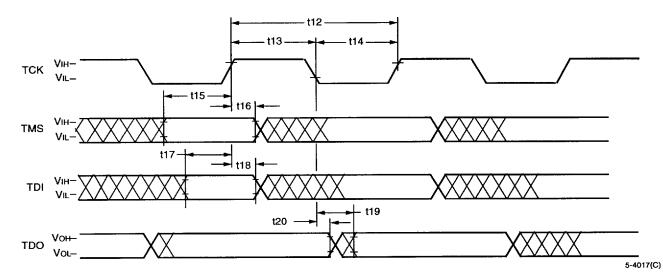

| Table 98. Timing Requirements for JTAG Input/Output                                                                                                   | . 03       |

| Table 99. Timing Characteristics for JTAG Input/Output.                                                                                               | . 03       |

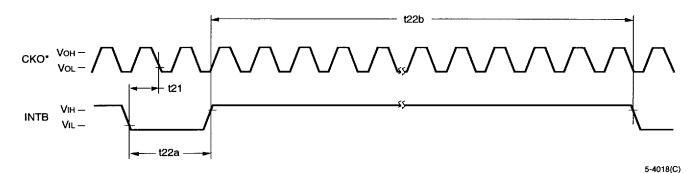

| Table 100. Timing Requirements for Interrupt.                                                                                                         | . 04       |

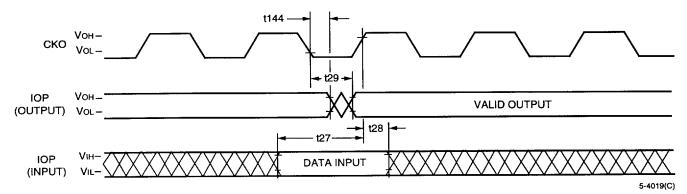

| Table 101. Timing Requirements for IOP Input Read                                                                                                     | . 05       |

| Table 102. Timing Characteristics for IOP Output.                                                                                                     | . 85       |

AT&T Microelectronics

🔲 0050026 0016541 354 📖

# List of Tables (continued)

## Page

| Table 103. Timing Characteristics for External Memory Enables (ERAMHI or ERAMLO)                      | 36 |

|-------------------------------------------------------------------------------------------------------|----|

| Table 104. Timing Characteristics for Delayed External Memory Enables (ioc = 0x000F)                  | 86 |

| Table 105. Timing Characteristics for Delayed Device Enable (ioc = 0x0010)       8                    | 86 |

| Table 106. Timing Characteristics for External Memory Access         8                                | 87 |

| Table 107. Timing Requirements for External Memory Read (ERAMHI or ERAMLO)                            |    |

|                                                                                                       | 89 |

| Table 109. Timing Characteristics for Write Cycle Followed by Read Cycle                              | 90 |

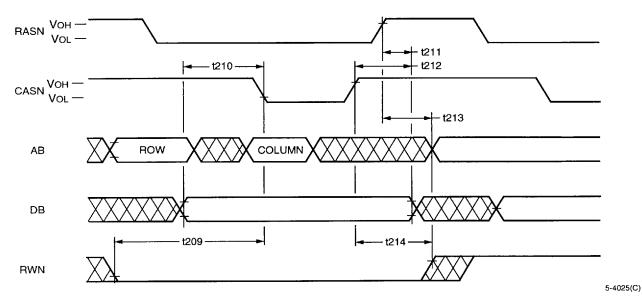

| Table 110. Timing Specification for a DRAM Read Cycle         9                                       |    |

| Table 111. Timing Specification for a DRAM Write Cycle         9                                      |    |

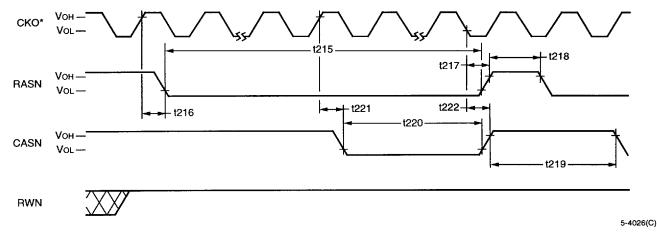

| Table 112. Timing Specification for DRAM Control Signals         9                                    |    |

| Table 113. Timing Specification for Refresh with XTAL1 Clock         9                                |    |

| Table 114. Timing Specification for Refresh Under XTAL2 Clock         9                               |    |

| Table 115. Timing Specifications for Refresh Interval Under XTAL1 Clocking         9                  |    |

| Table 116. Timing Specifications for Refresh Interval with XTAL2 Clocking         9                   |    |

| Table 117. Timing Characteristics for Serial Active Output         9                                  |    |

| Table 118. Timing Requirements for Serial Passive Output.         9                                   |    |

| Table 119. Timing Characteristics for Serial Passive Output       9                                   |    |

| Table 120. Timing Characteristics for Serial Active Input Clocks         9                            |    |

| Table 121. Timing Requirements for Serial Active Input         9                                      |    |

| Table 122. Timing Requirements for Serial Passive Input         10                                    |    |

| Table 123. Timing Characteristics for Signal Generation         10                                    |    |

| Table 124. Timing Requirements for PHIF Intel Mode Signaling         10                               |    |

| Table 125. Timing Characteristics for PHIF Intel Mode Signaling         10                            |    |

| Table 126. Pulse Period Requirements for PHIF Intel Mode Signaling         10                         |    |

| Table 127. Timing Requirements for PHIF Motorola Mode Signaling         10                            |    |

| Table 128. Timing Characteristics for PHIF Motorola Mode Signaling.         10                        |    |

| Table 129. Pulse Period Requirements for PHIF Motorola Mode Signaling.         10                     |    |

| Table 130. Timing Requirements for Intel and <i>Motorola</i> Mode Signaling (Status Register Read) 10 |    |

| Table 131. Timing Characteristics for Intel and Motorola Mode Signaling (Status Register Read)        |    |

| Table 132. DSP160X Device Coding                                                                      | 22 |

0050026 0016542 290 🔳

8

# **3 Pin Information**

The device is packaged in either a 68-pin PLCC (see Figure 1) or an 80-pin MQFP (see Figure 2).

Figure 1. DSP1605 68-Pin PLCC Pin Diagram

5-3980(C)

AT&T Microelectronics

0050026001654312? 🔳

Powered by ICminer.com Electronic-Library Service CopyRight 2003

5-3995(C)

Figure 2. DSP1605 80-Pin MQFP Diagram

AT&T Microelectronics

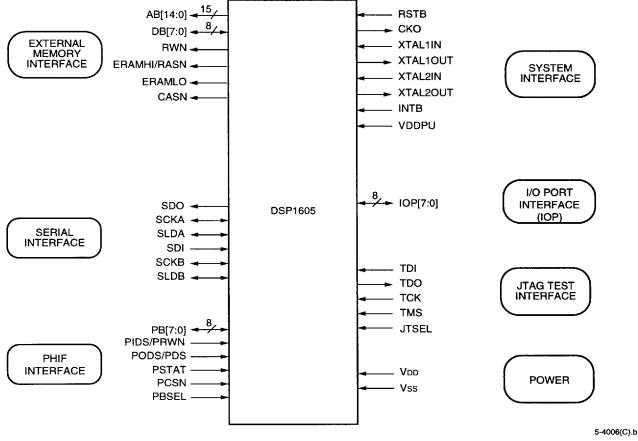

Figure 3 shows DSP1605 pins organized into their seven functional groups. Tables 1 and 2 and Sections 3.1 through 3.7 describe these pins.

Figure 3. DSP1605 Pinout by Group

Note: The CKO pin is available only on the 68-pin PLCC.

🖬 0050026 0016545 TTT 🎫

For each DSP1605 pin listed in Table 1:

- Each entry in the Type column is one of the following:

- —I (input)

- -I/O (input/output)

- -O (output)

- -TO (tristate output)

- Each entry in the Active column is one of the following:

- —High

- -Low

- Pgm (programmable polarity)

- -Neg (negative edge triggered)

#### Table 1. DSP1605 Pinout

|                 | Pin Number     |                |      |              |                                                                                                                                        |  |

|-----------------|----------------|----------------|------|--------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| Symbol          | 68-Pin<br>PLCC | 80-Pin<br>MQFP | Туре | Active       | Pin Description                                                                                                                        |  |

| AB14            | 36             | 13             | 0    | High         | 15-bit external memory address bus, bits 14—0.                                                                                         |  |

| AB[13:12]       | 37—38          | 15—16          |      |              |                                                                                                                                        |  |

| AB[11:8]        | 39—42          | 18—21          |      |              |                                                                                                                                        |  |

| AB[7:0]         | 4552           | 24—31          |      |              |                                                                                                                                        |  |

| CASN            | 5              | 58             | 0    | Low          | Column address select.                                                                                                                 |  |

| СКО             | —              | 44             | 0    | High         | Processor clock.<br>(The 68-pin PLCC has no CKO pin.)                                                                                  |  |

| DB[7:2]         | 28—33          | 4—9            | I/O  | High         | 8-bit external memory data bus. Each of these pins has an                                                                              |  |

| DB[1:0]         | 34—35          | 11—12          |      |              | internal pull-down resistor that is typically 68 k $\Omega$ .                                                                          |  |

| ERAMHI/<br>RASN | 4              | 57             | 0    | Low          | External RAM, high select, or row address select.                                                                                      |  |

| ERAMLO          | 3              | 56             | 0    | Low          | External RAM, low select.                                                                                                              |  |

| IOP7/TCK        | 63             | 46             | 1/0  | Pgm/<br>—    | I/O port bit 7, multiplexed with TCK (JTAG test clock).                                                                                |  |

| IOP6/TMS        | 64             | 47             | I/O  | Pgm/<br>High | I/O port bit 6, multiplexed with TMS (JTAG test mode select).                                                                          |  |

| IOP5/TDI        | 65             | 48             | 1/0  | Pgm/<br>High | I/O port bit 5, multiplexed with TDI (JTAG test data in).                                                                              |  |

| IOP4/TDO        | 66             | 49             | 1/0  | Pgm/<br>High | I/O port bit 4, multiplexed with TDO (JTAG test data out).                                                                             |  |

| IOP3            | 67             | 51             | 1/0  | Pgm          | I/O port bit 3.                                                                                                                        |  |

| IOP2/PBSEL      | 68             | 52             | 1/0  | Pgm/<br>High | I/O port bit 2, multiplexed with PBSEL (PHIF byte select).                                                                             |  |

| IOP1/SCKB       | 1              | 54             | 1/0  | Pgm          | I/O port bit 1, multiplexed with SCKB [serial clock channel B<br>(dual-channel mode), or serial input clock (single-channel<br>mode)]. |  |

| IOP0/INTB       | 2              | 55             | 1/0  | Pgm/<br>Neg  | I/O port bit 0, multiplexed with INTB (external interrupt, negative edge triggered).                                                   |  |

| JTSEL           | 62             | 45             |      | High         | JTAG select input.                                                                                                                     |  |

| PB[7:0]         | 18—25          | 74—80          | 1/0  | High         | 8-bit parallel data bus.                                                                                                               |  |

12

AT&T Microelectronics

#### 🔲 0050026 0016546 936 🖿

| Table 1. | DSP1605 | Pinout | (continued) |

|----------|---------|--------|-------------|

|----------|---------|--------|-------------|

|           | Pin Number     |                |      |          |                                                                                           |  |

|-----------|----------------|----------------|------|----------|-------------------------------------------------------------------------------------------|--|

| Symbol    | 68-Pin<br>PLCC | 80-Pin<br>MQFP | Туре | Active   | Pin Description                                                                           |  |

| PCSN      | 16             | 71             | . I  | Low      | Parallel device enable strobe.                                                            |  |

| PIDS/PWRN | 14             | 69             | Ι    | Low      | Parallel input data strobe, or parallel read/write.                                       |  |

| PODS/PDS  | 15             | 70             | Ι    | Low      | Parallel output data strobe, or parallel data strobe.                                     |  |

| PSTAT     | 17             | 72             | I    | High     | PHIF status.                                                                              |  |

| RSTB      | 58             | 39             | I/O  | Low      | Reset.                                                                                    |  |

| RWN       | 6              | 59             | 0    | <u> </u> | Read/write not.                                                                           |  |

| SCKA      | 8              | 61             | I/O  |          | Serial clock channel A (dual-channel mode), or serial output clock (single-channel mode). |  |

| SDI       | 7              | 60             | I    | High     | Serial data in.                                                                           |  |

| SDO       | 13             | 68             | ТО   | High     | Serial data out.                                                                          |  |

| SLDA      | 11             | 66             | I/O  | Pgm      | Serial load channel A (dual-channel mode), or serial output load (single-channel mode).   |  |

| SLDB      | 12             | 67             | I/O  | Pgm      | Serial load channel B (dual-channel mode), or serial input load (single-channel mode).    |  |

| VDDPU     | 59             | 40             |      | High     | VDD powerup.                                                                              |  |

| XTAL1IN   | 53             | 32             |      |          | High-frequency crystal in.                                                                |  |

| XTAL1OUT  | 54             | 34             | 0    | —        | High-frequency crystal out.                                                               |  |

| XTAL2IN   | 55             | 36             | 1    |          | Low-frequency crystal in.                                                                 |  |

| XTAL2OUT  | 56             | 37             | 0    | —        | Low-frequency crystal out.                                                                |  |

#### Table 2. DSP1605 Power Supply, Ground, and Unconnected Pins

| Combal | Pin                   | Pin Description            |                            |                  |

|--------|-----------------------|----------------------------|----------------------------|------------------|

| Symbol | Symbol                | 68-Pin PLCC                | 80-Pin MQFP                | Fill Description |

| VDD    | 10, 26, 44, and 60    | 2, 23, 41, and 65          | 5 V or 3.3 V power supply. |                  |

| Vss    | 9, 27, 43, 57, and 61 | 3, 22, 38, 42, and 62      | Ground.                    |                  |

| NC     |                       | 10, 14, 17, 33, 35, and 43 | No connection.             |                  |

AT&T Microelectronics

🔲 0050026 0016547 872 📟

# 3.1 System Interface

This section describes the system interface pins on the DSP1605.

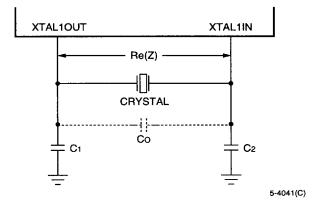

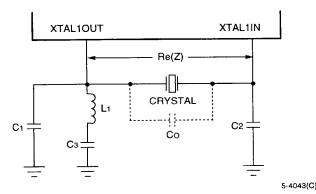

## 3.1.1 XTAL1IN, XTAL1OUT

**High-Frequency Crystal Oscillator.** Input/Output. The 1x crystal oscillator for high-frequency clocks. XTAL1IN is the input node for the oscillator amplifier. XTAL1OUT is the output node for the oscillator amplifier. If the high-frequency clock is selected (see the **ioc** register, Table 33, on page 54), this clock determines the DSP1605 instruction cycle time. For more information, see Section 9.1, High-Frequency Crystal Oscillator, on page 108.

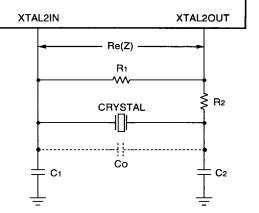

## 3.1.2 XTAL2IN, XTAL2OUT

**Low-Frequency Crystal Oscillator.** Input/Output. The 1x crystal oscillator generates the low-frequency clock, which typically generates the internal clock when the DSP is in low-power standby mode. XTAL2IN is the input node for the oscillator amplifier. XTAL2OUT is the output node for the oscillator amplifier. If the low-frequency clock is selected (see the **ioc** register, Table 33, on page 54), this clock provides DRAM refresh, determines the DSP1605 instruction cycle time, and drives TIMER1. For more information, see Section 9.2, Low-Frequency Crystal Oscillator or Resonator, on page 112.

## 3.1.3 CKO

**Clock Out.** (Only on 80-pin MQFP package.) Output clock or single-bit data output. CKO is selectable through programming the **ioc** register (see Table 33 on page 54). The following options are selectable: a free-running clock, a wait-stated clock, a logic 0, or a logic 1. If used as a single-bit output, this pin initializes to a free-running clock after reset.

## 3.1.4 RSTB

**Reset**. Bidirectional (Schmitt trigger). Negative Assertion. A high-to-low transition on RSTB causes the DSP1605 to enter the reset state. Upon deassertion, the DSP begins execution from location 0x0000. This input contains a Schmitt trigger providing a hysteresis between positive- and negative-going transitions.

**Note:** This pin is internally tied to the open-drain output of the power-loss detect circuit. To indicate a reset, a power-loss detect condition forces this pin low.

## 3.1.5 INTB

**Interrupt.** Input (Schmitt trigger). Negative Edge-Triggered. External interrupt to the DSP1605. This input contains a Schmitt trigger providing a hysteresis between positive- and negative-going transitions. An interrupt is posted when a negative-going transition is detected. Note that there is no interrupt acknowledge pin. External hardware must guarantee that the interrupt service routine has completed before issuing another interrupt on INTB. Any activity on INTB is not recognized during the interrupt service routine.

**Note:** This pin is multiplexed with IOP0 (see Section 3.4, I/O Port (IOP[7:0])).

## 3.1.6 VDDPU

**VDD Powerup**. Input. This pin should be connected to VDD to enable the internal power-loss detect circuit. To disable, this pin should be pulled low.

14

0050026 0016548 709 🛲

Powered by ICminer.com Electronic-Library Service CopyRight 2003

## **3.2 External Memory Interface**

#### 3.2.1 AB[14:0]

Address Bus. Output. Address bus for read or write transactions to external memory.

#### 3.2.2 DB[7:0]

**Data Bus**. Bidirectional. Data bus for read or write transactions to external memory or 1/O. Each pin has an internal pull-down resistor that is typically 68 k $\Omega$ .

#### 3.2.3 ERAMLO

**External RAM Lo Select**. Output. Negative assertion. Asserted when the ERAMLO segment in the Y memory space is accessed. The leading edge of ERAMLO may be programmed to be delayed by one half of an instruction cycle.

#### 3.2.4 ERAMHI/RASN

**External RAM Hi Select/Row Address Select**. Output. Negative assertion. The function of this pin depends on whether the DRAM controller is enabled in the **ioc** register. If the DRAM controller is enabled, this pin functions as RASN. Along with its assertion, the row address is driven on the AB pins. If the DRAM controller is not enabled, this pin functions as ERAMHI and is asserted when the ERAMHI segment in the Y memory (data) space is accessed. The leading edge of ERAMHI may be programmed to be delayed by one half of an instruction cycle.

## 3.2.5 CASN

**Column Address Select**. Output. Negative assertion. Asserted when the ERAMHI segment in the Y address space is accessed. Along with its assertion, the column address is driven on the AB pins.

#### 3.2.6 RWN

**Read/Write Not.** Output. When a logic 1, a read access is in progress; when a logic 0, a write access is in progress.

# 3.3 Serial Interface (SIO)

The SIO is configurable for either single-channel or dual-channel mode, selectable by the **sioc** register. The SIO pins perform different functions depending on whether the single-channel or dual-channel mode is selected. In the descriptions below, both functions are described for each pin. For more information about the **sioc** register, see Table 43 on page 59. For the **sioce** register, see Table 44 on page 60.

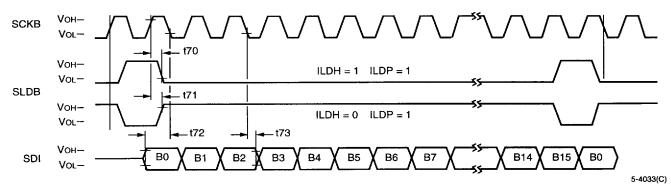

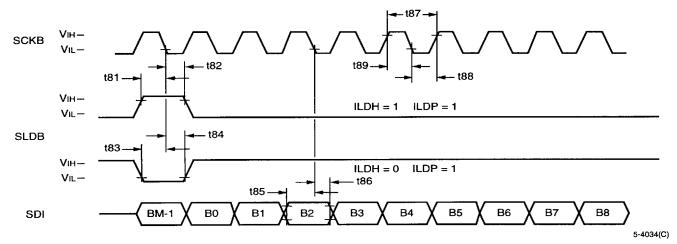

#### 3.3.1 SDI in Single-Channel Mode

Serial Data Input. Input. Serial input data latched on the falling edge of SCKB, either LSB or MSB first, according to the **sioc** register MSB field.

## 3.3.2 SDI in Dual-Channel Mode

Serial Data Input. Input. Channel A serial input data is latched on the falling edge of SCKA, and channel B serial input data is latched on the falling edge of SCKB. The data is either LSB or MSB first, according to the sioc register MSB field.

#### 3.3.3 SCKB Multiplexed

This pin is multiplexed with IOP1 (see Section 3.4, I/O Port (IOP[7:0])). This multiplexed signal is selected by the UENHSIO bit of the **ioc** register (see Table 33 on page 54). If the UENHSIO bit is cleared to zero, SCKB is internally tied to SCKA.

#### 3.3.4 SCKB in Single-Channel Mode

**Input Clock** (ICK). Bidirectional. Clock for serial input data. In active mode, SCKB is an output; in passive mode, SCKB is an input, according to the **sioc** register ICK field.

#### 3.3.5 SCKB in Dual-Channel Mode

Serial Clock B. Bidirectional. Channel B clock for serial input data and for serial output data. In active mode, SCKB is an output; in passive mode, SCKB is an input, according to the **sioc** register ICK field.

#### AT&T Microelectronics

🔲 0050026 0016549 645 🛲

## 3.3 Serial Interface (SIO) (continued)

## 3.3.6 SLDB in Single-Channel Mode

**Input Load** (ILD). Bidirectional. The strobe for loading the input buffer **sdx<0—1>\_**i from the input shift register. The assertion of SLDB indicates the beginning of a serial input word. In active mode, SLDB is an output. In passive mode, SLDB is an input and should only be asserted once per serial input word. Passive or active mode is set through the **sioc** register ILD field. The assertion level of SLDB is selectable through the **sioce** register ILDH field, and the duty cycle for the active SLDB is selectable through the **sioce** register ILDP field.

## 3.3.7 SLDB in Dual-Channel Mode

Serial Load B. Bidirectional. The strobe for channel B for loading the input buffer sdx<0--1>\_i from the input shift register and for loading the output shift register from the output buffer sdx<0--2>\_o. The assertion of SLDB indicates the beginning of a channel B serial input word and the beginning of a channel B serial output word. In active mode, SLDB is an output. In passive mode, SLDB is an input and should only be asserted once per serial input word. Passive or active mode is set through the sioc register ILD field. The assertion level of SLDB is selectable through the sioce register ILDH field, and the duty cycle for the active SLDB is selectable through the sioce register ILDP field.

## 3.3.8 SDO in Single-Channel Mode

Serial Data Output. Output. Serial output data is clocked out on the rising edge of SCKA and may be configured to be least significant bit (LSB) first or most significant bit (MSB) first through the MSB bit of the sioc register.

## 3.3.9 SDO in Dual-Channel Mode

**Serial Data Output**. Output. Serial output data for channel A is clocked out on the rising edge of SCKA, and serial output data for channel B is clocked out on the rising edge of SCKB. Data may be configured to be least significant bit (LSB) first or most significant bit (MSB) first through the MSB bit of the **sioc** register.

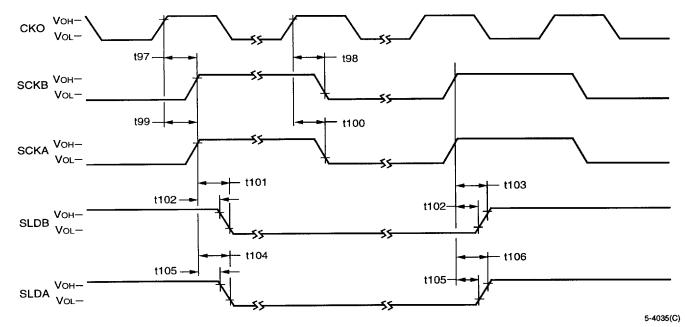

## 3.3.10 SCKA in Single-Channel Mode

**Output Clock** (OCK). Bidirectional. Clock for serial output data. In active mode, SCKA is an output; in passive mode, SCKA is an input, according to the **sioc** register OCK field.

## 3.3.11 SCKA in Dual-Channel Mode

**Serial Clock A**. Bidirectional. Channel A clock for serial input data and serial output data. In active mode, SCKA is an output; in passive mode, SCKA is an input, according to the **sioc** register OCK field.

## 3.3.12 SLDA in Single-Channel Mode

**Output Load** (OLD). Bidirectional. The strobe for loading the output shift register from the output buffer **sdx<0—2>\_**0. The assertion of SLDA indicates the beginning of a serial output word. In active mode, SLDA is an output. In passive mode, SLDA is an input and should only be asserted once per serial output word. Passive or active mode is set through the **sioc** register OLD field. The assertion level of SLDA is selectable through the **sioce** register OLDH field, and the duty cycle for the active SLDA is selectable through the **sioce** register OLDP field.

## 3.3.13 SLDA in Dual-Channel Mode

**Serial Load A.** Bidirectional. The strobe for channel A for loading the input buffer **sdx<0—1>\_**i from the input shift register and for loading the output shift register from the output buffer **sdx<0—2>\_**o. The assertion of SLDA indicates the beginning of a channel A serial input word and the beginning of a channel A serial output word. In active mode, SLDA is an output. In passive mode, SLDA is an input and should only be asserted once per serial input word. Passive or active mode is set through the **sioc** register OLD field. The assertion level of SLDA is selectable through the **sioce** register OLDH field, and the duty cycle for the active SLDA is selectable through the **sioce** register OLDP field.

# 3.4 I/O Port (IOP[7:0])

**I/O Port**. Bidirectional. These pins can be individually configured to be inputs or outputs. As outputs, each bit may be set, cleared, or toggled under program control. As inputs, they may be read.

**Note:** As shown in Figure 1 on page 9, Figure 2 on page 10, and Table 1 on page 12, IOP[7:4] and IOP[2:0] are multiplexed with other functions.

**AT&T Microelectronics**

0050026 0016550 367 🎟

16

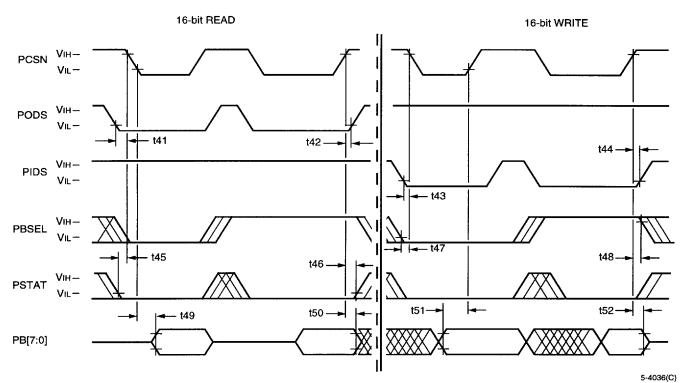

## 3.5 PHIF

This section describes the PHIF pins on the DSP1605.

## 3.5.1 PCSN

**Parallel Device Enable Strobe**. Input. Negative assertion. When asserted, the PHIF registers may be read or written by the host processor.

## 3.5.2 PODS/PDS

## Parallel Output Data Strobe/Parallel Data Strobe.

Input. This pin is configurable by the DSP in software. When configured as PODS, it has a negative assertion level. When PODS is asserted along with PCSN, the PHIF output data register or the PHIF status register is read by the host processor. When configured as PDS, the assertion level of the pin (active-high or active-low) is also configurable by the DSP in software. When PDS is asserted along with PCSN, the level of the PRWN signal determines whether a read or a write transaction is performed by the host processor.

#### 3.5.3 PIDS/PRWN

#### Parallel Input Data Strobe/Parallel Read/Write.

Input. This pin is configurable by the DSP in software. When configured as PIDS, it has a negative assertion level. When PIDS is asserted along with PCSN, the PHIF input data register is written by the host processor. When configured as PRWN, the state of PRWN when PCSN and PDS are asserted determines whether the host processor performs a read (PRWN = 1) or a write (PRWN = 0).

#### 3.5.4 PSTAT

PHIF Status. Input. A logic 0 on PSTAT during a write transaction selects the parallel input data register to be written; on a read transaction, the parallel output data register is read. A logic 1 on PSTAT during a read transaction selects the PHIF status register to be read.

#### 3.5.5 PBSEL

**PHIF Byte Select.** Input. When the PHIF is configured for 16-bit transfers through the **phifc** register, PBSEL selects the byte available for access by the host. For more information, see Table 38, phifc Register PHIF Function (8-Bit and 16-Bit Modes), on page 56.

This pin is multiplexed with IOP2 (see Section 3.4, I/O Port (IOP[7:0])). This multiplexed signal is selected by bit 7 of the **phifc** register (see Table 37 on page 56). If bit 7 is cleared to 0, this pin functions as IOP2 and the internal PBSEL signal is tied to logic 0.

#### 3.5.6 PB[7:0]

**Parallel Data Bus.** Bidirectional. On the host processor write transaction to the PHIF, the data written is placed on PB[7:0] by the host. On a host processor read transaction from the PHIF, the data being read is placed on PB[7:0] by the DSP1605.

**AT&T Microelectronics**

🔳 0050026 00l655l 2T3 📟

# 3.6 JTAG Test Mode Interface

This section describes the JTAG pins on the DSP1605.

## 3.6.1 JTSEL

**JTAG Select**. Input. This pin controls the multiplexing of the four JTAG pins (TCK, TMS, TDI, and TDO) with pins IOP[7:4]. Set JTSEL high to select the JTAG pins. Set JTSEL low to select IOP[7:4]. (See Section 3.4, I/O Port (IOP[7:0]).

## 3.6.2 TCK

This pin is multiplexed with IOP7.

**Test Clock.** Input. JTAG serial shift clock that clocks data into TDI and out of TDO and controls the JTAG port by latching TMS into the state machine controller.

## 3.6.3 TMS

This pin is multiplexed with IOP6.

**Test Mode Select.** Input. JTAG mode control signal that controls the state of the JTAG controller. TMS is sampled on the rising edge of TCK.

#### 3.6.4 TDI

This pin is multiplexed with IOP5.

**Test Data Input**. Input. JTAG serial input of all serialscanned data and instructions that is sampled on the rising edge of TCK.

## 3.6.5 TDO

This pin is multiplexed with IOP4.

**Test Data Output.** Tristate Output. JTAG serial output of all serial-scanned data and status bits. TDO changes on the falling edge of TCK.

## 3.7 PWR/GND

This section describes the power and ground pins on the DSP1605.

3.7.1 Vss

Ground. There are five ground pins.

3.7.2 VDD

5.0 V or 3.3 V Supply. There are four power pins.

18

AT&T Microelectronics

# **4 Hardware Architecture**

The DSP1605 is a 16-bit fixed-point digital signal processor (DSP) that is generally upward object code compatible with the DSP1610, except for specific I/O configurations and peripherals. The DSP1605 consists of a DSP1600 core together with internal memory and peripherals.

To minimize pin count, the DSP1605 multiplexes the following package pins:

- IOP0 is multiplexed with INTB

- IOP1 is multiplexed with SCKB

- IOP2 is multiplexed with PBSEL

- IOP4 is multiplexed with TDO

- IOP5 is multiplexed with TDI

- IOP6 is multiplexed with TMS

- IOP7 is multiplexed with TCK

## 4.1 DSP1605 Architectural Overview

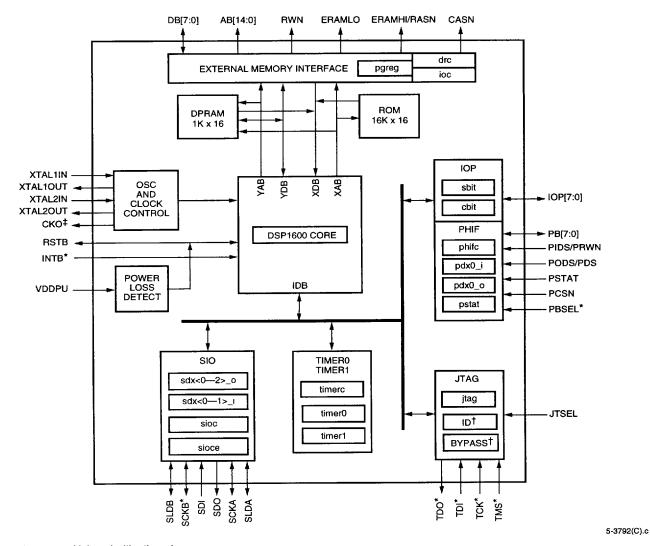

Figure 4 on page 20 shows a block diagram of the DSP1605, which consists of the modules described in Sections 4.1.1 through 4.1.9. Table 3 on page 21 shows a legend for the DSP1605 block diagram. Certain modules contain internal registers that are illustrated (not to scale) in Figure 4. The DSP has a pair of internal buses (address bus and data bus) for program/coefficient memory (X memory space) and a second independent pair of internal buses for data memory (Y memory space).

🔲 0050026 0016553 076 🖬

## 4.1 DSP1605 Architectural Overview (continued)

These pins are multiplexed with other pins.

† These registers are accessible through pins only.

‡ The CKO pin is available only on the 80-pin MQFP package.

The registers whose names are shown in lower-case letters are accessible by the DSP software (some are also accessible externally through the pins). The registers whose names are shown in upper-case letters are accessible only through the DSP pins. Note:

Figure 4. DSP1605 Block Diagram

20

## 0050026 0016554 TO2 💻

## 4.1 DSP1605 Architectural Overview (continued)

#### Table 3. DSP1605 Block Diagram Legend

| Symbol     | Name                                               |

|------------|----------------------------------------------------|

| BYPASS     | JTAG bypass register                               |

| cbit       | Control registers for IOP                          |

| drc        | DRAM control register                              |

| ID         | JTAG device identification register                |

| IDB        | Internal data bus                                  |

| ioc        | I/O configuration register                         |

| IOP        | I/O port                                           |

| jtag       | 16-bit serial/parallel register                    |

| OSC        | Internal high- and low-frequency clock oscillators |

| pdx0_i     | PHIF data register input buffer                    |

| pdx0_o     | PHIF data register output buffer                   |

| pgreg      | Page register for row address select               |

| PHIF       | Processor host interface                           |

| PSTAT      | PHIF status register                               |

| phifc      | PHIF control register                              |

| DPRAM      | Internal RAM (1K x 16)                             |

| ROM        | Internal ROM (16K x 16)                            |

| sbit       | Status register for IOP                            |

| sdx<01>_i  | Serial data transmit input registers               |

| sdx<0—2>_0 | Serial data transmit output registers              |

| SIO        | Serial I/O unit                                    |

| sioc       | Serial I/O control register                        |

| sioce      | Serial I/O extended control register               |

| TIMER<0,1> | Programmable timer units                           |

| timer<0,1> | Timer running count registers                      |

| timerc     | Timer control register                             |

| XAB        | X space (program space) address bus                |

| XDB        | X space data bus                                   |

| YAB        | Y space (data space) address bus                   |

| YDB        | Y space data bus                                   |

#### 4.1.1 DSP1600 Core

The DSP1600 core is the heart of the DSP1605. The core consists of a data arithmetic unit (DAU), two address arithmetic units (XAAU and YAAU), an instruction cache, and a control section. The core provides support for external memory wait-states and internal dual-port RAM, and features vectored interrupts and a trap mechanism. (For more information, see Section 4.2, DSP1600 Core Architectural Overview, on page 24.)

#### **AT&T Microelectronics**

III 0050026 0016555 949 III

# 4.1 DSP1605 Architectural Overview

(continued)

## 4.1.2 Dual-Port RAM (DPRAM)

This module contains one bank of zero wait-state memory. It consists of 1K of 16-bit words and has separate address and data ports to the instruction/coefficient and data memory spaces. A program can reference memory from either space at any time, transparently and without restriction. The DSP1600 core automatically performs the required multiplexing. In the event that references to both ports of DPRAM are made simultaneously, the DSP1600 core automatically inserts a wait-state and performs the data port access first, followed by the instruction/coefficient port access. Because the DSP has only one 1-Kword bank, all simultaneous accesses from X and Y space result in an added wait-state. See also Section 4.4, Memory Maps and Wait-States.

A program can be downloaded from slow off-device memory into DPRAM and then be executed without wait-states. DPRAM is also useful for improving convolution performance in cases where the coefficients are adaptive. Because DPRAM can be downloaded through the JTAG port, full-speed remote in-circuit emulation is possible. DPRAM can also be used for downloading self-test code through the JTAG port.

## 4.1.3 Read-Only Memory (ROM)

The DSP1605 contains 16K of 16-bit words of zero wait-stated mask-programmable ROM for program and fixed coefficients. A mask-programmable secure option is available, which prohibits reading out the ROM contents externally. This is accomplished by prohibiting the selection of memory map 3.

## 4.1.4 External Memory Interface (EMI)

By connecting the DSP1605 to external memory and I/O devices, the EMI supports read and write operations from and to data memory (Y memory space). The DSP1600 core automatically controls the EMI. Instructions can transparently reference external memory from the internal data bus. Through the EMI, both SRAMs and DRAMs can be interfaced to the DSP. For more information, see Section 4.5, External Memory Interface (EMI) and Section 4.4, Memory Maps and Wait-States.

## 4.1.5 Timers

Two timers are provided in the DSP1605. They are used to provide an interrupt at the expiration of a programmed interval. The interrupt may be a single interrupt or a repetitive interrupt. TIMER0 has a clock prescaler and supports over nine orders of magnitude of interval selection. TIMER1 counts at the frequency of the low-frequency crystal, XTAL2, divided by four, and does not have a prescaler. The timers may be stopped and restarted at any time. For more information, see Section 4.8.

## 4.1.6 Input/Output Port (IOP)

One 8-bit IOP unit provides convenient and efficient monitoring and control of eight individually configurable pins. When configured as outputs, the pins can be individually set, cleared, toggled or left unchanged. When configured as inputs, the entire port can be read (those configured as inputs as well as those configured as outputs). Note that most of the pins are multiplexed with other functions. For detailed information about IOP operation, see Section 4.7, I/O Port (IOP).

## 4.1.7 JTAG

The JTAG section contains logic that implements the JTAG/*IEEE* \* P1149.1 standard four-signal test port. No boundary-scan register is included. The JTAG port provides a mechanism for the DSP1600 core to communicate with remote test equipment or a remote hardware development system (DSP1600-HDS or *FlashDSP*1600-HDS). The JTAG port also supports program, memory, and register upload/download, and execution start/stop.

A 4-bit instruction register, a bypass register, and a device identification register have been implemented (see Table 34 on page 55). The JTAG instruction for accessing the ID register is 0xE (1110). The JTAG instruction for accessing the BYPASS register is 0xF (1111). Figure 4 on page 20 shows the ID and BYPASS registers. There is no separate TRST input pin.

\* *IEEE* is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc.

**AT&T Microelectronics**

00500260016556885 🎟

22

## 4.1 DSP1605 Architectural Overview

(continued)

## 4.1.8 Serial Input/Output Unit (SIO)

The SIO provides a serial interface to codecs and signal processors with few, if any, external devices. For example, the SIO port interfaces gluelessly to many industry-standard codecs, such as the AT&T T7513B and T7503. The high-speed, double-buffered port supports back-to-back transmissions.

Both passive mode, i.e., clock and load signals driven from an external source, and active mode, i.e., clock and load signals driven by the DSP, are supported. Output data transfers of 8, 16, 32, or 48 bits, and input data transfers of 8, 16, or 32 bits may be defined.

The SIO can be configured to operate in a dual-channel mode, in which data from two external serial devices are time-division multiplexed by sharing data in (SDI) and data out (SDO) pins. For more detail on the SIO, see Section 4.6, Serial I/O Unit (SIO).

#### 4.1.9 Power-Loss Detect Circuit

The power-loss detect circuit is enabled by connecting the VDDPU pin to the power supply, VDD. The output of the power-loss detect circuit is internally connected to the RSTB pin. If the supply voltage falls below the minimum required value, the bidirectional RSTB pin has an open-drain output that is pulled low. This causes an automatic device reset. The power-loss detect circuit is disabled by connecting the VDDPU pin to ground.

#### 4.1.10 Oscillator and Clock Control

The DSP includes two internal oscillators that provide a high-frequency clock (XTAL1) and a low-frequency clock (XTAL2). The **ioc** register bit 12 (see Table 33 on page 54) determines which clock is selected to run the core and peripherals. The DSP instruction cycle time is determined by the period of the selected clock.

The power dissipation is reduced when XTAL2 is selected, and is further reduced if the XTAL1 oscillator is then disabled by setting bit 13 of the **ioc** register.

The DSP1605 80-pin MQFP package provides an output clock pin, CKO. As shown in Table 4, **ioc** register bits 10 and 11 select one of four CKO pin output functions.

#### **Table 4. CKO Pin Output Functions**

| ioc Register |        | CKO Pin Output Function                                                                                                                                                                                                                                                                   |

|--------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 11       | Bit 10 |                                                                                                                                                                                                                                                                                           |

| 0            | 0      | Free-running unstretched cycle clock.                                                                                                                                                                                                                                                     |

| 0            | 1      | Wait-stated clock. The high-to-low<br>transition of the wait-stated clock is<br>synchronized with the high-to-low<br>transition of the free-running<br>unstretched cycle clock.                                                                                                           |

| 1            | 0      | Single-bit output held high.                                                                                                                                                                                                                                                              |

| 1            | 1      | Single-bit output held low. For<br>maximum power savings, set bits 10<br>and 11 to 1 (by the setting the <b>ioc</b><br>register to 0x3C00) before setting the<br>low-power standby mode. (For more<br>information, see Section 4.3.5, Low-<br>Power Standby Mode (AWAIT), on<br>page 28.) |

Note: Although the DSP1605 68-pin PLCC package does not provide a CKO pin, **ioc** register bits 10 and 11 must both still be set to 1 for minimum power consumption.

#### 4.1.11 Parallel Host Interface (PHIF)

The PHIF is a passive, 8-bit parallel port that can interface to an 8-bit bus containing other AT&T DSPs, microprocessors, or peripheral I/O devices. The PHIF port supports either *Motorola*<sup>\*</sup> or *Intel*<sup>†</sup> protocols, as well as 8-bit or 16-bit transfers, configured in software. The port data rate depends upon the instruction cycle rate.

The PHIF is accessed in two basic modes: 8-bit or 16-bit mode. In 16-bit mode, the host determines an access of the high or low byte. In 8-bit mode, only the low byte is accessed. Software-programmable features allow for a glueless host interface to microprocessors. For more detail, see Section 4.9, Parallel Host Interface (PHIF).

\* *Motorola* is a registered trademark of Motorola, Inc. † *Intel* is a registered trademark of Intel Corporation.

**AT&T** Microelectronics

00500260016557711 🖿

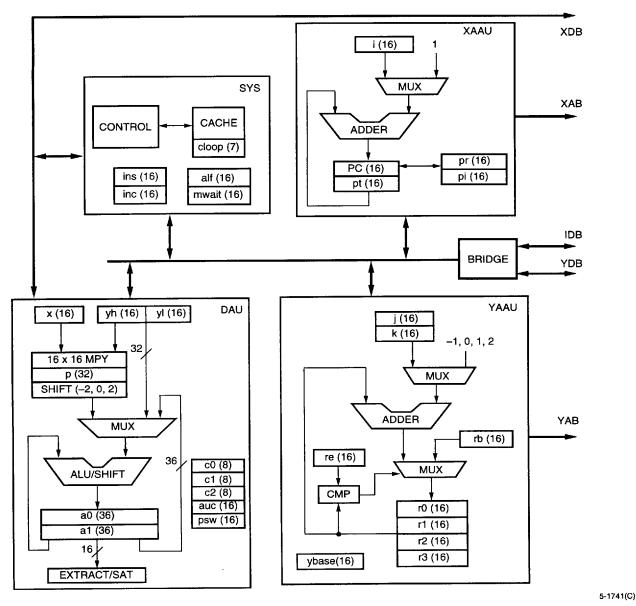

# 4.2 DSP1600 Core Architectural Overview

Figure 5 shows a block diagram of the DSP1600 core, which consists of the modules described in Sections 4.2.1 through 4.2.4. Table 5 on page 25 contains a legend for the DSP1600 core block diagram.

🛚 0050026 0016558 658 🎟

24

## 4.2 DSP1600 Core Architectural Overview (continued)

## Table 5. DSP1600 Core Block Diagram Legend

| Symbol      | Name                                                                    |

|-------------|-------------------------------------------------------------------------|

| 16 x 16 MPY | 16-bit by 16-bit multiplier                                             |

| a0a1        | Accumulators 0 and 1 (16-bit halves specified as a0, a0l, a1, and a1l)* |

| alf         | Low-power standby mode and memory map control                           |

| ALU/SHIFT   | Arithmetic logic unit/shifter                                           |

| auc         | Arithmetic unit control                                                 |

| c0c2        | Counters 0—2                                                            |

| cloop       | Cache loop count                                                        |

| CMP         | Comparator                                                              |

| DAU         | Digital arithmetic unit                                                 |