DVI and HDMI interface ESD and overcurrent protection, DDC/CEC buffering, hot plug detect and backdrive protection

Rev. 2 — 21 October 2011

**Product data sheet**

# 1. General description

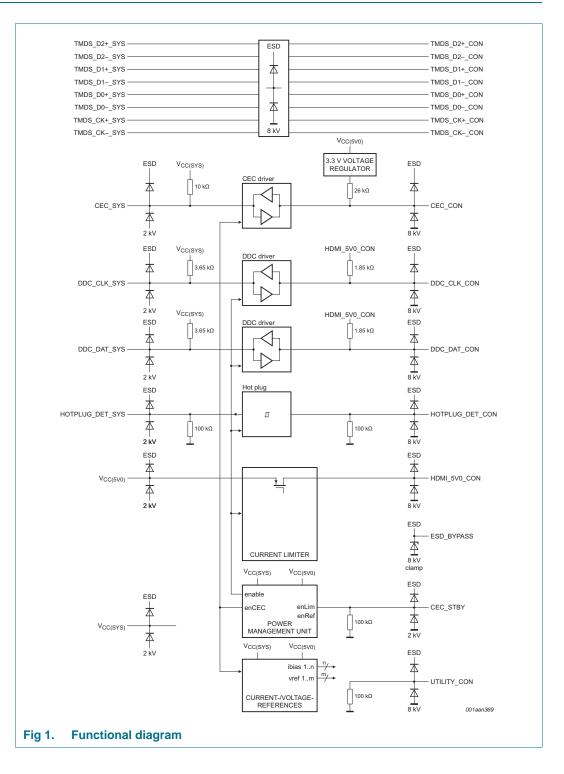

The IP4786CZ32 is designed to protect High-Definition Multimedia Interface (HDMI) transmitter host interfaces. It includes HDMI 5 V overcurrent / overvoltage protection, Data Display Channel (DDC) buffering and decoupling, hot plug detect, backdrive protection, Consumer Electronic Control (CEC) buffering and decoupling, and  $\pm 8$  kV contact ElectroStatic Discharge (ESD) protection for all I/Os in accordance with the IEC 61000-4-2, level 4 standard.

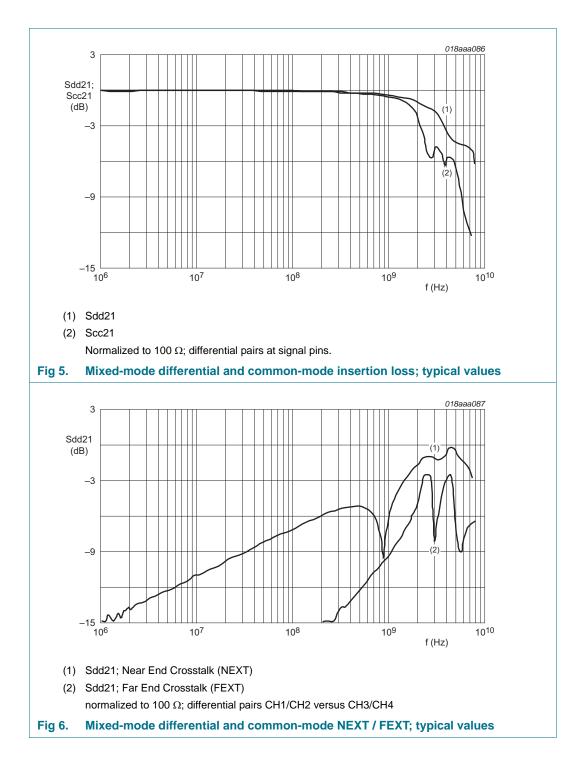

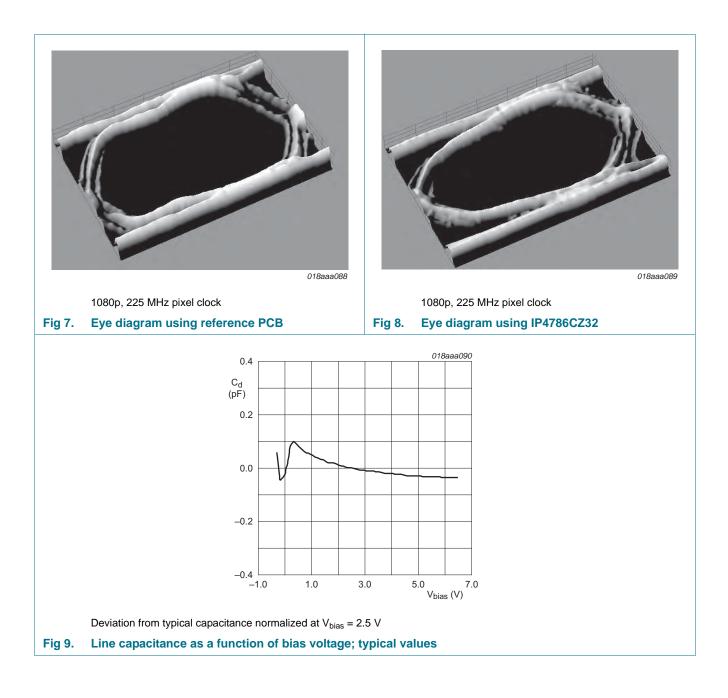

The IP4786CZ32 incorporates Transmission Line Clamping (TLC) technology on the high-speed Transition Minimized Differential Signaling (TMDS) lines to simplify routing and help reduce impedance discontinuities. All TMDS lines are protected by an impedance-matched diode configuration that minimizes impedance discontinuities caused by typical shunt diodes.

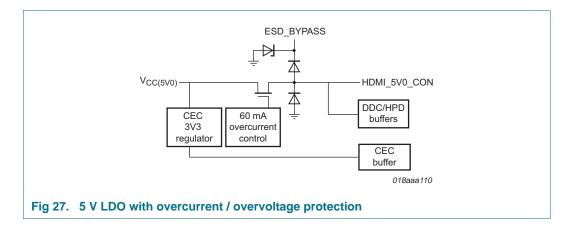

The enhanced 60 mA overcurrent / overvoltage linear regulator guarantees HDMI-compliant 5 V output voltage levels with up to 6.5 V inputs.

The DDC lines use a new buffering concept which decouples the internal capacitive load from the external capacitive load for use with standard Complementary Metal Oxide Semiconductor (CMOS) or Low Voltage Transistor-Transistor Logic (LVTTL) I/O cells down to 1.8 V. This buffering also redrives the DDC and CEC signals, allowing the use of longer or cheaper HDMI cables with a higher capacitance. The internal hot plug detect module simplifies the application of the HDMI transmitter to control the hot plug signal.

All lines provide appropriate integrated pull-ups and pull-downs for HDMI compliance and backdrive protection to guarantee that HDMI interface signals are not pulled down if the system is powered down or enters Standby mode. Only a single external capacitor is required for operation.

# 2. Features and benefits

- HDMI 1.3a and 1.4, 340 MHz pixel clock, deep color and HDMI Ethernet and Audio return Channel (HEAC) compatible

- Pb-free, Restriction of Hazardous Substances (RoHS) compliant and free of halogen and antimony (Dark Green compliant)

- Robust ESD protection without degradation after repeated ESD strikes

- Impedance matched 100 Ω differential transmission line ESD protection for TMDS lines (±10 Ω). No Printed-Circuit Board (PCB) pre-compensation required

- All external I/O lines with ESD protection of at least ±8 kV in accordance with the IEC 61000-4-2, level 4 standard

- DDC capacitive decoupling between system side and HDMI connector side and buffering to drive cable with high capacitive load (> 700 pF/25 m)

- Hot plug detect module

- CEC buffering and isolation, with integrated backdrive-protected 26 kΩ pull-up

- Simplified flow-through routing utilizing less overall PCB space

- Highest integration in a small footprint, PCB level, optimized RF routing, 32-pin HVQFN leadless package

# 3. Applications

- The IP4786CZ32 can be used for a wide range of HDMI source devices, consumer and computing electronics:

- Standard-Definition (SD) and High-Definition (HD) DVD player

- Set-top box

- PC graphic card

- Game console

- HDMI picture performance quality enhancer module

- Digital Visual Interface (DVI)

# 4. Ordering information

| Table 1. Order      | Table 1. Ordering information |                                                                                                             |          |  |  |  |  |  |  |

|---------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|--|

| Type number Package |                               |                                                                                                             |          |  |  |  |  |  |  |

|                     | Name                          | Description                                                                                                 | Version  |  |  |  |  |  |  |

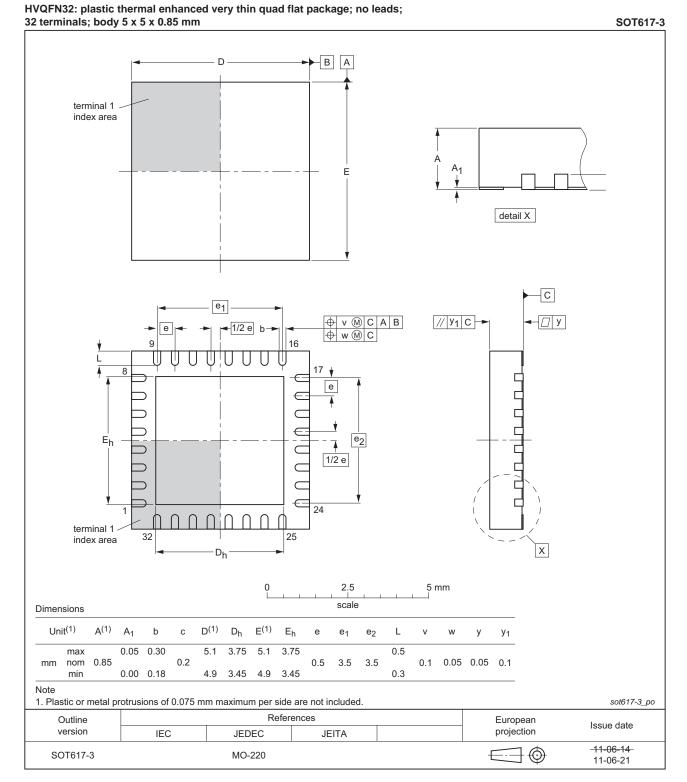

| IP4786CZ32          | HVQFN32                       | plastic thermal enhanced very thin quad flat package; no leads; 32 terminals; body $5 \times 5 \times 1$ mm | SOT617-3 |  |  |  |  |  |  |

#### DVI and HDMI interface ESD and overcurrent protection

# 5. Functional diagram

DVI and HDMI interface ESD and overcurrent protection

# 6. Pinning information

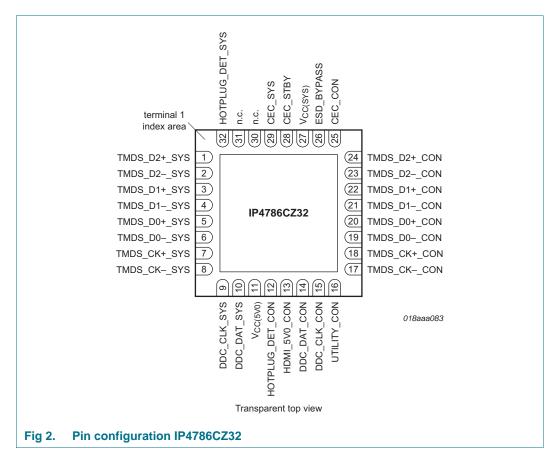

### 6.1 Pinning

### 6.2 Pin description

#### Pin description Table 2. Pin Name Description 1 TMDS\_D2+\_SYS TMDS to ASIC inside system 2 TMDS D2- SYS TMDS to ASIC inside system 3 TMDS\_D1+\_SYS TMDS to ASIC inside system 4 TMDS\_D1-\_SYS TMDS to ASIC inside system 5 TMDS\_D0+\_SYS TMDS to ASIC inside system 6 TMDS\_D0-\_SYS TMDS to ASIC inside system 7 TMDS\_CK+\_SYS TMDS to ASIC inside system 8 TMDS\_CK-\_SYS TMDS to ASIC inside system 9 DDC\_CLK\_SYS DDC clock system side DDC\_DAT\_SYS 10 DDC data system side 11 5 V supply input V<sub>CC(5V0)</sub> 12 HOTPLUG\_DET\_CON hot plug detect connector side 13 HDMI\_5V0\_CON 5 V overcurrent out to connector All information provided in this document is subject to legal disclaimers © NXP B.V. 2011. All rights reserved.

# DVI and HDMI interface ESD and overcurrent protection

| Table 2.  | Pin description continued |                                                                   |

|-----------|---------------------------|-------------------------------------------------------------------|

| Pin       | Name                      | Description                                                       |

| 14        | DDC_DAT_CON               | DDC data connector side                                           |

| 15        | DDC_CLK_CON               | DDC clock connector side                                          |

| 16        | UTILITY_CON               | utility line ESD protection                                       |

| 17        | TMDS_CKCON                | TMDS ESD protection to connector                                  |

| 18        | TMDS_CK+_CON              | TMDS ESD protection to connector                                  |

| 19        | TMDS_D0CON                | TMDS ESD protection to connector                                  |

| 20        | TMDS_D0+_CON              | TMDS ESD protection to connector                                  |

| 21        | TMDS_D1CON                | TMDS ESD protection to connector                                  |

| 22        | TMDS_D1+_CON              | TMDS ESD protection to connector                                  |

| 23        | TMDS_D2CON                | TMDS ESD protection to connector                                  |

| 24        | TMDS_D2+_CON              | TMDS ESD protection to connector                                  |

| 25        | CEC_CON                   | CEC signal connector side                                         |

| 26        | ESD_BYPASS                | ESD bias voltage                                                  |

| 27        | V <sub>CC(SYS)</sub>      | supply voltage for level shifting                                 |

| 28        | CEC_STBY                  | CEC Standby mode control (LOW for lowest<br>power, CEC-only mode) |

| 29        | CEC_SYS                   | CEC I/O signal system side                                        |

| 30        | n.c.                      | not connected                                                     |

| 31        | n.c.                      | not connected                                                     |

| 32        | HOTPLUG_DET_SYS           | hot plug detect system side                                       |

| ground pa | d GND                     | ground                                                            |

# 7. Limiting values

#### Table 3. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                                   | Parameter               | Conditions                                                                                                              |     | Min       | Max  | Unit |

|------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------|-----|-----------|------|------|

| V <sub>CC(5V0)</sub>                     | supply voltage (5.0 V)  |                                                                                                                         |     | GND - 0.5 | 6.5  | V    |

| VI                                       | input voltage           | I/O pins                                                                                                                |     | GND - 0.5 | 5.5  | V    |

| V <sub>ESD</sub>                         | electrostatic discharge | IEC 61000-4-2, level 4 (contact)                                                                                        | [1] | -         | ±8   | kV   |

|                                          | voltage                 | IEC 61000-4-2, level 1 (contact)                                                                                        | [2] | -         | ±2   | kV   |

| P <sub>tot</sub> total power dissipation |                         | DDC operating at 100 kHz;<br>CEC operating at 1 kHz;<br>50 % duty cycle; CEC_STBY = HIGH;<br>no current at HDMI_5V0_CON |     | -         | 50   | mW   |

|                                          |                         | DDC and CEC bus in idle mode;<br>CEC_STBY = HIGH;<br>no current at HDMI_5V0_CON                                         |     | -         | 3.0  | mW   |

|                                          |                         | DDC and CEC bus in idle mode;<br>CEC_STBY = LOW                                                                         |     | -         | 1.0  | mW   |

| T <sub>amb</sub>                         | ambient temperature     |                                                                                                                         |     | -25       | +85  | °C   |

| T <sub>stg</sub>                         | storage temperature     |                                                                                                                         |     | -55       | +125 | °C   |

[1] Connector-side pins (typically denoted with "\_CON" suffix) to ground.

[2] System-side pins: CEC\_SYS, DDC\_DAT\_SYS, DDC\_CLK\_SYS, HOTPLUG\_DET\_SYS, CEC\_STBY, V<sub>CC(SYS)</sub> and V<sub>CC(5V0)</sub>.

# 8. Static characteristics

#### Table 4. Supplies

$T_{amb} = -25 \ ^{\circ}C$  to +85  $\ ^{\circ}C$  unless otherwise specified.

| Symbol               | Parameter              | Conditions | Min            | Тур | Max | Unit |

|----------------------|------------------------|------------|----------------|-----|-----|------|

| V <sub>CC(5V0)</sub> | supply voltage (5.0 V) |            | <u>[1]</u> 4.5 | 5.0 | 6.5 | V    |

| V <sub>CC(SYS)</sub> | system supply voltage  |            | 1.62           | 3.3 | 5.5 | V    |

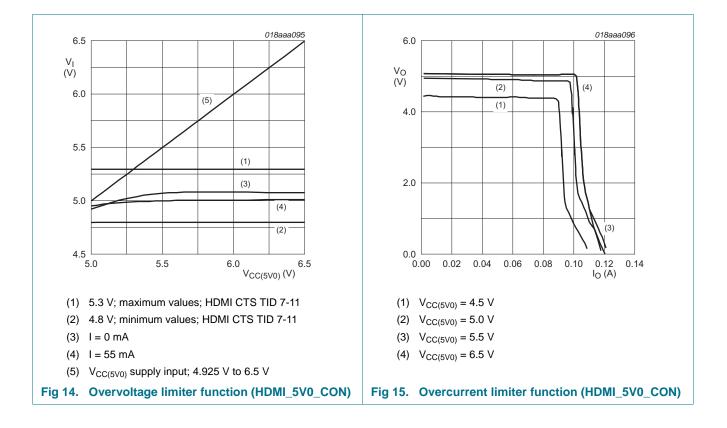

The IP4786CZ32 contains a 5 V voltage regulator function for higher input voltages. Any input voltage of 4.925 V < V<sub>CC(5V0)</sub> < 6.50 V will provide HDMI-compliant output levels of 4.8 V to 5.3 V on HDMI\_5V0\_CON.</li>

#### Table 5. TMDS protection circuit

$T_{amb} = -25 \ ^{\circ}C$  to +85  $\ ^{\circ}C$  unless otherwise specified.

|                             |                                                | •                                                                          |               |     |     |     |      |

|-----------------------------|------------------------------------------------|----------------------------------------------------------------------------|---------------|-----|-----|-----|------|

| Symbol                      | Parameter                                      | Conditions                                                                 |               | Min | Тур | Мах | Unit |

| TMDS chan                   | nel                                            |                                                                            |               |     |     |     |      |

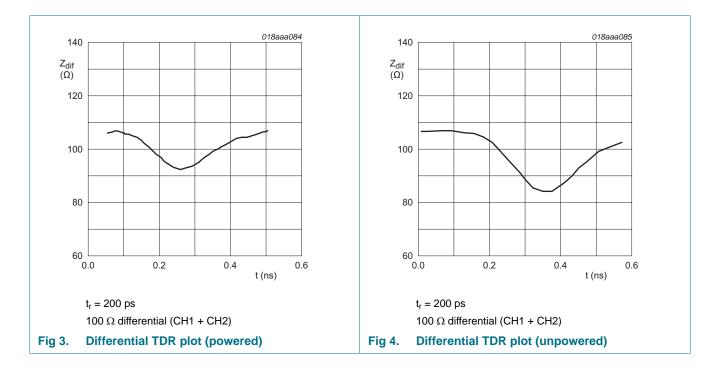

| Z <sub>i(dif)</sub>         | differential input<br>impedance                | TDR measured;<br>t <sub>r</sub> = 200 ps                                   |               | 90  | 100 | 110 | Ω    |

| C <sub>eff</sub>            | effective capacitance                          | equivalent shunt<br>capacitance for TDR<br>minimum; $t_r = 200 \text{ ps}$ | <u>[1][2]</u> | -   | 0.6 | -   | pF   |

| Protection of               | liode                                          |                                                                            |               |     |     |     |      |

| V <sub>BRzd</sub>           | Zener diode breakdown voltage                  | l = 1.0 mA                                                                 |               | 6.0 | -   | 9.0 | V    |

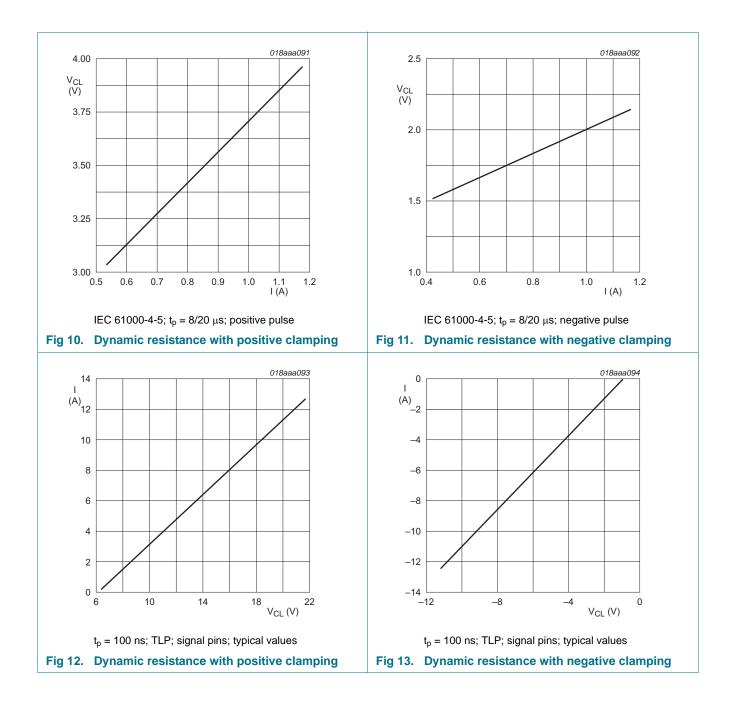

| r <sub>dyn</sub>            | dynamic resistance                             | surge; I = 1.0 A;<br>IEC 61000-4-5/9                                       |               |     |     |     |      |

|                             |                                                | positive transient                                                         |               | -   | 1.0 | -   | Ω    |

|                             |                                                | negative transient                                                         |               | -   | 1.0 | -   | Ω    |

|                             |                                                | TLP                                                                        |               |     |     |     |      |

|                             |                                                | positive transient                                                         | [3]           | -   | 1.0 | -   | Ω    |

|                             |                                                | negative transient                                                         | [3]           | -   | 1.0 | -   | Ω    |

| I <sub>bck</sub>            | back current                                   | $V_{CC(5V0)} < V_{ch(TMDS)}$                                               | [4][5]        | -   | 0.1 | 1.0 | μA   |

| I <sub>LR</sub>             | reverse leakage current                        | V <sub>I</sub> = 3.0 V                                                     |               | -   | 1.0 | -   | μA   |

| V <sub>F</sub>              | forward voltage                                |                                                                            |               | -   | 0.7 | -   | V    |

| V <sub>CL(ch)trt(pos)</sub> | positive transient channel<br>clamping voltage | 100 ns TLP; 50 $\Omega$ pulser at 50 ns                                    |               | -   | 8.0 | -   | V    |

|                             |                                                |                                                                            |               |     |     |     |      |

[1] This parameter is guaranteed by design.

[2] Capacitive dip at HDMI Time Domain Reflectometer (TDR) measurement conditions.

- [3] ANSI-ESDSP5.5.1-2004, ESD sensitivity testing Transmission Line Pulse (TLP) component level method 50 TDR.

- [4] Signal pins: TMDS\_D0+\_CON, TMDS\_D0-\_CON, TMDS\_D1+\_CON, TMDS\_D1-\_CON, TMDS\_D2+\_CON, TMDS\_D2-\_CON, TMDS\_CK+\_CON, TMDS\_CK-\_CON, TMDS\_D0+\_SYS, TMDS\_D0-\_SYS, TMDS\_D1+\_SYS, TMDS\_D1-\_SYS, TMDS\_D2+\_SYS, TMDS\_D2-\_SYS, TMDS\_CK+\_SYS and TMDS\_CK-\_SYS.

- [5] Backdrive current from TMDS\_x\_SYS and TMDS\_x\_CON pins to local V<sub>CC(5V0)</sub> bias rail at power-down. Device does not block backdrive current leakage through the device to/from ASIC I/O pins connected to TMDS\_x\_SYS pins.

#### **DVI and HDMI interface ESD and overcurrent protection**

| Symbol              | Parameter                    | Conditions                                                                                                                      |            | Min | Тур  | Max | Unit |

|---------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------|-----|------|-----|------|

| r <sub>dyn</sub>    | dynamic resistance           | TLP                                                                                                                             |            |     |      |     |      |

|                     |                              | positive transient                                                                                                              | <u>[1]</u> | -   | 1.0  | -   | Ω    |

|                     |                              | negative transient                                                                                                              | <u>[1]</u> | -   | 1.0  | -   | Ω    |

| V <sub>CL</sub>     | clamping voltage             | 100 ns TLP;<br>50 Ω pulser at 50 ns                                                                                             |            | -   | 8    | -   | V    |

| I <sub>O(max)</sub> | maximum output current       | $V_{(HDMI_5V0_CON)} = 4.8 V$                                                                                                    |            | 55  | -    | -   | mA   |

| I <sub>bck</sub>    | back current                 | $V_{CC(5V0)} < V_{(HDMI_5V0_CON)}$                                                                                              |            | -   | -    | 10  | μA   |

| I <sub>O(sc)</sub>  | short-circuit output current | $V_{(HDMI_5V0_CON)} = 0 V$                                                                                                      |            | -   | 125  | 175 | mA   |

| V <sub>do</sub>     | dropout voltage              | 4.5 V < V <sub>CC(5V0)</sub> < 4.925 V;<br>DDC = LOW                                                                            | [2]        |     |      |     |      |

|                     |                              | l <sub>O</sub> = 10 mA                                                                                                          |            | -   | 70   | -   | mV   |

|                     |                              | l <sub>O</sub> = 55 mA                                                                                                          |            | -   | -    | 125 | mV   |

| V <sub>O(LDO)</sub> | LDO output voltage           | $      I_O \le 55 \text{ mA}; \\       4.925 \text{ V} < \text{V}_{CC(5\text{V0})} < 6.5 \text{ V}; \\       DDC = \text{LOW} $ | [2]        | 4.8 | 5.05 | 5.3 | V    |

#### Table 6. HDMI\_5V0\_CON

25 °C to 185 °C unless otherwise specified

[1] ANSI-ESDSP5.5.1-2004, ESD sensitivity testing TLP component level method 50 TDR.

[2] The IP4786CZ32 contains a 5 V voltage regulator function for higher input voltages. Any input voltage of 4.925 V < V<sub>CC(5V0)</sub> < 6.50 V will provide HDMI-compliant output levels of 4.8 V to 5.3 V on HDMI\_5V0\_CON.

#### Table 7. UTILITY\_CON

| $T_{amb} = -2$ | 5 $^{\circ}$ C to +85 $^{\circ}$ C unles | s otherwise specified. |  |

|----------------|------------------------------------------|------------------------|--|

| Symbol         | Parameter                                | Conditions             |  |

| Supplies       | · nins Veerse and                        | Veryover               |  |

| Supplie          | es: pins $V_{CC(5V0)}$ and $V_{CC(S)}$ | YS)                                        |              |     |     |    |

|------------------|----------------------------------------|--------------------------------------------|--------------|-----|-----|----|

| r <sub>dyn</sub> | dynamic resistance                     | TLP                                        |              |     |     |    |

|                  |                                        | positive transient                         | <u>[1]</u> - | 1.0 | -   | Ω  |

|                  |                                        | negative transient                         | <u>[1]</u> - | 1.0 | -   | Ω  |

| V <sub>CL</sub>  | clamping voltage                       | 100 ns TLP;<br>50 $\Omega$ pulser at 50 ns | -            | 8.0 | -   | V  |

| Ci               | input capacitance                      |                                            | -            | 8.0 | 10  | pF |

| $R_{pd}$         | pull-down resistance                   |                                            | 60           | 100 | 140 | kΩ |

[1] ANSI-ESDSP5.5.1-2004, ESD sensitivity testing TLP component level method 50 TDR.

Min Typ Max Unit

### DVI and HDMI interface ESD and overcurrent protection

|                 |                                            |                                                                                                                                      |               | Min                                                             | Тур | Max                                                                                     | Unit |

|-----------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------|------|

| DDC buff        | er on connector side[1]                    |                                                                                                                                      |               |                                                                 |     |                                                                                         |      |

| V <sub>IH</sub> | HIGH-level input voltage                   |                                                                                                                                      |               | 0.5 ×                                                           | -   | 6.5                                                                                     | V    |

|                 |                                            |                                                                                                                                      |               | V <sub>(HDMI_5V0_CON)</sub>                                     |     |                                                                                         |      |

| VIL             | LOW-level input voltage                    |                                                                                                                                      |               | -0.5                                                            | -   | $\begin{array}{l} 0.3 \times \\ V_{(\text{HDMI}_5 \text{V0}_C \text{CON})} \end{array}$ | V    |

| V <sub>он</sub> | HIGH-level output voltage                  |                                                                                                                                      | [2]           | $\begin{array}{c} V_{(HDMI\_5V0\_CON)} \\ - \ 0.02 \end{array}$ | -   | V <sub>(HDMI_5V0_CON)</sub><br>+ 0.02                                                   | V    |

| V <sub>OL</sub> | LOW-level output voltage                   | internal pull-up and external sink                                                                                                   |               | -                                                               | 100 | 200                                                                                     | mV   |

| V <sub>IK</sub> | input clamping voltage                     | I <sub>I</sub> = -18 mA                                                                                                              |               | -                                                               | -   | -1.0                                                                                    | V    |

| C <sub>IO</sub> | input/output capacitance                   | $\label{eq:V_CC(5V0)} \begin{split} V_{CC(5V0)} &= 5.0 \text{ V}; \\ V_{CC(SYS)} &= 3.3 \text{ V}; \\ CEC\_STBY &= HIGH \end{split}$ | <u>[2][3]</u> | -                                                               | 8.0 | 10                                                                                      | pF   |

| R <sub>pu</sub> | pull-up resistance                         |                                                                                                                                      |               | 1.6                                                             | 1.8 | 2.0                                                                                     | kΩ   |

| DDC buff        | er on system side <u><sup>[1][4]</sup></u> |                                                                                                                                      |               |                                                                 |     |                                                                                         |      |

| V <sub>IH</sub> | HIGH-level input voltage                   | $V_{CC(SYS)} = 1.8 V$                                                                                                                |               | 450                                                             | -   | -                                                                                       | mV   |

|                 |                                            | $V_{CC(SYS)} = 2.5 V$                                                                                                                |               | 620                                                             | -   | -                                                                                       | mV   |

|                 |                                            | $V_{CC(SYS)} = 3.3 V$                                                                                                                |               | 760                                                             | -   | -                                                                                       | mV   |

|                 |                                            | $V_{CC(SYS)} = 5.0 V$                                                                                                                |               | 800                                                             | -   | -                                                                                       | mV   |

| VIL             | LOW-level input voltage                    | $V_{CC(SYS)} = 1.8 V$                                                                                                                |               | -                                                               | -   | 330                                                                                     | mV   |

|                 |                                            | $V_{CC(SYS)} = 2.5 V$                                                                                                                |               | -                                                               | -   | 370                                                                                     | mV   |

|                 |                                            | $V_{CC(SYS)} = 3.3 V$                                                                                                                |               | -                                                               | -   | 390                                                                                     | mV   |

|                 |                                            | $V_{CC(SYS)} = 5.0 V$                                                                                                                |               | -                                                               | -   | 410                                                                                     | mV   |

| V <sub>OH</sub> | HIGH-level output voltage                  |                                                                                                                                      | [2]           | $V_{CC(SYS)}-0.02$                                              | -   | $V_{CC(SYS)}$ + 0.02                                                                    | V    |

| / <sub>OL</sub> | LOW-level output voltage                   | $V_{CC(SYS)} = 1.8 V$                                                                                                                |               | -                                                               | -   | 500                                                                                     | mV   |

|                 |                                            | $V_{CC(SYS)} = 2.5 V$                                                                                                                |               | -                                                               | -   | 700                                                                                     | mV   |

|                 |                                            | $V_{CC(SYS)} = 3.3 V$                                                                                                                |               | -                                                               | -   | 810                                                                                     | mV   |

|                 |                                            | $V_{CC(SYS)} = 5.0 V$                                                                                                                |               | -                                                               | -   | 850                                                                                     | mV   |

| V <sub>IK</sub> | input clamping voltage                     | $I_{I} = -18 \text{ mA}$                                                                                                             |               | -                                                               | -   | -1.0                                                                                    | V    |

| Сю              | input/output capacitance                   |                                                                                                                                      | [2]           | -                                                               | 6.0 | 8.0                                                                                     | pF   |

|                 |                                            | f = 100 kHz                                                                                                                          |               |                                                                 |     |                                                                                         |      |

#### Table 8. **Static characteristics**

IP4786CZ32 **Product data sheet**

### DVI and HDMI interface ESD and overcurrent protection

| Symbol                                | Parameter                 | Conditions                                                                                                                                                    |     | Min                | Тур  | Max                  | Unit |

|---------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|------|----------------------|------|

| CEC_CO                                | N[1]                      |                                                                                                                                                               |     |                    |      |                      |      |

| VIH                                   | HIGH-level input voltage  |                                                                                                                                                               |     | 2.0                | -    | -                    | V    |

| V <sub>IL</sub>                       | LOW-level input voltage   |                                                                                                                                                               |     | -                  | -    | 0.80                 | V    |

| V <sub>OH</sub>                       | HIGH-level output voltage |                                                                                                                                                               |     | 2.88               | 3.3  | 3.63                 | V    |

| V <sub>OL</sub>                       | LOW-level output voltage  | I <sub>OL</sub> = 1.5 mA                                                                                                                                      |     | -                  | 100  | 200                  | mV   |

| C <sub>IO</sub>                       | input/output capacitance  | $\begin{split} &V_{CC(5V0)} = 0 \ V; \\ &V_{CC(SYS)} = 0 \ V; \\ &V_{bias} = 2.5 \ V; \\ &AC \ input = 3.5 \ V_{(p-p)}; \\ &f = 100 \ kHz \end{split}$        | [2] | -                  | 8.0  | 10                   | pF   |

| R <sub>pu</sub>                       | pull-up resistance        |                                                                                                                                                               |     | 23.4               | 26.0 | 28.6                 | kΩ   |

| CEC_SYS                               | <u>5[1][4]</u>            |                                                                                                                                                               |     |                    |      |                      |      |

| VIH                                   | HIGH-level input voltage  | $V_{CC(SYS)} = 1.8 V$                                                                                                                                         |     | 450                | -    | -                    | mV   |

|                                       |                           | $V_{CC(SYS)} = 2.5 V$                                                                                                                                         |     | 620                | -    | -                    | mV   |

|                                       |                           | $V_{CC(SYS)} = 3.3 V$                                                                                                                                         |     | 760                | -    | -                    | mV   |

|                                       |                           | $V_{CC(SYS)} = 5.0 V$                                                                                                                                         |     | 800                | -    | -                    | mV   |

| V <sub>IL</sub> LOW-level input volta | LOW-level input voltage   | $V_{CC(SYS)} = 1.8 V$                                                                                                                                         |     | -                  | -    | 330                  | mV   |

|                                       |                           | $V_{CC(SYS)} = 2.5 V$                                                                                                                                         |     | -                  | -    | 370                  | mV   |

|                                       |                           | $V_{CC(SYS)} = 3.3 V$                                                                                                                                         |     | -                  | -    | 390                  | mV   |

|                                       |                           | $V_{CC(SYS)} = 5.0 V$                                                                                                                                         |     | -                  | -    | 410                  | mV   |

| V <sub>OH</sub>                       | HIGH-level output voltage |                                                                                                                                                               | [2] | $V_{CC(SYS)}-0.02$ | -    | $V_{CC(SYS)} + 0.02$ | V    |

| V <sub>OL</sub>                       | LOW-level output voltage  | $V_{CC(SYS)} = 1.8 V$                                                                                                                                         |     | -                  | -    | 500                  | mV   |

|                                       |                           | $V_{CC(SYS)} = 2.5 V$                                                                                                                                         |     | -                  | -    | 700                  | mV   |

|                                       |                           | $V_{CC(SYS)} = 3.3 V$                                                                                                                                         |     | -                  | -    | 810                  | mV   |

|                                       |                           | $V_{CC(SYS)} = 5.0 V$                                                                                                                                         |     | -                  | -    | 850                  | mV   |

| C <sub>IO</sub>                       | input/output capacitance  | $\begin{split} &V_{CC(5V0)} = 0 \ V; \\ &V_{CC(SYS)} = 0 \ V; \\ &V_{bias} = 2.5 \ V; \\ &AC \ input = 3.5 \ V_{(p-p)}; \\ &f = 100 \ \text{kHz} \end{split}$ | [2] | -                  | 6.0  | 7.0                  | pF   |

| R <sub>pu</sub>                       | pull-up resistance        |                                                                                                                                                               |     | 8.5                | 10   | 11.5                 | kΩ   |

| HOTPLU                                | G_DET_CON <sup>[1]</sup>  |                                                                                                                                                               |     |                    |      |                      |      |

| V <sub>IH</sub>                       | HIGH-level input voltage  |                                                                                                                                                               |     | 2.0                | -    | -                    | V    |

| V <sub>IL</sub>                       | LOW-level input voltage   |                                                                                                                                                               |     | -                  | -    | 0.8                  | V    |

| R <sub>pd</sub>                       | pull-down resistance      |                                                                                                                                                               |     | 60                 | 100  | 140                  | kΩ   |

| Ci                                    | input capacitance         |                                                                                                                                                               | [2] | -                  | 8.0  | 10                   | pF   |

#### Table 8. Static characteristics ... continued

#### **DVI and HDMI interface ESD and overcurrent protection**

| $T_{amb} = -2\xi$ | 5 $^{\circ}$ C to +85 $^{\circ}$ C unless other |                          |                         |     |     |      |

|-------------------|-------------------------------------------------|--------------------------|-------------------------|-----|-----|------|

| Symbol            | Parameter                                       | Conditions               | Min                     | Тур | Max | Unit |

| HOTPLU            | G_DET_SYS <sup>[1]</sup>                        |                          |                         |     |     |      |

| V <sub>OH</sub>   | HIGH-level output voltage                       | I <sub>OL</sub> = 1 mA   | $0.7\times V_{CC(SYS)}$ | -   | -   | V    |

| V <sub>OL</sub>   | LOW-level output voltage                        | $I_{OL} = -1 \text{ mA}$ | -                       | 200 | 300 | mV   |

| R <sub>pd</sub>   | pull-down resistance                            |                          | 60                      | 100 | 140 | kΩ   |

Table 8 Static characteristics continued

[1] The device is active if the input voltage at pin CEC\_STBY is above the HIGH level.

[2] This parameter is guaranteed by design.

Capacitive load measured at power-on. [3]

No external pull-up resistor attached. [4]

#### Table 9. **CEC\_STBY** power management circuit

$V_{CC(SYS)} = 1.62 \text{ V to } 5.5 \text{ V}; V_{CC(5V0)} = 4.5 \text{ V to } 6.5 \text{ V}; \text{ GND} = 0 \text{ V}; T_{amb} = -25 \text{ }^{\circ}\text{C} \text{ to } +85 \text{ }^{\circ}\text{C} \text{ unless otherwise specified.}$

| Symbol          | Parameter                | Conditions                  | Min             | Тур | Max | Unit |

|-----------------|--------------------------|-----------------------------|-----------------|-----|-----|------|

| Board side      | : input pin CEC_STBY[1]  |                             |                 |     |     |      |

| V <sub>IH</sub> | HIGH-level input voltage | HIGH = active               | [2] 1.2         | -   | 6.5 | V    |

| V <sub>IL</sub> | LOW-level input voltage  | LOW = standby               | <u>[3]</u> –0.5 | -   | 0.8 | V    |

| R <sub>pd</sub> | pull-down resistance     |                             | 60              | 100 | 140 | kΩ   |

| Ci              | input capacitance        | $V_I = 3 V \text{ or } 0 V$ | -               | 6   | 7   | pF   |

[1] The CEC\_STBY pin should be connected permanently to V<sub>CC(5V0)</sub> or V<sub>CC(SYS)</sub> if no enable control is needed.

[2] DDC buffers, Hot Plug Detect (HPD) buffer, and HDMI\_5V0\_CON out enabled; CEC buffer enabled.

DDC buffers, HPD buffer, and HDMI\_5V0\_CON out disabled; CEC buffer enabled. [3]

# 9. Dynamic characteristics

#### Table 10. Dynamic characteristics

$V_{CC(5V0)} = 5.0$  V;  $V_{CC(SYS)} = 1.8$  V; GND = 0 V;  $T_{amb} = -25$  °C to +85 °C unless otherwise specified.

| Symbol                                                            | Parameter                     | Conditions                              | Min | Тур | Max | Unit |

|-------------------------------------------------------------------|-------------------------------|-----------------------------------------|-----|-----|-----|------|

| DDC_DAT_SYS, DDC_CLK_SYS, DDC_DAT_CON, DDC_CLK_CON <sup>[1]</sup> |                               |                                         |     |     |     |      |

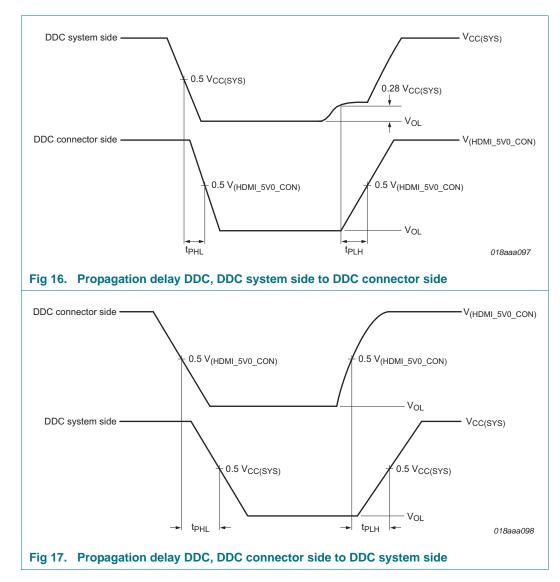

| t <sub>PLH</sub>                                                  | LOW to HIGH propagation delay | system side to connector side Figure 16 | -   | 80  | -   | ns   |

| t <sub>PHL</sub>                                                  | HIGH to LOW propagation delay | system side to connector side Figure 16 | -   | 60  | -   | ns   |

| t <sub>PLH</sub>                                                  | LOW to HIGH propagation delay | connector side to system side Figure 17 | -   | 120 | -   | ns   |

| t <sub>PHL</sub>                                                  | HIGH to LOW propagation delay | connector side to system side Figure 17 | -   | 80  | -   | ns   |

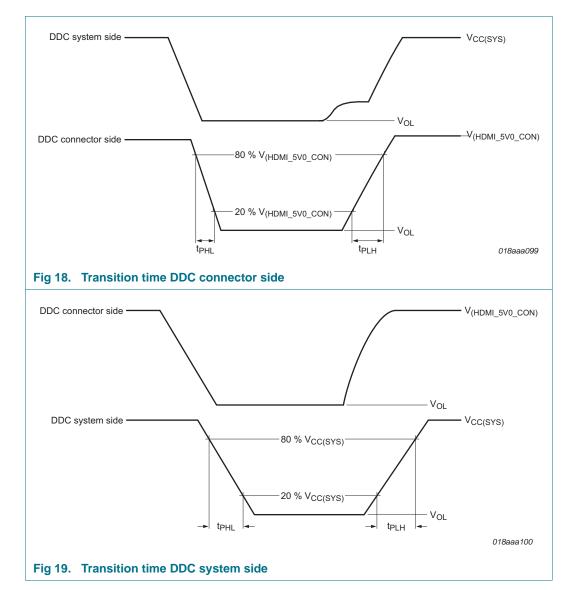

| t <sub>TLH</sub>                                                  | LOW to HIGH transition time   | connector side Figure 18                | -   | 150 | -   | ns   |

| t <sub>THL</sub>                                                  | HIGH to LOW transition time   | connector side Figure 18                | -   | 100 | -   | ns   |

| t <sub>TLH</sub>                                                  | LOW to HIGH transition time   | system side Figure 19                   | -   | 250 | -   | ns   |

| t <sub>THL</sub>                                                  | HIGH to LOW transition time   | system side Figure 19                   | -   | 80  | -   | ns   |

[1] All dynamic measurements are done with a 75 pF load. Rise times are determined by internal pull-up resistors.

# **NXP Semiconductors**

# IP4786CZ32

#### DVI and HDMI interface ESD and overcurrent protection

### DVI and HDMI interface ESD and overcurrent protection

# **NXP Semiconductors**

# IP4786CZ32

#### DVI and HDMI interface ESD and overcurrent protection

# **NXP Semiconductors**

# IP4786CZ32

#### **DVI and HDMI interface ESD and overcurrent protection**

**DVI and HDMI interface ESD and overcurrent protection**

# 10. AC waveforms

# 10.1 DDC propagation delay

#### **DVI and HDMI interface ESD and overcurrent protection**

# **10.2 DDC transition time**

P4786CZ32 Product data sheet

# **11.** Application information

### 11.1 TMDS ESD

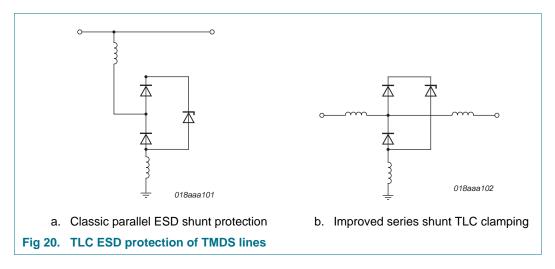

To protect the TMDS lines and also to comply with the impedance requirements of the HDMI specification, the IP4786CZ32 provides ESD protection with matched TLC ESD structures. Typical Dual Rail Clamp (DRC) or rail-to-rail shunt structures are common for low-capacitance ESD protection (as shown on the left side of Figure 20) where the dominant factor for the TMDS line impedance dip is determined by the capacitive load to ground. Parasitic lead inductances of the packaging in this case works against the ESD clamping performance by including the  $\Delta I/\Delta t$  reactance of the inductance into the path of the ESD shunt.

The IP4786CZ32 utilizes these inherent inductances in series with the transmission line in order to present an effective capacitive load of roughly only 0.7 pF. This TLC structure minimizes the capacitive dip, for ideal signal integrity (Figure 20; right side) without complicated PCB pre-compensation. As a beneficial side effect, this enhances the ESD performance of the device as well, since the reactance of the series inductance attenuates the fast initial peak of the ESD pulse, for a lower residual pulse delivered to the Application Specific Integrated Circuit (ASIC).

IP4786CZ32 Product data sheet

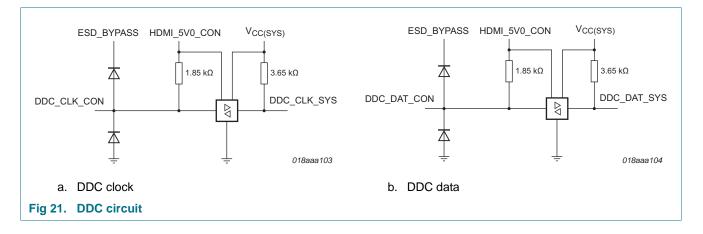

### 11.2 DDC circuit

The DDC bus circuit integrates all required pull-ups, and provides full capacitive decoupling between the HDMI connector and the DDC bus lines on the PCB. The capacitive decoupling ensures that the maximum capacitive load is well within the 50 pF maximum of the HDMI specification. No external pull-ups or pull-downs are required.

The bidirectional buffers support high-capacitive load on the HDMI cable-side. Various non-compliant but prevalent low-cost cables have been observed with a capacitive load of up to 6 nF on the DDC lines, far exceeding the 700 pF HDMI limit. The IP4786CZ32 can easily decouple this from the weaker ASIC I/O buffers, and drive the rogue cable successfully.

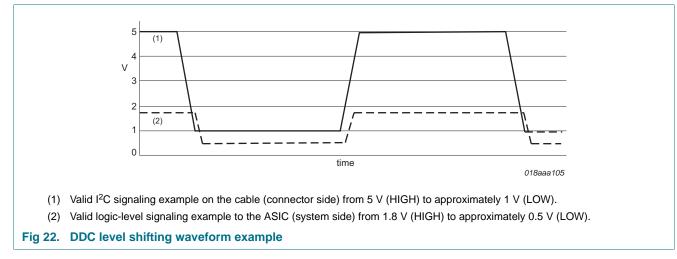

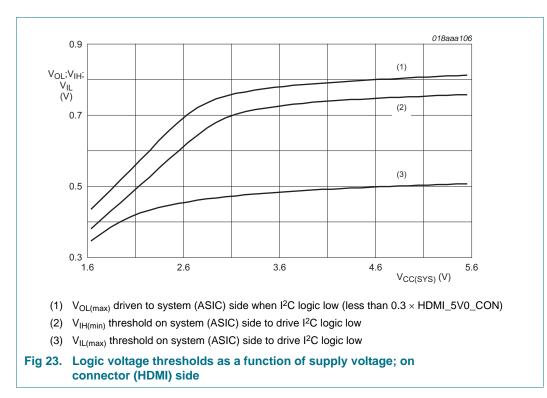

# 11.3 Logic low I<sup>2</sup>C voltage shifter

The DDC buffers provide an additional feature commonly required for high-integration HDMI ASICs which are limited to CMOS or LVTTL LOW-level input voltage (V<sub>IL</sub>) on their available I/O buffer cells. These I/Os are not strictly compliant with the 0.3 V<sub>DD</sub> threshold voltage levels of I<sup>2</sup>C and may miss intended logic low levels on the cable between 0.8 V and 1.5 V (typical values).

This feature is also included in the CEC buffer, and thus allows standard I/O buffer cells to be used in ASICs and microcontrollers.

P4786CZ32 Product data sheet

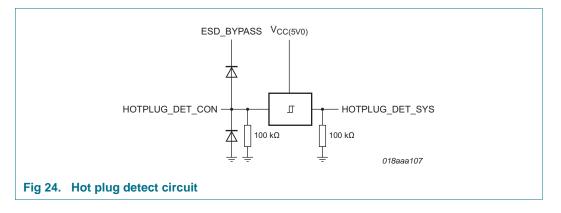

### 11.4 Hot plug detect circuit and HEAC support

The IP4786CZ32 includes a hot plug detect circuit that simplifies the hot plug application. The circuit generates a standard logic level from the hot plug signal.

The hot plug detect circuit is pulling down the signal to avoid any floating signal. The comparator guarantees a save detection of the 2 V hot plug signal without any glitches or oscillation at the hot plug output.

The IP4786CZ32 also provides an additional ESD pin to protect the reserved / HEAC pin along with hot plug detect to 8 kV IEC 61000-4-2, level 4.

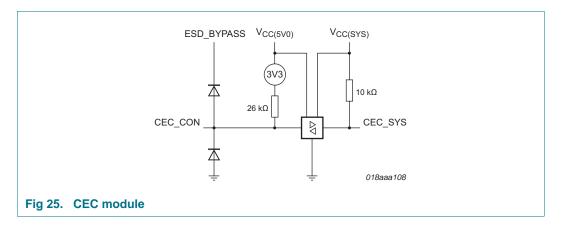

### 11.5 CEC

The logical multidrop topology of the CEC bus can include complex physical stubs, loading cables, and interconnects that may deteriorate signal quality. The IP4786CZ32 includes a full bidirectional buffer to drive the CEC bus and isolate the CEC microcontroller or ASIC General-Purpose Input/Output (GPIO).

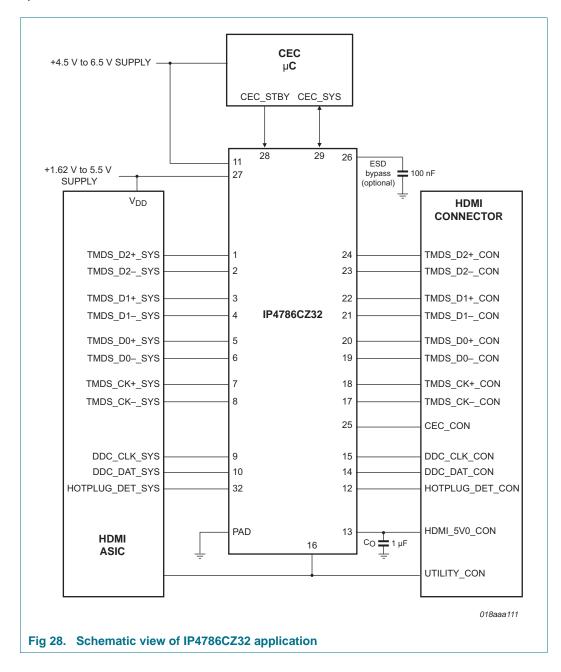

The CEC buffer derives power from an on-board 3.3 V regulator from the V<sub>CC(5V0)</sub> domain (see <u>Figure 25</u>). This allows extensive system power management configurations and guarantees an HDMI-compliant V<sub>(CEC\_CON)</sub> on the connector, as well as the backdrive-protected 125  $\mu$ A nominal CEC pull-up which does not degrade the bus when powered down.

By placing the CEC microcontroller and  $V_{CC(5V0)}$  input on a 5 V rail as shown in Figure 28, the CEC microcontroller can communicate over CEC for power commands, and then enable the HDMI port via the CEC\_STBY pin, as well as the rest of the system as needed.

If IP4786CZ32 Standby modes are not required, or if the Power-down modes are not desired, the CEC\_STBY pin can be pulled HIGH to  $V_{CC(5V0)}$  or  $V_{CC(SYS)}$  for continuous HDMI and CEC operation.

Strapping the CEC\_STBY =  $V_{CC(SYS)} = V_{DD}$  of ASIC guarantees that all interface signals ending with the suffix "\_SYS" on the system side will be disabled when  $V_{CC(SYS)}$  goes low, protecting the ASIC I/O signals from exceeding its local  $V_{DD}$ . In this mode, even if  $V_{CC(5V0)}$ is powered, HDMI\_5V0\_CON go active and hot plug events can be detected only when the ASIC power supply rail is on.

Strapping CEC\_STBY =  $V_{CC(5V0)}$  is the most basic configuration where the buffers are enabled whenever the local  $V_{CC(5V0)}$  and  $V_{CC(SYS)}$  supplies reach minimum operating levels.

All information provided in this document is subject to legal disclaimers

DVI and HDMI interface ESD and overcurrent protection

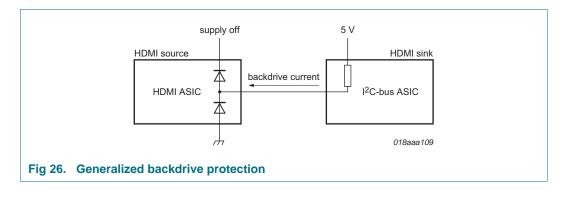

# **11.6 Backdrive protection**

The HDMI connector contains various signals which can partly supply current into an HDMI device that is powered down.

Typically, the DDC lines and the CEC signals can force significant current back into the powered-down rails as shown in <u>Figure 26</u>, causing power-on reset problems with the system, and possible damage. The IP4786CZ32 prevents this backdrive condition whenever the I/O voltage is greater than the local supply.

### 11.7 55 mA overcurrent / overvoltage LDO function

The IP4786CZ32 integrates a complete linear output overcurrent protection to isolate faults from the source power supply, while still meeting HDMI output specifications.

The Low DropOut (LDO) design provides a low-cost solution requiring just a single output capacitor (1  $\mu$ F or higher, Equivalent Series Resistance (ESR) < 1  $\Omega$ ), eliminating start-up and ripple concerns (see Figure 27).

A typical 100 mV V<sub>do</sub> overcurrent-only solution would require a 5.1 V  $\pm$  3 % input supply to guarantee 4.8 V to 5.3 V over 0 mA to 55 mA at the HDMI connector. The overcurrent / overvoltage feature of the IP4786CZ32 allows the use of wider tolerance input supplies up to 6.5 V while still meeting the 4.8 V-to-5.3 V output limit required by HDMI. This means, for example, a cost-reduced 5.2 V  $\pm$  5 % or even a 5.5 V  $\pm$  10 % supply can be used with the IP4786CZ32.

As with all the I/O pins, this block is ESD-protected and also provides backdrive protection when a rogue HDMI sink powers the HDMI cable unexpectedly.

IP4786CZ32

24 of 35

### 11.8 Schematic view of application

Only a single external component ( $C_0 = 1 \ \mu F$ ) is required to protect and interface the ASIC to a complete and compliant HDMI port. The 100 nF ESD bypass capacitor is optional.

# **11.9 Typical application**

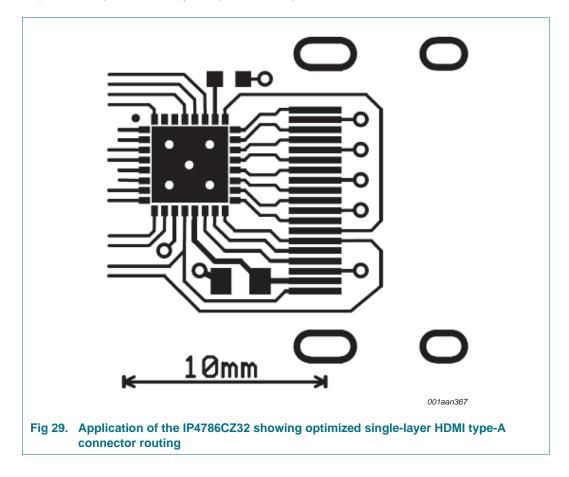

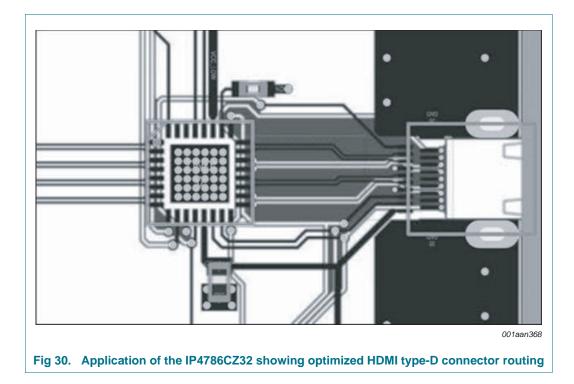

The IP4786CZ32 is designed to simplify routing to the HDMI connector, and ease the incorporation of high-level ESD protection into delicately balanced high-speed TMDS lines. These lines rely on tightly controlled microstrip or stripline transmission lines with minimal impedance discontinuities, which can deteriorate return loss, increase deterministic jitter and generally erode overall link signal integrity.

Normally when designing the PCB with standard shunt ESD clamps, careful consideration must be given to manual pre-compensation of the additional load of the added ESD component. With the IP4786CZ32 TLCs, the ESD suppressor is designed to maintain the characteristic impedance of the PCB microstrip or stripline, and therefore the designer needs only be concerned with the standard-controlled impedance of the unloaded PCB lines. This simplifies the task of the PCB designer, and minimizes the tuning cycles, which are sometimes required when pre-compensation misses the mark. A basic application diagram for the ESD protection of an HDMI interface is shown in Figure 29 and Figure 30 for type-A and type-D HDMI connector versions.

The optimized HVQFN32 pinning simplifies the PCB design to keep the ESD protection close to the connector where it can minimize the coupling of the ESD pulse onto other lines in the system during a strike.

Due to the integrated pull-up and pull-down resistors, only two external capacitors are required to implement a fully compliant HDMI port.

DVI and HDMI interface ESD and overcurrent protection

### **NXP Semiconductors**

# IP4786CZ32

### DVI and HDMI interface ESD and overcurrent protection

# 12. Package outline

#### Fig 31. Package outline SOT617-3 (HVQFN32)

All information provided in this document is subject to legal disclaimers.

# 13. Soldering of SMD packages

This text provides a very brief insight into a complex technology. A more in-depth account of soldering ICs can be found in Application Note *AN10365* "Surface mount reflow soldering description".

### 13.1 Introduction to soldering

Soldering is one of the most common methods through which packages are attached to Printed Circuit Boards (PCBs), to form electrical circuits. The soldered joint provides both the mechanical and the electrical connection. There is no single soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and Surface Mount Devices (SMDs) are mixed on one printed wiring board; however, it is not suitable for fine pitch SMDs. Reflow soldering is ideal for the small pitches and high densities that come with increased miniaturization.

# 13.2 Wave and reflow soldering

Wave soldering is a joining technology in which the joints are made by solder coming from a standing wave of liquid solder. The wave soldering process is suitable for the following:

- Through-hole components

- Leaded or leadless SMDs, which are glued to the surface of the printed circuit board

Not all SMDs can be wave soldered. Packages with solder balls, and some leadless packages which have solder lands underneath the body, cannot be wave soldered. Also, leaded SMDs with leads having a pitch smaller than ~0.6 mm cannot be wave soldered, due to an increased probability of bridging.

The reflow soldering process involves applying solder paste to a board, followed by component placement and exposure to a temperature profile. Leaded packages, packages with solder balls, and leadless packages are all reflow solderable.

Key characteristics in both wave and reflow soldering are:

- Board specifications, including the board finish, solder masks and vias

- · Package footprints, including solder thieves and orientation

- · The moisture sensitivity level of the packages

- Package placement

- Inspection and repair

- Lead-free soldering versus SnPb soldering

### 13.3 Wave soldering

Key characteristics in wave soldering are:

- Process issues, such as application of adhesive and flux, clinching of leads, board transport, the solder wave parameters, and the time during which components are exposed to the wave

- Solder bath specifications, including temperature and impurities

### 13.4 Reflow soldering

Key characteristics in reflow soldering are:

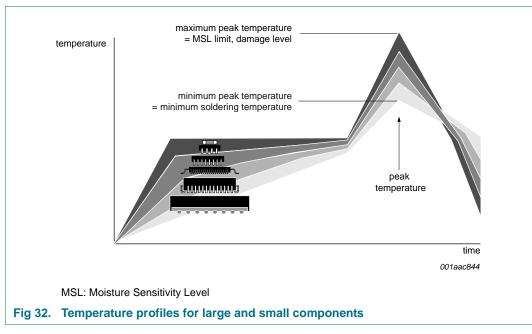

- Lead-free versus SnPb soldering; note that a lead-free reflow process usually leads to higher minimum peak temperatures (see <u>Figure 32</u>) than a SnPb process, thus reducing the process window

- Solder paste printing issues including smearing, release, and adjusting the process window for a mix of large and small components on one board

- Reflow temperature profile; this profile includes preheat, reflow (in which the board is heated to the peak temperature) and cooling down. It is imperative that the peak temperature is high enough for the solder to make reliable solder joints (a solder paste characteristic). In addition, the peak temperature must be low enough that the packages and/or boards are not damaged. The peak temperature of the package depends on package thickness and volume and is classified in accordance with Table 11 and 12

#### Table 11. SnPb eutectic process (from J-STD-020C)

| Package thickness (mm) | Package reflow temperature (°C) |       |  |

|------------------------|---------------------------------|-------|--|

|                        | Volume (mm <sup>3</sup> )       |       |  |

|                        | < 350                           | ≥ 350 |  |

| < 2.5                  | 235                             | 220   |  |

| ≥ 2.5                  | 220                             | 220   |  |

#### Table 12. Lead-free process (from J-STD-020C)

| Package thickness (mm) | Package reflow temperature (°C)<br>Volume (mm <sup>3</sup> ) |             |        |  |

|------------------------|--------------------------------------------------------------|-------------|--------|--|

|                        |                                                              |             |        |  |

|                        | < 350                                                        | 350 to 2000 | > 2000 |  |

| < 1.6                  | 260                                                          | 260         | 260    |  |

| 1.6 to 2.5             | 260                                                          | 250         | 245    |  |

| > 2.5                  | 250                                                          | 245         | 245    |  |

Moisture sensitivity precautions, as indicated on the packing, must be respected at all times.

Studies have shown that small packages reach higher temperatures during reflow soldering, see Figure 32.

**DVI and HDMI interface ESD and overcurrent protection**

For further information on temperature profiles, refer to Application Note *AN10365 "Surface mount reflow soldering description"*.

# 14. Glossary

HDMI sink — Device which receives HDMI signals e.g. a TV set. HDMI source — Device which transmit HDMI signal e.g. DVD player.

31 of 35

# **15. Revision history**

| Document ID    | Release date                      | Data sheet status                 | Change notice | Supersedes     |

|----------------|-----------------------------------|-----------------------------------|---------------|----------------|

| IP4786CZ32 v.2 | 20111021                          | Product data sheet                | -             | IP4786CZ32 v.1 |

| Modifications: | • <u>Figure 3, 4</u> a            | nd 21: corrected                  |               |                |

|                | <ul> <li>Section 16 "L</li> </ul> | <u>egal information</u> : updated |               |                |

| IP4786CZ32 v.1 | 20110415                          | Product data sheet                | -             | -              |

# **16. Legal information**

### 16.1 Data sheet status

| Document status[1][2]          | Product status <sup>[3]</sup> | Definition                                                                            |

|--------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development                   | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification                 | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production                    | This document contains the product specification.                                     |

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term 'short data sheet' is explained in section "Definitions".

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

### 16.2 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

# 16.3 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

33 of 35

#### DVI and HDMI interface ESD and overcurrent protection

**Non-automotive qualified products** — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

# 16.4 Licenses

#### Purchase of NXP ICs with HDMI technology

Use of an NXP IC with HDMI technology in equipment that complies with the HDMI standard requires a license from HDMI Licensing LLC, 1060 E. Arques Avenue Suite 100, Sunnyvale CA 94085, USA, e-mail: admin@hdmi.org.

### 16.5 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

17. Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

### **NXP Semiconductors**

# IP4786CZ32

DVI and HDMI interface ESD and overcurrent protection

# **18. Contents**

| 1    | General description                           | . 1       |

|------|-----------------------------------------------|-----------|

| 2    | Features and benefits                         | . 1       |

| 3    | Applications                                  | . 2       |

| 4    | Ordering information                          |           |

| 5    | Functional diagram                            |           |

| 6    | Pinning information                           |           |

| 6.1  | Pinning                                       |           |

| 6.2  | Pin description                               |           |

| 7    | Limiting values                               |           |

| 8    | Static characteristics                        |           |

| 9    | Dynamic characteristics                       |           |

| 10   | AC waveforms                                  | 17        |

| 10.1 | DDC propagation delay                         | 17        |

| 10.2 | DDC transition time                           | 18        |

| 11   | Application information.                      | 19        |

| 11.1 | TMDS ESD                                      | 19        |

| 11.2 | DDC circuit                                   | 20        |

| 11.3 | Logic low I <sup>2</sup> C voltage shifter    | 21        |

| 11.4 | Hot plug detect circuit and HEAC support      | 22        |

| 11.5 | CEC                                           | 22        |

| 11.6 | Backdrive protection                          | 23        |

| 11.7 | 55 mA overcurrent / overvoltage               | 24        |

| 11.8 | LDO function<br>Schematic view of application | 24<br>25  |

| 11.9 | Typical application                           | 26        |

| 12   | Package outline                               | 28        |

| 13   | Soldering of SMD packages                     | 29        |

| 13.1 | Introduction to soldering                     | <b>29</b> |

| 13.1 | Wave and reflow soldering                     | 29        |

| 13.3 | Wave soldering                                | 29        |

| 13.4 | Reflow soldering                              | 30        |

| 14   | Glossary                                      | 31        |

| 15   | Revision history                              | 32        |

| 16   | Legal information                             | 33        |

| 16.1 | Data sheet status                             | 33        |

| 16.2 | Definitions                                   | 33        |

| 16.3 | Disclaimers                                   | 33        |

| 16.4 |                                               | 34        |

| 16.5 | Trademarks                                    | 34        |

| 17   | Contact information                           | 34        |

| 18   | Contents                                      | 35        |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

#### © NXP B.V. 2011.

#### All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 21 October 2011 Document identifier: IP4786CZ32