|                                                                                                |             |      |      |                                                           |      |                                                                                                                   |   |     |        |   | RE                                                              | VISI  | ONS            | 3           |                    |      | . '          |  |  |   |          |   |   |  |   |   |

|------------------------------------------------------------------------------------------------|-------------|------|------|-----------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------|---|-----|--------|---|-----------------------------------------------------------------|-------|----------------|-------------|--------------------|------|--------------|--|--|---|----------|---|---|--|---|---|

| LTR                                                                                            | DESCRIPTION |      |      |                                                           |      |                                                                                                                   |   |     |        |   | DAT                                                             | E (YR | - <b>M</b> O-[ | )<br>(A)    | A                  | PPR  | OVED         |  |  |   |          |   |   |  |   |   |

| А                                                                                              | II, f       | i gu | re 1 | , a                                                       | nd t | r, CAGE 34335. Made changes to table I, table<br>I throughout drawing. Added figure 8.<br>nactive for new design. |   |     |        |   |                                                                 |       | e              | 1988        | 3 OC               | Т 12 | 12 M.C. Jupe |  |  |   | le<br>Le |   |   |  |   |   |

|                                                                                                |             |      |      |                                                           |      |                                                                                                                   |   |     |        |   |                                                                 |       |                |             |                    |      |              |  |  |   |          |   |   |  |   |   |

| REV                                                                                            |             |      |      |                                                           |      |                                                                                                                   |   |     |        |   |                                                                 |       |                |             |                    |      |              |  |  |   |          |   |   |  |   |   |

| SHEET                                                                                          |             |      |      |                                                           |      |                                                                                                                   |   |     |        |   |                                                                 |       |                |             |                    |      |              |  |  |   |          |   |   |  |   |   |

| REV                                                                                            |             |      |      |                                                           |      |                                                                                                                   |   |     |        |   | _                                                               |       |                |             | $oldsymbol{\perp}$ |      |              |  |  |   |          |   |   |  | Ш |   |

| SHEET                                                                                          |             |      |      |                                                           |      |                                                                                                                   |   |     |        |   |                                                                 |       | Ш              |             |                    |      |              |  |  |   |          |   |   |  |   |   |

| REV STA                                                                                        |             | L    | RE   | V                                                         |      | Α                                                                                                                 | Α | Α   | Α      | Α | Α                                                               |       | Α              | Α           |                    |      | L.,          |  |  | Α | Α        | Α | Α |  | Ш |   |

| OF SHE                                                                                         |             |      | SH   | PREPARED BY  Lick Office  DEFENSE ELECTRONICS SUPPLY CENT |      |                                                                                                                   |   | NTE | L<br>R |   |                                                                 |       |                |             |                    |      |              |  |  |   |          |   |   |  |   |   |

| STANDARDIZED MILITARY DRAWING                                                                  |             |      |      | CHECKED BY Ray Monnin  APPROVED BY                        |      |                                                                                                                   |   |     |        |   | MICROCIRCUITS, DIGITAL, NMOS, 256X8 BIT RAM, MONOLITHIC SILICON |       |                |             | віт                |      |              |  |  |   |          |   |   |  |   |   |

| THIS DRAWING IS AVAILABLE FOR USE BY ALL DEPARTMENTS AND AGENCIES OF THE DEPARTMENT OF DEFENSE |             |      |      | DRAWING APPROVAL DATE 07 AUGUST 1987 REVISION LEVEL       |      |                                                                                                                   |   |     |        | 1 | SIZE CAGE CODE A 67268 5962-87                                  |       |                | 75 <u>9</u> | 93                 |      |              |  |  |   |          |   |   |  |   |   |

| AMSC                                                                                           | N/A         |      |      |                                                           |      |                                                                                                                   |   | Α   |        |   |                                                                 |       |                |             |                    | SHE  | ET           |  |  |   |          |   |   |  |   | 1 |

\* U.S. GOVERNMENT PRINTING OFFICE: 1987 -- 748-129/60911

5962-E971

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

1. SCOPE 1.1 Scope. This drawing describes device requirements for class B microcircuits in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices". 1.2 Part number. The complete part number shall be as shown in the following example: 5962-87593 Drawing number Device type Case outline Lead finish per (1.2.1)(1.2.2)MIL-M-38510 1.2.1 Device types. The device types shall identify the circuit function as follows: Device type Generic number Circuit function 2K RAM W/ I/O ports and timer,  $I_{IL}$  ( $\overline{CE}$ ) 01 8155/BQA 02 8156/BOA 2K RAM W/ I/O ports and timer,  $I_{IL}^{--}$  (CE) 1.2.2 Case outline. The case outline shall be as designated in appendix C of MIL-M-38510, and as follows: Outline letter Case outline Q D-5 (40-lead, 2.096" x .620" x .225"), dual-in-line package 1.3 Absolute maximum ratings. -0.5 V dc to +7.0 V dc -0.5 V dc to +7.0 V dc -65°C to +150°C Supply voltage range - - - - - - - - - - - - - -Input voltage range with respect to GND-----Storage temperature range- - - - - - - - - - - - -Maximum power dissipation ( $P_D$ ) - - - - - - - Lead temperature (soldering, 5 seconds) - - - - - -1.5 W +270°C Thermal resistance, junction-to-case ( $\theta_{JC}$ ): See MIL-M-38510, appendix C Junction temperature (T<sub>J</sub>)--------+150°C 1.4 Recommended operating conditions. 4.5 V dc to 5.5 V dc 2.0 V dc 0.8 V dc -55°C to +125°C SIZE STANDARDIZED Α 5962-87593 MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER **REVISION LEVEL** SHEET

DESC FORM 193A SEP 87

☆ U. S. GOVERNMENT PRINTING OFFICE: 1988—549-904

Α

DAYTON, OHIO 45444

#### 2. APPLICABLE DOCUMENTS

2.1 Government specification and standard. Unless otherwise specified, the following specification and standard, of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

**SPECIFICATION**

**MILITARY**

MIL-M-38510

- Microcircuits, General Specification for.

STANDARD

MILITARY

MIL-STD-883

Test Methods and Procedures for Microelectronics.

(Copies of the specification and standard required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

- 2.2 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

- 3. REQUIREMENTS

- 3.1 Item requirements. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein.

- 3.2 Design, construction, and physical dimensions. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 and herein.

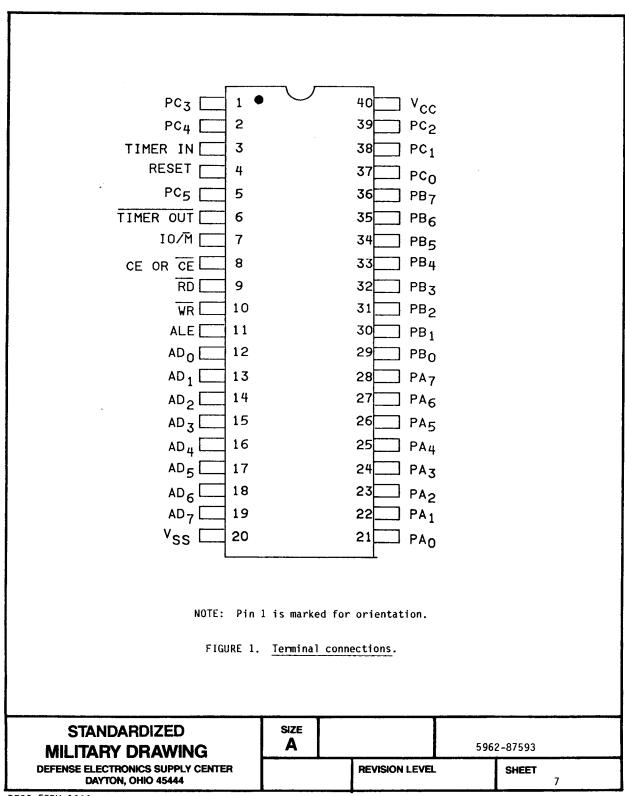

- 3.2.1 Terminal connections. The terminal connections shall be as specified on figure 1.

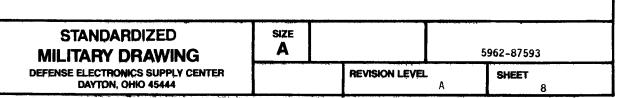

- 3.2.2 Block diagram. The block diagram shall be as specified on figure 2.

- 3.2.3 Case outline. The case outline shall be in accordance with 1.2.2 herein.

- 3.3 <u>Electrical performance characteristics</u>. Unless otherwise specified, the electrical performance characteristics are as specified in table I and apply over the full case operating temperature range.

- 3.4 <u>Marking</u>. Marking shall be in accordance with MIL-STD-883 (see 3.1 herein). The part shall be marked with the part number listed in 1.2 herein. In addition, the manufacturer's part number may also be marked as listed in 6.4 herein.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br><b>A</b> |               |     | 962-87593 |  |

|------------------------------------------------------|------------------|---------------|-----|-----------|--|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVE | L A | SHEET 3   |  |

DESC FORM 193A SEP 87

**☆ U. S. GOVERNMENT PRINTING OFFICE: 1988---549-904**

TABLE I. Electrical performance characteristics. Limits Conditions  $-55^{\circ}$  C  $\leq$   $T_{\text{C}} \leq +125^{\circ}$  C Test Symbol Device Group A Unit subgroups types | Min Max 1/ -0.5 | 0.8 Input low voltage VIL V<sub>CC</sub> = 4.5 V 1, 2, 3 A11 ٧ Input high voltage VIH  $V_{CC} = 4.5 \text{ V}$ 2.0 VCC +0.5 A11 1, 2, 3 ٧ Output low voltage  $v_{OL}$  $V_{IL} = 0.8 \text{ V}$   $V_{CC} = 5.5 \text{ V}, V_{IH} = 2.0 \text{ V}$ 1, 2, 3 ٧ A11 10.45 I V<sub>OH</sub>  $v_{IL}$  = 0.8 V,  $v_{IH}$  = 2.0 V  $v_{CC}$  = 5.5 V,  $I_{OL}$  = -400  $\mu\text{A}$ Output high voltage 1, 2, 3 2.4 A11 ٧ V<sub>CC</sub> = 5.5 V, V<sub>IN</sub> = 5.5 V to 0 V Input leakage current | I<sub>IL</sub> 1, 2, 3 A11 10 μА -10 μА  $|V_{CC}| = 5.5 \text{ V},$  $|V_{OUT}| = 5.5 \text{ V to 0.45 V}$ Output leakage current|I<sub>IO</sub> 1, 2, 3 A11  $\mu \boldsymbol{A}$ 10 -10 μΑ V<sub>CC</sub> supply current 1V<sub>CC</sub> = 5.5 V Icc 2/ 1, 2, 3 A11 125 'nΑ İΙΙL V<sub>CC</sub> = 5.5 V V<sub>IN</sub> = 5.5 V to 0 V Chip enable leakage 1, 2, 3 01 160 μΑ (CE) V<sub>CC</sub> = 5.5 V V<sub>IN</sub> = 5.5 V to 0 V Chip enable leakage IIL 1, 2, 3 02 100 μA (CE) Functional testing |See 4.3.1c 7,8

See footnotes at end of table.

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

5962-87593

REVISION LEVEL

A

SHEET

4

DESC FORM 193A SEP 87

**☆** U. S. GOVERNMENT PRINTING OFFICE: 1988—549-904

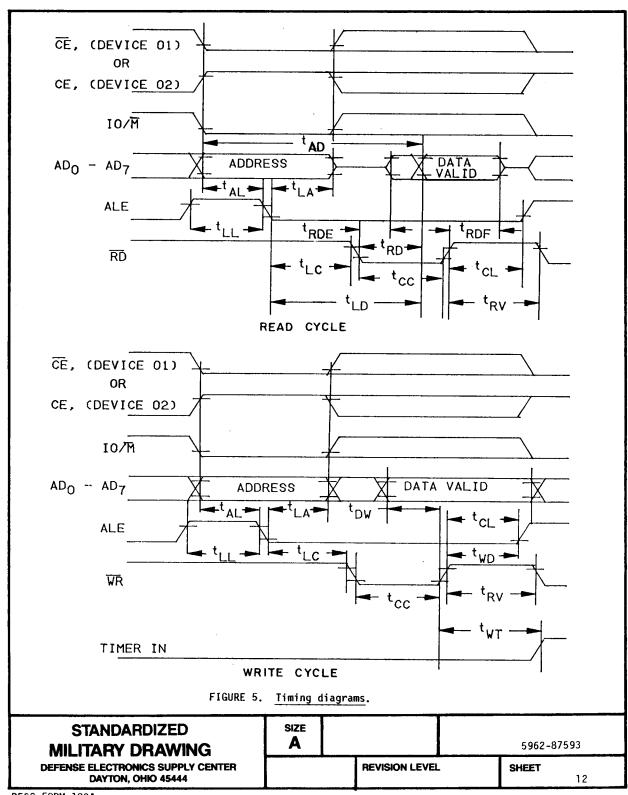

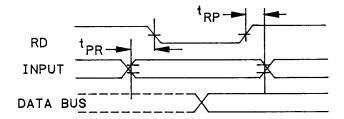

TABLE I. Electrical performance characteristics - Continued. Limits Test Symbol | Conditions Group A Device Unit -55°C < T<sub>C</sub> < +125°C subgroups | types | Min Max Address to LATCH setup|tal  $|V_{CC} = 5.5 \text{ V}, 4.5 \text{ V}|$ 9, 10, 11 A11 50 ns time  $V_{IH} = 2.4 V$ Address hold time tLA 9, 10, 11 A11 80 ns after LATCH  $V_{IL} = 0.45 V$ ATCH to READ/WRITE  $V_{OH} = 2.0 V$ tLC 9, 10, 11 100 ns control  $V_{OL} = 0.8 V$ Valid data out from t<sub>RD</sub> 9, 10, 11 A11 170 ns READ control Address stable to data tal 9, 10, 11 A11 400 ns out valid ATCH enable width  $t_{LL}$ 9, 10, 11 A11 100 ns Data bus float after 9, 10, 11 A11 0 100 trdf. ns READ 3/ READ/WRITE control to tÇL 9, 10, 11 A11 20 ns LATCH enable READ/WRITE control t<sub>CC</sub> 9, 10, 11 A11 250 ns width Data into WRITE t<sub>DW</sub> 4/ 9, 10, 11 A11 150 ns setup time Data in hold time two 9, 10, 11 ns after WRITE Recovery time between 9, 10, 11 ItRV A11 300 ns controls WRITE to port output 9, 10, 11 A11 400 ns Port input setup time |t<sub>PR</sub> 19, 10, 11 70 A11 ns Port input hold time  $t_{RP}$ 19, 10, 11 50 A11 ns STB to buffer full t<sub>SBF</sub> 19, 10, 11 | 400 A11 ns STB width 19, 10, 11 200  $\mathsf{t}_{\mathsf{SS}}$ **A11** ns See footnotes at end of table. **STANDARDIZED** SIZE Α 5962-87593 MILITARY DRAWING **DEFENSE ELECTRONICS SUPPLY CENTER REVISION LEVEL** SHEET DAYTON, OHIO 45444 5

DESC FORM 193A SEP 87

± U. S. GOVERNMENT PRINTING OFFICE: 1988--549-904

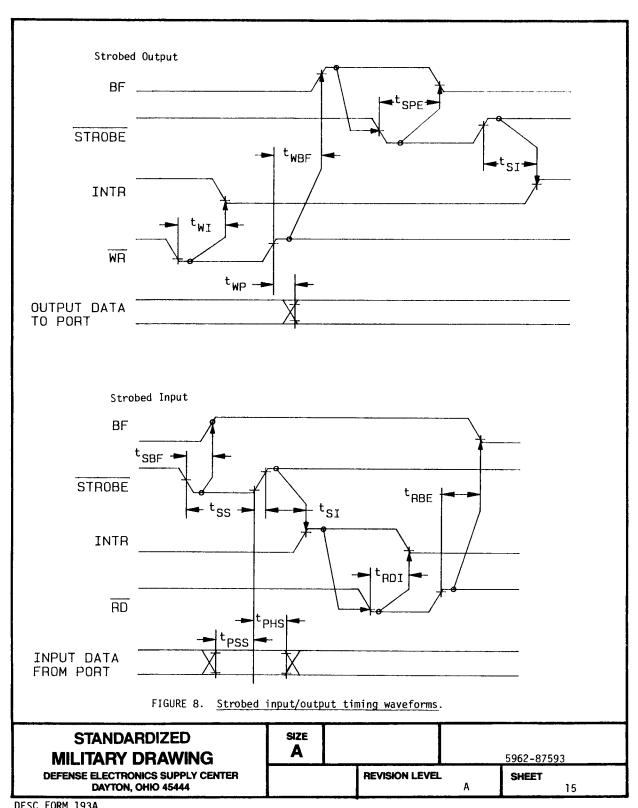

| Test                                 | <br> Symbol               | Conditions                                                 | Group A   | Device        | l Limits |            | Unit |

|--------------------------------------|---------------------------|------------------------------------------------------------|-----------|---------------|----------|------------|------|

|                                      | ]<br>[                    | Conditions $-55^{\circ}C \leq T_{C} \leq +125^{\circ}C$    |           | types         |          | Max        | <br> |

| READ to buffer empty                 | t <sub>RBE</sub>          | V <sub>CC</sub> = 5.5 V, 4.5 V                             | 9, 10, 11 | <br>  All<br> |          | 400        | ns   |

| STB to INTR on                       | <br> t <sub>SI</sub><br>  | V <sub>IH</sub> = 2.4 V<br> <br>  V <sub>IL</sub> = 0.45 V | 9, 10, 11 | A11<br>       |          | 400        | ns   |

| READ to INTR off                     | <br> t <sub>RDI</sub><br> | V <sub>OH</sub> = 2.0 V                                    | 9, 10, 11 | A11           | l<br>I   | 400        | ns   |

| Port setup time to STB               | t <sub>PSS</sub>          | V <sub>OL</sub> = 0.8 V<br> <br>  V <sub>IL</sub> = 0.45 V | 9, 10, 11 | <br>  A11<br> | 50       | <br>       | ns   |

| Port hold time after<br>STB          | t <sub>PHS</sub>          | <u>4</u> /                                                 | 9, 10, 11 | <br>  All<br> | 120      |            | ns   |

| STB to buffer empty                  | t <sub>SBE</sub>          | <br>                                                       | 9, 10, 11 | All           |          | 400        | ns   |

| WRITE to buffer full                 | twar                      |                                                            | 9, 10, 11 | <br>  A]]     |          | 400        | ns   |

| WRITE to INTR off                    | <br> t <sub>WI</sub><br>  | !<br>!<br>!                                                | 9, 10, 11 | <br>  A11<br> |          | 400        | ns   |

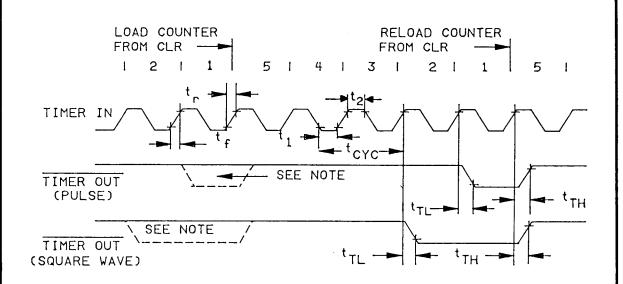

| TIMER-IN to TIMER-OUT                | tŢĹ                       | <br>                                                       | 9, 10, 11 | <br>  A11<br> |          | 400        | ns   |

| TIMER-IN to TIMER-OUT  <br>high      | t <sub>TH</sub>           | <br> <br>                                                  | 9, 10, 11 | All           |          | 400        | ns   |

| Data bus enable from<br>READ control | t <sub>RDE</sub>          |                                                            | 9, 10, 11 | All           | 10       |            | ns   |

| TIMER-IN low time                    | t <sub>1</sub>            | <br>                                                       | 9, 10, 11 | All           | 88       | <br>  <br> | ns   |

| TIMER-IN high time                   | t <sub>2</sub>            | <br>                                                       | 9, 10, 11 | All           | 120      | İ          | ns   |

$<sup>\</sup>underline{1}\!/$  These  $v_{IL}$  and  $v_{IH}$  values are guaranteed by design and are not tested.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A | 5962-87593     | 593    |         |  |

|------------------------------------------------------|-----------|----------------|--------|---------|--|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | -<br>A | SHEET 6 |  |

$<sup>\</sup>underline{2}/$  The supply current is measured with unloaded outputs while running functional patterns.

$<sup>\</sup>underline{3}/$  AC float timing parameter  $t_{\mbox{rdf}}$  is tested logic 0 to float only.

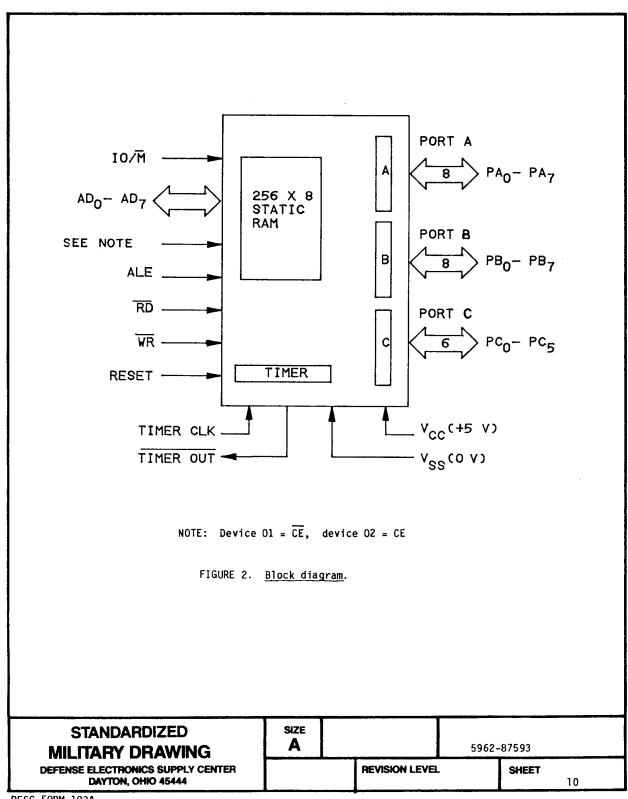

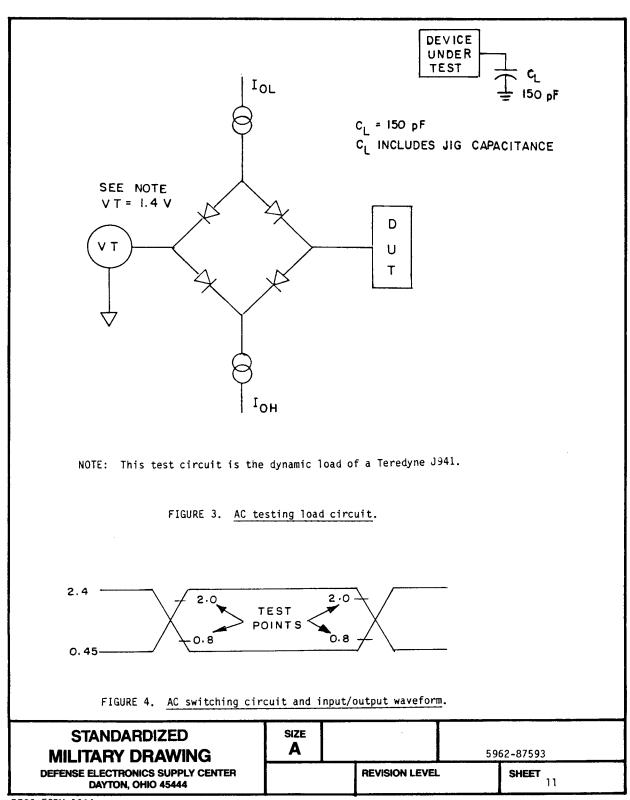

<sup>4/</sup> See figures 3, 4, 5, 6, 7, and 8.

☆ U.S. GOVERNMENT PRINTING OFFICE: 1987 748-129-60913

|         |                                                                    |     | Pin description.                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|--------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin no. | Name                                                               | 1/0 | Pin description                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4       | RESET                                                              | I   | The RESET signal is a pulse provided by the 8085AH to initialize the lsystem. Input high on this line resets the chip and initializes the lthree I/O ports to input code. The width of RESET pulse should ltypically be 600 ns. (Two 8085AH clock cycle times.)                                                                                                                                                                              |

| 12-19   | AD <sub>O</sub> -AD <sub>7</sub><br> <br> <br> <br> <br> <br> <br> | 1/0 | These are 3-state Address/Data lines that interface with the CPU llower 8-bit Address/Data bus. The 8-bit address is latched into the laddress latch on the falling edge of the ALE. The address can be leither for the memory section or the I/O section depending on the lpolarity of the IO/M input signal. The 8-bit data is either written linto the chip or read from the chip depending on the status of WRITE lor READ input signal. |

| 8       | ICE - CE                                                           | I   | <br> Chip enable. On the O1 device, this pin is CE and is active low.<br> On the O2 device, this pin is CE and is active high.                                                                                                                                                                                                                                                                                                               |

| 9       | RD                                                                 | I   | Input low on this line with the chip enable active enables the $AD_{Q-7}$ buffers. If $IO/M$ pin is LOW, the RAM content will be read out to the AD bus. Otherwise, the content of the selected I/O port will be read to the AD bus.                                                                                                                                                                                                         |

| 10      | WR                                                                 | I   | Input low on this line with the chip enable active causes the data on the AD lines to be written to the RAM or I/O ports, depending on the of IO/M.                                                                                                                                                                                                                                                                                          |

| 11      | ALE                                                                | I   | Address latch enable. This control signal latches the address on the AD <sub>O-7</sub> lines and the state of the chip enable and IO/M into the chip at the falling edge of ALE.                                                                                                                                                                                                                                                             |

| 7       | IO/M<br>                                                           | I   | IO/MEMORY select. This line selects the memory if LOW and selects the IO if HIGH.                                                                                                                                                                                                                                                                                                                                                            |

FIGURE 1. <u>Terminal connections</u> - Continued.

★ U. S. GOVERNMENT PRINTING OFFICE: 1988—549-904

|                  | <u> </u>                                  |        | Pin description - Continued.                                                                                                                                                                                                                                             |

|------------------|-------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin no.          | Name                                      | 1/0    | Pin description                                                                                                                                                                                                                                                          |

| 21-28            | PA <sub>0</sub> -PA <sub>7</sub>          | 1/0    | These 8 pins are general purpose I/O pins. The in/out direction is selected by programming the Command/Status register.                                                                                                                                                  |

| 29-36            | <br> PB <sub>O</sub> -PB <sub>7</sub><br> | I I/0  | These 8 pins are general purpose I/O pins. The in/out direction is selected by programming the Command/Status register.                                                                                                                                                  |

| 37-39<br>1, 2, 5 | PC <sub>O</sub> -PC <sub>5</sub>          | I/0    | These 6 pins can function as either input port, output port or as control signals for PA and PB. Programming is done through the C/E lregister. When $PC_{0-5}$ are used as control signals, they will produce the following: $PC_{0-A} \text{ INTR (Port A interrupt)}$ |

|                  | İ                                         | }      | PC1-A BF (Port A buffer full)                                                                                                                                                                                                                                            |

|                  | 1                                         | İ<br>I | PC <sub>2</sub> -A STB (Port A strobe)                                                                                                                                                                                                                                   |

|                  |                                           | 1      | PC3-B INTR (Port B interrupt)                                                                                                                                                                                                                                            |

|                  |                                           |        | PC <sub>4</sub> -B BF (Port B buffer full)                                                                                                                                                                                                                               |

|                  |                                           |        | PC5-B STB (Port B strobe)                                                                                                                                                                                                                                                |

| 3                | TIMER IN                                  | I      | <br> This is the input to the counter timer.                                                                                                                                                                                                                             |

| 6                | TIMER OUT                                 | 0      | <br> This pin is the timer output. This output can be either a square<br> wave a pulse depending on the timer code.                                                                                                                                                      |

| 40               | V <sub>CC</sub>                           |        | +5 volt supply.                                                                                                                                                                                                                                                          |

| 20               | V <sub>SS</sub>                           | <br>   |                                                                                                                                                                                                                                                                          |

FIGURE 1. Terminal connections - Continued.

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

5962-87593

REVISION LEVEL

A

9

DESC FORM 193A SEP 87

**☆** U. S. GOVERNMENT PRINTING OFFICE: 1988—549-904

$\dot{\infty}$  U.S. GOVERNMENT PRINTING OFFICE: 1987 - 748-129-60913

\$1.S. GOVERNMENT PRINTING OFFICE: 1987 - 748-129-60913

. ☆c.s. government printing office: 1987 - 748-129-609B

## BASIC INPUT MODE

# BASIC OUTPUT MODE

NOTE: Data bus timing is shown on figure 5.

FIGURE 6. Basic input/output timing waveform.

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

5962-87593

REVISION LEVEL

SHEET

13

DESC FORM 193A SEP 87

☆ U.S. GOVERNMENT PRINTING OFFICE: 1987 - 748-129-60913

NOTE: The timer output is periodic if an automatic reload mode ( $M_1$  mode bit = 1)

FIGURE 7. Timer output waveform countdown from five to one.

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

5962-87593

REVISION LEVEL

SHEET

14

DESC FORM 193A SEP 87

☆ U.S. GOVERNMENT PRINTING OFFICE: 1987 748-129-60913

± U. S. GOVERNMENT PRINTING OFFICE: 1988--549-90

- 3.5 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in 6.4. The certificate of compliance submitted to DESC-ECS prior to listing as an approved source of supply shall state that the manufacturer's product meets the requirements of MIL-STD-883 (see 3.1 herein) and the requirements herein.

- 3.6 Certificate of conformance. A certificate of conformance as required in MIL-STD-883 (see 3.1 herein) shall be provided with each lot of microcircuits delivered to this drawing.

- 3.7 Notification of change. Notification of change to DESC-ECS shall be required in accordance with MIL-SID-883 (see 3.1 herein).

- 3.8 Verification and review. DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 Sampling and inspection. Sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein).

- 4.2 <u>Screening.</u> Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test method 1015 of MIL-STD-883.

- Test condition D using the circuit submitted with the certificate of compliance (see 3.5 herein).

- (2)  $T_A = +125^{\circ}C$ , minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

- 4.3 Quality conformance inspection. Quality conformance inspection shall be in accordance with method 5005 of MIL-SID-883 including groups A, B, C, and D inspections. The following additional criteria shall apply.

- 4.3.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. Subgroups 4, 5, and 6 in table I, method 5005 of MIL-STD-883 shall be omitted.

- c. Subgroups 7 and 8 testing shall be sufficient to verify the functional operation of the device.

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

5962-87593

REVISION LEVEL

A

16

DESC FORM 193A SEP 87

★ U. 8. GOVERNMENT PRINTING OFFICE: 1988-549-904

| TABLE II. | Electrical | test | requirements. |

|-----------|------------|------|---------------|

|           |            |      |               |

| MIL-STD-883 test requirements                                                   | Subgroups  <br>  (per method  <br>  5005, table I) |

|---------------------------------------------------------------------------------|----------------------------------------------------|

| <br> Interim electrical parameters<br>  (method 5004)<br>                       |                                                    |

| <br> Final electrical test parameters<br>  (method 5004)<br>                    | 1*, 2, 3, 7, 8,  <br> 9, 10**, 11**                |

| <br> Group A test requirements<br>  (method 5005)<br>                           | 1*, 2, 3, 7, 8,  <br>  9, 10**, 11**               |

| <br> Groups C and D end-point<br>  electrical parameters<br>  (method 5005)<br> | 2, 8(hot), 10  <br>                                |

### 4.3.2 Groups C and D inspections.

- a. End-point electrical parameters shall be as specified in table II herein.

- b. Steady-state life test conditions, method 1005 of MIL-STD-883.

- (1) Test condition D using the circuit submitted with the certificate of compliance (see 3.5 herein).

- (2)  $T_A = +125^{\circ}C$ , minimum.

- (3) Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

#### 5. PACKAGING

5.1 Packaging requirements. The requirements for packaging shall be in accordance with MIL-M-38510.

### 6. NOTES

- 6.1 Intended use. Microcircuits conforming to this drawing are intended for use when military specifications do not exist and qualified military devices that will perform the required function are not available for OEM application. When a military specification exists and the product covered by this drawing has been qualified for listing on QPL-38510, the device specified herein will be inactivated and will not be used for new design. The QPL-38510 product shall be the preferred item for all applications.

- 6.2 Replaceability. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

| STANDARDIZED MILITARY DRAWING                           | SIZE<br>A |                  | 5962-87593 |  |  |  |

|---------------------------------------------------------|-----------|------------------|------------|--|--|--|

| DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 |           | REVISION LEVEL A | SHEET 17   |  |  |  |

DESC FORM 193A SEP 87

**☆ U. S. GOVERNMENT PRINTING OFFICE: 1988—549-904**

PDA applies to subgroup 1. Subgroups 10 and 11, if not tested, shall be guaranteed to the limits specified in table I.

- 6.3 Comments. Comments on this drawing should be directed to DESC-ECS, Dayton, Ohio 45444, or telephone 513-296-5375.

- 6.4 Approved source of supply. An approved source of supply is listed herein. Additional sources will be added as they become available. The vendor listed herein has agreed to this drawing and a certificate of compliance (see 3.5 herein) has been submitted to DESC-ECS.

| <br>  Military drawing<br>  part number | Vendor  <br>  CAGE<br>  number | Vendor<br>similar part<br>number <u>1</u> / |

|-----------------------------------------|--------------------------------|---------------------------------------------|

| 5962-8759301QX                          | 34649                          | MD8155H/B                                   |

| 5962-8759302QX                          | 2/                             | AM8156/BQA                                  |

- $\frac{1}{Items} \begin{tabular}{ll} Caution. & Do not use this number for item acquisition. \\ \hline Items acquired to this number may not satisfy the performance requirements of this drawing. \\ \hline \end{tabular}$

- $\underline{\mathbf{Z}}'$  Inactive for new design, not available from an approved source of supply.

Vendor CAGE number 34649 Vendor name and address

Intel Corporation 5000 W. Chandler Boulevard Chandler, AZ 85226

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE A 5962-87593

REVISION LEVEL SHEET A 18

DESC FORM 193A SEP 87

**★** U. S. GOVERNMENT PRINTING OFFICE: 1988—550-547

011808 \_\_\_\_

JUN 0 3 1991