# SSI 32R1562R/63R +5, -3V, 10-Channel MR Read/Write/Servo Write Advance Information

February 1996

#### DESCRIPTION

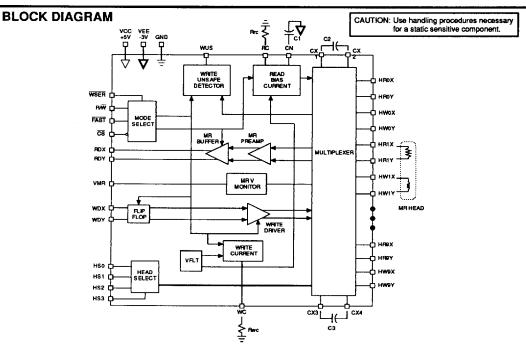

The SSI 32R1562R/63R is a BiCMOS monolithic integrated circuit designed for use with four-terminal, Magneto-Resistive recording heads. It provides a write driver, MR read bias current, low noise read amplifier and fault detection circuitry for up to ten channels. In a write servo mode two banks of 5 write heads each can be separately selected. The device requires +5V and -3V power supplies, and comes in a 64-lead TQFP package.

### **FEATURES**

- +5V, -3V ±10% supply

- Designed for four-terminal MR heads with minimum external components

- · Write unsafe detection

- Truly differential current blas/voltage sense MR read amp

- MR head bias current range = 6 to 16 mA

- MR read gain = 150 V/V

- MR read input noise = 0.75 nV/ $\sqrt{\text{Hz}}$  (Nom)

- MR read input resistance =  $900\Omega$  (Min)

- MR read input capacitance = 12 pF (Nom)

- No flip-flop bond option, 32R1563R

- Head voltage swing = 10 Vp-p (Nom)

Write current range = 10 to 40 mA

- Max write current rise/fall time = 3.5 ns (Typ. head)

- Enhanced system write to read and read to write recovery time

- Fast thermal asperity recovery

- Power supply fault protection

- Servo write feature

02/20/96 - rev.

3A-55

■ 8253965 0014148 T21

### **FUNCTIONAL DESCRIPTION**

#### **CIRCUIT OPERATION**

The SSI 32R1562R/63R addresses up to 10 four terminal MR heads providing write drive or read bias and amplification. The mode control and head selection are accomplished with TTL pins  $\overline{CS}$ , R/W,  $\overline{FAST}$ ,  $\overline{WSER}$  and HSn as shown in Tables 1, 2 and 3. All the TTL inputs have internal pull-up resistor so that when left opened, it will default to the TTL High state. Exception to this rule are head select inputs HSn which have internal pull-down resistors and, consequently, will default to the TTL Low state.

**TABLE 1: Head Selection**

| HS3 | HS2 | HS1 | HS0 | HEAD SELECTED |

|-----|-----|-----|-----|---------------|

| 0   | 0   | 0   | 0   | 0             |

| 0   | 0   | 0   | 1   | 1             |

| 0   | 0   | 1   | 0   | 2             |

| 0   | 0   | 1   | 1   | 3             |

| 0   | 1   | 0   | 0   | 4             |

| 0   | 1   | 0   | 1   | 5             |

| 0   | 1   | 1   | 0   | 6             |

| 0   | 1   | 1 . | 1   | 7             |

| 1   | 0   | 0   | 0   | 8             |

| 1   | 0   | 0   | 1   | 9             |

**TABLE 2: Mode Selection**

| ĊS | R/W | WSER | FAST | DESCRIPTION                         |

|----|-----|------|------|-------------------------------------|

| 0  | 1   | Х    | 1    | read mode only                      |

| 0  | 0   | 1    | Х    | write mode, MR bias current ON      |

| 0  | 1   | 1    | 0    | thermal asperity fast recovery mode |

| 0  | 0   | 0    | Х    | Servo bank write                    |

| 1  | х   | Х    | X    | idle mode                           |

**TABLE 3: Head Selection in Servo Mode**

| <u>cs</u> | WSER | HS3 | HS2 | HS1 | HS0 | Head Selected for Servo Write |

|-----------|------|-----|-----|-----|-----|-------------------------------|

| 0         | 0    | 0   | 0   | 0   | 0   | 4, 3, 2, 1, 0 *               |

| 0         | 0    | 0   | 0   | 0   | 1   | 9, 8, 7, 6, 5 *               |

| 0         | 0    | 0   | 0   | 1   | 0   | 3, 2, 1, 0                    |

| 0         | 0    | 0   | 0   | 1   | 1   | 7, 6, 5, 4                    |

| 0         | 0    | 0   | 1   | 1   | 0   | 2, 1, 0                       |

| 0         | 0    | 0   | 1   | 0   | 1   | 5, 4, 3                       |

| 0         | 0    | 0   | 1   | 1   | 0   | 8, 7, 6                       |

| 0         | 0    | 0   | 1   | 1   | 1   | 9                             |

| 0         | 0    | 1   | 0   | 0   | 0   | 1, 0                          |

| 0         | 0    | 1   | 0   | 0   | 1   | 3, 2                          |

| 0         | 0    | 1   | 0   | 1   | 0   | 5, 4                          |

| 0         | 0    | 1   | 0   | 1   | 1   | 7, 6                          |

| 0         | 0    | 1   | 1   | 0   | 0   | 9, 8                          |

<sup>\*</sup> Maximum I<sub>w</sub> < 35 mA

3A-57

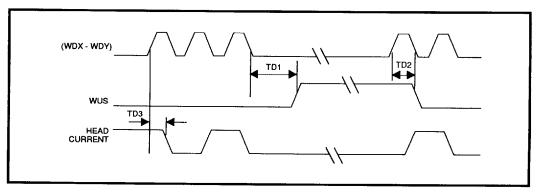

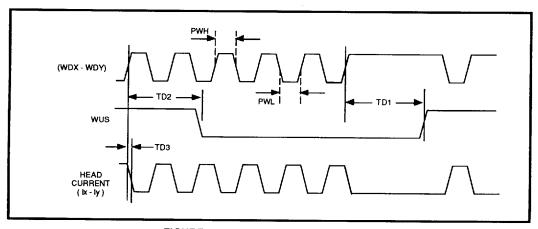

#### WRITE MODE

Taking both  $\overline{\text{CS}}$  and R/W low selects write mode which configures the SSI 32R1562R/63R as a current switch and activates the Write Unsafe (WUS) detect circuitry. Head current is toggled between the X (HWnX) and Y (HWnY) side of the selected head on each Low to High transition of the differential PECL signal WDX-WDY. Changing from read or Idle mode to write mode initializes the write Data Flip-Flop to pass write current into the "X" pin, i. e., the Y side of the head will be higher potential then X side. For no flip-flop option (32R1563R) WDX > WDY will cause Iw to flow from Y to X. The write current is externally programmed either by a resistor Rwc connected from pin WC to GND or by a current sink from pin WC. The magnitude of the current (0-pk) is given by:

$$lw = \frac{Aw \cdot Vwc}{Rwc} = \frac{Kwc}{Rwc}$$

where Aw is 20 mA/mA and Vwc is 2V.

Note that the actual head current lx,y is given by:

$$I_{X, y} = \frac{Iw}{1 + Rh/Rd}$$

where Rh is the head DC resistance and Rd is the damping resistance.

#### **SERVO WRITE MODE**

Taking  $\overline{\text{CS}}$ , RW and  $\overline{\text{WSER}}$  low enables write servo mode. In this mode five write heads comprising one servo bank are simultaneously activated. Write servo banks are selected by HS0-HS3 lines according to Table 3.

#### **WRITE UNSAFE**

Any of the following conditions will be indicated as a high level on the Write Unsafe (WUS) open collector output:

WDX/WDY frequency too low Device in read mode No head current Head open

Upon entering write mode, WUS is valid after two Low to High transitions of WDX - WDY following the required Read-Write transition time (0.5  $\mu$ s max).

#### READ MODE

Taking  $\overline{\text{CS}}$  low and R/W high selects read mode which activates the MR bias current generator and low noise differential amplifier. The outputs of the read amplifier RDX and RDY are emitter followers and are in phase with the resistivity change at the selected input ports HRnX and HRnY where the respective MR head is attached. The DC current necessary for biasing the MR sensor is externally programmed either by a resistor Rrc connected from pin RC to GND or by a current sink. The magnitude of the bias current is given by:

$$Ir = \frac{Ar \cdot Vrc}{Rrc} = \frac{Krc}{Rrc}$$

where Ar is 20 mA/mA and Vrc is 2.0V.

An external capacitor connected from pin CN to VEE is used for reducing the noise from MR bias current source. A low inductance capacitor with a value of 0.1 µF is recommended. Two external floating capacitors C2 and C3 connected between pins CX1/CX2 and CX3/CX4 respectively are required for DC blocking. For the application that uses up to five MR heads, i. e., head 0 to head 4, only one floating capacitor connected between pins CX1 and CX2 is required. Care should be taken to use low inductance high frequency capacitors and to locate them as close to the pins as possible because the stray inductance will degrade the amplifier's noise and frequency response performance. The value of the DC blocking capacitors C2/C3 will have direct effect on the write to read recovery time. For fast recovery time, the capacitor value should be kept as small as possible. The value of the capacitor C2/C3 also sets the low frequency cutoff of the read amplifier. The -3 dB low-frequency corner is given by:

$$f_i = 1/(2\pi \cdot 15\Omega \cdot C2)$$

For example, a 0.03 µF capacitor for C2/C3 will result in the -3 dB low-frequency of about 354 kHz.

The voltage drop across the MR head is monitored internally. The VMR pin provides a monitor voltage referenced to ground of the MR head bias voltage. The maximum output current of the VMR pin should not exceed 1 mA.

3A-58

8253965 0014151 516 **=**

To improve the write to read recovery time, the MR bias current in the selection head is left on during write mode. With the MR bias current turned on, the voltage change across the DC blocking capacitor C2/C3 between write and read modes will be minimized which would then result in faster write to read recovery time. In read mode, the voltage at the midpoint of the selected MR head is forced to the ground potential. For the unselected MR heads, the head ports become high impedance and thus will prevent the heads from conducting current in the event of head to disk contact.

#### THERMAL ASPERITY RECOVERY MODE

Making  $\overline{FAST}=0$  activates the thermal asperity recovery mode. The time constant at the DC blocking capacitors C2 and C3 is reduced by a factor of three to speed up the recovery of the large signal caused by the  $\Delta R$  induced by the thermal asperity.

#### **IDLE MODE**

Making  $\overline{\text{CS}} = 1$  selects Idle mode which deactivates both the write current source and MR bias current. The voltages at RC pin remain active so that an internal dummy head can be switched on to provide proper voltage biasing for the DC blocking capacitor C2/C3. The pins RDX/RDY, VMR, WC, and RC are switched into high impedance state to facilitate multiple device applications where these pins could be wire OR'ed.

#### **POWER SUPPLY FAULT PROTECTION**

A voltage fault detection circuit improves data security by disabling the write current generator and MR bias current during a voltage fault or power startup regardless of mode.

3A-59

8253965 001,4152 452

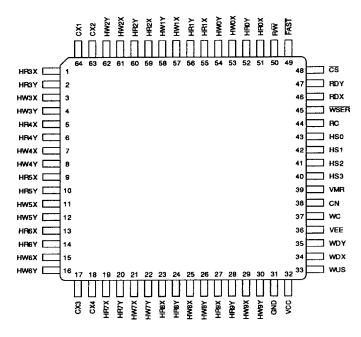

### **PIN DESCRIPTION**

| NAME                  | TYPE | DESCRIPTION                                                                                                      |

|-----------------------|------|------------------------------------------------------------------------------------------------------------------|

| HRnX                  | 1    | MR read head input X connection                                                                                  |

| HRnY                  | l    | MR read head input Y connection                                                                                  |

| HWnX                  | 0    | Inductive write head X connection                                                                                |

| HWnY                  | 0    | Inductive write head Y connection                                                                                |

| CN                    | - 1  | Noise filter Cap C1; X side, Y side of C1 must be connected to VEE                                               |

| CX1, CX2              | l I  | Floating DC blocking cap C2; for head 0 to head 4                                                                |

| CX3, CX4              | ı    | Floating DC blocking cap C3: for head 5 to head 9                                                                |

| WDX, WDY              | I    | Differential PECL write Data Input, a positive transition of (WDX-WDY) toggles the direction of the head current |

| RDX, RDY              | 0    | Differential MR head read Data Output                                                                            |

| wc                    | ı    | Write Current set: used to set the magnitude of the write current                                                |

| RC                    | i    | Read Current set; used to set the magnitude of the MR bias current                                               |

| WUS                   | 0    | Write Unsafe; open collector; a high level indicates an unsafe writing condition                                 |

| HS0, HS1,<br>HS2, HS3 | 1    | Head Select; select one of ten heads; TTL                                                                        |

| CS                    | 1    | Chip Select; a high inhibits the chip; TTL                                                                       |

| R∕ <b>W</b>           | ı    | Read/Write; a high selects read mode, TTL                                                                        |

| WSER                  | I    | Write servo; a low enables write in servo mode; TTL                                                              |

| FAST                  |      | A low level activates the thermal asperity fast recovery mode; TTL                                               |

| VMR                   | 0    | MR head DC voltage drop monitor, referenced to ground                                                            |

| VCC                   | - 1  | +5V Supply                                                                                                       |

| VEE                   | 1    | -3V Supply                                                                                                       |

| GND                   | 1    | Ground                                                                                                           |

3A-60

### **ELECTRICAL SPECIFICATIONS**

### **ABSOLUTE MAXIMUM RATINGS**

Operation above maximum ratings may result in permanent damage to the device.

| PARAMETER                      |         | RATING                |

|--------------------------------|---------|-----------------------|

| DC Supply Voltage              | VCC     | +6 VDC                |

|                                | VEE     | -3.6 VDC              |

| Logic Input Voltage            | TTL     | -0.3 to VCC + 0.3 VDC |

|                                | PECL    | 0 to VCC VDC          |

| Write Current                  | lw      | 50 mA                 |

| MR Bias Current                | lr      | 30 mA                 |

| Output Current                 | WUS     | +8 mA                 |

|                                | RDX/RDY | -5 mA                 |

| Operating Junction Temperature | Tj      | +125°C                |

| Storage Temperature            | Tstg    | -65 to +150°C         |

#### **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                     |     | RATING    |  |

|-------------------------------|-----|-----------|--|

| DC Supply Voltage             | VCC | +5V, ±10% |  |

|                               | VEE | -3V, ±10% |  |

| Operating Ambient Temperature | Та  | 0 to 70°C |  |

3A-61

**=** 8253965 0014154 225 **=**

### **ELECTRICAL SPECIFICATIONS** (continued)

### **DC CHARACTERISTICS**

Recommended operating conditions apply unless otherwise specified. Ir = 11 mA, Iw = 30 mA

| PARAMETER          | CONDITION                                 | MIN   | NOM                      | MAX   | UNIT |

|--------------------|-------------------------------------------|-------|--------------------------|-------|------|

| VCC Supply Current | read mode                                 |       | 45 + 1.15 lr             |       | mA   |

|                    | write mode                                |       | 44 + 1.2 lw<br>+ 1.15 ln |       | mA   |

|                    | servo mode                                |       | 81 + 5.8 lw              |       | mA   |

|                    | idle mode                                 |       | 9                        |       | mA   |

| VEE Supply Current | read mode                                 |       | 25 + 1.1 lr              |       | mA   |

|                    | write mode                                |       | 35 + 1.2 lw<br>+ 1.1 ln  |       | mA   |

|                    | servo mode                                |       | 67+ 6.05 lw              |       | mA   |

|                    | idle mode                                 |       | 8                        |       | mA   |

| Power Dissipation  | read mode                                 |       | 385                      |       | mW   |

|                    | write mode                                |       | 705                      |       | mW   |

|                    | servo mode, lw = 10 mA,<br>H0 - H4 active |       | 1080                     |       | W    |

|                    | idle mode                                 |       | 70                       |       | mW   |

| VCC Fault Voltage  | lw < 0.2 mA, lr < 0.2 mA                  | 3.5   | 3.85                     | 4.2   | VDC  |

| VEE Fault Voltage  | lw < 0.2 mA, lr < 0.2 mA                  | -2.52 | -2.31                    | -2.10 | VDC  |

### **DIGITAL INPUTS AND OUTPUTS**

| Input Low Voltage          | VIL  | TTL                |           |      | 0.8       | ٧  |

|----------------------------|------|--------------------|-----------|------|-----------|----|

| Input High Voltage         | VIH  | TTL                | 2         |      |           | V  |

| Input Low Current          | LIL  | Vil = 0.8V         | -0.4      | -0.2 |           | mA |

| Input High Current         | LIH  | Vih = 2V           |           |      | 100       | μА |

| Input Low Voltage          | VIL2 | WDX, WDY           | Vcc -2.2  |      | VIH2 -0.3 | ٧  |

| Input High Voltage         | VIH2 | WDX, WDY           | Vcc -1.08 |      | Vcc - 0.5 | V  |

| Input Differential Voltage |      | V(WDX) - V(WDY)    | 0.3       |      |           | ٧  |

| Input Low Current          | LIL2 | Vil2 = Vcc - 1.25V |           |      | 50        | μА |

| Input High Current         | LIH2 | Vih2 = Vcc - 0.75V |           |      | 50        | μА |

| Output High Current        | LOH  | WUS                |           |      | 50        | mA |

| Output Low Current         | LOL  | WUS                |           |      | 4.0       | mA |

| Output Low Voltage         | VOL. | WUS, lol = 2 mA    |           |      | 0.5       | ٧  |

| Input Low Current          | LIL3 | TTL, HSn inputs    | -100      |      | 1         | μА |

| Input High Current         | LIH3 | TTL, HSn inputs    |           |      | 0.4       | mA |

3A-62

**■** 8253965 0014155 161 **■**

### READ CHARACTERISTICS, MR HEAD AMPLIFIER

Recommended operating conditions apply unless otherwise specified. Rmr = 23 $\Omega$ ; Rrc = 3.64K; Rwc = 1.33K

CL (RDX, RDY) < 20 pFRL (RDX, RDY) > 1K

| PARAMETER                             | CONDITION                                                                   | MIN  | NOM        | MAX  | UNIT     |

|---------------------------------------|-----------------------------------------------------------------------------|------|------------|------|----------|

| MR Head Resistance*                   |                                                                             | 10   | 23         | 32   | Ω        |

| MR Current Range                      |                                                                             | 4    | 11         | 16   | mA       |

| MR Current Gain AR                    | read mode                                                                   |      | 20         |      | mA/mA    |

|                                       | idle mode                                                                   |      |            | 0.01 | mA/mA    |

| MR Current Setting Voltage VRC        | read/write modes                                                            |      | 2          |      | ٧        |

| "Kr" Factor                           | Kr = Ar • Vrc                                                               | 36   | 40         | 44   | ٧        |

| MR Head Potential                     | selected head                                                               | -330 |            | 330  | mV       |

|                                       | unselected heads                                                            | -1.0 |            | -0.3 | ٧        |

| Unselected MR Current                 |                                                                             |      |            | 0.1  | mA       |

| Differential Voltage Gain             | Vin = 1 mVp-p @ 5 MHz                                                       | 125  | 150        | 180  | V/V      |

| Voltage BW                            | Rmr = 23Ω                                                                   | 80   |            |      | MHz      |

| -1 dB                                 | Lmr = 20 nH                                                                 | 80   |            |      | MHz      |

| -3 dB                                 | Vin = 1 mVp-p                                                               | 100  | ļ <u></u>  |      |          |

| Input Noise Voltage                   | exclude head noise, lmn = 10 mA                                             |      | 0.45       | 0.60 | nV/√Hz   |

| Input Noise Current                   | exclude head noise, IMR = 10 mA                                             |      | 20         |      | pA∕√H̄z̄ |

| Differential Input Resistance         | Vin = 1 mVp-p @ 5 MHz<br>C2 = C3 = 0.03 μF                                  | 900  |            |      | Ω        |

| Differential Input Capacitance        | Vin = 1 mVp-p @ 5 MHz<br>C2 = C3 = 0.03 μF                                  |      | 12         |      | pF       |

| Input Dynamic Range                   | AC input voltage where gain falls to 90% of its small signal value, @ 5 MHz | 8    |            |      | mVp-p    |

| CMRR                                  | Vin = 100 mVp-p @ 5 MHz                                                     | 45   |            |      | dB       |

| PSRR                                  | 100 mVp-p @ 5 MHz on<br>VCC or VEE                                          | 45   |            |      | dB       |

| Channel Separation                    | unselected channels driven with 100 mVp-p @ 5 MHz                           | 45   |            |      | dB       |

| Output Offset Voltage                 |                                                                             | -100 |            | 100  | mV       |

| MR Head Voltage Monitor VMR           |                                                                             |      | 264        |      | m∨       |

| Output Resistance                     | singled-ended                                                               |      | 35         | 70   | Ω        |

| Output Current                        |                                                                             | 1.5  | 2.2        |      | mA       |

| RDX/RDY Common Mode<br>Output Voltage |                                                                             |      | Vcc - 1.65 |      | V        |

| RDX/RDY High Imp Leakage              | write/ idle mode                                                            |      | 200        |      | μA       |

<sup>\*</sup> Maximum MR head resistance can be as high as 85 $\Omega$  if Is • Imr  $\leq$  660 mV.

3A-63

■ 8253965 DD14156 OT8 **■**

### **ELECTRICAL SPECIFICATIONS** (continued)

#### WRITE CHARACTERISTICS

Recommended operating conditions apply unless otherwise specified. W = 30 mA, Lh = 220 nH, Rh =  $25\Omega$

| PARAMETER                                  | CONDITION       | MIN | NOM | MAX | UNIT  |

|--------------------------------------------|-----------------|-----|-----|-----|-------|

| Write Current Range                        |                 | 10  |     | 40  | mA    |

| Write Current Gain Aw                      | write mode      |     | 20  |     | mA/mA |

| Write Current Setting Vwc<br>Voltage       | write/read mode |     | 2   |     | V     |

| "Kw" Factor                                | Kw = Aw • Vwc   | 36  | 40  | 44  | V     |

| Differential Head Voltage Swing            | open head       |     | 10  |     | Vp-p  |

| Unselected Head Current                    | DC              |     |     | 0.1 | mA    |

|                                            | AC              |     |     | 1   | mApk  |

| Head Differential Damping Rd<br>Resistance |                 | 360 | 450 | 540 | Ω     |

| Head Differential Load<br>Capacitance      |                 |     |     | 15  | pF    |

### **SWITCHING CHARACTERISTICS**

Recommended operating conditions apply unless otherwise specified.

Rmr = 23 $\Omega$ , 10% variation; Rrc = 3.64K; Rwc = 1.33K; CL (RDX, RDY) < 20 pF; C1 = 0.1  $\mu$ F

$C2 = C3 = 0.03 \mu F$

RL (RDX, RDY) > 1K; Lh = 220 nH, Rh =  $25\Omega$ ; F (WDX/WDY) = 5 MHz

| R/W     | Read to Write      | to 90% of write current                                 |     | 100 | ns |

|---------|--------------------|---------------------------------------------------------|-----|-----|----|

|         | Write to Read      | to within 100 mV of final                               | 1.0 | 2.0 | μs |

|         |                    | DC steady state                                         |     |     |    |

| CS      | Idle to Read       | to within 100 mV of final DC steady state               |     | 20  | μs |

| HSO, 1, | 2, 3 to any MR     | to within 100 mV of final                               |     | 5   | μs |

|         |                    | DC steady state                                         |     |     |    |

| wus     | Safe to Unsafe TD1 | write mode, from loss of WDX/WDY transition             | 0.7 | 1.4 | μs |

|         | Unsafe to Safe TD2 | fault cleared, from first positive (WDX-WDY) transition |     | 0.5 | μS |

3A-64

■ 8253965 0014157 T34 **■**

### **SWITCHING CHARACTERISTICS (continued)**

| PARAMETER               |                          | CONDITION                                                 | MIN | NOM | MAX | UNIT |

|-------------------------|--------------------------|-----------------------------------------------------------|-----|-----|-----|------|

| Head Current            | Propagation<br>Delay TD3 | 50% (WDX - WDY) to<br>50% (Ix - Iy)                       | 6   |     | 20  | ns   |

|                         | Rise/Fall Time           | lw = 30 mA, Lh = 220 nH,<br>Rh = 25Ω<br>10% to 90% points |     | 2.7 | 3.5 | ns   |

|                         |                          | lw = 30 mA, Lh = 0, Rh = 0                                |     | 1.1 |     | ns   |

| Write Current Asymmetry |                          | propagation delay difference                              |     |     | 0.5 | ns   |

FIGURE 1: 32R1562R Write Mode Timing

FIGURE 2: 32R1563R Write Mode Timing

3A-65

**■** 8253965 0014158 970 **■**

### PACKAGE PIN DESIGNATIONS

(Top View)

64-Lead TQFP

CAUTION: Use handling procedures necessary for a static sensitive component.

Advance Information: Indicates a product still in the design cycle, and any specifications are based on design goals only. Do not use for final design.

No responsibility is assumed by Silicon Systems for use of this product nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights or trademarks of Silicon Systems. Silicon Systems reserves the right to make changes in specifications at any time without notice. Accordingly, the reader is cautioned to verify that the data sheet is current before placing orders.

Silicon Systems, Inc., 14351 Myford Road, Tustin, CA 92680-7022 (714) 573-6000, FAX (714) 573-6914

02/20/96 - rev.

3A-66

©1994 Silicon Systems, Inc.

**=** 8253965 0014159 807 1