## **Programmable Peripheral** ZPSD4XX Family Field-Programmable Microcontroller Peripherals

# *Key Features* Complete family of Field Programmable Microcontroller Peripherals enables the user to efficiently implement a highly integrated embedded control system in a short time. The ZPSD4XX family has a variety of functions such as ZPLDs , I/O Ports, Power

Management, EPROM and SRAM.

- □ "No Glue-Logic" user programmable interface to 8 or 16 bit microcontroller multiplexed and non-multiplexed bus. The bus control logic can directly decode control signals generated by 8031, 80196, 80186, 68HC11, 68HC16, 683XX, 16000, Z80, and Z8 architecture. Extended address capability up to 24 bits of address.

- ❑ A range of ZPLD (Zero Power PLD) architectures have up to 24 macrocells, 59 inputs and 126 output product terms. The ZPSD4XX includes 2 functional ZPLDs which enable the user to efficiently implement a variety of state machines, logic functions, address decoding and control of the internal ZPSD4XX functional blocks.

- □ The ZPLDs use a Zero Power CMOS technology that reduces the device standby current to 5 uA typical. Unused product terms are disabled to reduce operating power.

- 40 I/O Ports that can be individually configured by the user as standard MCU I/O ports, PLD I/O, latched address outputs and special function I/O. Two eight bit I/O ports can be configured as Open Drain Outputs.

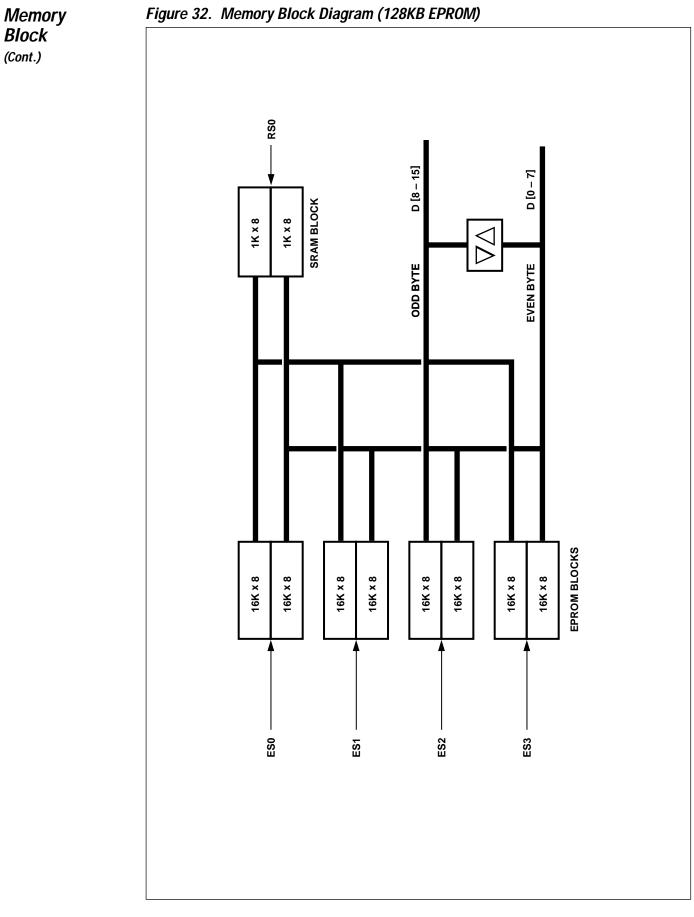

- ❑ The ZPSD4XX family contains EPROM densities of 256 Kbit, 512 Kbit and 1 Mbit that can be configured as 8 or 16 bit data width. The EPROM is divided into 4 equal blocks that can be mapped to different address spaces. Access time is 70 ns which includes address latching and decoding PLD. The EPROM has a low power mode that is controlled by the CMiser-Bit.

- ❑ The ZPSD4XX family contains a 16 Kbit scratch pad SRAM that can be configured as 8 or 16 bit data width. Access time is 70 ns which includes address latching and decoding PLD. The SRAM can be used as standby storage if standby power is supplied to the Vstdby pin. Switching between V<sub>CC</sub> and Vstdby occurs automatically.

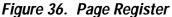

- □ Page Logic is connected to the ZPLDs and enables address space expansion of Microcontrollers with limited address space capability. Up to 16 pages are available.

- □ A security bit prevents reading the ZPSD4XX configuration, ZPLD and EPROM contents. This inhibits copying the device on a programmer.

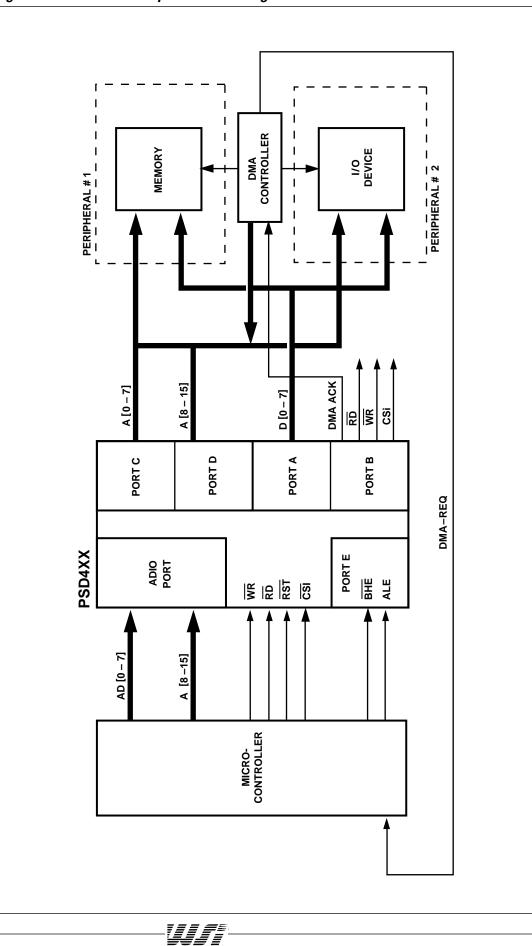

- Port A can be used as a buffered microcontroller data bus (Peripheral I/O Mode) of the microcontroller bus. This provides easy access to sub-systems that require more drive on the data bus or accessing a resource that is shared by another MCU or DMA Controller.

#### ZPSD4XX Family

| Key Features<br>(Cont.) | ZPSD4XX standard versions are ideal for general purpose applications                                                                                                                                                                                                                                                                                                                                 |                                                                                  |  |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|--|--|

|                         | <ul> <li>ZPSD4XXV versions (2.7.0 to 5.5 volt operation) are excellent for very low power applications</li> <li>ZPSD4XXM mask-programmable versions are ideal for code-stable, high-volume low cost applications.</li> </ul>                                                                                                                                                                         |                                                                                  |  |  |  |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |  |  |  |

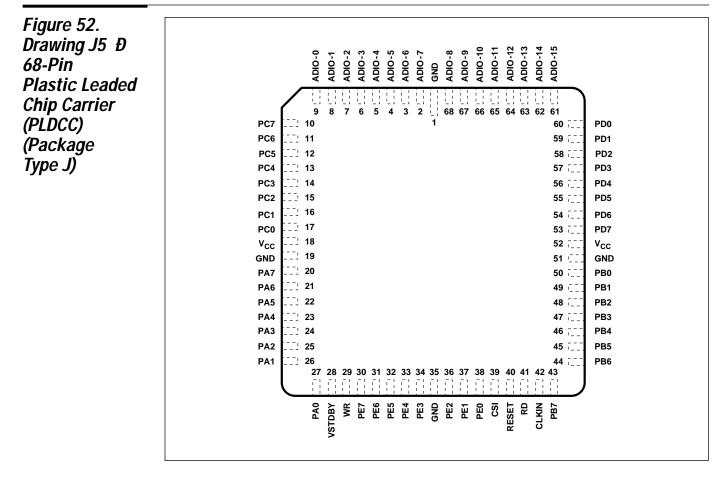

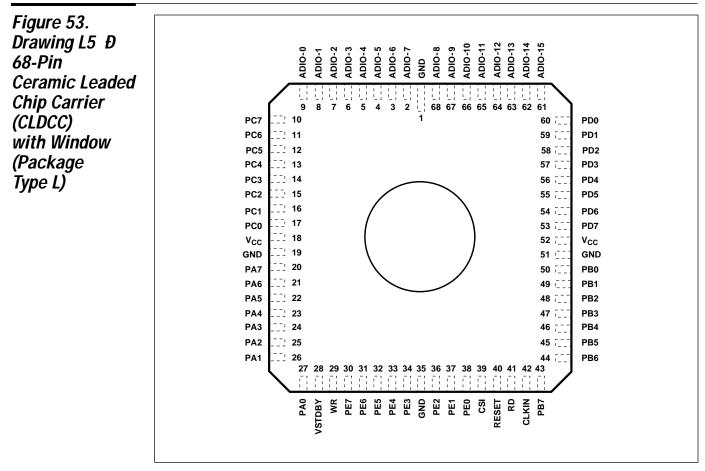

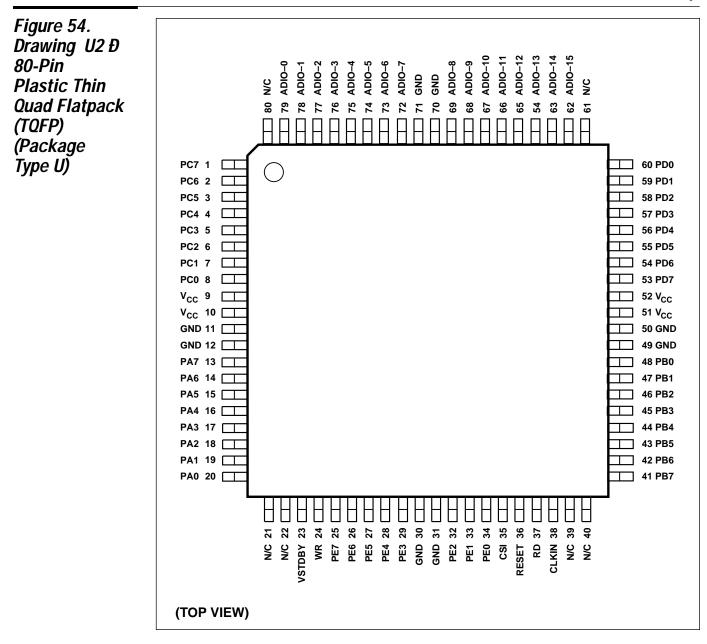

|                         | Package choices include 68 pin plastic (J) and ceramic (L) chip carriers.                                                                                                                                                                                                                                                                                                                            |                                                                                  |  |  |  |

|                         | □ The ZPSD4XX family is supported with PC based PSDsoft <sup>™</sup> MS-Windows <sup>®</sup> compatible development tools. Offering ABEL <sup>®</sup> as a design entry method (PSDabel <sup>™</sup> ), an efficient Fitter, Address Translator, MagicPro <sup>®</sup> programmer and a full chip simulator (SILOS III <sup>™</sup> from SIMUCAD <sup>™</sup> ) (PSDsim <sup>™</sup> ) are included. |                                                                                  |  |  |  |

|                         | ZPSD                                                                                                                                                                                                                                                                                                                                                                                                 | Portable and battery powered systems have recently become major embedded control |  |  |  |

| Background              | application segments. As a result, the demand for electronic components having extremely low power consumption has increased dramatically. Recognizing this peed, WSL lnc, has                                                                                                                                                                                                                       |                                                                                  |  |  |  |

application segments. As a result, the demand for electronic components having extremely low power consumption has increased dramatically. Recognizing this need, WSI, Inc. has developed a new ZPSD (Zero Power PSD) technology. ZPSD products virtually eliminate the DC component of power consumption reducing it to standby levels. Eliminating the DC component is the basis for the words "Zero Power" in the ZPSD name. ZPSD products also minimize the AC power component when the chip is changing states. The result is a programmable microcontroller peripheral family that replaces at least six discrete circuit functions while drawing much less power than a single EPROM. Integrated Power Management™ Operation Upon each address or logic input change to the ZPSD, the device powers up from low power standby for a short time. Then the ZPSD consumes only the necessary power to deliver new logic or memory data to its outputs as a response to the input change. After the new outputs are stable, the ZPSD latches them and automatically reverts back to standby mode. The I<sub>CC</sub> current flowing during standby mode and during DC operation is identical and is only a few microamperes.

The ZPSD automatically reduces its DC current drain to these low levels and does not require controlling by the CSI (Chip Select) input. Disabling the CSI pin unconditionally forces the ZPSD to standby mode independent of other input transitions.

The only significant power consumption in the ZPSD occurs during AC operation.

The ZPSD contains the first architecture to apply zero power techniques to memory circuit blocks as well as logic.

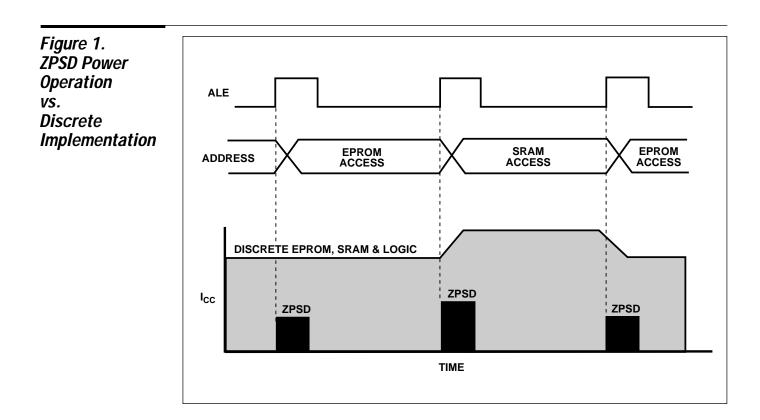

Figure 1 compares ZPSD zero power operation to the operation of a discrete solution. A standard microcontroller (MCU) bus cycle usually starts with an ALE (or AS) pulse and the generation of an address. The ZPSD detects the address transition and powers up for a short time. The ZPSD then latches the outputs of the PAD, EPROM and SRAM to the new values. After finishing these operations, the ZPSD shuts off its internal power, entering standby mode. The time taken for the entire cycle is less than the ZPSD's "access time."

The ZPSD will stay in standby mode if the address does not change between bus cycles (for example, looping on a single address or a Halt operation). In an alternate system implementation using discrete EPROM, SRAM and other discrete components, the system will consume operating power during the entire bus cycle. This is because the chip select inputs on the memory devices are usually active throughout the entire cycle. The AC power consumption of the ZPSD may be calculated using the ALE frequency.

*General Description* The ZPSD4XX series of Field Programmable Microcontroller Peripherals represent a major advance in the evolution of Programmable Peripherals. They combine an innovative architecture with state of the art technology to provide user programmability (logic, functions, memory), flexibility, high integration, optimum performance, and low power . For example, the PSD413A2 can implement a full peripheral subsystem and has the following features:

- □ Two ZPLDs with a total of 59 inputs, 126 product terms outputs, 24 macrocells and 24 I/O pins.

- □ 40 individually programmable I/O pins that are divided into 5 Ports.

- □ 4-Bit Page Register for external memory addressing

- □ 1 Mbit EPROM consisting of four 256 Kbit blocks.

- □ 16 Kbit of standby SRAM that can automatically switch into standby mode.

- Dever management unit with automatic standby and sleep modes.

- Security mode.

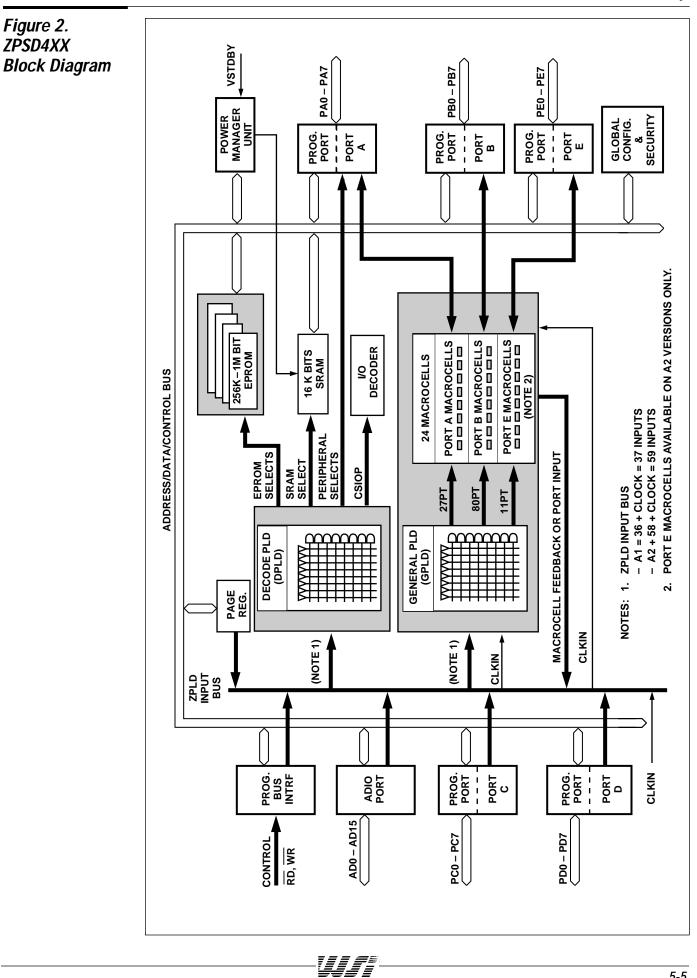

Figure 2 is a top level block diagram of the ZPSD4XX. Refer to Table 1 and other sections for details on functionality, DC/AC specifications, packages and ordering information.

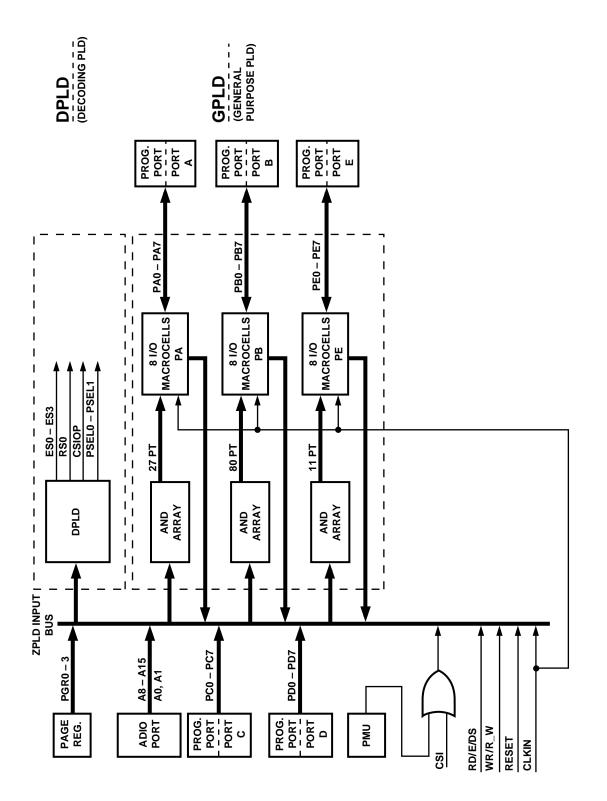

At the core of the ZPSD4XX are ZPLDs dedicated to the functions they perform:

- Decoding ZPLD (DPLD)

- General Purpose ZPLD (GPLD)

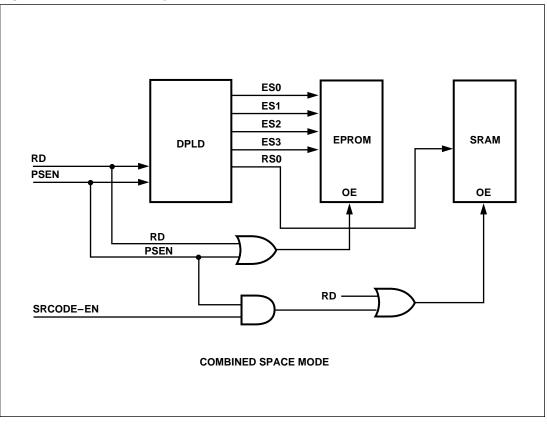

Both ZPLDs receive the same inputs through the ZPLD bus and are differentiated by their output destinations. The Decoder PLD (DPLD) has as its main function to perform address space decoding for the internal I/O Ports, four blocks of EPROM, standby SRAM and peripheral mode of Port A. The address decoding can be based on any address input, control signal (RD, PSEN, etc.) and page logic. Address inputs originate from either the microcontroller interface (ADIO Port) or other I/O Ports for additional decoding. The DPLD also supports special requirements of 8031 architecture based designs that need to store data in the EPROM or execute programs from the SRAM.

The general purpose PLD (GPLD) is a general purpose ZPLD that can be used to implement state machines and logic . The GPLD has up to 59 inputs, 118 product terms, 24 flexible macrocells and 24 I/O pins that are connected to Ports A, B and E. The GPLD can also decode the microcontroller address bus and generate chip selects to external peripherals or memories.

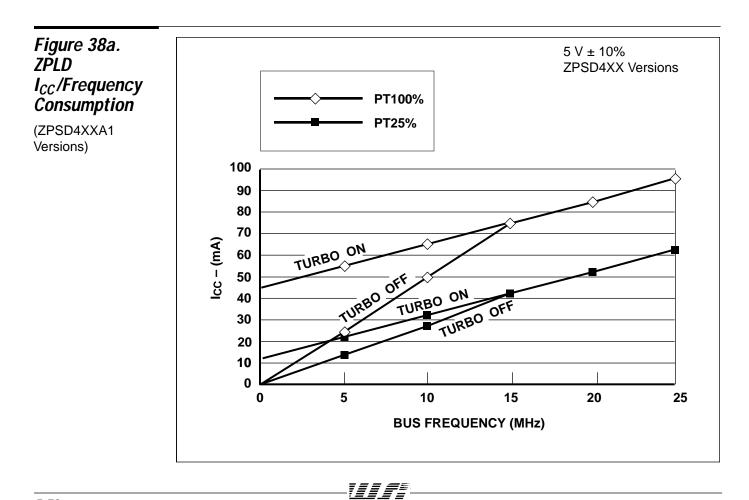

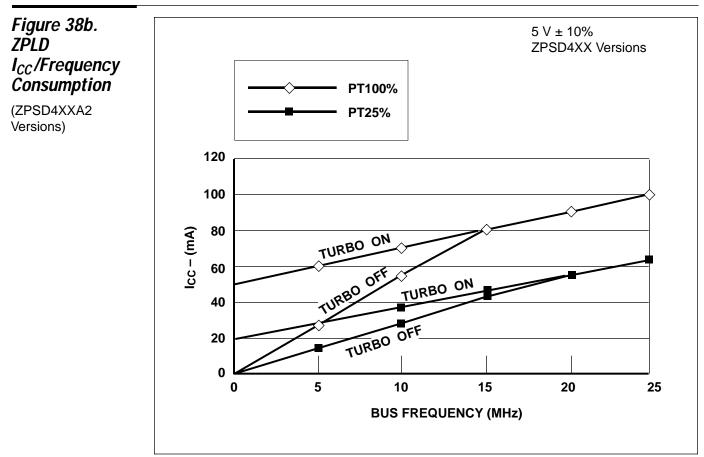

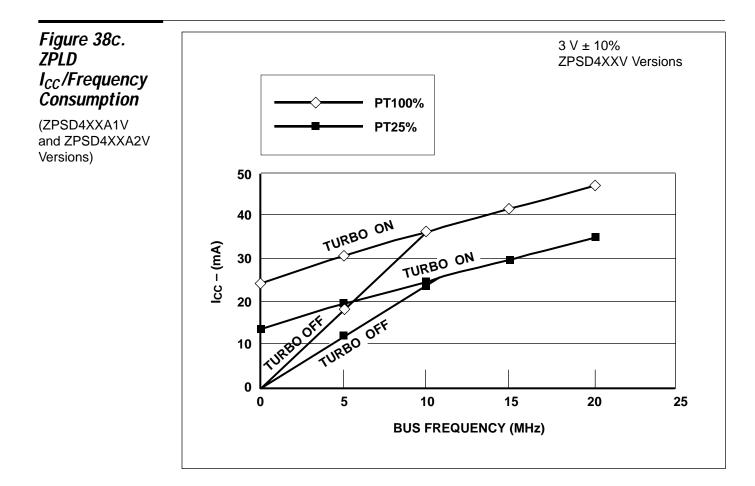

The ZPLDs are designed to consume minimum power using Zero Power design techniques. A configuration bit (Turbo bit), that can be set by the MCU, will automatically place the ZPLDs into standby if no inputs are changing. Any unused product terms will be turned off during programming and will not consume any power in the system.

The ZPSD4XX has 40 I/O pins that are divided into 5 ports. Each I/O pin can be individually configured to provide many functions. Ports A, B and E have the capability to be configured as standard MCU I/O ports, GPLD I/O, or latched address outputs for multiplexed address/data controllers. Ports C and D are standard I/O ports that can also be configured as ZPLD inputs or as a data bus for microcontrollers with a non-multiplexed bus.

The ZPSD4XX can easily interface with no "glue-logic" to a variety of 8 and 16-bit microcontrollers with a multiplexed or non-multiplexed bus. All of the control signals are connected to the two ZPLDs enabling the user to generate timing and decoding signals for external peripherals. For controllers that do not have a Reset output, the ZPSD4XX can generate a RESET output based on its RESET input. This input includes hysteresis.

General Description (Cont.)

The ZPSD4XX contains EPROM and scratchpad SRAM. The EPROM densities are 256 Kbit, 512 Kbit and 1 Mbit and are divided into four blocks. Each block can be located in a different address location. The access time of the EPROM includes the address latching and DPLD decoding. The 16 Kbit Standby SRAM may be used as an extension of the microcontroller SRAM and also to store backup information that is necessary after a system power down. Backup power to the SRAM is supplied by the Vstdby pin. Switching between  $V_{CC}$  and Vstdby occurs automatically when  $V_{CC}$  power is removed.

A four bit Page Register enables easy access to the I/O Section, EPROM and SRAM for microcontrollers with limited address space . The Page Register outputs are connected to all ZPLDs and can be used to page external devices as well as the internal ZPSD4XX functional units.

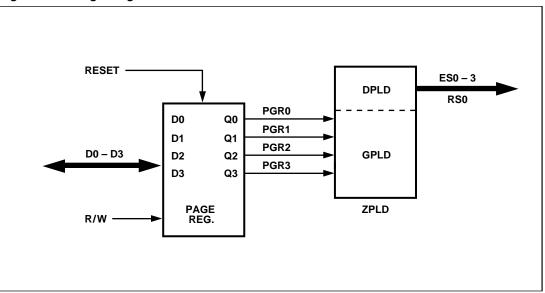

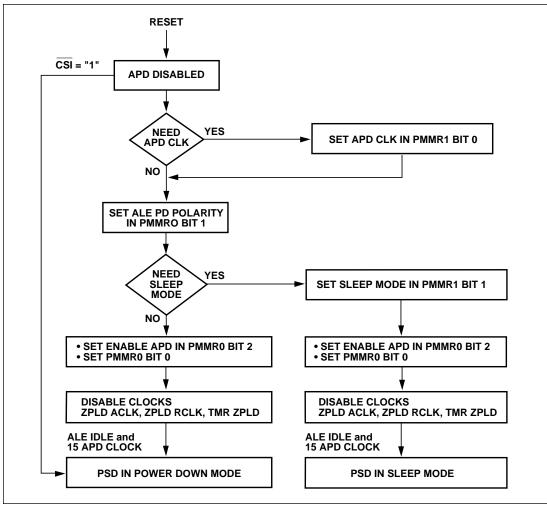

A Power Management Unit (PMU) in the ZPSD4XX enables the user to control the power consumption on selected functional blocks based on system requirements. For microcontrollers that do not generate a Chip Select input (CSI) to the peripheral device, the PMU includes an Automatic Power Down unit (APD) that will turn off the ZPSD4XX (into standby or sleep mode) based on inactivity of the ALE. The polarity of ALE inactivity can be defined by the user. In addition to standby mode, the ZPSD4XX includes a SLEEP mode that will reduce the power consumption to 1  $\mu$ A.

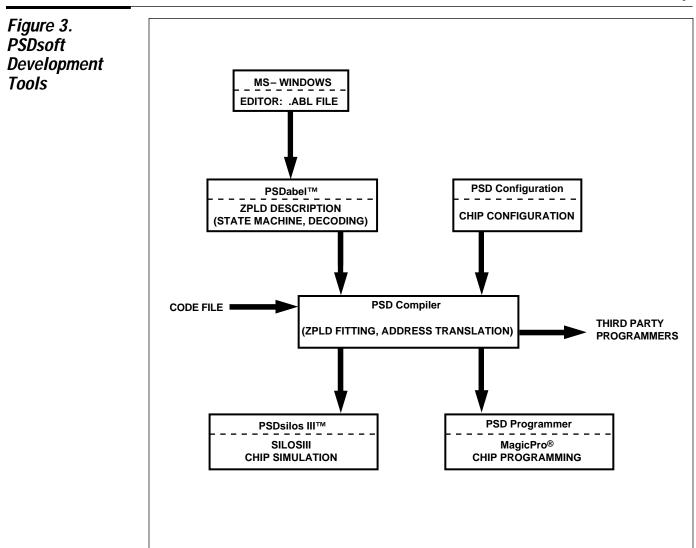

The ZPSD4XX family is supported by the WSI-PSD Development System (PSDsoft, see Figure 3) which runs under MS-Windows on the PC. Design entry is done using PSDabel which creates a minimized logic implementation. PSDabel also provides logic simulation of the ZPLD. The ZPSD4XX desired configuration is entered using a simple Windows based menu. The PSDcompiler, which consists of a Fitter and Address Translator, generates an object file from the PSDabel and MCU code files. The object file can be down loaded to a programmer (MagicPro<sup>®</sup>, Data I/O or other third party) or to PSDsim (Silos III Logic simulator) providing full chip simulation.

The ZPSD4XX standard versions include up to 1 Mb of EPROM, 16 Kbit SRAM, Decode PLD (DPLD), General Purpose PLD (GPLD), and five 8-bit I/O Ports. They are ideal for general purpose embedded systems applications.

The ZPSD4XXV low-voltage, low-power versions operate down to 2.7 volts and feature Sleep Mode current of only 1 microamp (typical).

The ZPSD4XXM mask-programmable versions deliver the lowest cost ZPSD4XX solution. See the Masked-PSD Ordering Information chapter in this databook for the mask-programmable ZPSD4XXM ordering procedure.

References in this document to ZPSD4XX versions are generic and also specifically include any "non-V" products (ZPSD4XX, ZPSD4XXM, and ZPSD4XXRM).

References to ZPSD4XXV versions include ZPSD4XXV and ZPSD4XXVM products.

References to ZPSD4XXM versions include ZPSD4XXM and ZPSD4XXVM products.

## ZPSD4XX Family

There are 12 unique devices in the PSD4XX family. The part classifications are based on ZPLD configuration and size, EPROM size, and data bus width. The features of each part are listed in Table 1.

| Table 1. |

|----------|

| ZPSD4XX  |

| Product  |

| Matrix   |

| Part     | Pue        | DPLD + GPLD |                  |                          | 1/0         |     |                | CDAM          |

|----------|------------|-------------|------------------|--------------------------|-------------|-----|----------------|---------------|

| Pan<br># | Bus<br>Bit | Inputs      | Product<br>Terms | Registered<br>Macrocells | I/O<br>Pins | PMU | EPROM<br>K Bit | SRAM<br>K Bit |

| 401A1    | x8/x16     | 37          | 113              | 8                        | 40          | Yes | 256            | 16            |

| 411A1    | x8         | 37          | 113              | 8                        | 40          | Yes | 256            | 16            |

| 402A1    | x8/x16     | 37          | 113              | 8                        | 40          | Yes | 512            | 16            |

| 412A1    | x8         | 37          | 113              | 8                        | 40          | Yes | 512            | 16            |

| 403A1    | x8/x16     | 37          | 113              | 8                        | 40          | Yes | 1024           | 16            |

| 413A1    | x8         | 37          | 113              | 8                        | 40          | Yes | 1024           | 16            |

| 401A2    | x8/x16     | 59          | 126              | 24                       | 40          | Yes | 256            | 16            |

| 411A2    | x8         | 59          | 126              | 24                       | 40          | Yes | 256            | 16            |

| 402A2    | x8/x16     | 59          | 126              | 24                       | 40          | Yes | 512            | 16            |

| 412A2    | x8         | 59          | 126              | 24                       | 40          | Yes | 512            | 16            |

| 403A2    | x8/x16     | 59          | 126              | 24                       | 40          | Yes | 1024           | 16            |

| 413A2    | x8         | 59          | 126              | 24                       | 40          | Yes | 1024           | 16            |

**NOTE:** PMU = Power Management Unit.

## *Table 2. ZPSD4XX Pin Descriptions*

The following table describes the pin names and pin functions of the ZPSD4XX. Pins that have multiple names and/or functions are defined by user configuration.

| Pin Name       | Pin Function                                                       | Туре                    | Function Descriptions                                                                                                                                                                                           |

|----------------|--------------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADIO0 – ADIO15 | Address/data bus                                                   | I/O                     | <ol> <li>Address/data bus, multiplexed<br/>bus mode</li> <li>Address bus, non-multiplexed<br/>bus mode</li> </ol>                                                                                               |

| RD             | Multiple Names<br>1. Read<br>2. <u>E</u><br>3. <u>DS</u><br>4. LDS | I                       | Multiple functions<br>1. Read signal<br>2. E signal (Clock)<br>3. Data strobe signal<br>4. Low byte data strobe                                                                                                 |

| WR             | Multiple Names<br>1. WR<br>2. <u>R/W</u><br>3. WRL                 | I                       | Multiple functions<br>1. Write signal<br>2. Read-write signal<br>3. Low byte write signal                                                                                                                       |

| CSI            | Chip Select Input                                                  | I                       | Active low, select ZPSD4XX standby mode if high.                                                                                                                                                                |

| RESET          | Reset Input                                                        | I                       | Reset I/O ports, ZPLD/macrocells,<br>and Configuration Registers.<br>Active low.                                                                                                                                |

| CLKIN          | Input clock                                                        | I                       | Clock input to ZPLD macrocells,<br>ZPLD Array and APD counter.<br>Connect to ground if Clock Input<br>not used.                                                                                                 |

| PA0 - PA7      | I/O Port A                                                         | I/O                     | <ul> <li>Multiple functions</li> <li>1. I/O port</li> <li>2. ZPLD/macrocell I/O port</li> <li>3. Latched address outputs<br/>(PA0 – PA7) → (A0 – A7)</li> <li>4. High address inputs (A16 – A23)</li> </ul>     |

| PB0 – PB7      | I/O Port B                                                         | I/O                     | <ul> <li>Multiple functions</li> <li>1. I/O port</li> <li>2. ZPLD/macrocell I/O port</li> <li>3. Latched address outputs<br/>(PB0–PB7) → (A0–A7) or (A8–A15)</li> </ul>                                         |

| PC0 – PC7      | I/O Port C                                                         | I/O<br>CMOS<br>or<br>OD | <ul> <li>Multiple functions</li> <li>1. I/O port</li> <li>2. ZPLD input port*</li> <li>3. Latched address outputs<br/>(PC0 – PC7) → (A0–A7)</li> <li>4. Data Port (D0 – D7,<br/>non-multiplexed bus)</li> </ul> |

| PD0 – PD7      | I/O Port D                                                         | I/O<br>CMOS<br>or<br>OD | Multiple functions<br>1. I/O port<br>2. ZPLD input port*<br>3. Latched address outputs<br>(PD0-PD7) $\rightarrow$ (A0-A7) or (A8-A15)<br>4. Data Port (D8-D15,<br>non-multiplexed bus)                          |

\*Available only in ZPSD4XXA2 Series.

Table 2. ZPSD4XX Pin Descriptions (Cont.)

| Pin Name        | Pin Function                                                                                     | Туре | Function Descriptions                                                                                                                                                                                                                            |

|-----------------|--------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PEO             | Port PE, pin 0<br>1. BHE<br>2. PSEN<br>3. WRH<br>4. UDS<br>5. SIZO<br>6. PE0<br>7. PE0<br>8. PE0 | I/O  | Multiple functions<br>1. High byte enable, 16 bit data<br>2. Read program memory, 8031 signal<br>3. Write high data byte<br>4. Upper Data Strobe<br>5. Byte enable, 68300 signal<br>6. I/O pin<br>7. ZPLD I/O pin<br>8. Latched Address Out – A0 |

| PE1             | Port PE, pin 1<br>1. ALE<br>2. PE1<br>3. PE1<br>4. PE1                                           | I/O  | Multiple functions<br>1. Address strobe<br>2. I/O pin<br>3. ZPLD I/O pin<br>4. Latched Address Out – A1                                                                                                                                          |

| PE2             | Port PE, pin 2<br>1. PE2<br>2. PE2<br>3. PE2                                                     | I/O  | Multiple functions<br>1. I/O pin<br>2. ZPLD I/O pin*<br>3. Latched Address Out – A2                                                                                                                                                              |

| PE3             | Port PE, pin 3<br>1. PE3<br>2. PE3<br>3. PE3                                                     | I/O  | Multiple functions<br>1. I/O pin<br>2. ZPLD I/O pin*<br>3. Latched Address Out – A3                                                                                                                                                              |

| PE4             | Port PE, pin 4<br>1. PE4<br>2. PE4<br>3. PE4                                                     | I/O  | Multiple functions<br>1. I/O pin<br>2. ZPLD I/O pin*<br>3. Latched Address Out – A4                                                                                                                                                              |

| PE5             | Port PE, pin 5<br>1. PE5<br>2. PE5<br>3. PE5                                                     | I/O  | Multiple functions<br>1. I/O pin<br>2. ZPLD I/O pin*<br>3. Latched Address Out – A5                                                                                                                                                              |

| PE6             | Port PE, pin 6<br>1. PE6<br>2. PE6<br>3. PE6                                                     | I/O  | Multiple functions<br>1. I/O pin<br>2. ZPLD I/O pin*<br>3. Latched Address Out – A6                                                                                                                                                              |

| PE7             | Port PE, pin 7<br>1. APD CLK<br>2. PE7<br>3. PE7<br>4. PE7                                       | I/O  | Multiple functions<br>1. Automatic Power Down Clock Input<br>2. I/O pin<br>3. ZPLD I/O pin*<br>4. Latched Address Out – A7                                                                                                                       |

| Vstdby          | Vstdby                                                                                           | I    | SRAM power pin for standby operation (battery backup)                                                                                                                                                                                            |

| V <sub>CC</sub> | V <sub>CC</sub>                                                                                  | I    | V <sub>CC</sub> power pin                                                                                                                                                                                                                        |

| GND             | GND                                                                                              | I    | Ground pin                                                                                                                                                                                                                                       |

\*Available only in ZPSD4XXA2 series.

| The ZPSD4XX<br>Architecture | <ul> <li>ZPSD4XX consists of five major functional blocks:</li> <li>ZPLD Block</li> <li>Bus Interface</li> <li>I/O Ports</li> <li>Memory Block</li> <li>Power Management Unit</li> </ul> The functions of each block are described in the following sections. Many of the blocks perform multiple functions, and are user configurable. The chip configurations are specified by the user in the PSDsoft Development Software. Other configurations are specified by setting up the appropriate bits in the configuration registers during run time.                             |  |  |  |  |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| The ZPLD<br>Block           | The ZPSD4XX series devices provide two ZPLD configurations. The ZPLD in the <b>ZPSD4XXA1</b> devices has 8 registered macrocells, 8 combinatorial macrocells, and up to 113 product terms.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                             | The <b>ZPSD4XXA2</b> has a full function ZPLD with 24 registered macrocells and up to 126 product terms.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| The ZPSD4XXA1<br>ZPLD Block | Key Features         2 Embedded ZPLD devices         8 registered and 8 combinatorial macrocells         Combinatorial/registered outputs         Maximum 113 product terms         Programmable output polarity         User configured register clear/preset         User configured register clock input         37 Inputs         Power Saving Mode         UV-Erasable                                                                                                                                                                                                      |  |  |  |  |

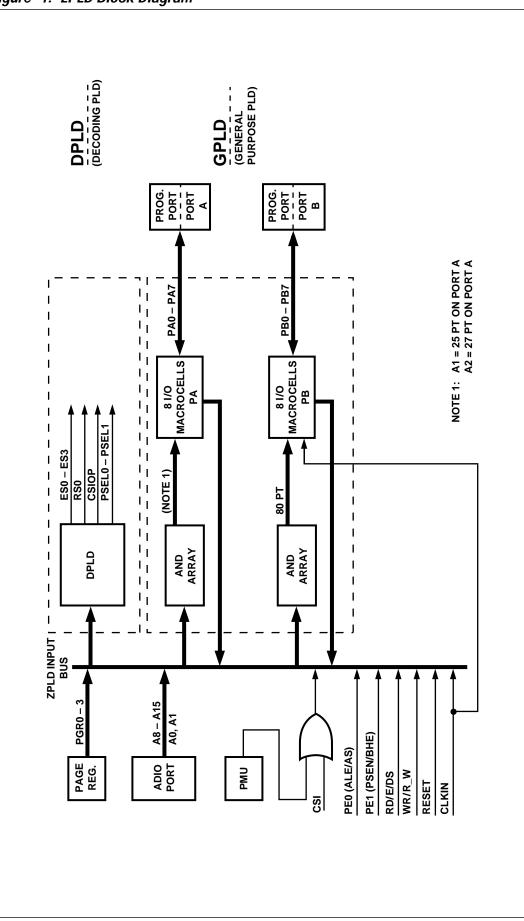

|                             | <ul> <li>General Description</li> <li>The ZPLD block has 2 embedded PLD devices:</li> <li>DPLD<br/>The Address Decoding PLD, generating select signals to internal I/O or memory blocks.</li> <li>GPLD<br/>The General Purpose PLD provides 8 registered and combinatorial programmable<br/>macrocells for general or complex logic implementation; dedicated to user application.</li> <li>Figure 4 shows the architecture of the ZPLD. The PLD devices all share the same input<br/>bus. The true or complement of the 37 input signals are fed to the programmable</li> </ul> |  |  |  |  |

bus. The true or complement of the 37 input signals are fed to the programmable AND-ARRAY. Names and sources of the input signals are shown in Table 3. The PB signals, depending on user configuration, can either be macrocell feedbacks or inputs from Port B.

**US**

#### Table 3. ZPLD Input Signals

| Signal Name      | From                                      |

|------------------|-------------------------------------------|

| PA0 - PA7        | Port A inputs or Macrocell PA feedback    |

| PB0 – PB7        | Port B inputs or Macrocell PB feedback    |

| PE0 – PE1        | Port E inputs (signals ALE, PSEN/BHE)     |

| PGR0 – PGR3      | Page Mode Register                        |

| A8 – A15, A0, A1 | MCU Address Lines                         |

| RD/E/DS          | MCU bus signal                            |

| WR/R_W           | MCU bus signal                            |

| CLKIN            | Input Clock                               |

| RESET            | Reset input                               |

| CSI              | CSI input (ORed with power down from PMU) |

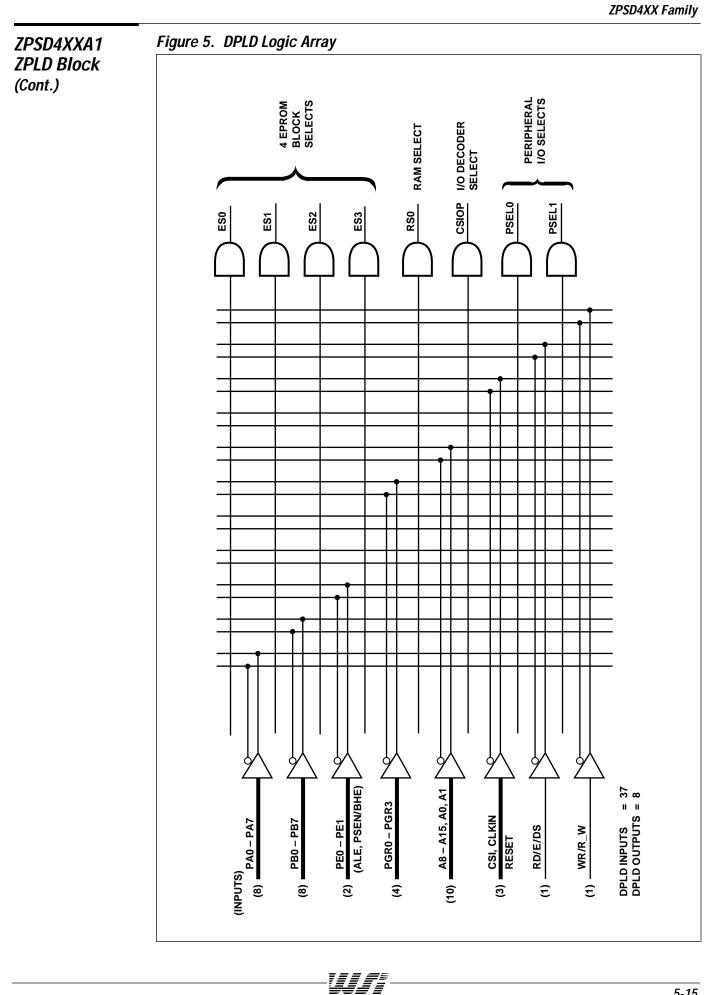

#### The DPLD

The DPLD is used for internal address decoding generating the following eight chip select signals:

🖵 ESO Ð ES3

EPROM selects, block 0 to block 3

🗆 RSO

SRAM block select

CSIOP

I/O Decoder chip select

Description PSEL0 Description PSEL0 Description

Peripheral I/O mode select signals

The I/O Decoder enabled by the CSIOP generates chip selects for on-chip registers or I/O ports based on address inputs A[7:0].

As shown in Figure 5, the DPLD consists of a large programmable AND ARRAY. There are a total of 37 inputs and 8 outputs. Each output consists of a single product term. Although the user can generate select signals from any of the inputs, the select signals are typically a function of the address and Page Register inputs. The select signals are defined by the user in the ABEL file (PSDabel).

The address line inputs to the DPLD include A0, A1 and A8 – A15. If more address lines are needed, the user can bring in the lines through Port A to the DPLD.

## ZPSD4XXA1 ZPLD Block

(Cont.)

#### The GPLD

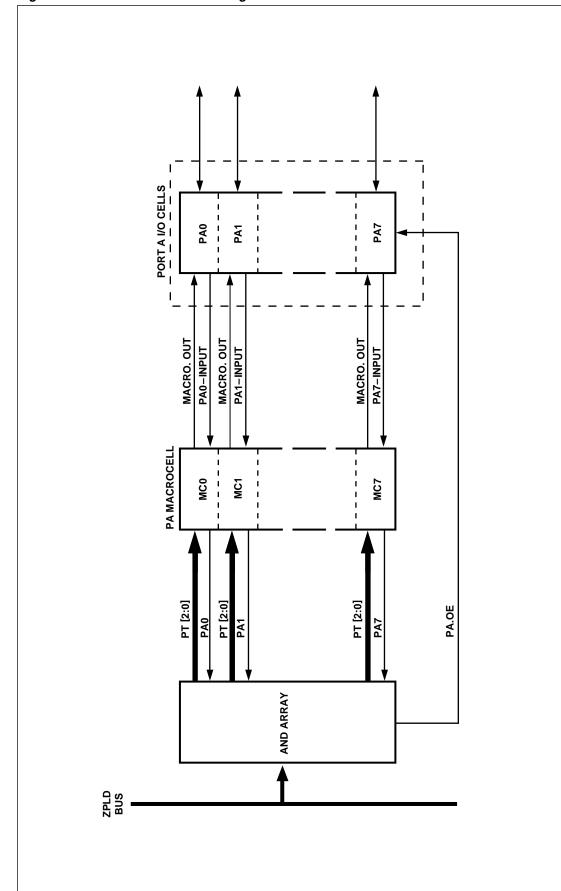

The structure of the General Purpose PLD consists of a programmable AND ARRAY and 2 sets of I/O Macrocells. The ARRAY has 37 input signals, same as the DPLD. From these inputs, "ANDed" functions are generated as product term inputs to the macrocells. The I/O Macrocell sets are named after the I/O Ports they are linked to, e.g., the macrocells connected to Port B are named PB Macrocells. The PB macrocells are registered macrocells with D-type flip-flops, where PA consists of combinatorial macrocells.

#### PA Macrocell Structure

Figure 6 shows the PA Macrocell block, which consists of 8 identical combinatorial macrocells. Each macrocell output can be connected to its own I/O pin on Port A. There is one user programmable global product term that is output from the GPLD's AND ARRAY which is shared by all the macrocells in Port A:

#### D PA.OE

Enable or tri-state Port A output pins

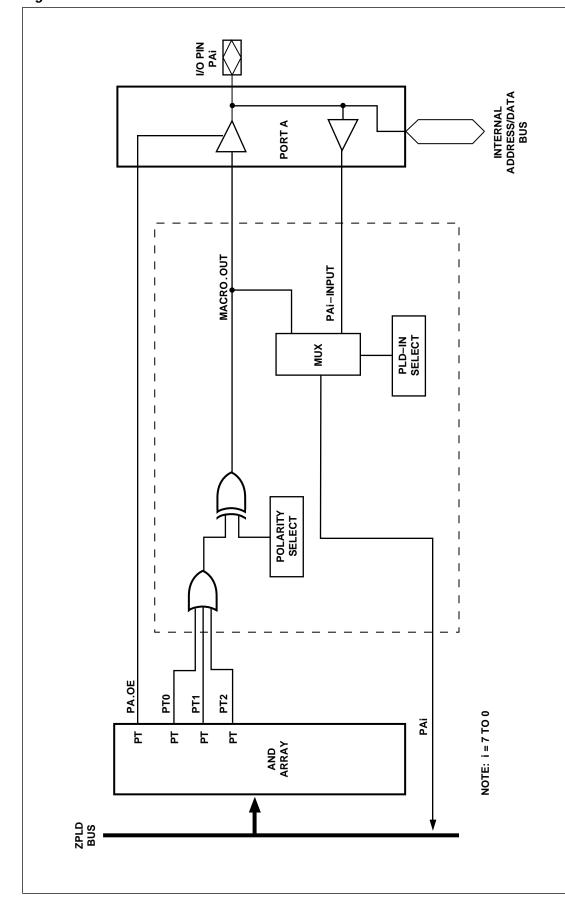

The circuit of a PA Macrocell is shown in Figure 7. There are 4 product terms from the GPLD's AND ARRAY as inputs to the macrocell. Users can select the polarity of the output, and configure the macrocell to operate as:

#### GPLD Input

Use Port A pin as dedicated input

GPLD Output

Use Port A pin as dedicated output

## Figure 6. PA Macrocell Block Diagram

## ZPSD4XXA1 ZPLD Block (Cont.)

**US**

## Figure 7. PA Macrocell

## ZPSD4XXA1 ZPLD Block

**W**f

5-17

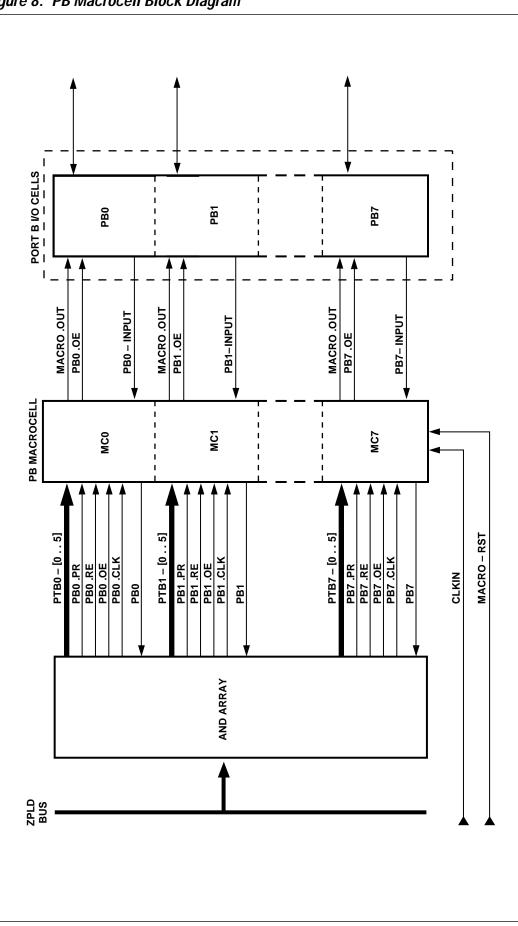

#### Port B Macrocell Structure

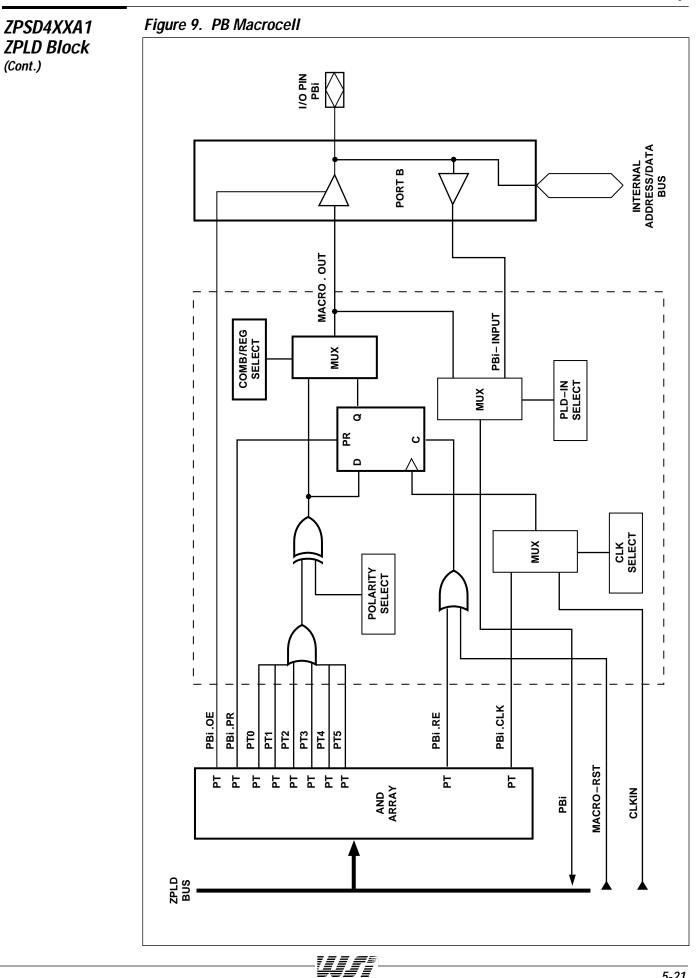

Figure 8 shows the PB Macrocell block, which consists of 8 identical macrocells. Each macrocell output can be connected to its own I/O pin on Port B. The two inputs, CLKIN and MACRO-RST, are used as clock and clear inputs to all the macrocells. The CLKIN comes directly from the CLKIN input pin. The MACRO-RST is the same as the Reset input pin except it is user configurable.

The circuit of a PB Macrocell is shown in Figure 9. There are 10 product terms from the GPLDs AND ARRAY as inputs to the macrocell. Users can select the polarity of the output, and configure the macrocell to operate as:

#### **Registered Output**

Select output from D flip flop.

- Combinatorial Output Select output from OR gate.

- GPLD Input Use Port B pin as dedicated input.

- GPLD Output Use Port B pin as dedicated output.

- GPLD I/O

Use Port B pin as bidirectional pin.

#### □ Macrocell Feedback

Register feedback for state machine implementations or expander feedback from the combinatorial output, to possibly expand the number of product terms available to another macrocell.

In case of "Buried Feedback", where the output of the macrocell is not connected to a Port B pin, Port B can be configured to perform other user defined I/O functions.

Each D flip flop in the macrocells has its own dedicated asynchronous clear, preset and clock input. The signals are defined as follow:

#### PRESET

Active only if defined by a product term (PBi.PR)

Two selectable inputs: Reset input and/or user defined product term (PBi.RE)

Two selectable inputs – CLKIN input or user defined product term (PBi.CLK). The macrocell is operated in Synchronous Mode if the clock input is CLKIN, and is in Asynchronous Mode if the clock is a product-term clock defined by the user.

Figure 10 shows the input/output path of a PB macrocell to the Port pin with which it is associated. If the Port pin is specified as a PB output pin in the PSDsoft, the MUX in the I/O Port Cell selects the PB Macrocell as an output of the Port pin. The output enable signal to the buffer in the I/O cell can be controlled by a product term from the AND Array.

If the Port pin is specified as a ZPLD input pin, the MUX in the PB Macrocell selects the Port input signal to be one of the 61 signals in the ZPLD Input Bus.

#### The ZPLD Power Management

The ZPLD implements a Zero Power Mode, which provides considerable power savings for low to medium frequency operations. To enable this feature, the ZPLD Turbo bit in the Power Management Mode Register 0 (PMMR0) has to be turned off.

If none of the inputs to the ZPLD are switching for a time period of 90ns, the ZPLD puts itself into Zero Power Mode and the current consumption is minimal. The ZPLD will resume normal operation as soon as one or more of the inputs change state.

Two other features of the ZPLD provide additional power savings:

#### 1. Clock Disable:

Users can disable the clock input to the ZPLD and/or macrocells,thereby reducing AC power consumption.

#### 2. Product Term Disable:

Unused product terms in the ZPLD are disabled by the PSDsoft Software automatically for further power savings.

The ZPLD power configuration is described in the Power Management Unit section.

**W**f

5-21

The ZPSD4XXA2 ZPLD Block

#### Key Features

- 2 Embedded ZPLD devices

- 24 macrocells

- □ Combinatorial/registered outputs

- □ Maximum 126 product terms

- Programmable output polarity

- □ User configured register clear/preset

- User configured register clock input

- 59 Inputs

- □ Accessible via 24 I/O pins

- Power Saving Mode

- UV-Erasable

#### **General Description**

The ZPLD block has 2 embedded PLD devices:

🖵 DPLD

The Address Decoding PLD, generating select signals to internal I/O or memory blocks.

🖵 GPLD

The General Purpose PLD provides 24 programmable macrocells for general or complex logic implementation; dedicated to user application.

Figure 11 shows the architecture of the ZPLD. The PLD devices all share the same input bus. The true or complement of the 59 input signals are fed to the programmable AND-ARRAY. Names and source of the input signals are shown in Table 4. The PA, PB, PE signals, depending on user configuration, can either be macrocell feedbacks or inputs from Port A, B or E.

**W**S

#### Table 4. ZPLD Input Signals

| Signal Name      | From                                      |

|------------------|-------------------------------------------|

| PA0 - PA7        | Port A inputs or Macrocell PA feedback    |

| PB0 – PB7        | Port B inputs or Macrocell PB feedback    |

| PE0 – PE7        | Port E inputs or Macrocell PE feedback    |

| PC0 – PC7        | Port C inputs                             |

| PD0 – PD7        | Port D inputs                             |

| PGR0 – PGR3      | Page Mode Register                        |

| A8 – A15, A0, A1 | MCU Address Lines                         |

| RD/E/DS          | MCU bus signal                            |

| WR/R_W           | MCU bus signal                            |

| CLKIN            | Input Clock                               |

| RESET            | Reset input                               |

| CSI              | CSI input (ORed with power down from PMU) |

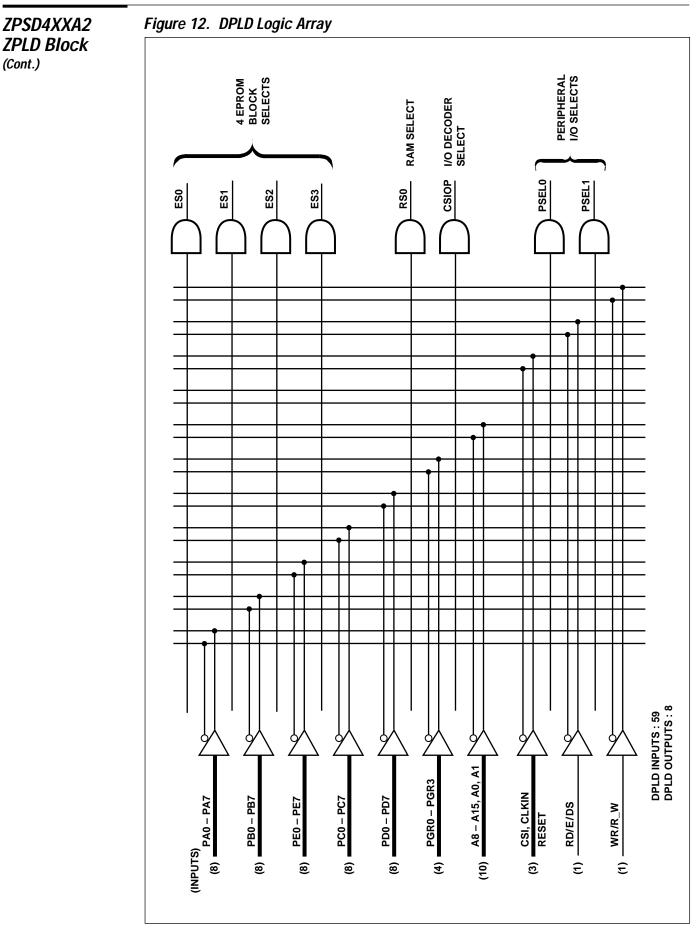

#### The DPLD

The DPLD is used for internal address decoding generating the following eight chip select signals:

🖵 ESO Ð ES3

EPROM selects, block 0 to block 3

🗆 RS0

SRAM block select

CSIOP

I/O Decoder chip select

Description PSEL1

Peripheral I/O mode select signals

The I/O Decoder enabled by the CSIOP generates chip selects for on-chip registers or I/O ports based on address inputs A[7:0].

As shown in Figure 12, the DPLD consists of a large programmable AND ARRAY. There are a total of 59 inputs and 8 outputs. Each output consists of a single product term. Although the user can generate select signals from any of the inputs, the select signals are typically a function of the address and Page Register inputs. The select signals are defined by the user in the ABEL file (PSDabel).

The address line inputs to the DPLD include A0, A1 and A8 – A15. If more address lines are needed, the user can bring in the lines through Port A to the DPLD.

#### **ZPSD4XX** Family

**W**S

#### The GPLD

The structure of the General Purpose PLD consists of a programmable AND ARRAY and 3 sets of I/O Macrocells. The ARRAY has 59 input signals, same as the DPLD. From these inputs, "ANDed" functions are generated as product term inputs to the macrocells. The I/O Macrocell sets are named after the I/O Ports they are linked to, e.g., the macrocells connected to Port A are named PA Macrocells. The 3 sets of macrocells, PA, PB and PE, are similar in structure and function.

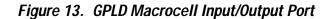

Figure 13 shows the output/input path of a GPLD macrocell to the Port pin with which it is associated. If the Port pin is specified as a GPLD output pin in PSDsoft, the MUX in the I/O Port Cell selects the GPLD macrocell as an output of the Port pin. The output enable signal to the buffer in the I/O cell can be controlled by a product term from the AND ARRAY.

If the Port pin is specified as a ZPLD input pin, the MUX in the GPLD macrocell selects the Port input signal to be one of the 61 signals in the ZPLD Input Bus.

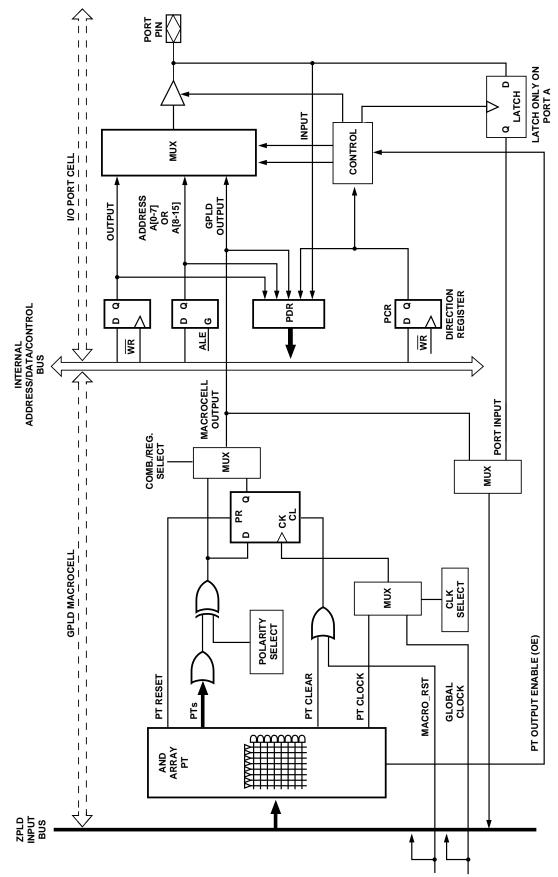

#### Port A Macrocell Structure

Figure 14 shows the PA Macrocell block, which consists of 8 identical macrocells. Each macrocell output can be connected to its own I/O pin on Port A. There are 3 user programmable global product terms output from the GPLD's AND ARRAY which are shared by all the macrocells in Port A:

DA.OE

Enable or tri-state Port A output pins

🖵 pa.pr

Preset D flip flop in the macrocells

PA.RE

Reset/Clear D flip flop in the macrocells

Two other inputs, CLKIN and MACRO-RST, are used as clock and clear inputs to the D flip flop. The CLKIN comes directly from the CLKIN input pin. The MACRO-RST is the same as the Reset input pin except it is user configurable.

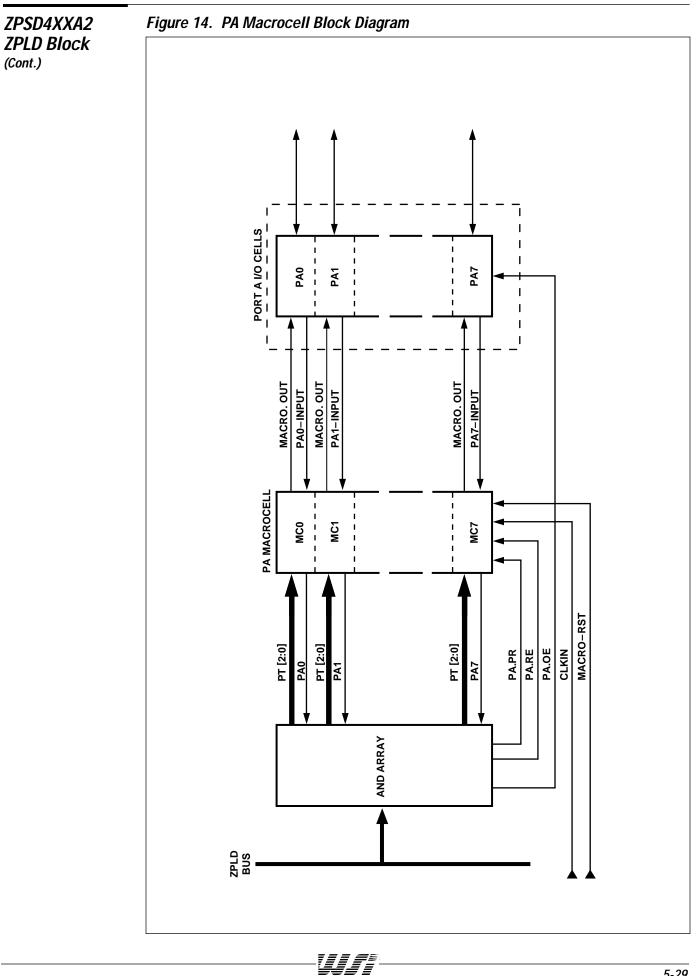

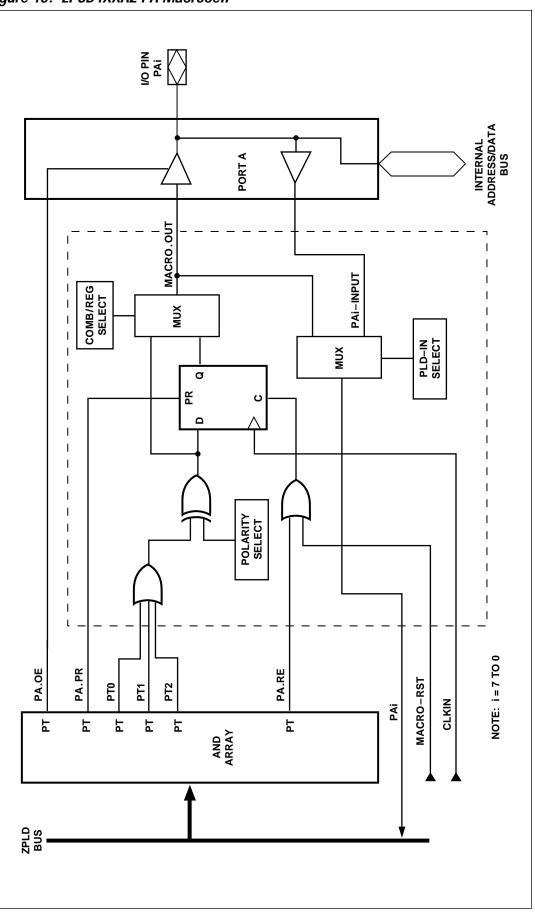

The circuit of a PA Macrocell is shown in Figure 15. There are 6 product terms from the GPLD's AND ARRAY as inputs to the macrocell. Users can select the polarity of the output, and configure the macrocell to operate as:

Registered Output

Select output from D flip flop

- Combinatorial Output Select output from OR gate

- GPLD Input

Use Port A pin as dedicated input

GPLD Output

Use Port A pin as dedicated output

GPLD I/O

Use Port A pin as bidirectional pin

□ Macrocell Feedback

Register feedback for state machine implementations or expander feedback from the combinatorial output, to expand the number of product terms available to another macrocell.

In case of "Buried Feedback", where the output of the macrocell is not connected to a Port A pin, Port A can be configured to perform other user defined I/O functions.

The two global product terms assigned for asynchronous clear (PA.RE) and preset (PA.PR) are mainly for proper PA Macrocell initialization. The macrocell flip-flop can also be cleared during reset by MACRO-RST, if such an option is chosen. The clock source is always the input clock CLKIN.

**W**S

**W**f

## ZPSD4XXA2 ZPLD Block

#### (Cont.)

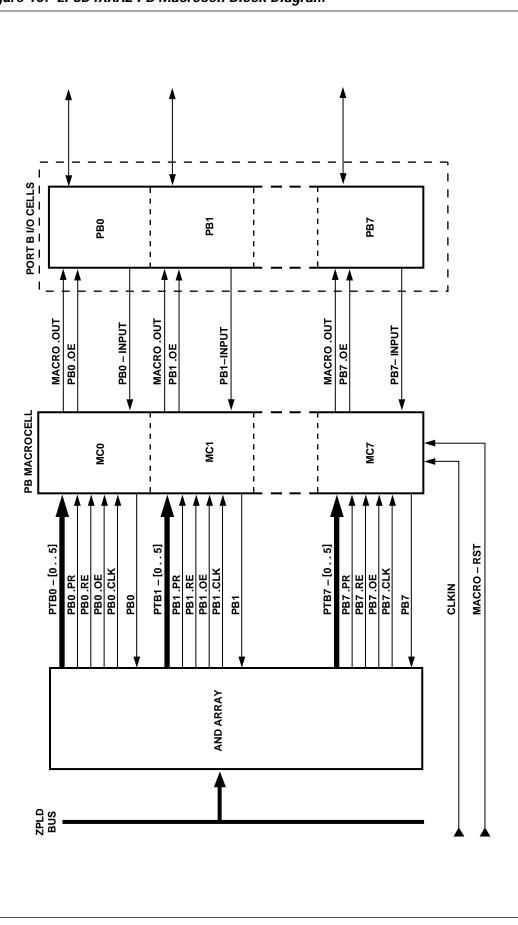

#### Port B Macrocell Structure

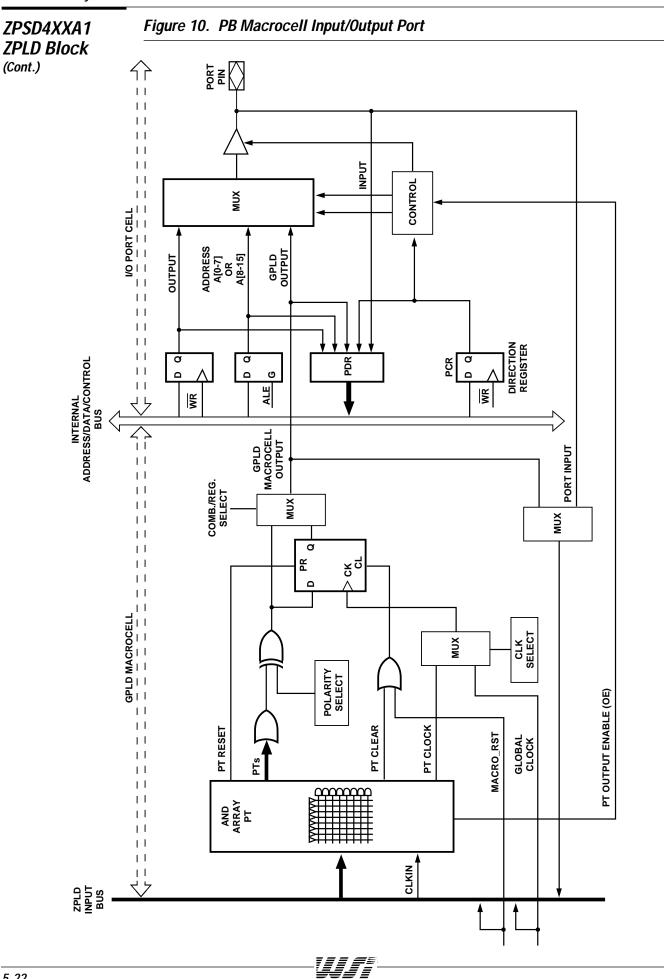

Figure 16 shows the PB Macrocell block, which consists of 8 identical macrocells. Each macrocell output can be connected to its own I/O pin on Port B. The two inputs, CLKIN and MACRO-RST, are used as clock and clear inputs to all the macrocells. The CLKIN comes directly from the CLKIN input pin. The MACRO-RST is the same as the Reset input pin except it is user configurable.

The circuit of a PB Macrocell is shown in Figure 17. There are 10 product terms from the GPLD's AND ARRAY as inputs to the macrocell. Users can select the polarity of the output, and configure the macrocell to operate as:

#### **Registered Output**

Select output from D flip flop.

#### **Combinatorial Output**

Select output from OR gate.

GPLD Input Use Port B pin as dedicated input.

#### GPLD Output

Use Port B pin as dedicated output.

GPLD I/O

Use Port B pin as bidirectional pin.

#### □ Macrocell Feedback

Register feedback for state machine implementations or expander feedback from the combinatorial output, to possibly expand the number of product terms available to another macrocell.

In case of "Buried Feedback", where the output of the macrocell is not connected to a Port B pin, Port B can be configured to perform other user defined I/O functions.

Each D flip flop in the macrocells has its own dedicated asynchronous clear, preset and clock input. The signals are defined as follow:

#### PRESET

Active only if defined by a product term (PBx.PR)

####

Two selectable inputs: Reset input or user defined product term (PBx .RE)

🗆 CLK

Two selectable inputs – CLKIN input or user defined product term (PBx.CLK). The macrocell is operated in Synchronous Mode if the clock input is CLKIN, and is in Asynchronous Mode if the clock is a product-term clock defined by the user.

**W**f

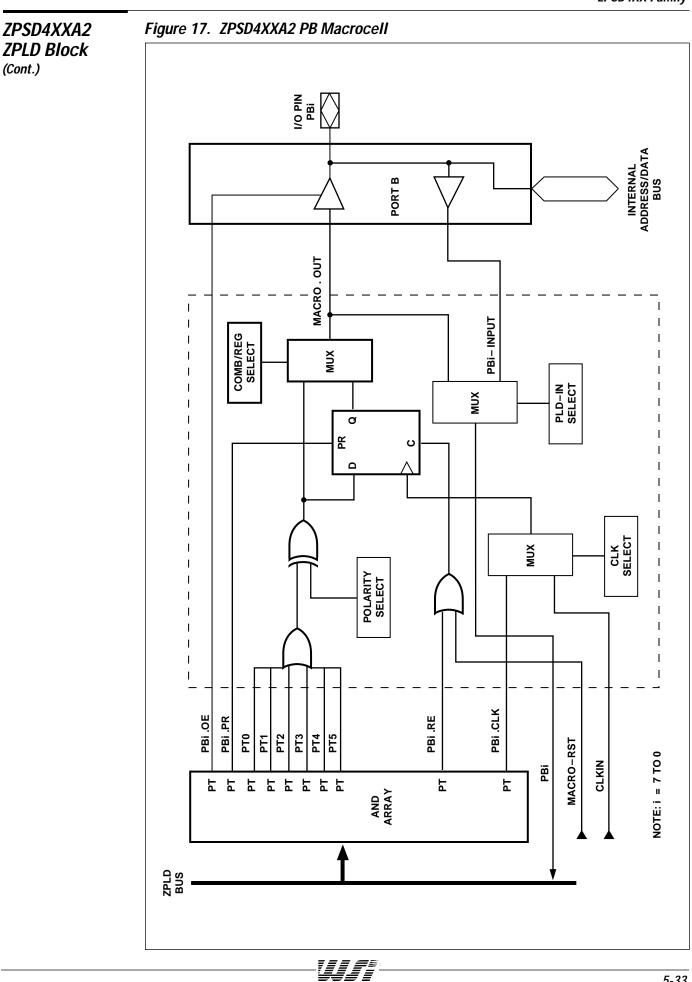

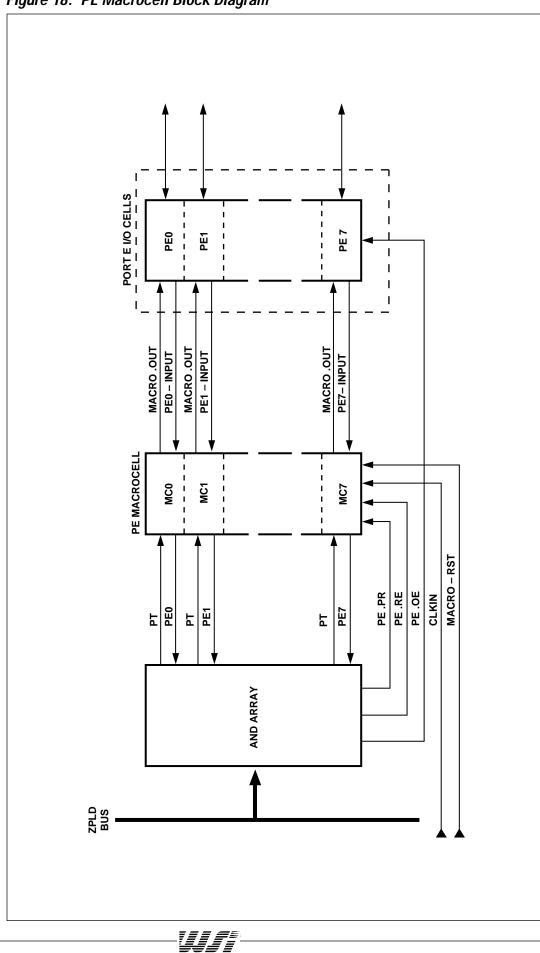

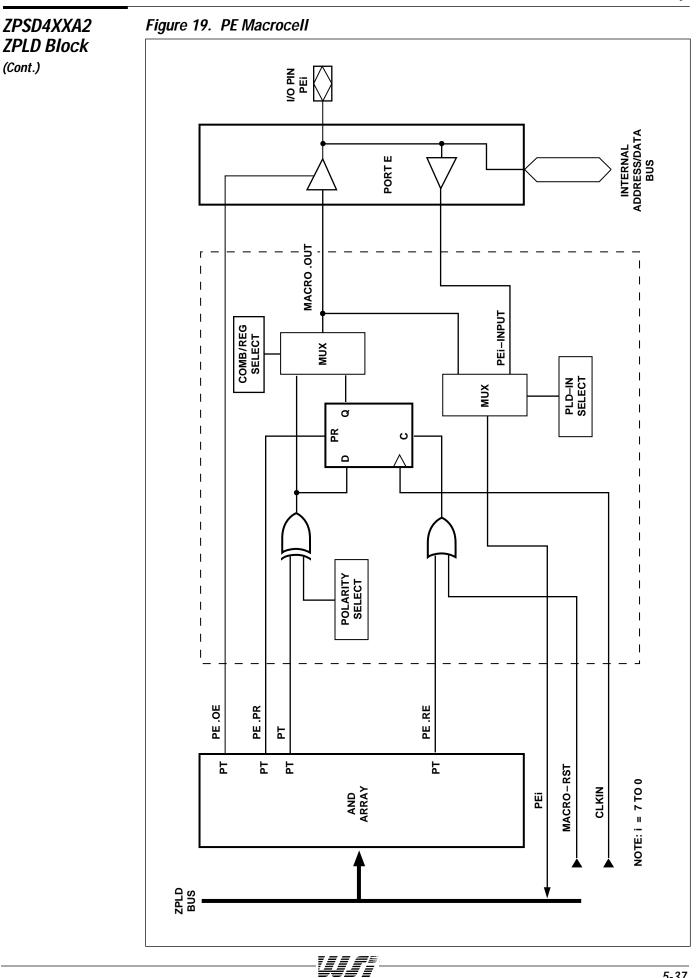

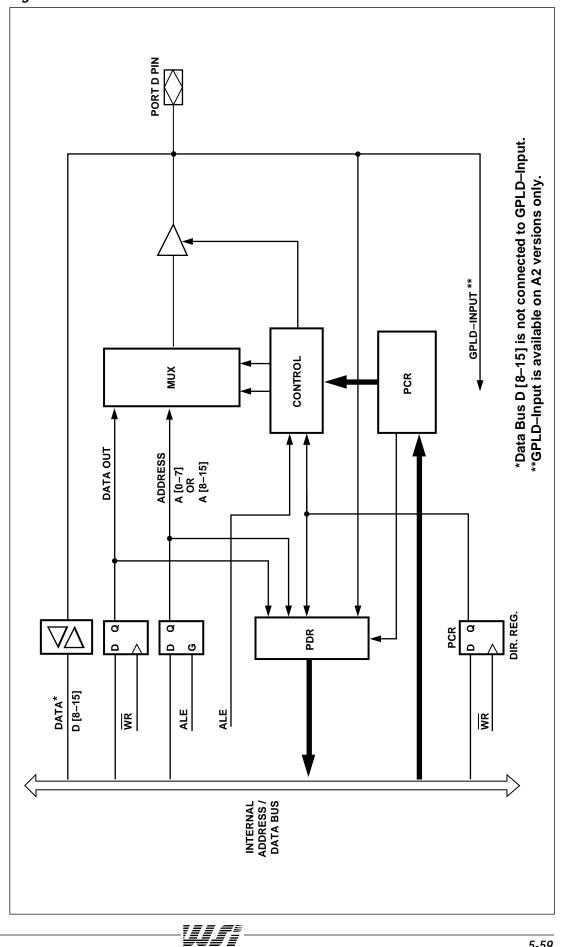

#### Port E Macrocell Structure

Figure 18 shows the PE Macrocell block, which consists of 8 identical macrocells. Each macrocell output can be connected to its own I/O pin on Port E. There are 3 user programmable global product terms output from the GPLD's AND ARRAY which are shared by all the macrocells in Port E:

D PE.OE

Enable or tri-state Port PE output pins

PE.PR

Preset D flip flop in the macrocells

D PE.RE

Reset/Clear D flip flop in the macrocells

Two other inputs, CLKIN and MACRO-RST, are used as clock and clear inputs to the D flip flop. The CLKIN comes directly from the CLKIN input pin. The MACRO-RST is the same as the Reset input pin except it is user configurable.

The circuit of a PE Macrocell is shown in Figure 19. There is only one product term from the GPLD's AND ARRAY as input to the macrocell. Users can select the polarity of the output and configure the macrocell to operate as:

Registered Output

Select output from D flip flop

- Combinatorial Output Select output from OR gate

- GPLD Input Use Port E pin as dedicated input

- GPLD Output Use Port E pin as dedicated output

- GPLD I/O

Use Port E pin as bidirectional pin

#### □ Macrocell Feedback

Register feedback for state machine implementations or expander feedback from the combinatorial output, to possibly expand the number of product terms available to another macrocell.

In case of "Buried Feedback", where the output of the macrocell is not connected to Port E pin, Port E can be configured to perform other user defined I/O functions. If pins PE0 and PE1 are used as bus control signal inputs (ALE, PSEN/BHE), the corresponding macrocells' feedbacks are disabled. The bus control signals are connected to the ZPLD Input Bus.

The two global product terms assigned for asynchronous clear (PE.RE) and preset (PE.PR) are for proper PE Macrocell initialization.

The macrocell flip-flop can also be cleared during reset by MACRO-RST as an option. The clock source is always the input clock CLKIN.

#### The ZPLD Power Management

The ZPLD implements a Zero Power Mode, which provides considerable power savings for low to medium frequency operations. To enable this feature, the ZPLD Turbo bit in the Power Management Mode Register 0 (PMMR0) has to be turned off.

If none of the inputs to the ZPLD are switching for a time period of 90ns, the ZPLD puts itself into Zero Power Mode and the current consumption is minimal. The ZPLD will resume normal operation as soon as one or more of the inputs change state.

Two other features of the ZPLD provide additional power savings:

#### 1. Clock Disable:

Users can disable the clock input to the ZPLD and/or macrocells, thereby reducing AC power consumption.

#### 2. Product Term Disable:

Unused product terms in the ZPLD are disabled by the PSDsoft Software automatically for further power savings.

The ZPLD power configuration is described in the Power Management Unit section.

ZPSD4XXA2

## Figure 18. PE Macrocell Block Diagram

ZPLD Block (Cont.)

# Bus Interface

The Bus Interface is very flexible and can be configured to interface to most microcontrollers with no glue logic. Table 5 lists some of the bus types to which the Bus Interface is able to interface.

| Multiplexed     | Data Bus<br>Width | Bus Control<br>Signals  | Microcontroller |  |  |  |  |  |  |

|-----------------|-------------------|-------------------------|-----------------|--|--|--|--|--|--|

| Mux             | 8                 | WR, RD, PSEN, A0        | 8031            |  |  |  |  |  |  |

| Mux/<br>Non-mux | 8/16              | R/W, E, BHE, A0         | 6811            |  |  |  |  |  |  |

| Mux             | 8/16              | WR, RD, BHE, A0         | 80196/80186     |  |  |  |  |  |  |

| Mux             | 16                | WRL, RD, WRH, A0        | 80196SP         |  |  |  |  |  |  |

| Non-mux         | 16                | R/W, LDS, UDS           | 68302           |  |  |  |  |  |  |

| Non-mux         | 8/16              | R/W, DS, SIZ0, A0       | 68340           |  |  |  |  |  |  |

| Non-mux         | 16                | R/W, DS, BHE, BLE 68330 |                 |  |  |  |  |  |  |

Table 5. Typical Microcontroller Bus Types

# **Bus Interface Configuration**

The Bus Interface Logic is user configurable. The type of bus interface is specified by the user in the PSDsoft software (PSD configuration). The bus control input pins have multi-function capabilities. By choosing the right configuration, the ZPSD4XX is able to interface to most microcontrollers, including the ones listed in Table 5. In Table 6, the names of the bus control input signal pins and their multiple functions are shown. For example, Pin PE0 can be configured by the PSD configuration software to perform any one of the five functions. Examples on the interface between the ZPSD4XX and some typical microcontrollers are shown in following sections.

#### Table 6. Alternate Pin Functions

| Pin Name | Pin<br>Function<br>1 | Pin<br>Function<br>2 | Pin<br>Function<br>3 | Pin<br>Function<br>4 | Pin<br>Function<br>5 |

|----------|----------------------|----------------------|----------------------|----------------------|----------------------|

| RD       | RD                   | E                    | DS                   | LDS                  |                      |

| WR       | WR                   | R/W                  | WRL                  |                      |                      |

| PE0      | BHE                  | PSEN                 | WRH                  | UDS                  | SIZ0                 |

| PE1      | ALE                  |                      |                      |                      |                      |

| AD0      | A0                   | BLE                  |                      |                      |                      |

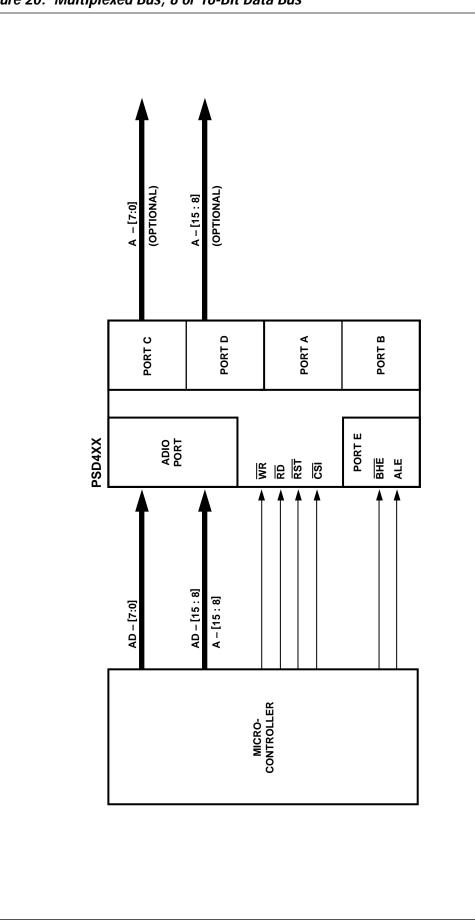

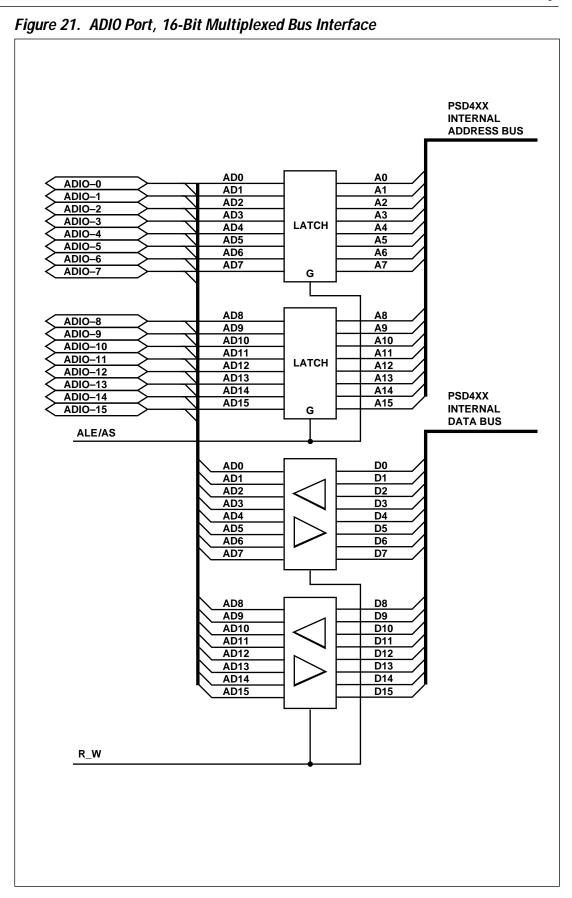

# ZPSD4XX Interface To a Multiplexed Bus

Figure 20 shows a typical connection to a microcontroller with a multiplexed bus. The ADIO port of the ZPSD4XX is connected directly to the microcontroller address/data bus (AD0-AD15 for 16 bit bus). The ALE input signal latches the address lines internally. In a read bus cycle, data is driven out through the ADIO Port transceivers after the specified access time. The internal ADIO Port connection for a 16 bit multiplexed bus is shown in Figure 21. The ADIO Port is in tri-state mode if none of the ZPSD4XX internal devices are selected.

5-38

Bus Interface

(Cont.)

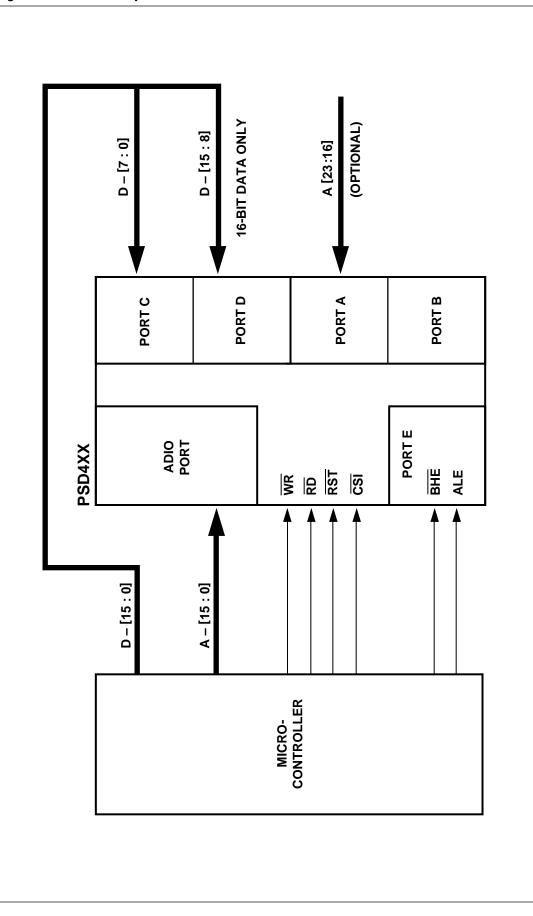

#### ZPSD4XX Interface To Non-Multiplexed Bus

Figure 22 shows a ZPSD4XX interfacing to a microcontroller with a non-multiplexed address/data bus. The address bus is connected to the ADIO Port, and the data bus is connected to Port C and/or Port D, depending on the bus width. There is no need for the ADIO Port to latch the address internally, but the user is offered the option to do so in the ZPSD4XX PSDsoft Software. The data Ports are in tri-state mode when the ZPSD4XX is not accessed by the microcontroller.

## Data Byte Enable

Microcontrollers have different data byte orientations with regard to the data bus. The following tables show how the ZPSD4XX handles the byte enable under different bus configurations. Even byte refers to locations with address A0 equal to "0", and odd byte as locations with A0 equal to "1".

#### Table 7. 8-Bit Data Bus

| BHE | AO | D7 Ð D0   |

|-----|----|-----------|

| Х   | 0  | Even Byte |

| Х   | 1  | Odd Byte  |

### Table 8. 16-Bit Data Bus With BHE

| BHE | AO | D15 Ð D8 | D7 Ð D0   |

|-----|----|----------|-----------|

| 0   | 0  | Odd byte | Even byte |

| 0   | 1  | Odd byte | -         |

| 1   | 0  | _        | Even byte |

#### Table 9. 16-Bit Data Bus With WRH and WRL

| WRH | WRL | D15 Ð D8 | D7 Ð D0   |

|-----|-----|----------|-----------|

| 0   | 0   | Odd byte | Even byte |

| 0   | 1   | Odd byte | -         |

| 1   | 0   | _        | Even byte |

#### Table 10. 16-Bit Data Bus With SIZO, AO

|      | 1  |           |          |

|------|----|-----------|----------|

| SIZO | AO | D15 Đ D8  | D7 Ð D0  |

| 0    | 0  | Even byte | Odd byte |

| 1    | 0  | Even byte | _        |

| 1    | 1  | _         | Odd byte |

# Table 11. 16-Bit Data Bus With UDS, LDS

| LDS | UDS | D15 Ð D8  | D7 Ð D0  |

|-----|-----|-----------|----------|

| 0   | 0   | Even byte | Odd byte |

| 1   | 0   | Even byte | _        |

| 0   | 1   | _         | Odd byte |

# Figure 20. Multiplexed Bus, 8 or 16-Bit Data Bus

Interface (Cont.)

Bus

# Bus Interface

(Cont.)

# Figure 22. Non-Multiplexed, 8 or 16-Bit Data

Bus Interface (Cont.)

**W**f

# Bus Interface (Cont.)

#### **Optional Features**

The ZPSD4XX provides two optional features to add flexibility to the Bus Interface:

#### 1. Address In

Port A can be configured as high order address (A16-A23) inputs to the ZPLD for EPROM or other decoding. Inputs are latched by ALE/AS if Multiplexed Bus is selected. Other Ports can be configured as address input ports for the ZPLD. These inputs should not be used for EPROM decoding and are not latched internally.

#### 2. Address Out

For multiplexed bus only. Latched address lines A0-A15 are available on Port A, B, C or D.

Details on the optional features are described in the I/O Port section.

#### **Bus Interface Examples**

The next four figures show the ZPSD4XX interfacing with some popular microcontrollers. The examples show only the basic bus connections; some of the pin names on the ZPSD4XX parts change to reflect the actual pin functions.

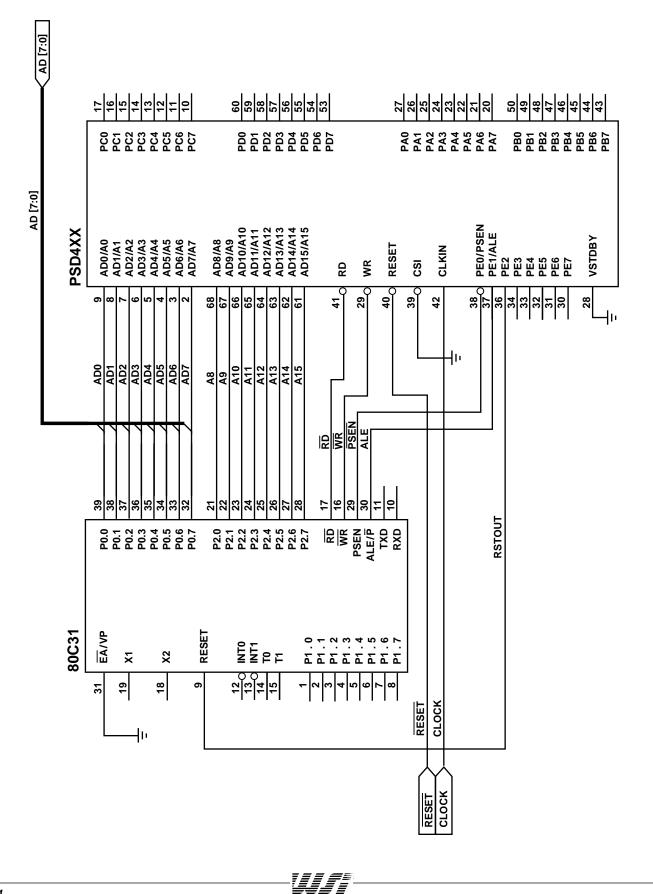

Figure 23 shows the interface to the 80C31. The 80C31 has a 16 bit address bus and an 8-bit data bus. The lower address byte is multiplexed with the data bus. The RD and WR signals are used for accessing the data memory (SRAM) and the PSEN signal is for reading program memory (EPROM). The ALE signal is active high and is used to latch the address internally. Port C provides latched address outputs A[7:0]. Ports A, B, D, and E (PE2-PE7) can be configured to perform other functions. The RSTOUT reset to the 80C31 is generated by the ZPLD from the RESET input. This configuration eliminates any reset race condition between the 80C31 and the ZPSD4XX.

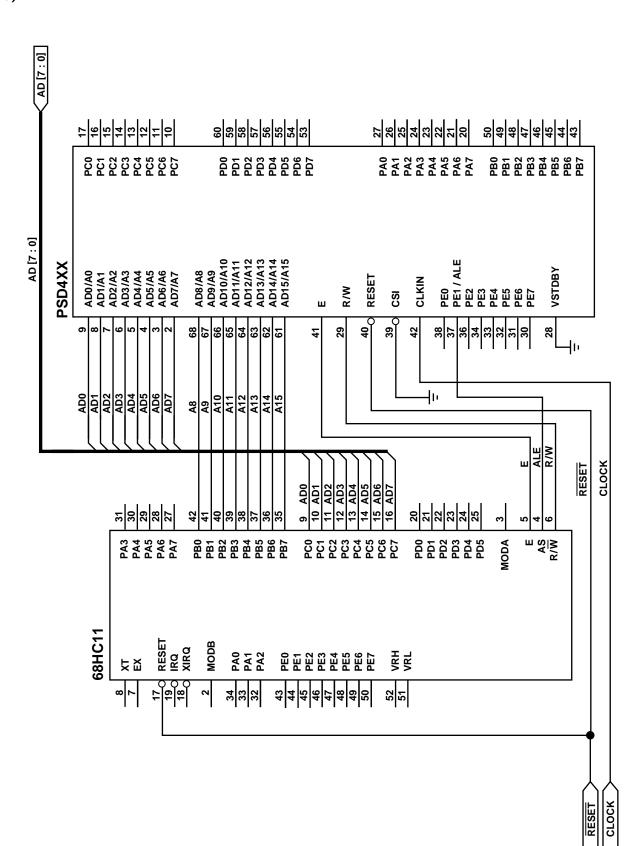

Figure 24 shows the 68HC11 interface, which is similar to the 80C31 except the ZPSD4XX generates internal  $\overline{RD}$  and  $\overline{WR}$  from the 68HC11's E and  $\overline{R/W}$  signals.

In Figure 25, the Intel 80C196 microcontroller is inter<u>faced</u> to the ZPSD4XX. The 80C196 has a multiplexed 16-bit address and data bus. The BHE signal is used for data byte selection. Ports C and D are used as output ports for latched address A[15:0]. Pins PE6 and PE7 can be programmed as ZPLD outputs to provide the READY and BUSWIDTH control signals to the 80C196.

Figure 26 shows Motorola's MC68331 interfacing to the ZPSD4XX. The MC68331 has a 16-bit data bus and a 24-bit address bus. D15 - D8 from the MC68331 are connected to Port D, and D7 - D0 are connected to Port C.

# Bus Interface

(Cont.)

**UUS**

Bus Interface (Cont.)

| D [46.0]   | [n · c]] |        | 17    | 16                       | 15<br>     | 14         | 2          | £                    | <del></del> 9 |                                         |                        | 8         | 6         | 22          | 56                       | 22          | 53       |                                                                                                    |   |              |            | 27  | 26  | 52<br>57 | 53    | 22      | 502                  |            | 20   | 64<br>84 | 47                     | <del>8</del><br>8<br>8<br>8<br>8<br>8 | 43                |

|------------|----------|--------|-------|--------------------------|------------|------------|------------|----------------------|---------------|-----------------------------------------|------------------------|-----------|-----------|-------------|--------------------------|-------------|----------|----------------------------------------------------------------------------------------------------|---|--------------|------------|-----|-----|----------|-------|---------|----------------------|------------|------|----------|------------------------|---------------------------------------|-------------------|

|            |          |        |       | 222                      | PC2        | PC3        | PC4        | 5 G                  | PC7           |                                         |                        | PD0       | PD1       | PD2         |                          | PD5         | PD6      | PD7                                                                                                |   |              |            | PAO | PA1 | PA2      | PA3   | PA5     | PA6                  | PA7        | PB0  | PB1      | PB2<br>PB3             | PB4<br>PB5                            | РВ7<br>РВ7        |

| D [15 : 0] |          | PSD4XX |       | AD0/A0<br>AD1/A1         | AD2/A2     | AD3/A3     | AD4/A4     | AD5/A5               | AD7/A7        |                                         | AD8/A8<br>AD9/A9       | AD10/A10  | AD11/A11  | AD12/A12    | AD13/A13<br>AD14/A14     | AD15/A15    |          | RD                                                                                                 |   | WR           | DECET      |     | CSI |          | CLKIN | PE0/BHE |                      | PE2<br>DE3 | PE4  | PE5      | PE6<br>PE7             |                                       | VSIUBY            |

|            |          |        | б     | 8                        | 7          | יז פ       | 4          | с                    | 2             | 68                                      | 67                     | 66<br>65  | 64        | 63          | 62                       | 61          |          | 41                                                                                                 |   | 0<br>50<br>0 | 40         |     | 39  | 42       | ŧ     | 38      | 3/<br>36             | 34         | 33   | 31       | 30                     | 28                                    | L <sub>I</sub> ,  |

|            |          |        | AD0   | AD1                      | AD2        |            | AD5        | AD6                  | AD7           | AD8                                     | AD9                    | AD10      | AD12      | AD13        | AD14                     | AD15        |          |                                                                                                    |   |              |            |     |     | CLKOUT   |       |         |                      | · · ·      |      | 1        |                        |                                       |                   |

|            |          |        | ~     | 6                        |            |            |            | 4                    | 2             | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | -                      |           |           |             | 9                        | 2           | RD<br>DR |                                                                                                    |   | Z ALE        |            |     | 59  | 58       | - w   | ات      | 48 47                | اما        | 20   | 49       | .  <sub>m</sub>        | RESET                                 | BUSWIDTH<br>READY |

|            |          |        | x2 12 | _                        |            |            | AD4 55     |                      |               | 52                                      |                        | AD10 50   |           |             |                          | AD15 45     | 61       | 면 없<br>[<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 0 | ALE 62       |            |     |     |          |       |         | P1 :5<br>6<br>4<br>4 |            |      |          | HSO .2 43<br>HSO .3 43 | ]                                     |                   |

|            |          |        |       | P3 - U/AD0<br>P3 - 1/AD1 | P3 . 2/AD2 | P3 . 3/AD3 | P3 . 4/AD4 | P3.5/AD5<br>P3.6/AD6 | P3.7/AD7      | ì                                       | P4 . U/AD8<br>P4 1/AD9 | P4.2/AD10 | P4.3/AD11 | P4 . 4/AD12 | P4 . 5/AD13<br>P4 6/AD14 | P4 . 7/AD15 |          |                                                                                                    |   |              | 2          |     |     |          |       |         |                      |            | Ĥ    | Ξ        | Ϋ́Υ                    |                                       |                   |

|            |          | 80C196 | X1    |                          |            |            |            | CDF                  |               | RESET                                   | ACHO/PO 0              |           |           |             | ACH4/P0.4                |             |          | P2_0/TXD                                                                                           |   |              | P2.3/T2CLK |     |     |          |       | HSI.1   |                      |            | VREF |          | ANGND<br>EA            |                                       |                   |

|            |          |        | 5     |                          |            | ~          | 43         | 14                   | 64            |                                         | 9                      | 1 01      | - ₹       | ÷           | 9                        | ∞           | 5        | 18                                                                                                 | 1 | 15           | 42         | 39  | 33  | 38       | 24    | 25      | 27                   |            | 13   | 12       | 2<br>7                 | - <b> </b> 1-                         |                   |

|            |          |        |       |                          |            |            |            |                      |               | •                                       |                        |           |           |             |                          |             |          |                                                                                                    |   |              |            |     |     |          |       |         |                      |            |      |          |                        |                                       |                   |

|            |          |        |       |                          |            |            |            |                      |               | RESET                                   |                        |           |           |             |                          |             |          |                                                                                                    |   |              |            |     |     |          |       |         |                      |            |      |          |                        |                                       |                   |

|            |          |        |       |                          |            |            |            |                      | l             |                                         |                        |           |           |             |                          |             |          |                                                                                                    |   |              |            |     |     |          |       |         |                      |            |      |          |                        |                                       |                   |

Figure 25. Interfacing ZPSD4XX With 80C196

# Bus Interface

ZPSD4XX Family

(Cont.)

| P 46 - A   |            | 10-011v |          |          |          |        |           |          |           |     |          |            |            |            |                |            |            |            |            |     |         |         |         |         |          |                       |        |        |      |          |         |        |        |        |           |         |         |                  |        |

|------------|------------|---------|----------|----------|----------|--------|-----------|----------|-----------|-----|----------|------------|------------|------------|----------------|------------|------------|------------|------------|-----|---------|---------|---------|---------|----------|-----------------------|--------|--------|------|----------|---------|--------|--------|--------|-----------|---------|---------|------------------|--------|

| D [15 : 0] | A [18 : 0] |         |          | 15       | 14       | 13     | 12        | 11       | PC6 10 D7 | 5   |          |            |            | 23<br>F8   | 20             | 51         | 56<br>     | 55         | PD6 54 D14 | _   |         |         |         |         | 27       | PA0 <u></u><br>Bo1 26 |        |        |      | PA5 21   |         | I      | BBA 50 |        | PB2 48    |         | PB5 45  | PB6 43<br>PB7 43 | i<br>- |

|            |            | PSD4XX  | AD0 / A0 | AD1 / A1 | AD2 / A2 | AD3/A3 | AD4 / A4  | CA / CUA | AD6 / A6  |     | AD8 / A8 | AD9 / A9   | AD10 / A10 | AD11 / A11 | AD12 / A12     | AD13 / A13 | AD14 / A14 | AD15 / A15 |            |     | DS      |         | R /W    |         | RESET    | 192                   | 50     | CLKIN  |      | PE0/SIZ0 | PE1/ALE | PE2    | 7E3    | PE5    | PE6       | PE7     | VSTDBY  |                  |        |

|            |            |         | 60       | 2        | . 9      | 5      | 4         | 3        | 2         | 1   | 89       | ٥ <i>١</i> | 00         | C0         | 45<br>52       | 36         | 29         | 61         |            |     | 40      | 20      | 3       | 40      | ¢<br>₽   | 39                    | )      | 42     | 00   | 37       | 36      | 34     | 33     | 32     | 30        |         | 28      | - ı-             | _      |

|            |            |         | AO       | 82       | A3       | A4     | A5        | A6       | A7        |     | A8       | AS         | AIU        | A11        | A12            | A13        | A14        | A15        |            |     |         |         |         |         |          |                       |        |        |      |          | -       |        |        |        |           |         |         |                  |        |

|            |            |         | AO       |          | R3       | A4     | A5        | A6       | A7        | A8  | 8        | Alu        |            | A12        |                | ₽<br>₽     | A15        | A16        | A17        | A18 |         |         |         |         |          | ALE                   | RW     | DS     | 0110 | 0120     | CLKOUT  |        |        |        |           |         |         |                  | RESET  |

|            |            |         | 06       | 21       | 52       | 23     | 24        | 25       | 26        | 27  | 30       | 51         | 25         | 35         | 30             | 02         | 37         | 38         | 41         | 42  | 121     |         | 124     | 121     | 3        | 82                    | 79     | 85     | 2    | 80       | 66      | 112    | 113    | 114    | 115       | 119     | 120     |                  |        |

|            |            |         | A0       | A1       | A2       |        | - 54<br>V | A6       | A7        | A8  | A9       | A10        | A11 -      | A12        | A13            | A14        | A15        | A16        | A17        | A18 | A19_CS6 | A20-CS7 | AZ1-CS8 | A22-C59 | A23_C310 | <u>As</u>             | R_N.   | N<br>S |      | SIZ0     |         | CSBOOT | BR-CS0 | BG-CS1 | BGACK-CS2 | FC1-CS4 | FC2-CS5 |                  |        |

|            |            | MC68331 |          | 8        | 5        | 22.2   | 03        | 4        |           | 20  | 80       | 60         | D10        | D11        | 012            | D13        | 014        | 015        |            |     |         |         | RESET   |         |          |                       | DSACK1 |        |      | RQ1      | RQ2     |        |        |        | RQ7       |         |         |                  |        |

|            |            | Σ       | 2        | 110      | Т        | 108    | 105       | 104      |           | 102 | ē        | 66         | Т          | 8          | <del>,</del> 5 | 5          | D14 92     | 9          |            |     |         | 89      | Т       |         |          |                       | 8      |        |      | Т        | Т       | г      |        | 12     |           |         |         |                  |        |

|            |            |         |          |          |          |        |           |          |           |     |          |            |            |            |                |            |            |            |            |     |         |         | RESET   |         |          |                       |        |        |      |          |         |        |        |        |           |         |         |                  |        |

# Bus Interface (Cont.)

#### ZPSD4XX Family

## I/O Ports

There are 5 programmable 8-bit I/O ports: Port A, Port B, Port C, Port D and Port E. These ports all have multiple operating modes, depending on the configuration. Some of the basic functions are providing input/output for the ZPLD, or can be used for standard I/O. Each port pin is individually configurable, thus enabling a single 8-bit port to perform multiple functions. The I/O ports occupy 256 bytes of memory space as defined by "CSIOP". Refer to the System Configuration section for I/O register address offset.

To set up the port configuration the user is required to:

- 1. Define I/O Port Chip Select (CSIOP) in the ABEL file.

- 2. Initialize certain port configuration registers in the user's program and/or

- 3. Specify the configuration in the ZPSD4XX PSDsoft Software.

- 4. Unused input pins should be tied to  $V_{CC}$  or GND.

The following is a description of the operating modes of the I/O ports. The functions of the port registers are described in later sections.

#### Standard MCU I/O

The Standard MCU I/O Mode provides additional I/O capability to the microcontroller. In this mode, the ports can perform standard I/O functions such as sensing or controlling various external I/O devices. Operation options of this mode are as follows:

- **Configuration**

- 1. Declare pins or signals which are used as I/O in the ABEL file.

- 2. Set the bit or bits in the Control Register to "1".

- 3. As Output Port

- Write output data to Data Out Register

- Set Direction Register to output mode

- 4. As Input Port

- Set Direction Register to input mode

- Read input from Data In Register

The port remains an output or input port as long as the Direction Register is not changed.

#### PLD I/0

The PLD I/O mode enables the port to be configured as an input to the ZPLD, or as an output from the GPLD macrocell. The output can be tri-stated with a control signal defined by a product term from the ZPLD. This mode is configured by the user in the ZPSD4XX PSDsoft Software, and is enabled upon power up. For a detailed description, see the section on the ZPLD.

#### Configuration

- 1. Declare pins or signals in the ABEL file (PSDsoft).

- 2. Write logic equations in the ABEL file.

- 3. PSD Compiler maps the PLD functions to the PSD.

# I/O Ports

(Cont.)

#### Address Out

For microcontrollers with a multiplexed address/data bus, the I/O ports in Address-Out mode are able to provide latched address outputs (A0 - A15) to external devices. This mode of operation requires the user to:

#### Configuration

- 1. Declare the pins used as address line outputs in the ABEL file (PSDsoft).

- 2. Write "0" to the corresponding bit in the Control Register associated with each I/O port.

- 3. Set the Direction Register to Output Mode.

#### Address In

There are two Address In modes:

- 1. For Port A as other address line (A2-A7 and A16-A23) inputs to the DPLD. Additional address inputs included in the EPROM decoding must come from Port A. The address inputs are latched internally by ALE/AS if Multiplexed Bus is specified in PSDsoft.

- 2. For Ports C and D as address inputs to the ZPLD for general decoding, should not be used in EPROM decoding.

#### **Configuration**

- 1. Declare pins or signals used as Address In in the ABEL file (PSDsoft).

- 2. Write latch equations in the .ABL file, e.g., A16.LE = ALE.

- 3. Include latched address in logic equations.

#### Data Port

In this mode, the port is acting as a data bus port for a microcontroller which has a non-multiplexed address/data bus. The Data Port is connected to the data bus of the microcontroller and the ADIO port is connected to the address bus.

#### Configuration

Select the non-multiplexed bus option in PSD configuration (PSDsoft).

#### Alternate Function In

This mode is per-pin configurable and enables the user to define pin PE7 of Port E as Automatic Power Down (APD) CLK input.

#### Configuration

- 1. Select input functions in PSD configuration.

- 2. PSD Compiler assigns pins for the selected options.

I/O Ports (Cont.)

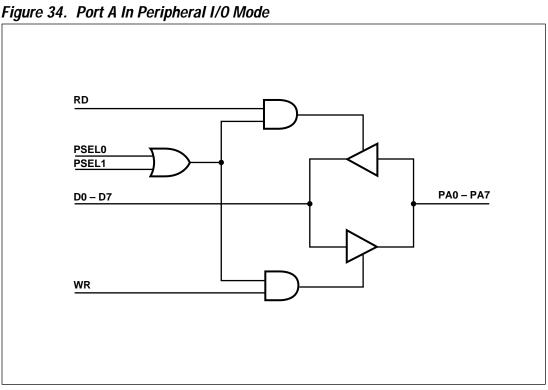

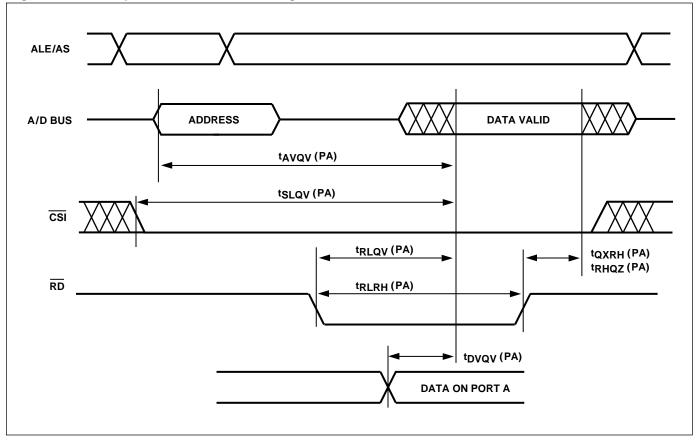

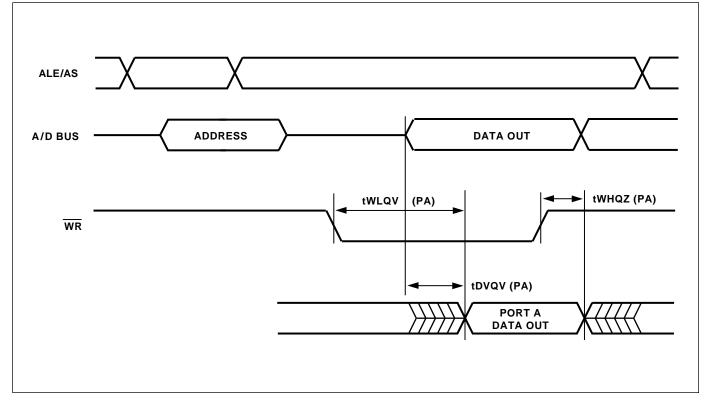

## Peripheral I/0

This mode enables the microcontroller to read or write to a peripheral though Port A. When there is no read/write operation, Port A is tri-stated. One of the applications of Peripheral I/O is in a DMA based design.

#### **Configuration**

1. Declare the pins used as pheripheral I/O in the ABEL file.

2. Write logic equations for PSEL0 and PSEL1.

3. Write a "1" to the PIO bit in the VM Register to activate the Peripheral I/O operation. See the section on Peripheral I/O for a detailed description.

#### **Open Drain Outputs**

This mode enables the user to configure Ports C and D pins as open drain outputs. CMOS output is the default configuration. Writing "1" to the corresponding bit in the Open Drain Register changes the pin to open drain output.

## Table 12. Operating Modes of the I/O Ports

Table 12 summarizes the operating modes of the I/O ports. Not all the functions are available to every port.

| Port Mode             | Port A | Port B | Port C      | Port D      | Port E |

|-----------------------|--------|--------|-------------|-------------|--------|

| Standard MCU I/O      | Yes    | Yes    | Yes         | Yes         | Yes    |

| PLD I/O               | Yes    | Yes    | Input Only* | Input Only* | Yes*   |

| Address Out           | Yes    | Yes    | Yes         | Yes         | Yes    |

| Address In            | Yes    | Yes**  | Yes**       | Yes**       |        |

| Data Port             |        |        | Yes         | Yes         |        |

| Alternate Function In |        |        |             |             | Yes    |

| Peripheral I/O        | Yes    |        |             |             |        |

| Open Drain            |        |        | Yes         | Yes         |        |

\* ZPSD4XXA2 Only.

\*\* For external decoding. Cannot be latched by ALE

#### Port Registers

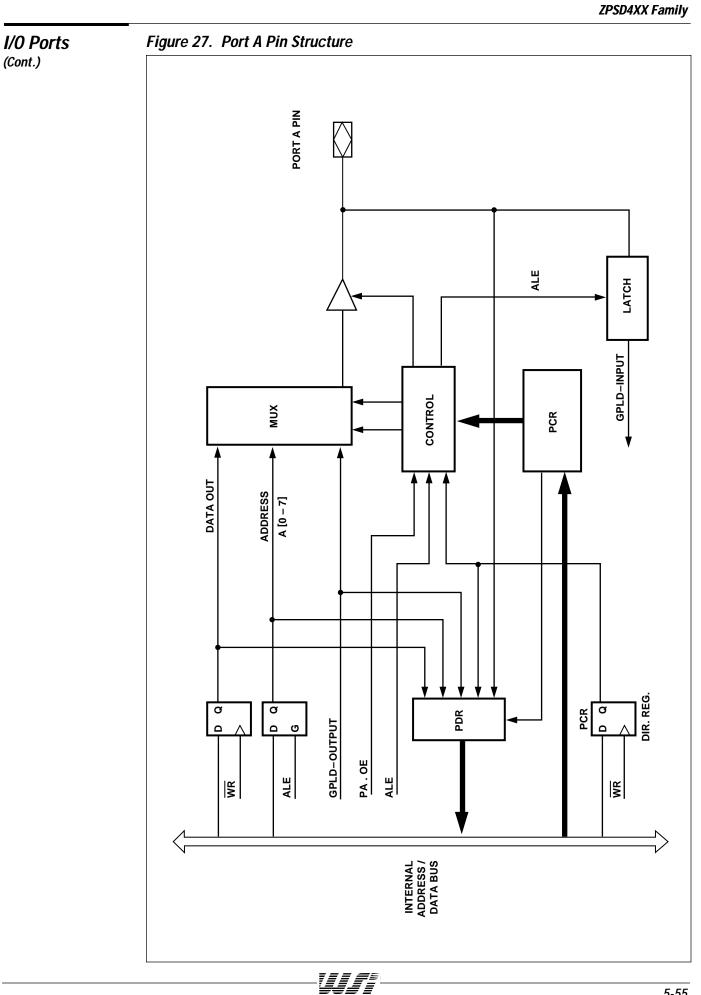

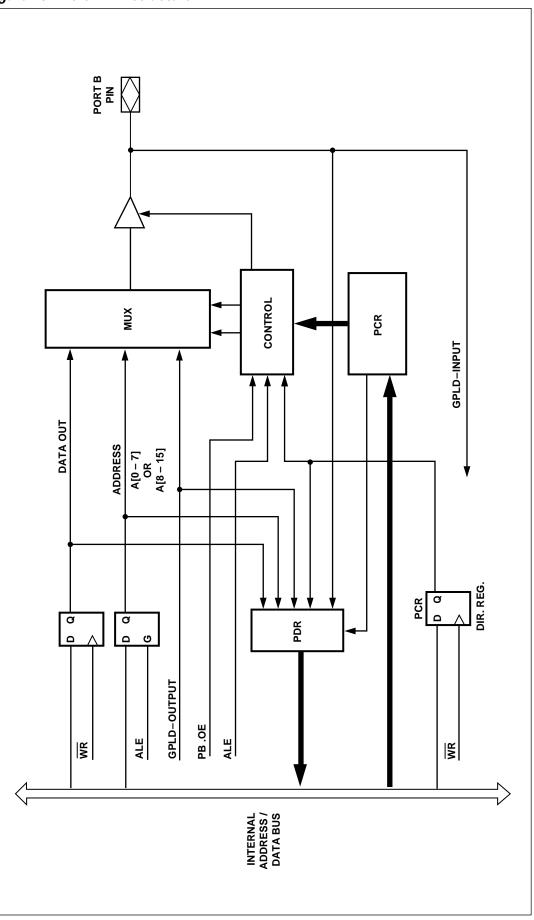

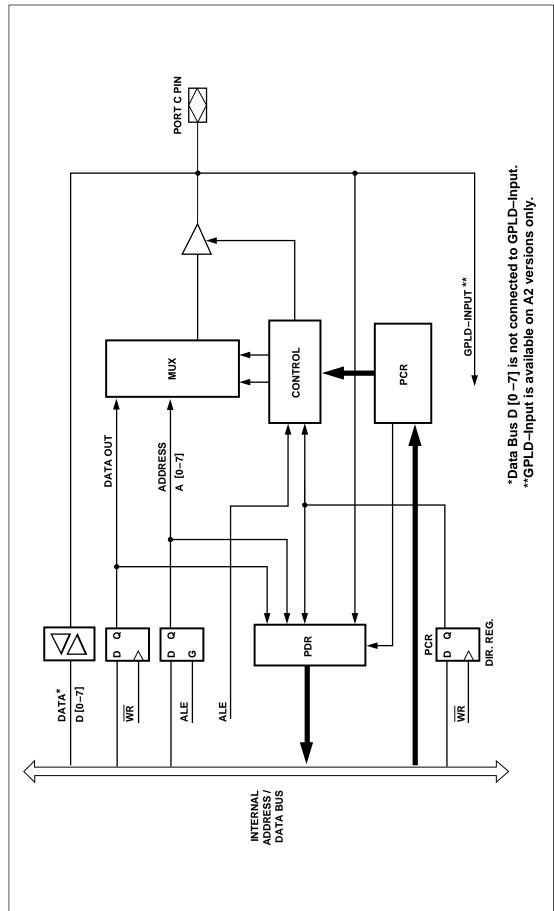

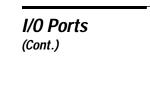

There are two sets of registers per I/O port: the Port Configuration Registers (PCR) which consist of four 8-bit registers; and the Port Data Registers (PDR) which include three 8-bit registers. The PCR is used for setting up the port configuration, while the PDR enables the microcontroller to write or read port data or status bits. Tables 13 and 14 show the names and the registers and the ports to which they belong.

All the registers in the PCR and PDR are 8-bits wide and each bit is associated with a pin in the I/O port. In Table 15, the LSB of the Data In Register of Port A is connected to pin PA0, and the MSB is connected to PA7. This pin configuration also applies to other registers and ports. For example, in the Direction Register of Port A, writing a hex value of 07 to the register configures pins PA0 – PA2 as output pins, while PA3 – PA7 remain as input pins.