1

**ISSUE 2**

DATA SHEET PMC- 2012568

OCTAL SHORT-HAUL E1/T1/J1 LINE INTERFACE DEVICE

**PM4319**

OCTLIU-SH

# OCTAL SHORT-HAUL E1/T1/J1 LINE INTERFACE DEVICE

DATA SHEET

PROPRIETARY AND CONFIDENTIAL

PRELIMINARY

ISSUE 2: APRIL 2002

DATA SHEET PMC- 2012568

**ISSUE 2**

ISSUE 2

OCTAL SHORT-HAUL E1/T1/J1 LINE INTERFACE DEVICE

# **CONTENTS**

| 1 |   | FEATU  | RES                                                           | 11   |

|---|---|--------|---------------------------------------------------------------|------|

|   |   | 1.1    | EACH RECEIVER SECTION:                                        | 11   |

|   |   | 1.2    | EACH TRANSMITTER SECTION:                                     | . 12 |

| 2 |   | APPLIC |                                                               |      |

| 3 |   | REFER  | RENCES                                                        | . 15 |

| 4 |   | APPLIC | CATIONS                                                       | . 17 |

| 5 |   | BLOCK  | ( DIAGRAM                                                     | 18   |

| 6 |   | DE005  | NOTION                                                        | 40   |

| 7 |   | PIN DI | AGRAM                                                         | . 20 |

| 8 |   | PIN DE | AGRAM                                                         | 21   |

| 9 |   | FUNCT  | ΓΙΟΝΑL DESCRIPTION                                            | 38   |

|   |   | 9.1    | OCTANTS                                                       | 38   |

|   |   | 9.2    | RECEIVE INTERFACE                                             | 38   |

|   |   | 9.3    | CLOCK AND DATA RECOVERY (CDRC)                                | 38   |

|   |   | 9.4    | RECEIVE JITTER ATTENUATOR (RJAT)                              | 40   |

|   |   | 9.5    | T1 INBAND LOOPBACK CODE DETECTOR (IBCD)                       | . 40 |

|   |   | 9.6    | T1 PULSE DENSITY VIOLATION DETECTOR (PDVD)                    | . 41 |

|   |   | 9.7    | PERFORMANCE MONITOR COUNTERS (PMON)                           | . 41 |

|   |   | 9.80   | PSEUDO RANDOM BINARY SEQUENCE GENERATION AND DETECTION (PRBS) |      |

|   | 0 | 9.9    | T1 INBAND LOOPBACK CODE GENERATOR (XIBC)                      | . 42 |

|   |   | 9.10   | PULSE DENSITY ENFORCER (XPDE)                                 | . 42 |

|   |   | 9.11   | TRANSMIT JITTER ATTENUATOR (TJAT)                             | . 42 |

|   |   | 9.12   | LINE TRANSMITTER                                              | . 47 |

|   |   | 9.13   | TIMING OPTIONS (TOPS)                                         | . 47 |

|   |   |        |                                                               |      |

ISSUE 2

|    | 9.14   | EXTERNAL ANALOGUE INTERFACE CIRCUITS                  | 48    |

|----|--------|-------------------------------------------------------|-------|

|    | 9.15   | SCALEABLE BANDWIDTH INTERCONNECT (SBI) INTERFACE      | 49    |

|    | 9.16   | SBI EXTRACTER AND PISO                                | 49    |

|    | 9.17   | SBI INSERTER AND SIPO                                 | 50    |

|    | 9.18   | JTAG TEST ACCESS PORT                                 | 50    |

|    | 9.19   | MICROPROCESSOR INTERFACEIAL MODE REGISTER DESCRIPTION | 50    |

| 10 | NORM   | AL MODE REGISTER DESCRIPTION                          | 51    |

|    | 10.1   | NORMAL MODE REGISTER MEMORY MAP                       | 52    |

| 11 | TEST F | FEATURES DESCRIPTION                                  | . 166 |

|    | 11.1   | JTAG TEST PORT                                        | . 166 |

| 12 | OPERA  | ATION                                                 | . 169 |

|    | 12.1   | CONFIGURING THE OCTLIU-SH FROM RESET                  | . 169 |

|    | 12.2   | SERVICING INTERRUPTS                                  | . 169 |

|    | 12.3   | USING THE PERFORMANCE MONITORING FEATURES             | 170   |

|    | 12.4   | USING THE TRANSMIT LINE PULSE GENERATOR               | . 170 |

|    | 12.5   | USING THE LINE RECEIVER                               | . 186 |

|    | 12.6   | USING THE PRBS GENERATOR AND DETECTOR                 | 193   |

|    | 12.7   | LOOPBACK MODES                                        | . 193 |

|    |        | 12.7.1 LINE LOOPBACK                                  | . 193 |

|    | 8      | 12.7.2 DIAGNOSTIC DIGITAL LOOPBACK                    | 194   |

|    | 12.8   | INITIALIZATION OF THE RJAT AND TJAT                   | . 195 |

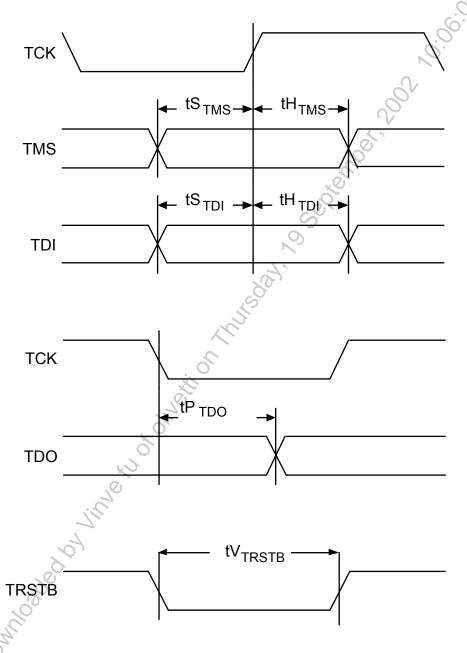

|    | 12.9   | JTAG SUPPORT                                          | . 195 |

|    |        | 12.9.1 TAP CONTROLLER                                 | . 197 |

| 13 | FUNC   | TIONAL TIMING                                         | . 204 |

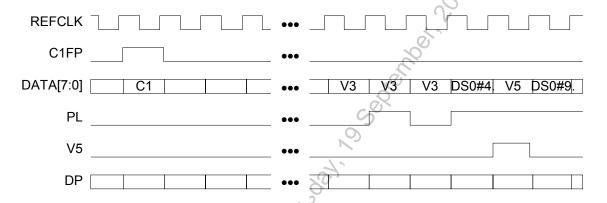

|    | 13.1   | SBI BUS INTERFACE TIMING                              | 204   |

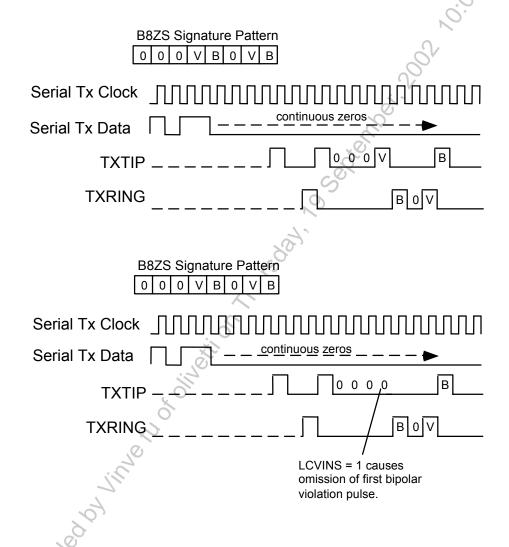

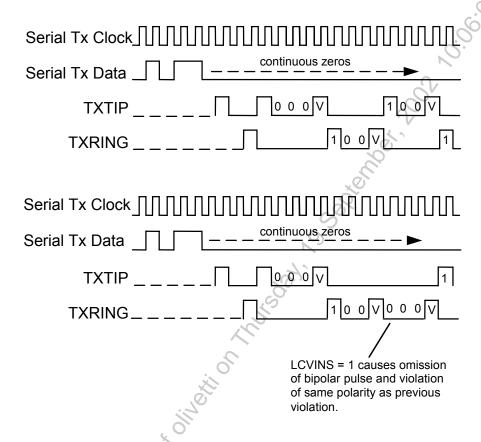

|    | 13.2   | LINE CODE VIOLATION INSERTION                         | 205   |

ISSUE 2

|    | 13.3   | ALARM INTERFACE                             |

|----|--------|---------------------------------------------|

| 14 | ABSO   | LUTE MAXIMUM RATINGS                        |

| 15 | D.C. C | CHARACTERISTICS                             |

| 16 | MICRO  | OPROCESSOR INTERFACE TIMING CHARACTERISTICS |

| 17 | OCTL   | IU-SH TIMING CHARACTERISTICS                |

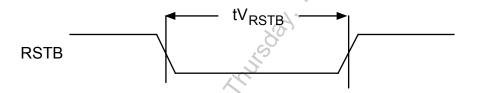

|    | 17.1   | RSTB TIMING (FIGURE 28)                     |

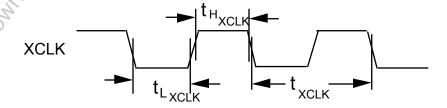

|    | 17.2   | XCLK INPUT TIMING (FIGURE 29)               |

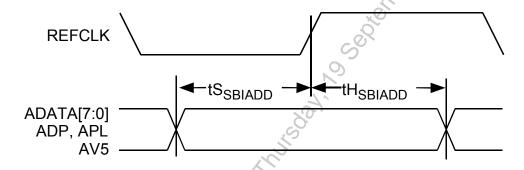

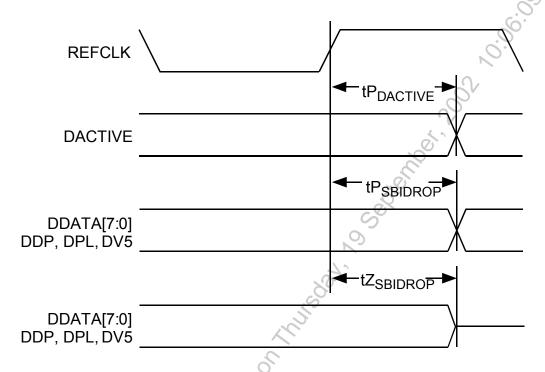

|    | 17.3   | SBI INTERFACE (FIGURE 30 TO FIGURE 32)      |

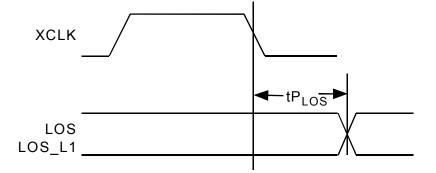

|    | 17.4   | ALARM INTERFACE (FIGURE 33)220              |

|    | 17.5   | JTAG PORT INTERFACE (FIGURE 34)             |

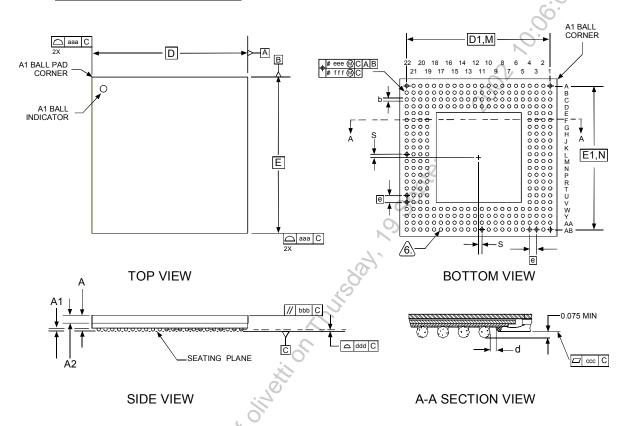

| 18 | ORDE   | RING AND THERMAL INFORMATION                |

| 19 | MECH   | IANICAL INFORMATION                         |

ISSUE 2

OCTAL SHORT-HAUL E1/T1/J1 LINE INTERFACE DEVICE

# **LIST OF FIGURES**

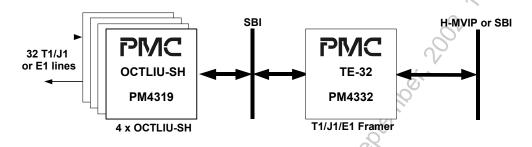

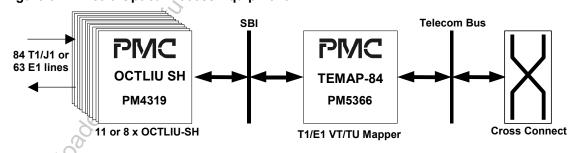

| FIGURE 1  | - HIGH DENSITY T1/E1 FRAMER/TRANSCEIVER APPLICATION             | 17   |

|-----------|-----------------------------------------------------------------|------|

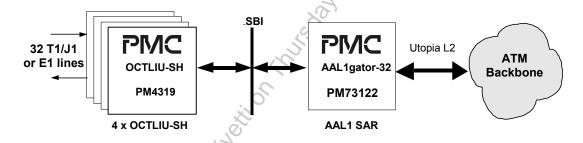

| FIGURE 2  | - HIGH DENSITY LEASED LINE CIRCUIT EMULATION APPLICATION        | 17   |

| FIGURE 3  | - METRO OPTICAL ACCESS EQUIPMENT                                | 17   |

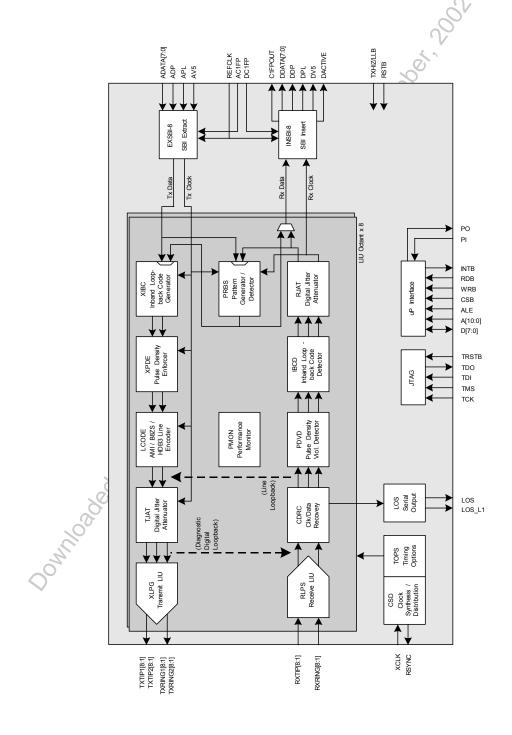

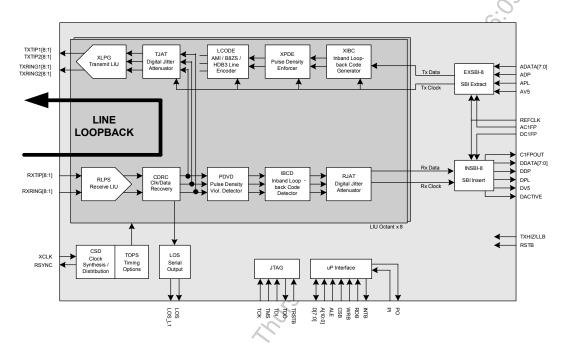

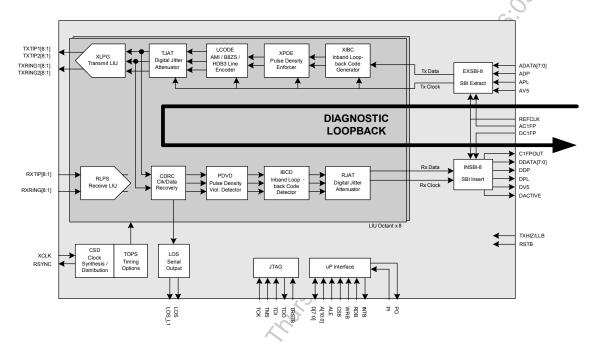

| FIGURE 4  | - OCTLIU-SH BLOCK DIAGRAM                                       | 18   |

| FIGURE 5  | – PIN DIAGRAM (BOTTOM VIEW)                                     | 20   |

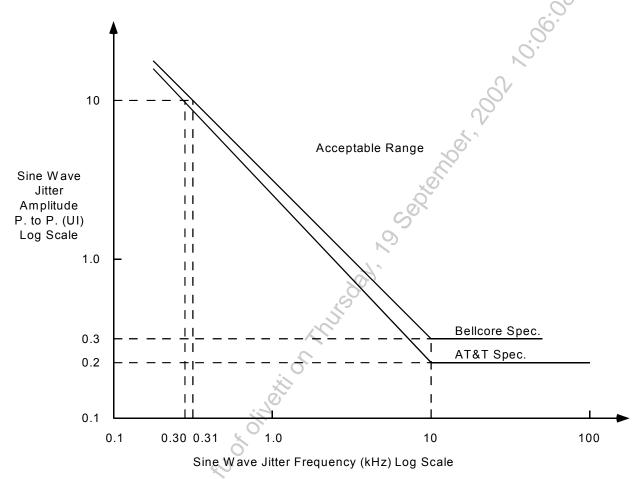

| FIGURE 6  | - PIN DIAGRAM (BOTTOM VIEW)  - T1 JITTER TOLERANCE              | 39   |

| FIGURE 7  | - COMPLIANCE WITH ITU-T SPECIFICATION G.823 FOR E1 INPUT JITTER | . 40 |

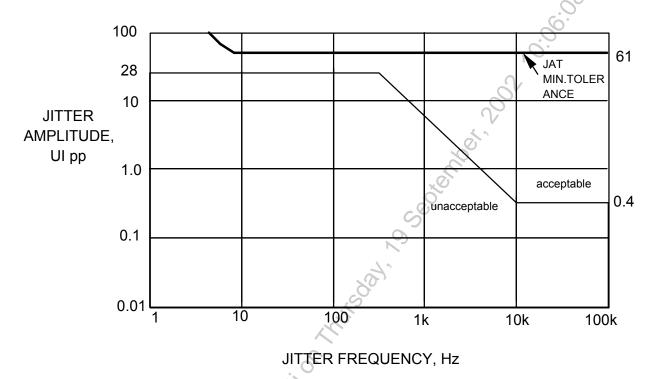

| FIGURE 8  | - TJAT JITTER TOLERANCE                                         | 44   |

| FIGURE 9  | - TJAT MINIMUM JITTER TOLERANCE VS. XCLK ACCURACY               |      |

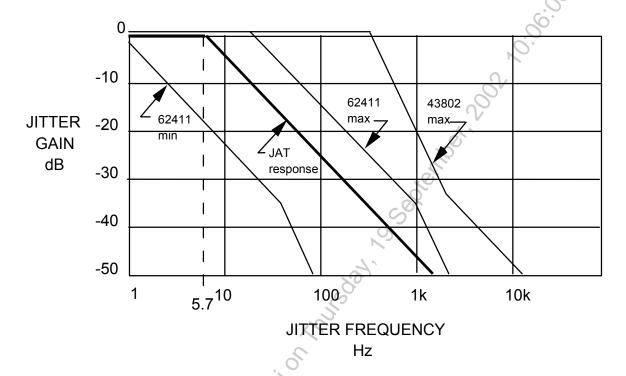

| FIGURE 10 | - TJAT JITTER TRANSFER                                          | 46   |

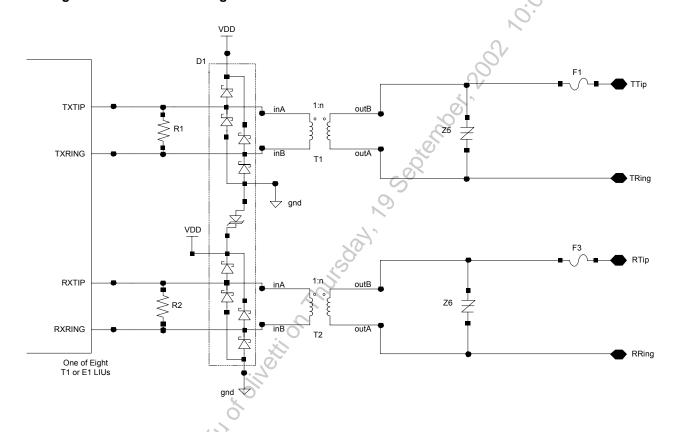

| FIGURE 11 | - EXTERNAL ANALOGUE INTERFACE CIRCUITS                          | 48   |

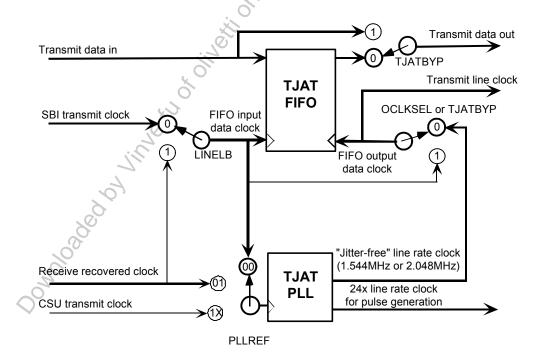

| FIGURE 12 | - TRANSMIT TIMING OPTIONS                                       |      |

| FIGURE 13 | - LINE LOOPBACK                                                 | 194  |

| FIGURE 14 | - DIAGNOSTIC DIGITAL LOOPBACK                                   | 195  |

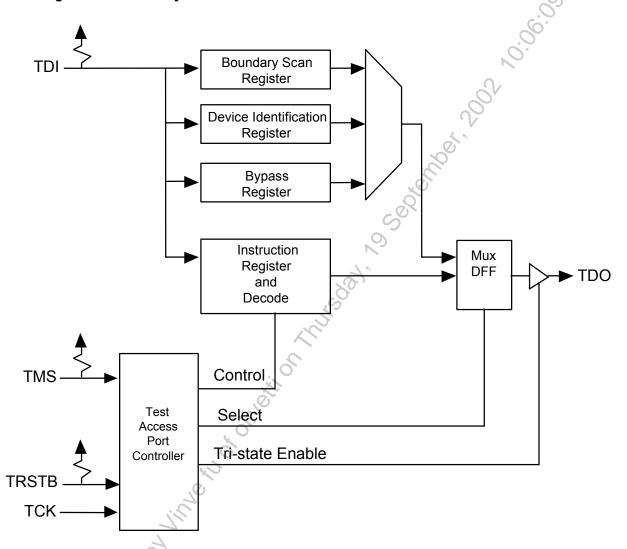

| FIGURE 15 | - BOUNDARY SCAN ARCHITECTURE                                    | 196  |

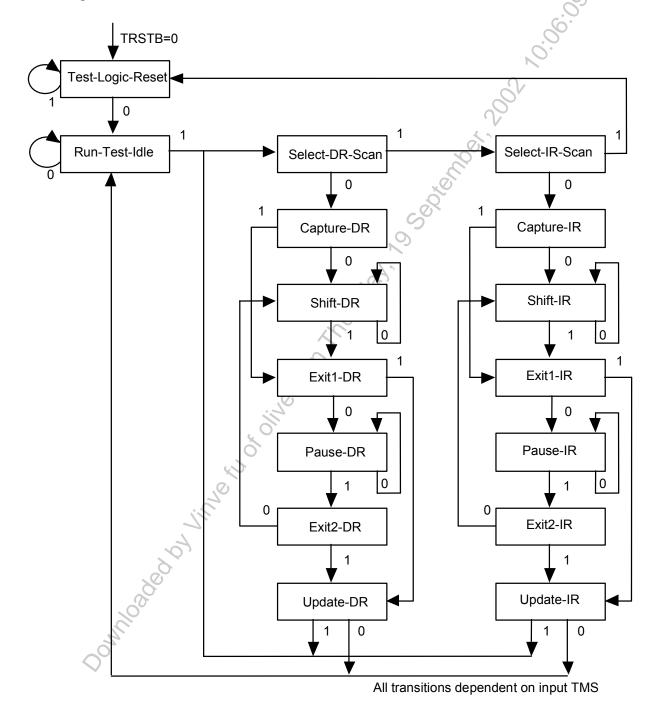

| FIGURE 16 | - TAP CONTROLLER FINITE STATE MACHINE                           | 198  |

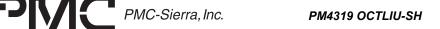

| FIGURE 17 | - INPUT OBSERVATION CELL (IN_CELL)                              | 201  |

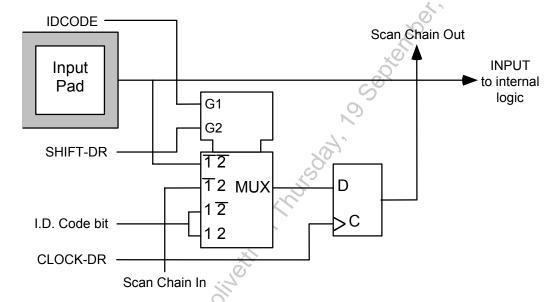

| FIGURE 18 | - OUTPUT CELL (OUT_CELL) OR ENABLE CELL (ENABLE)                | 202  |

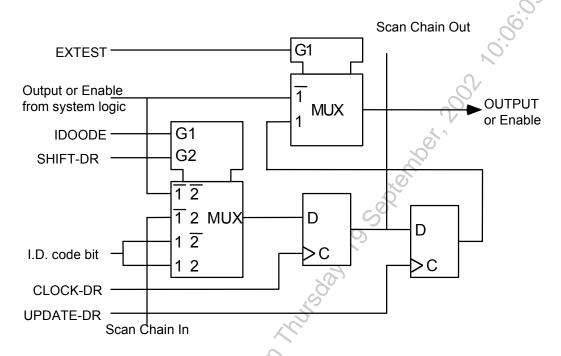

| FIGURE 19 | – BIDIRECTIONAL CELL (IO_CELL)                                  | 202  |

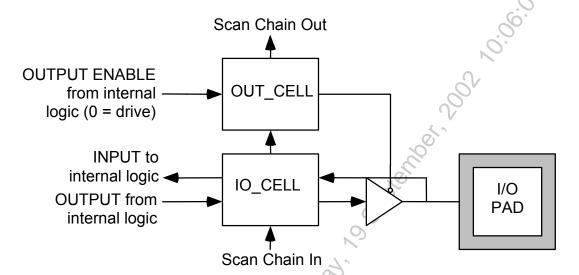

| FIGURE 20 | - LAYOUT OF OUTPUT ENABLE AND BIDIRECTIONAL CELLS               | 203  |

| FIGURE 21 | – SBI BUS FUNCTIONAL TIMING.                                    | 204  |

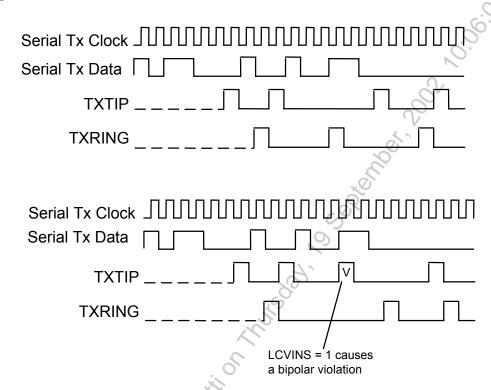

| FIGURE 22 | - B8ZS LINE CODE VIOLATION INSERTION                            | 205  |

| FIGURE 23 | - HDB3 LINE CODE VIOLATION INSERTION                            | 206  |

| FIGURE 24 | - AMI LINE CODE VIOLATION INSERTION                             | 207  |

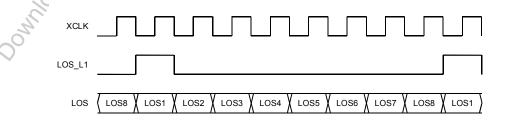

| FIGURE 25 | - LOS ALARM SERIAL OUTPUT               | . 207 |

|-----------|-----------------------------------------|-------|

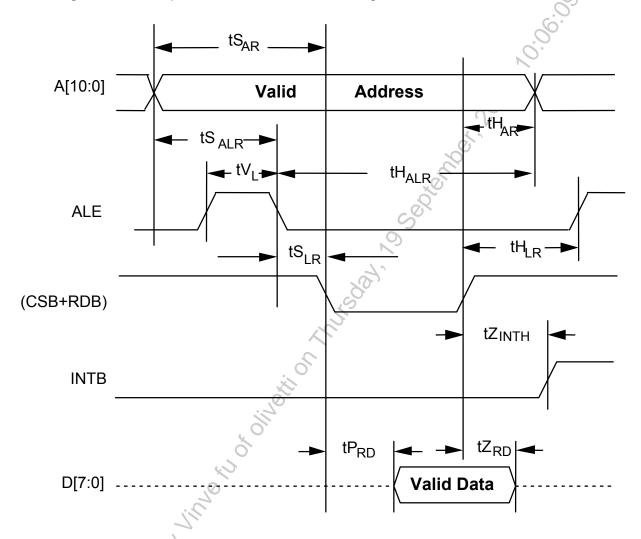

| FIGURE 26 | - MICROPROCESSOR INTERFACE READ TIMING  | . 214 |

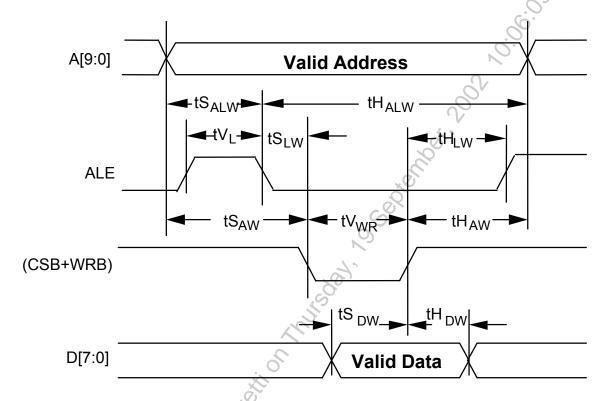

| FIGURE 27 | - MICROPROCESSOR INTERFACE WRITE TIMING | . 216 |

| FIGURE 28 | - RSTB TIMING                           | . 217 |

|           | - XCLK INPUT TIMING                     |       |

|           | - SBI FRAME PULSE TIMING                |       |

| FIGURE 31 | – SBI ADD BUS TIMING                    | . 219 |

| FIGURE 32 | – SBI DROP BUS TIMING                   | . 220 |

| FIGURE 33 | – ALARM INTERFACE TIMING                | . 220 |

| FIGURE 34 | – JTAG PORT INTERFACE TIMING.           | . 222 |

ISSUE 2

OCTAL SHORT-HAUL E1/T1/J1 LINE INTERFACE DEVICE

# **LIST OF TABLES**

| TABLE 1  | - EXTERNAL COMPONENT DESCRIPTIONS                                                    | 48    |

|----------|--------------------------------------------------------------------------------------|-------|

| TABLE 2  | - NORMAL MODE REGISTER MEMORY MAP                                                    | 52    |

| TABLE 3  | - CLOCK SYNTHESIS MODE                                                               | 67    |

| TABLE 4  | - TJAT FIFO OUTPUT CLOCK SOURCE                                                      | 75    |

| TABLE 5  | - TJAT FIFO OUTPUT CLOCK SOURCE  - TJAT PLL SOURCE  - EXSBI CLOCK GENERATION OPTIONS | 76    |

| TABLE 6  | - EXSBI CLOCK GENERATION OPTIONS                                                     | . 106 |

| TABLE 7  | - TRANSMIT IN-BAND CODE LENGTH                                                       | 112   |

| TABLE 8  | - RECOMMENDED N1/N2 VALUES                                                           | 116   |

| TABLE 9  | - RECOMMENDED N1/N2 VALUES                                                           | . 121 |

| TABLE 10 | - LOOPBACK CODE CONFIGURATIONS                                                       | . 124 |

| TABLE 11 | - LOSS OF SIGNAL THRESHOLDS                                                          | . 130 |

| TABLE 12 | - TRANSMIT OUTPUT AMPLITUDE                                                          | . 146 |

| TABLE 13 | - ALOS DETECTION/CLEARANCE THRESHOLDS                                                | . 153 |

| TABLE 14 | - BOUNDARY SCAN REGISTER                                                             | . 167 |

| TABLE 15 | - DEFAULT SETTINGS                                                                   | . 169 |

| TABLE 16 | – T1.102 TRANSMIT WAVEFORM VALUES FOR T1 SHORT HAUL (0 – 110 F                       | =T.)  |

| TABLE 17 | - T1.102 TRANSMIT WAVEFORM VALUES FOR T1 SHORT HAUL (110 - 220 FT.)                  | . 173 |

| TABLE 18 | – T1.102 TRANSMIT WAVEFORM VALUES FOR T1 SHORT HAUL (220 – 330 FT.)                  | . 174 |

| TABLE 19 | - T1.102 TRANSMIT WAVEFORM VALUES FOR T1 SHORT HAUL (330 - 440 FT.)                  | . 175 |

| TABLE 20 | - T1.102 TRANSMIT WAVEFORM VALUES FOR T1 SHORT HAUL (440 - 550 FT.)                  | . 176 |

| TABLE 21 | – T1.102 TRANSMIT WAVEFORM VALUES FOR T1 SHORT HAUL (550 – 660 FT.)                  | . 177 |

ISSUE 2

| TABLE 22 | - TR62411 TRANSMIT WAVEFORM VALUES FOR T1 SHORT HAUL (0 - 110 FT.)178 |

|----------|-----------------------------------------------------------------------|

| TABLE 23 | - TR62411 TRANSMIT WAVEFORM VALUES FOR T1 SHORT HAUL (110 - 220 FT.)  |

| TABLE 24 | - TR62411 TRANSMIT WAVEFORM VALUES FOR T1 SHORT HAUL (220 - 330 FT.)  |

| TABLE 25 | - TR62411 TRANSMIT WAVEFORM VALUES FOR T1 SHORT HAUL (330 - 440 FT.)  |

| TABLE 26 | - TR62411 TRANSMIT WAVEFORM VALUES FOR T1 SHORT HAUL (440 - 550 FT.)  |

| TABLE 27 | - TR62411 TRANSMIT WAVEFORM VALUES FOR T1 SHORT HAUL (550 – 660 FT.)  |

| TABLE 28 | - TRANSMIT WAVEFORM VALUES FOR E1 120 OHM 184                         |

| TABLE 29 | - TRANSMIT WAVEFORM VALUES FOR E1 75 OHM 185                          |

| TABLE 30 | - RLPS REGISTER PROGRAMMING                                           |

| TABLE 31 | - RLPS EQUALIZER RAM TABLE (T1 MODE)                                  |

| TABLE 32 | - RLPS EQUALIZER RAM TABLE (E1 MODE)                                  |

| TABLE 33 | - ABSOLUTE MAXIMUM RATINGS                                            |

| TABLE 34 | - D.C. CHARACTERISTICS                                                |

| TABLE 35 | - MICROPROCESSOR INTERFACE READ ACCESS                                |

| TABLE 36 | - MICROPROCESSOR INTERFACE WRITE ACCESS                               |

| TABLE 37 | - RTSB TIMING                                                         |

| TABLE 38 | - XCLK INPUT TIMING                                                   |

| TABLE 39 | – CLOCKS AND SBI FRAME PULSE                                          |

| TABLE 40 | – SBI ADD BUS                                                         |

| TABLE 41 | – SBI DROP BUS                                                        |

| TABLE 42 | - ALARM INTERFACE 220                                                 |

| TABLE 43 | – JTAG PORT INTERFACE                                                 |

| TABLE 44 | - ORDERING INFORMATION224                                             |

DATA SHEET PMC- 2012568

| ISSUE 2 | OCTAL SHORT-HAUL E1/T1/J1 |

|---------|---------------------------|

|         | LINE INTERFACE DEVICE     |

|         | E.                        |

|         |                           |

| TABLE 45 | – OCTLIU-SH THETA JC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <u>-</u> | . 224 |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|

| TABLE 46 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          | . 224 |

| TABLE 47 | - OCTLIU-SH JUNCTION TEMPERATURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 70.      | . 224 |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2        |       |

|          | No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | )        |       |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |       |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |       |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |       |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |       |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |       |

|          | 807                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |       |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |       |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |       |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |       |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |       |

|          | * 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |       |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |       |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |       |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |       |

|          | to the second se |          |       |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |       |

| 0        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |       |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |       |

| 00       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |       |

|          | OCTLIU-SH THETA JA VS. AIRFLOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |       |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |       |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |       |

ISSUE 2

OCTAL SHORT-HAUL E1/T1/J1 LINE INTERFACE DEVICE

#### 1 FEATURES

- Monolithic device which integrates eight T1/J1 or E1 short haul line interface circuits:

- Software switchable between T1/J1 and E1 operation on a per-device basis.

- Meets or exceeds T1/J1 and E1 short haul network access specifications including ANSI T1.102, T1.403, T1.408, AT&T TR 62411, ITU-T G.703, G.704 as well as ETSI 300-011, CTR-4, CTR-12 and CTR-13.

- Provides encoding and decoding of B8ZS, HDB3 and AMI line codes.

- Provides receive equalization, clock recovery and line performance monitoring.

- Provides transmit and receive jitter attenuation.

- Provides digitally programmable short haul transmit templates.

- Provides a selectable, per channel independent de-jittered T1 or E1 recovered clock for system timing and redundancy.

- Provides PRBS generators and detectors on each tributary for error testing at DS1 and E1 rates as recommended in ITU-T 0.151.

- Provides parallel Scaleable Bandwidth Interconnect (SBI) interfaces on the system side.

- Provides an 8-bit microprocessor bus interface for configuration, control, and status monitoring.

- Uses line rate system clock.

- Provides an IEEE 1149.1 (JTAG) compliant Test Access Port (TAP) and controller for boundary scan test.

- Implemented in a low power 3.3 V tolerant 1.8/3.3 V CMOS technology.

- Available in a high density 288-pin Tape-SBGA (23 mm by 23 mm) package.

- Provides a –40°C to +85°C Industrial temperature operating range.

#### 1.1 <u>Each Receiver Section:</u>

- Supports T1 signal reception for distances with up to 12 dB of cable attenuation at nominal conditions using PIC 22 gauge cable emulation.

- Supports E1 signal reception for distances with up to 12 dB of cable attenuation at nominal conditions using PIC 22 gauge cable emulation.

- Supports G.772 compliant non-intrusive protected monitoring points.

- Recovers clock and data using a digital phase locked loop for high jitter tolerance.

ISSUE 2

OCTAL SHORT-HAUL E1/T1/J1 LINE INTERFACE DEVICE

- Tolerates more than 0.4 UI peak-to-peak; high frequency jitter as required by AT&T TR 62411 and Bellcore TR-TSY-000170.

- Outputs parallel data in SBI bus format.

- Performs B8ZS or AMI decoding when processing a bipolar DS-1 signal and HDB3 or AMI decoding when processing a bipolar E1 signal.

- Detects line code violations (LCVs), B8ZS/HDB3 line code signatures, and 4 (E1), 8 (T1+B8ZS) or 16 (T1 AMI) successive zeros.

- Accumulates up to 8191 line code violations (LCVs), for performance monitoring purposes, over accumulation intervals defined by the period between software write accesses to the LCV register.

- Detects loss of signal (LOS), which is defined as 10, 15, 31, 63, or 175 successive zeros.

- Detects programmable inband loopback activate and deactivate code sequences received in the DS-1 data stream when they are present for 5.1 seconds. Optionally, enters loopback mode automatically on detection of an inband loopback code.

- Detects violations of the ANSI T1.403 12.5% pulse density rule over a moving 192-bit window.

- A pseudo-random sequence user selectable from 2<sup>11</sup> –1, 2<sup>15</sup> –1 or 2<sup>20</sup> –1, may be detected in the T1/E1 stream in either the receive or transmit directions. The detector counts pattern errors using a 24-bit saturating PRBS error counter.

#### 1.2 Each Transmitter Section:

- Supports transfer of transmitted single rail PCM and signaling data from 1.544 Mbit/s and 2.048 Mbit/s backplane buses.

- Generates DSX-1 shorthaul pulses with programmable pulse shape compatible with AT&T, ANSI and ITU requirements.

- Generates E1 pulses compliant to G.703 recommendations.

- Provides a digitally programmable pulse shape extending up to 5 transmitted bit periods for custom short haul pulse shaping applications.

- Provides line outputs that are current limited and may be tristated for protection or in redundant applications.

- Provides a digital phase locked loop for generation of a low jitter transmit clock complying with all jitter attenuation, jitter transfer and residual jitter specifications of AT&T TR 62411 and ETSI TBR 12 and TBR 13.

- Provides a FIFO buffer for jitter attenuation and rate conversion in the transmit path.

- Allows bipolar violation (BPV) transparent operation for error restoring regenerator applications.

ISSUE 2

- Allows bipolar violation (BPV) insertion for diagnostic testing purposes.

- Supports all ones transmission for alarm indication signal (AIS) generation.

- Accepts parallel data from the SBI interface.

- Performs B8ZS or AMI encoding when processing an SBI-sourced DS-1 signal and HDB3 or AMI encoding when processing an SBI-sourced E1 signal.

- A pseudo-random sequence user selectable from 2<sup>11</sup> –1, 2<sup>15</sup> –1 or 2<sup>20</sup> –1, may be inserted into or detected from the T1 or E1 stream in either the receive or transmit directions.

- Detects violations of the ANSI T1.403 12.5% pulse density rule over a moving 192-bit window and optionally stuffs ones to maintain minimum ones density.

- Supports transmission of a programmable unframed inband loopback code sequence.

DATA SHEET PMC- 2012568

ISSUE 2

OCTAL SHORT-HAUL E1/T1/J1 LINE INTERFACE DEVICE

# 2 **APPLICATIONS**

- Metro Optical Access Equipment

- Edge Router Linecards

- Multiservice ATM Switch Linecards

- 3G Base Station Controllers (BSC)

- 3G Base Transceiver Stations (BTS)

- Digital Private Branch Exchanges (PBX)

- Digital Access Cross-Connect Systems (DACS) and Electronic DSX Cross-Connect Systems (EDSX)

- Test Equipment

DATA SHEET PMC- 2012568

**ISSUE 2**

OCTAL SHORT-HAUL E1/T1/J1 LINE INTERFACE DEVICE

#### 3 REFERENCES

- ANSI T1.102-1993 American National Standard for Telecommunications Digital Hierarchy – Electrical Interfaces.

- ANSI T1.107-1995 American National Standard for Telecommunications Digital Hierarchy – Formats Specification.

- 3. ANSI T1.403-1999 American National Standard for Telecommunications Carrier to Customer Installation DS-1 Metallic Interface Specification.

- 4. ANSI T1.408-1990 American National Standard for Telecommunications Integrated Services Digital Network (ISDN) Primary Rate Customer Installation Metallic Interfaces Layer 1 Specification.

- 5. AT&T TR 62411 Accunet T1.5 Service Description and Interface Specification, December 1990.

- 6. AT&T TR 62411 Accunet T1.5 Service Description and Interface Specification, Addendum 1, March 1991.

- 7. AT&T TR 62411 Accunet T1.5 Service Description and Interface Specification, Addendum 2, October 1992.

- 8. TR-TSY-000170 Bellcore Digital Cross-Connect System Requirements and Objectives, Issue 1, November 1985.

- 9. TR-N1WT-000233 Bell Communications Research Wideband and Broadband Digital Cross-Connect Systems Generic Criteria, Issue 3, November 1993.

- 10. TR-NWT-000303 Bell Communications Research Integrated Digital Loop Carrier Generic Requirements, Objectives, and Interface, Issue 2, December, 1992.

- TR-TSY-000499 Bell Communications Research Transport Systems Generic Requirements (TSGR): Common Requirement, Issue 5, December, 1993.

- 12. ETSI ETS 300 011 ISDN Primary Rate User-Network Interface Specification and Test Principles, 1992.

- 13. ETSI ETS 300 233 Access Digital Section for ISDN Primary Rates.

- 14. ETSI CTR 4 Integrated Services Digital Network (ISDN); Attachment requirements for terminal equipment to connect to an ISDN using ISDN primary rate access, November 1995.

- 15. ETSI CTR 12 Business Telecommunications (BT); Open Network Provision (ONP) technical requirements; 2 048 kbit/s digital unstructured leased lines (D2048U) Attachment requirements for terminal equipment interface, December 1993.

**ISSUE 2**

- 16. ETSI CTR 13 Business Telecommunications (BTC); 2 048 kbit/s digital structured leased lines (D2048S); Attachment requirements for terminal equipment interface, January 1996.

- 17. FCC Rules Part 68.308 Signal Power Limitations.

- ITU-T Recommendation G.703 Physical/Electrical Characteristics of Hierarchical Digital Interface, Geneva, 1998.

- 19. ITU-T Recommendation G.704 Synchronous Frame Structures Used at Primary Hierarchical Levels, July 1998.

- 20. ITU-T Recommendation G.772 Protected Monitoring Points Provided on Digital Transmission Systems, 1992.

- 21. ITU-T Recommendation G.775 Loss of Signal (LOS), November 1998.

- 22. ITU-T Recommendation G.823, The Control of Jitter and Wander Within Digital Networks Which are Based on the 2048 kbit/s Hierarchy, 1993.

- ITU-T Recommendation I.431 Primary Rate User-Network Interface Layer 1 Specification, 1993.

- 24. ITU-T Recommendation O.151, Error Performance Measuring Equipment For Digital Systems at the Primary Bit Rate and Above, 1992.