## **Dual 5-Bit Bus Switch**

#### **Features**

- Zero propagation delay

- 2 $\Omega$  switches connect inputs to outputs

- Direct bus connection when switches are ON

- High (>500 Meg  $\Omega$ ) resistance when switch is OFF

- Performs bidirectional translator function between 3.3V and 5.0V power supplies

- . CMOS for low power dissipation

- Edge-rate control circuitry for significantly improved noise characteristics

- Inputs and outputs interface with 5.0V CMOS, TTL, or 3.3V CMOS

- ESD > 2000V

- · Power-off disable

#### CYBUS3L384

· Low power version

### **Functional Description**

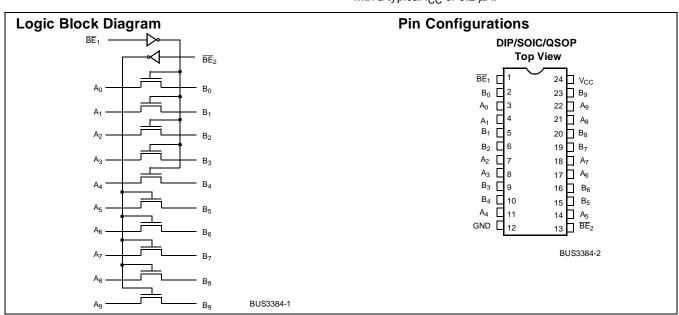

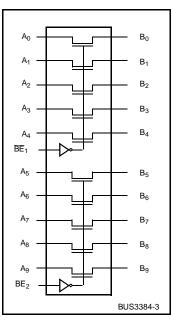

The CYBUS3384 and CYBUS3L384 are ten-bit, two-port bidirectional bus switches that allow one bus to be connected directly to, or isolated from, another without introducing additional propagation delay or ground noise. The input and output voltage levels allow direct interface with TTL and CMOS devices. Two bus enable signals,  $\overline{BE}_1$  and  $\overline{BE}_2$ , turn on the upper and lower five bits, respectively.

Designed with a low resistance of  $2\Omega$ , the CYBUS3384 and CYBUS3L384 are ideal for use in VME or other high DC drive applications.

The power-off disable feature enables modules and cards to be either inserted or withdrawn from operating equipment without shutting down power. Additionally, they facilitate bidirectional interfacing between 3.3V and 5V systems by placing a single diode in series with the 5V  $V_{\rm CC}$  line and a resistor from pin 24 to ground.

The CYBUS3384 and CYBUS3L384 are also suitable for small signal analog application where crosstalk and off isolation performance of –66 dB at 50 MHz is required.

The CYBUS3L384 is a low-power version of the CYBUS3384 with a typical  $I_{CC}$  of 0.2  $\mu\text{A}.$

### **Pin Description**

| Name                              | Description              |

|-----------------------------------|--------------------------|

| Α                                 | Bus A, Inputs or Outputs |

| В                                 | Bus B, Inputs or Outputs |

| BE <sub>1</sub> , BE <sub>2</sub> | Bus Switch Enable        |

#### Function Table<sup>[1]</sup>

| BE <sub>1</sub> | BE <sub>2</sub> | B <sub>0-4</sub> | B <sub>5-9</sub> | Function    |

|-----------------|-----------------|------------------|------------------|-------------|

| Н               | Н               | High-Z           | High-Z           | Non-connect |

| L               | Н               | A <sub>0-4</sub> | High-Z           | Connect     |

| Н               | L               | High-Z           | A <sub>5-9</sub> | Connect     |

| L               | L               | A <sub>0-4</sub> | A <sub>5-9</sub> | Connect     |

Note:

1. H = HIGH Voltage Level. L = LOW Voltage Level. X = Don't Care.

### Maximum Ratings<sup>[2, 3]</sup>

| Power Dissipation              | 0.5W    |

|--------------------------------|---------|

| Static Discharge Voltage       | .>2001V |

| (per MIL-STD-883, Method 3015) |         |

### **Operating Range**

| Range      | Ambient<br>Temperature | V <sub>CC</sub> |

|------------|------------------------|-----------------|

| Commercial | -40°C to +85°C         | 4.0V to 5.5V    |

| Military   | −55°C to +125°C        | 4.0V to 5.5V    |

### **Electrical Characteristics** Over the Operating Range

| Parameter        | Description                                 | Test Conditions                                                               | Min. | Typ. <sup>[4]</sup> | Max. | Unit |

|------------------|---------------------------------------------|-------------------------------------------------------------------------------|------|---------------------|------|------|

| V <sub>IH</sub>  | Input HIGH Voltage                          | Control Inputs Only                                                           | 2.0  |                     |      | V    |

| V <sub>IL</sub>  | Input LOW Voltage                           | Control Inputs Only                                                           |      |                     | 0.8  | V    |

| V <sub>H</sub>   | Hysteresis <sup>[5]</sup>                   | Control Inputs Only                                                           |      | 0.2                 |      | V    |

| V <sub>IK</sub>  | Input Clamp Diode Voltage                   | V <sub>CC</sub> =Min., I <sub>IN</sub> =–18 mA                                |      | -0.7                | -1.2 | V    |

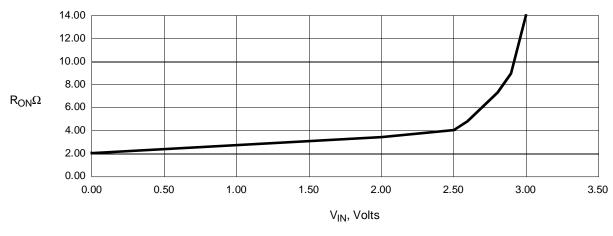

| R <sub>ON</sub>  | Switch On Resistance <sup>[6]</sup>         | V <sub>CC</sub> =4.75V, V <sub>IN</sub> =0.0V, I <sub>ON</sub> =30 mA         |      | 2                   | 4    | W    |

|                  |                                             | V <sub>CC</sub> =4.75V, V <sub>IN</sub> =2.4V, I <sub>ON</sub> =15 mA         |      | 4                   | 8    | W    |

| I <sub>IN</sub>  | Input Leakage Current                       | V <sub>CC</sub> =Max., V <sub>IN</sub> =V <sub>CC</sub>                       |      |                     | ±1   | μΑ   |

| I <sub>OZ</sub>  | Off State Current (High-Z)                  | V <sub>CC</sub> =Max., V <sub>OUT</sub> =0.5V                                 |      | 0.001               | ±1   | μΑ   |

| I <sub>OFF</sub> | Power-Off Disable                           | V <sub>CC</sub> =0V, V <sub>OUT</sub> =4.5V, V <sub>IN</sub> =V <sub>CC</sub> |      |                     | ±1   | μΑ   |

| Ios              | Output Short Circuit Current <sup>[7]</sup> | V <sub>CC</sub> =Max., V <sub>OUT</sub> =0.0V                                 |      | 100                 |      | mA   |

### On Resistance vs. V<sub>IN</sub> @ 4.75 V<sub>CC</sub>

- Unless otherwise noted, these limits are over the operating free-air temperature range. Unused inputs must always be connected to an appropriate logic voltage level, preferably either  $V_{CC}$  or ground.

- Typical values are at  $V_{CC}$ =5.0V,  $T_A$ =+25°C ambient.

This parameter is guaranteed but not tested.

Measured by voltage drop between A and B pin at indicated current through the switch. On resistance is determined by the lower of the voltages on pin A

- or pin B.

Not more than one output should be shorted at a time. Duration of short should not exceed one second. The use of high-speed test apparatus and/or sample and hold techniques are preferable in order to minimize internal chip heating and more accurately reflect operational values. Otherwise prolonged shorting of a high output may raise the chip temperature well above normal and thereby cause invalid readings in other parametric tests. In any sequence of parameter tests, I<sub>OS</sub> tests should be performed last.

### Capacitance<sup>[6]</sup>

| Parameter        | Description        | Typ. <sup>[4]</sup> | Max. | Unit |

|------------------|--------------------|---------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | 3                   | 4    | pF   |

| C <sub>OUT</sub> | Output Capacitance | 7                   | 8    | pF   |

### **Power Supply Characteristics**

| Parameter        | Description                                                | Test Conditions <sup>[8]</sup>                                                                  |       | Typ. <sup>[4]</sup> | Max. | Unit       |

|------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------|---------------------|------|------------|

| I <sub>CC</sub>  | Quiescent Power Supply Current                             | V <sub>CC</sub> =Max., V <sub>IN</sub> ≤GND or V <sub>CC</sub> , f=0                            | 3384  | 0.2                 | 3.0  | μΑ         |

|                  |                                                            |                                                                                                 | 3L384 | 0.2                 | 3.0  | μΑ         |

| Δl <sub>CC</sub> | Quiescent Power Supply Current (Input HIGH) <sup>[9]</sup> | V <sub>CC</sub> =Max., V <sub>IN</sub> =3.4V, f=0, Per Control Input                            |       |                     | 2.0  | mA         |

| I <sub>CCD</sub> | Dynamic Power Supply Current <sup>[10]</sup>               | V <sub>CC</sub> =Max., Control Input Toggling,<br>@ 50% Duty Cycle, A & B Pins Open             |       |                     | 0.12 | mA/<br>MHz |

| I <sub>C</sub>   | Total Power Supply Current <sup>[11, 12]</sup>             | V <sub>CC</sub> =Max.,                                                                          | 3384  |                     | 4.4  | mA         |

|                  |                                                            | Two Control Inputs Toggling, @ 50%<br>Duty Cycle, f <sub>1</sub> =10 MHz, V <sub>IN</sub> =3.4V | 3L384 |                     | 4.4  | mA         |

### Switching Characteristics Over the Operating Range<sup>[13]</sup>

|                                      |                                                                                                 | Milit | Military |      | Commercial |      |

|--------------------------------------|-------------------------------------------------------------------------------------------------|-------|----------|------|------------|------|

| Parameter                            | Description                                                                                     | Min.  | Max.     | Min. | Max.       | Unit |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>A to B <sup>[14, 15]</sup>                                                 |       | 0.25     |      | .25        | ns   |

| t <sub>PZH</sub><br>t <sub>PZL</sub> | Switch Turn On Delay,<br>BE <sub>1</sub> , BE <sub>2</sub> to A, B <sup>[13]</sup>              | 1.5   | 7.5      | 1.5  | 6.5        | ns   |

| t <sub>PHZ</sub><br>t <sub>PHZ</sub> | Switch Turn Off Delay, $\overline{BE}_1$ , $\overline{BE}_2$ to A, $\overline{BE}_1^{[13, 14]}$ | 1.5   | 6.5      | 1.5  | 5.5        | ns   |

| Q <sub>ci</sub>                      | Charge Injection, Typical <sup>[16, 17]</sup>                                                   |       | 1.5      |      | 1.5        | рC   |

#### Notes:

- For conditions shown as MIN or MAX use the appropriate values specified under DC specifications. Per TTL driven input ( $V_{IN}$ =3.4V); A and B pins do not contribute to  $I_{CC}$ . All other inputs at  $V_{CC}$  or GND.

- This current applies to the control inputs only and represents the current required to switch internal capacitance at the specified frequency. The A and B inputs generate no significant AC or DC currents as they transition. This parameter is not tested but is guaranteed by design.

- generate no significant AC of DC currents as they transition. This  $I_{\rm C} = I_{\rm QUIESCENT} + I_{\rm INPUTS} + I_{\rm DYNAMIC}$   $I_{\rm C} = I_{\rm CC} + \Delta I_{\rm CC} D_{\rm H} N_{\rm T} + I_{\rm CC} D_{\rm H} (J_{\rm C} + I_{\rm I} N_{\rm T})$   $I_{\rm CC} = I_{\rm CC} + I_{\rm CC} D_{\rm H} N_{\rm T} + I_{\rm CC} D_{\rm CC} + I_{\rm CC} + I_{\rm CC} D_{\rm H} N_{\rm T} + I_{\rm CC} D_{\rm CC} + I_{\rm CC} + I_{\rm CC} D_{\rm CC} + I_{\rm CC} + I_{\rm$

- = Duty Cycle for TTL inputs HIGH

- Duty Gyole for The Imposition.

Number of TTL inputs at D<sub>H</sub>

Dynamic Current caused by an input transition pair (HLH or LHL)

The Imposition of Imposition o

- = Clock frequency for registered devices, otherwise zero

- Input signal frequency

- = Number of inputs changing at f<sub>1</sub>

- 12. Note that activity on A or B inputs do not contribute to I<sub>C</sub>. The switches merely connect and pass through activity on these pins.

- Note that activity on A or B inputs do not continuous to I<sub>C</sub>. The switches meety connect and pass through activity on these pins.

See Test Circuit and Waveform. Minimum limits are guaranteed but not tested.

This parameter is guaranteed by design but not tested.

The bus switch contributes no propagation delay other than the RC delay of the on resistance of the switch and the load capacitance. The time constant for the switch is much smaller than the rise/fall times of typical driving signals, it adds very little propagation delay to the system. Propagation delay of the bus switch when used in a system is determined by the driving circuit on the driving side of the switch and its interaction with the load on the driven side.

Measured at switch turn off, A to C, load=50 pF in parallel with 10 meg scope probe, V<sub>IN</sub> at A=0.0V.

- 17. Tested initially and after any design change which may affect this parameter.

### **Ordering Information CYBUS3384**

| Speed (ns) | Ordering Code | Package<br>Name | Package Type                    | Operating<br>Range |

|------------|---------------|-----------------|---------------------------------|--------------------|

| 0.25       | CYBUS3384PC   | P13/13A         | 24-Lead (300-Mil) Molded DIP    | Commercial         |

|            | CYBUS3384QC   | Q13             | 24-Lead (150-Mil) QSOP          |                    |

|            | CYBUS3384SOC  | S13             | 24-Lead (300-Mil) Molded SOIC   |                    |

| 0.25       | CYBUS3384DMB  | D14             | 24-Lead (300-Mil) CerDIP        | Military           |

|            | CYBUS3384LMB  | L64             | 28-Square Leadless Chip Carrier |                    |

### Ordering Information CYBUS3L384

| Speed<br>(ns) | Ordering Code | Package<br>Name | Package Type                  | Operating<br>Range |

|---------------|---------------|-----------------|-------------------------------|--------------------|

| 0.25          | CYBUS3L384PC  | P13/13A         | 24-Lead (300-Mil) Molded DIP  | Commercial         |

|               | CYBUS3L384QC  | Q13             | 24-Lead (150-Mil) QSOP        | _                  |

|               | CYBUS3L384SOC | S13             | 24-Lead (300-Mil) Molded SOIC |                    |

Figure 1. CYBUS3384

#### **Application Information**

The CYBUS3384 is a ten-channel bidirectional solid state bus switch with a "near zero" propagation delay.

The CYBUS3384 is organized into two groups of five N-Channel MOSFETs. Each group has an independent control input for output enable (see *Figure 1*). Because the N-channel MOSFET is physically symmetric, the device pin can act as an input or an output.

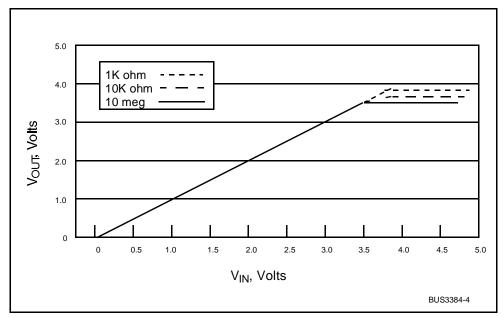

The two enable input ( $\overline{BE}_1$  and  $\overline{BE}_2$ ) sense TTL level signals and drive the gates of the N-channel MOSFETs to VCC. With the gate at V<sub>CC</sub>, the output voltage will follow the input voltage up to V<sub>CC</sub> minus the threshold voltage. At this point the N-channel MOSFET begins to turn off, rapidly increasing the

Figure 2. V<sub>OUT</sub> vs. Volts

effective resistance (R<sub>ON</sub>) such that further increases to input voltage no longer increase the output voltage (see *Figure 2*).

When either the input or output of the CYBUS3384 is near zero volts and the gate is at  $V_{CC}$ , the device is fully on, (low resistance) and available to pass large currents in either direction. In this condition, the CYBUS3384 inputs are directly connected to the outputs.

The CYBUS3384 provides no signal drive itself. As a result the rise and fall times of the CYBUS3384 outputs are determined by the device driving the CYBUS3384 inputs rather than the CYBUS3384 itself.

The propagation delay contributed by the CYBUS3384 is essentially zero when the N-channel gate is at  $V_{\rm CC}$ .

When the device is unpowered, the CYBUS3384 draws no current from the I/O or control inputs, and there is no current

path from the I/O or control to the power pins. There are no back power or current drain problems when the device is unpowered.

The CYBUS3384 provides an ideal interface between 5V and 3.3V components, since the CYBUS3384 provides no signal drive, the  $I_{\rm CC}$  demands are small, limited to AC switching of the N-channel gates, control circuitry, and a minute amount of I/O leakage. Due to the low current demands of the CYBUS3384, it is possible to lower the CYBUS3384 VCC from a standard 5.0V supply with a small, inexpensive diode and a resistor to provide a low-current full-bidirectional signal compatibility between 5V logic family signals and 3.3V logic family signals.

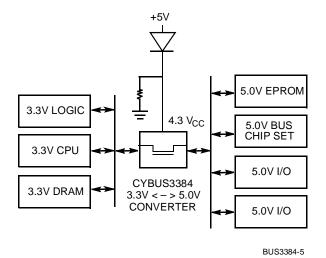

By adding a small, inexpensive diode and a resistor, the CYBUS3384  $V_{CC}$  supply voltage can be shifted to 4.3V as shown in *Figure 3*. 5V signals will then be limited to 3.3V as they pass through the CYBUS3384. 3.3V signals will pass back through the CYBUS3384 unaltered and provide compatibility with 5V TTL input requirements. Note that the conversion is bidirectional and is limited to 3.3V independent of which side is driven to 5V. The CYBUS3384 could convert 5V signals for use on a 3.3V bus of convert a 5V bus to signals compatible with 3.3V components.

#### 3.3V/5V Supply Operation

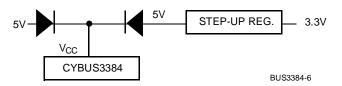

In certain system applications, the CYBUS3384 must operate from either a 5V or 3.3V power supply, depending on the state of the system. If this occurs, the circuit shown in Figure 4 can be added to step the 3.3V supply up to a nominal 5V level. The low-cost, high-efficiency Step Up regulator shown in the figure is available for Linear Technology, Maxim, and other suppliers. The diode arrangement will automatically select the active supply. Standard silicon diodes can be used because the CYBUS3384  $\rm V_{CC}$  is specified at 4.0V.

Figure 3. System with CYBUS3384 as 5V TTL to 3V Converter

Figure 4. 3.3V/5V Supply Switch

#### Low Power Bus Isolation

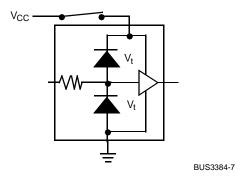

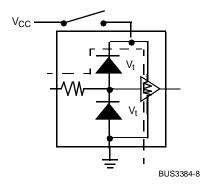

Modern battery-operated systems rely on internal power management schemes to disconnect power from subsystems not in use. Usually the subsystem bus input ESD protection circuits consist of a pair of clamp diodes to limit input voltage excursions to a maximum of  $V_{CC}+Vt$  and -Vt (see Figure 5). Removing power from these causes the VCC ESD clamp diode to connect the dead circuit inputs to GND, often significantly increasing bus loading and power dissipation (see Figure 6). The CYBUS3384 placed on the input of the load to be disconnected effectively prevents bus loading and its associated problems.

Figure 5. Gate Input (Power ON)

Figure 6. Gate Input (Power OFF)

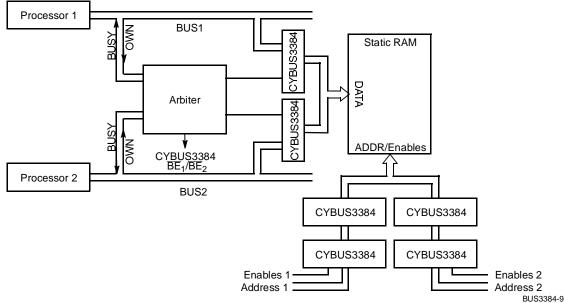

Figure 7. High Speed Dual Port RAM

#### **High Speed Dual Port RAM**

As shown in Figure 7, a high-speed, dual-port memory is implemented using a combination of commodity SRAM, a simple arbitration circuit, and the CYBUS3384. Processor 1 is the system host processor while Processor 2 is dedicated peripheral processor (such as a DSP for acquisitioning and manipulating data). Either processor can own the SRAM by first reading the BUSY bit to determine if the SRAM is available. If so, the requesting processor takes control by writing the OWN bit (which redirects the bus through the CYBUS3384s and sets the BUSY bit notifying the other bus the SRAM is not available). Processor 1 owns the bus and may now access the SRAM as needed. When finished, Processor 1 resets the OWN bit releasing the SRAM. The SRAM access sequence is identical for Processor 2. In this application, the CYBUS3384 saves 10 ns compared to using an F244 address buffer and an F245 data bus transceiver. This, in turn, allows the use of a slower, more available SRAM, resulting in lower system cost and power savings.

#### **Selectable Termination Loads**

In some applications, it is desirable to vary the characteristic termination impedance as the system configuration changes. This is a common problem in automatic test equipment applications. Because of their low ON resistance, miniature relays are often used to switch termination loads. A single CYBUS3384 can replace as many as 10 such relays resulting in faster switching operation, lower power, and significant cost savings.

#### **Fast Latch**

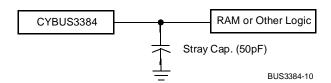

Figures 8 and 9 show variations of a latch having a sub 1-ns propagational delay time using the CYBUS3384 in combination with other components. This circuit has the advantage of being four to ten times faster than an equivalent implementation using a 373 latch—and with no added noise. Figure 8 relies on the stray capacitance of the bus to maintain data when the CYBUS3384 opens. Assuming 50-pF stray capacitance at room temperature and a 1 microampere input leakage

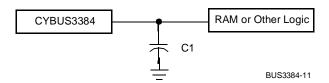

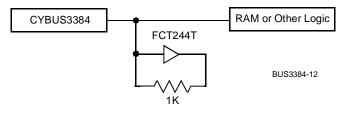

current, a 1 volt "droop" from the initial voltage level would take 50 microseconds. Figure 9 shows the addition of a physical capacitor if there is insufficient stray capacitance. Figure 10 shows an active bus termination capable of sustaining the programmed logic for an indefinite period of time in the presence of  $V_{CC}$ .

Figure 8. Latch Variation with Spray Capacitance

Figure 9. Latch Variation with Physical Capacitor

Figure 10. Active Bus Termination

Document #: 38-00355

### **Package Diagrams**

# **24-Lead (300-Mil) CerDIP D14**MIL-STD-1835 D-9 Config.A

###

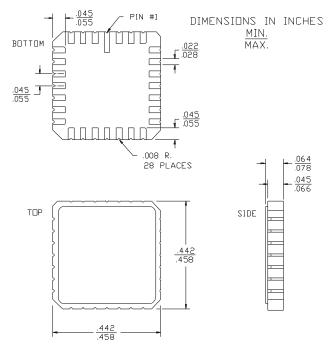

#### 28-Square Leadless Chip Carrier L64 MIL-STD-1835 C-4

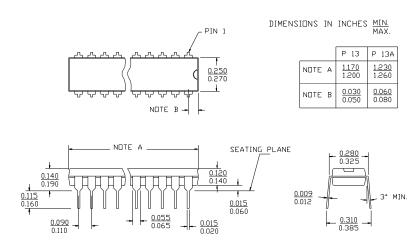

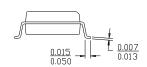

### 24-Lead (300-Mil) Molded DIP P13/P13A

### Package Diagrams (Continued)

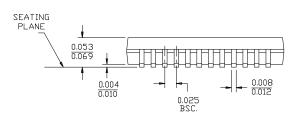

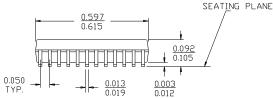

#### 24-Lead Quarter Size Outline Q13

DIMENSIONS IN INCHES  $\frac{\text{MIN.}}{\text{MAX.}}$  LEAD COPLANARITY 0.004 MAX.

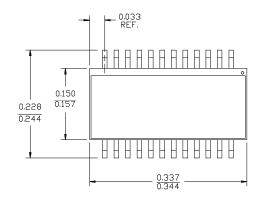

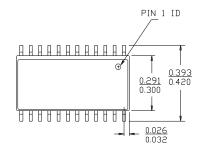

#### 24-Lead (300-Mil) Molded SOIC S13

DIMENSIONS IN INCHES MIN. MAX.

LEAD COPLANARITY 0.004 MAX.

<sup>©</sup> Cypress Semiconductor Corporation, 1996. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfurnion or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.