# RISC FLOATING POINT ACCELERATOR (FPA)

IDT79R3010A IDT79R3010AE

#### **FEATURES:**

- Hardware Support of Single and Double-Precision Operations:

- Floating-Point Add

- Floating-Point Subtract

- Floating-Point Multiply

- Floating-Point Divide

- Floating-Point Comparisons

- Floating-Point Conversions

- Sustained performance:

- 11 MFLOPS single precision LINPACK

- 7.3 MFLOPS double precision LINPACK

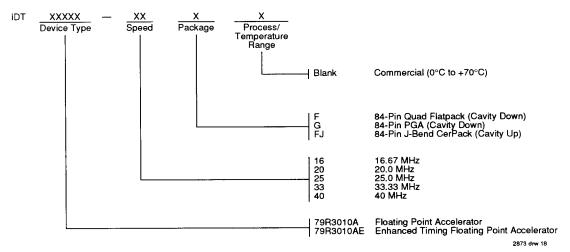

- 16.7MHz through 40MHz operation

- Direct, high-speed interface with IDT79R3000A and IDT79R3001 Processor

- Supports Full Conformance With IEEE 754-1985 Floating-PointSpecification

- Full 64-bit operation using sixteen 64-bit data registers

- High-speed CMOS technology

- 32-bit status/control register providing access to all IEEE-Standard exception handling

- Load/store architecture allows data movement directly between FPA and memory or between CPU and FPA

- · Overlapped operation of independent floating point ALUs

#### **DESCRIPTION:**

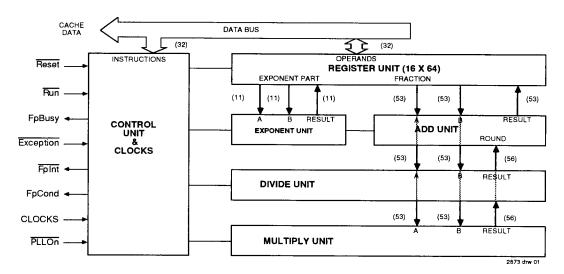

The IDT79R3010A Floating-Point Accelerator (FPA) operates in conjunction with the IDT79R3000A Processor and extends the IDT79R3000As instruction set to perform arithmetic operations on values in floating-point representations. The IDT79R3010A FPA, with associated system software, fully conforms to the requirements of ANSI/IEEE Standard 754-1985, "IEEE Standard for Binary Floating-Point Arithmetic." In addition, the architecture fully supports the standard's recomendations.

This data sheet provides an overview of the features and architecture of the 79R3010A FPA. A more detailed description of the operation of the device is incorporated in the R3000A Family Hardware User's Manual, available from IDT, and a more detailed architectural overview is provided in the MIPS RISC Architecture book, available from MIPS/SGI.

Figure 1. IDT79R3010A Functional Block Diagram

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

COMMERCIAL TEMPERATURE RANGE

**JUNE 1992**

© 1992 Integrated Device Technology, Inc.

6.1

DSC-9039/4

#### **IDT79R3010A FPA REGISTERS**

The IDT79R3010A FPA provides 32 general purpose 32-bit registers, a Control/Status register, and a Revision Identi-

fication register. The tightly-coupled coprocessor interface causes the register resources of the FPA to appear to the systems programmers as an extension of the CPU internal registers. The FPA registers are shown in Figure 2.

## General Purpose Registers (FGR/FPR)

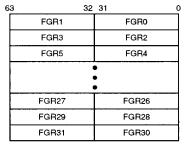

Figure 2. IDT79R3010A FPA Registers

Floating-point coprocessor operations reference three types of registers:

- Floating-Point Control Registers (FCR)

- Floating-Point General Registers (FGR)

- Floating-Point Registers (FPR)

#### Floating-Point General Registers (FGR)

There are 32 Floating-Point General Registers (FGR) on the FPA. They represent directly-addressable 32-bit registers, and can be accessed by Load, Store, or Move Operations.

#### Floating-Point Registers (FPR)

The 32 FGRs described in the preceding paragraph are also used to form sixteen 64-bit Floating-Point Registers (FPR). Pairs of general registers (FGRs), for example FGR0 and FGR1 (refer to Figure 2) are physically combined to form a single 64-bit FPR. The FPRs hold a value in either single-or double-precision floating-point format. Double-precision format FPRs are formed from two adjacent FGRs.

#### Floating-Point Control Registers (FCR)

There are 2 Floating-Point Control Registers (FCR) on the FPA. They can be accessed only by Move operations and include the following:

- Control/Status register, used to control and monitor exceptions, operating modes, and rounding modes;

- Revision register, containing revision information about the FPA.

#### COPROCESSOR OPERATION

The FPA continually monitors the IDT79R3000A processor instruction stream. If an instruction does not apply to the coprocessor, it is ignored; if an instruction does apply to the coprocessor, the FPA executes that instruction and transfers necessary result and exception data synchronously to the IDT79R3000A main processor.

The FPA performs three types of operations:

- · Loads and Stores;

- Moves:

- · Two- and three-register floating-point operations.

#### Load, Store, and Move Operations

Load, Store, and Move operations move data between memory or the IDT79R3000A Processor registers and the IDT79R3010A FPA registers. These operations perform no format conversions and cause no floating-point exceptions. Load, Store, and Move operations reference a single 32-bit word of either the Floating-Point General Registers (FGR) or the Floating-Point Control Registers (FCR).

#### Floating-Point Operations

The FPA supports the following single- and double-precision format floating-point operations:

- Add

- Subtract

- Multiply

- Divide

- Absolute Value

- Move

- Negate

- Compare

In addition, the FPA supports conversions between singleand double-precision floating-point formats and fixed-point formats.

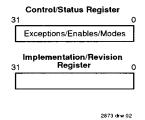

The FPA incorporates separate Add/Subtract, Multiply, and Divide units, each capable of independent and concurrent operation. Thus, to achieve very high performance, floating point divides can be overlapped with floating point multiplies and floating point additions. These floating point operations occur independently of the actions of the CPU. allowing further overlap of integer and floating point operations. Figure 3 illustrates an example of the types of overlap permissible.

Figure 3. Examples of Overlapping Floating Point Operation

#### **Exceptions**

The IDT79R3010A FPA supports all five IEEE standard exceptions:

- Invalid Operation

- Inexact Operation

- · Division by Zero

- Overflow

- Underflow

The FPA also supports the optional, Unimplemented Operation exception that allows unimplemented instructions to trap to software emulation routines.

The FPA provides precise exception capability to the CPU; that is, the execution of a floating point operation which generates an exception causes that exception to occur at the CPU instruction which caused the operation. This precise exception capability is a requirement in applications and languages which provide a mechanism for local software exception handlers within software modules.

#### INSTRUCTION SET OVERVIEW

All IDT79R3010A instructions are 32 bits long and they can be divided into the following groups:

- Load/Store and Move instructions move data between memory, the main processor and the FPA general registers.

- Computational instructions perform arithmetic operations on floating point values in the FPA registers.

- Conversion instructions perform conversion operations between the various data formats.

- **Compare** instructions perform comparisons of the contents of registers and set a condition bit based on the results. The result of the compare operation is output on the FpCond output of the FPA, which is typically used as CpCond1 on the CPU for use in coprocessor branch operations.

Table 1 lists the instruction set of the IDT79R3010A FPA.

| OP        | Description                           | OP         | Description                   |

|-----------|---------------------------------------|------------|-------------------------------|

|           | Load/Store/Move Instructions          |            | Computational Instructions    |

| LWC1      | Load Word to FPA                      | ADD.fmt    | Floating-point Add            |

| SWC1      | Store Word from FPA                   | SUB.fmt    | Floating-point Subtract       |

| MTC1      | Move Word to FPA                      | MUL. fmt   | Floating-point Multiply       |

| MFC1      | Move Word from FPA                    | DIV.fmt    | Floating-point Divide         |

| CTC1      | Move Control word to FPA              | ABS.fmt    | Floating-point Absolute value |

| CFC1      | Move Control word from FPA            | MOV.fmt    | Floating-point Move           |

|           |                                       | NEG.fmt    | Floating-point Negate         |

|           | Conversion Instructions               |            | Compare Instructions          |

| CVT.S.fmt | Floating-point Convert to Single FP   | C.cond.fmt | Floating-point Compare        |

| CVT.D.fmt | Floating-point Convert to Double FP   |            | 1                             |

| CVT.W.fmt | Floating-point Convert to fixed-point |            |                               |

Table 1. IDT79R3010A Instruction Summary

2873 tol 01

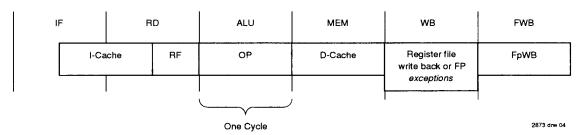

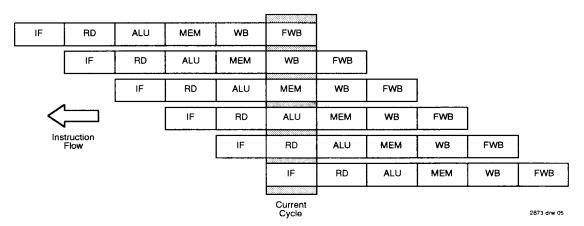

#### **ID79R3010 PIPELINE ARCHITECTURE**

The IDT79R3010A FPA provides an instruction pipeline that parallels that of the IDT79R3000A processor. The FPA, however, has a 6-stage pipeline instead of the 5-stage pipeline of the IDT79R3000: the additional FPA pipe stage is used to provide efficient coordination of exception responses between the FPA and main processor.

The execution of a single IDT79R3010A instruction consists of six primary steps:

- IF—Instruction Fetch. The main processor calculates the insruction address required to read an instruction from the I-Cache. No action is required of the FPA during this pipe stage since the main processor is responsible for address generation.

- RD—The instruction is present on the data bus during phase 1 of this pipe stage and the FPA decodes the

- instruction on the bus to determine if it is an instruction for the FPA.

- 3) **ALU**—If the instruction is an FPA instruction, instruction execution commences during this pipe stage.

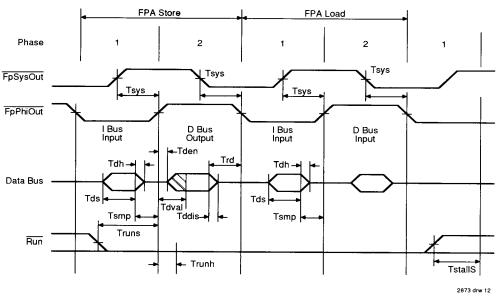

- 4) MEM—If this is a coprocessor load or store instruction, the FPA presents or captures the data during phase 2 of this pipe stage.

- WB—The FPA uses this pipe stage solely to deal with exceptions.

- 6) FWB—The FPA uses this stage to write back ALU results to its register file. This stage is the equivalent of the WB stage in the IDT79R3000A main processor.

Each of these steps requires approximately one FPA cycle as shown in Figure 3 (parts of some operations spill over into another cycle while other operations require only 1/2 cycle).

#### INSTRUCTION EXECUTION

Figure 4. IDT79R3010A Instruction Summary

Figure 5. IDT79R3010A Instruction Pipeline

The IDT79R3010A uses a 6-stage pipeline to achieve an instruction execution rate approaching one instruction per FPA cycle. Thus, execution of six instructions at a time are overlapped as shown in Figure 5.

This pipeline operates efficiently because different FPA resources (address and data bus accesses, ALU operations. register accesses, and so on) are utilized on a non-interfering basis.

#### PACKAGE THERMAL SPECIFICATIONS

The IDT79R3010A utilizes special packaging techniques to improve both the thermal and electrical characteristics of the floating point accelerator.

In order to improve the electrical characteristics of the device, the package is constructed using multiple signal planes, including individual power planes and ground planes to reduce noise associated with high-frequency TTL parts.

In order to improve the thermal characteristics of the floating point accelerator, the device is housed using cavity down packaging for the flatpack and the PGA (the J-bend CerQuad is cavity up). In addition, these packages incorporate a copper-tungsten thermal slug designed to efficiently transfer heat from the die to the case of the package, and thus effectively lower the thermal resistance of the package. The use of an additional external heat sink affixed to the package thermal slug further decreases the effective thermal resistance of the package.

The case temperature may be measured in any environment to determine whether the device is within the specified operating range. The case temperature should be measured at the

center of the top surface opposite the package cavity (the package cavity is the side where the package lid is mounted).

The equivalent allowable ambient temperature, TA, can be calculated using the thermal resistance from case to ambient (Øca) for the given package. The following equation relates ambient and case temperature:

where P is the maximum power consumption, calculated by using the maximum loc from the DC Electrical Characteristic section.

Typical values for Øca at various airflows are shown in Table 2 for the various CPU packages.

|                   |                       | Airflow - (ft/min) |    |   |     |     |  |  |  |

|-------------------|-----------------------|--------------------|----|---|-----|-----|--|--|--|

|                   | 0 200 400 600 800 100 |                    |    |   |     |     |  |  |  |

| Øca (84-PGA)      | 22                    | 8                  | 3  | 2 | 1.5 | 1.0 |  |  |  |

| Øca (84-Flatpack) | 22                    | 9                  | 4  | 3 | 2   | 1.5 |  |  |  |

| Øca (84-CerQuad)  | 25                    | 17                 | 12 | 8 | 7   | 6   |  |  |  |

2873 tbl 0

Table 2. Thermal Resistance (Oca) at Various Airflows

6

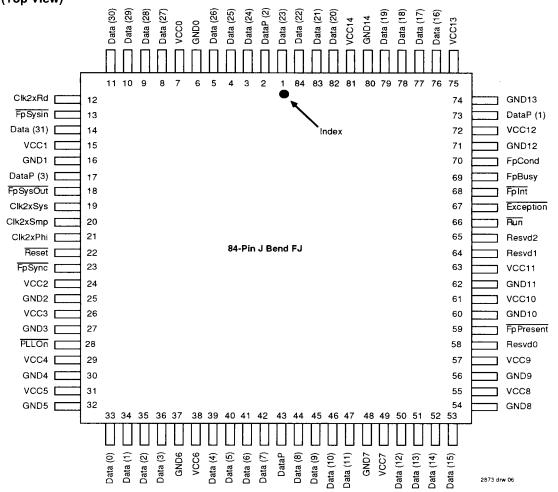

# PIN CONFIGURATION<sup>(1)</sup> (Top View)

#### NOTE:

1. Reserved pins must not be connected

### 6

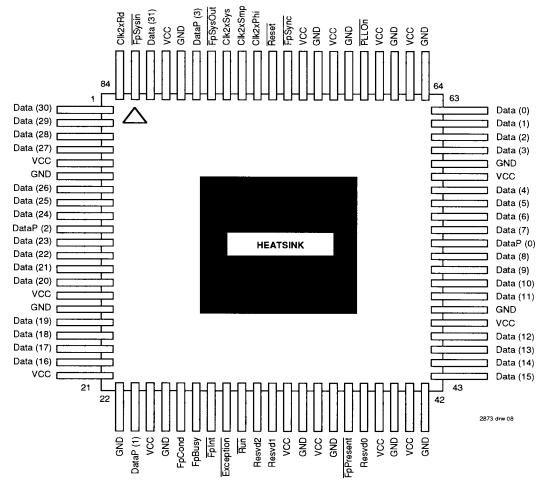

### PIN CONFIGURATION<sup>(1)</sup> (Ceramic, Cavity Down) – BOTTOM VIEW

| М | Vss         | Vcc        | Data<br>17            | DataP<br>1 | Vss          | FP<br>Cond | FPInt          | Vss | Run        | Rsrvd<br>1    | Vcc        | Vss        |

|---|-------------|------------|-----------------------|------------|--------------|------------|----------------|-----|------------|---------------|------------|------------|

| L | Data<br>21  | Data<br>20 | Data<br>18            | Data<br>16 | Vcc          | FPBusy     | Excep-<br>tion | Vcc | Rsrvd<br>2 | FP<br>Present | Data<br>15 | Data<br>14 |

| К | Vss         | Vcc        | Data<br>19            |            |              |            |                |     |            | Rsrvd<br>0    | Vcc        | Vss        |

| J | Data<br>23  | Data<br>22 |                       | •          |              |            |                |     |            |               | Data<br>13 | Data<br>12 |

| н | Data<br>24  | DataP<br>2 |                       |            |              |            |                |     |            |               | Data<br>11 | Data<br>10 |

| G | Data<br>26  | Data<br>25 |                       |            | 84-Pin       | Ceramic F  |                | ray |            |               | Vœ         | Vss        |

| F | Vss         | Vcc        |                       |            |              |            |                |     |            |               | Data<br>8  | Data<br>9  |

| E | Data<br>27  | Data<br>28 |                       |            |              |            |                |     |            |               | Data<br>7  | DataP<br>0 |

| D | Data<br>29  | Data<br>30 |                       |            |              | •          |                |     |            |               | Data<br>5  | Data<br>6  |

| С | Vss         | Vcc        | Clk2x<br>Rd           |            |              |            |                |     |            | Data<br>2     | Vœ         | Vss        |

| В | Fp<br>SysIn | Data<br>31 | DataP<br>3            | Vcc        | Clk2x<br>Sys | Vcc        | Clk2x<br>Phi   | Vœ  | PIIOn      | Data<br>1     | Data<br>3  | Data<br>4  |

| Α | Vss         | Vcc        | F <u>pSy</u> s<br>Out | Vss        | Clk2x<br>Smp | Vss        | Reset .        | Vss | FP<br>Sync | Data<br>0     | Vœ         | Vss        |

| , | 1           | 2          | 3                     | 4          | 5            | 6          | 7              | 8   | 9          | 10            | 11         | 12         |

2873 drw 07

#### NOTE:

Reserved pins must not be connected.

### PIN CONFIGURATION<sup>(1)</sup> 84-L QUAD FLATPACK (CAVITY DOWN) TOP VIEW

#### NOTE:

Reserved pins must not be connected.

#### **PIN DESCRIPTIONS**

| Pin Name    | I/O | Description                                                                                                                                                                                      |

|-------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data (0-31) | 1/0 | A multiplexed 32-bit bus used for instruction and data transfers on phase 1 and phase 2, respectively.                                                                                           |

| DataP (0-3) | 0   | A 4-bit bus containing even parity over the data bus. Parity is generated by the FPA on stores.                                                                                                  |

| Run         | 1   | Input to the FPA which indicates whether the processor-coprocessor system is in the run or stall state.                                                                                          |

| Exception   | 1   | Input to the FPA which indicates exception related status information.                                                                                                                           |

| FpBusy      | 0   | Signal to the CPU indicating a request for a coprocessor busy stall.                                                                                                                             |

| FpCond      | 0   | Signal to the CPU indicating the result of the last comparision operation.                                                                                                                       |

| FpInt       | 0   | Signal to the CPU indicating that a floating-point exception has occured for the current FPA instruction.                                                                                        |

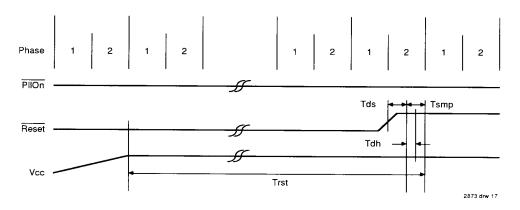

| Reset       | _   | Synchronous initialization input used to distinguish the processor-FPA synchronization period from the execution period. Reset must be synchronized by the leading edge of SysOut from the CPU.  |

| PIIOn       | 1   | Input which during the reset period determines whether the phase lock mechanism is enabled and during the execution period determines the output timing model.                                   |

| FpPresent   | 0   | Output which is pulled to ground through an impedance of approximately 0.5kΩ. By providing an external pullup on this line, an indication of the presence or absence of the FPA can be obtained. |

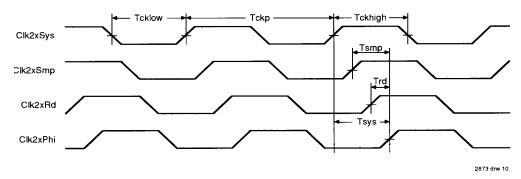

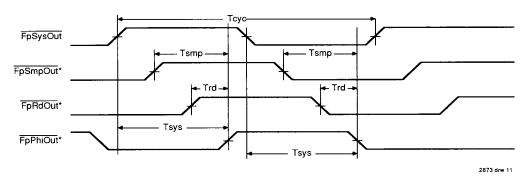

| Clk2xSys    | 1   | A double frequency clock input used for generating FpSysOut.                                                                                                                                     |

| Clk2xSmp    | !   | A double frequency clock input used to determine the sample point for data coming in to the FPA.                                                                                                 |

| Clk2xRd     | _   | A double frequency clock input used to determine the disable point for the data drivers.                                                                                                         |

| Clk2xPhi    | _   | A double frequency clock input used to determine the position of the internal phases, phase 1 and phase 2.                                                                                       |

| FpSysOut    | 0   | Synchronization clock from the FPA.                                                                                                                                                              |

| FpSysin     | ı   | Input used to receive the synchronization clock from the FPA.                                                                                                                                    |

| FpSync      | _   | Input used to receive the synchronization clock from the CPU.                                                                                                                                    |

2873 tbl 03

#### ABSOLUTE MAXIMUM RATINGS(1,3)

| Symbol | Rating                                     | Commercial                                                       | Unit |

|--------|--------------------------------------------|------------------------------------------------------------------|------|

| VTERM  | Terminal Voltage<br>with Respect<br>to GND | -0.5 to +7.0                                                     | V    |

| Ta, Tc | Operating<br>Temperature                   | 0 to +70 <sup>(4)</sup> (Ambient) 0 to +90 <sup>(5)</sup> (Case) | °C   |

| TBIAS  | Case Temperature<br>Under Bias             | -55 to +125 <sup>(4)</sup><br>0 to +90 <sup>(5)</sup>            | °C   |

| Tstg   | Storage<br>Temperature                     | -55 to +125                                                      | °C   |

| lin    | Input Voltage                              | -0.5 to +7.0                                                     | V    |

#### NOTE:

- Stresses greater than those listed under ABSOLUTE MAXIMUM RAT-INGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- VIN minimum = -3.0V for pulse width less than 15ns.

VIN should not exceed VCC +0.5 Volts.

- Not more than one output should be shorted at a time. Duration of the short should not exceed 30 seconds.

- 4. 16-33MHz only.

- 5. 40MHz only.

### **AC TEST CONDITIONS**

| Symbol | Parameter          | Min. | Max. | Unit |

|--------|--------------------|------|------|------|

| Vін    | Input HIGH Voltage | 3.0  |      | ٧    |

| VIL    | Input LOW Voltage  |      | 0.4  | ٧    |

| ViHs   | Input HIGH Voltage | 3.5  | _    | ٧    |

| Vils   | Input LOW Voltage  |      | 0.4  | ٧    |

| Vінс   | Input HIGH Voltage | 4.0  | _    | ٧    |

| Vilc   | Input LOW Voltage  |      | 0.4  | ٧    |

2873 tbl 05

2873 tb! 04

# RECOMMENDED OPERATING TEMPERATURE AND SUPPLY VOLTAGE

| Grade                  | Temperature               | GND | Vcc     |

|------------------------|---------------------------|-----|---------|

| Commercial<br>16-33MHz | 0°C to +70°C<br>(Ambient) | ov  | 5.0 ±5% |

| Commercial<br>40MHz    | 0°C to +90°C<br>(Case)    | ov  | 5.0 ±5% |

2873 tbl 06

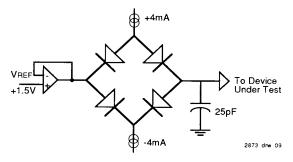

#### **OUTPUT LOADING FOR AC TESTING**

### DC ELECTRICAL CHARACTERISTICS FOR IDT79R3010A COMMERCIAL TEMPERATURE RANGE (TA = 0°C to + 70°C, Vcc = + 5.0 V ± 5%)

|             |                                   |                        | 16.6 | 7 MHz | 20.0     | MHz  | Unit |

|-------------|-----------------------------------|------------------------|------|-------|----------|------|------|

| Symbol      | Parameter                         | Test Conditions        | Min. | Max.  | Min.     | Max. | Unit |

| Vон         | Output HIGH Voltage               | Vcc = Min, Ioн = -4mA  | 3.5  | _     | 3.5      | _    | ٧    |

| <b>V</b> OL | Output LOW Voltage                | Vcc = Min, loL = 4mA   | _    | 0.4   | T -      | 0.4  | V    |

| VOLFP       | Output LOW Voltage <sup>(5)</sup> | Vcc = Min, loL = 1.5mA | _    | 0.5   | _        | 0.5  | V    |

| Vін         | Input HIGH Voltage <sup>(6)</sup> |                        | 2.0  | _     | 2.0      | _    | V    |

| VIL         | Input LOW Voltage <sup>(1)</sup>  |                        | _    | 0.8   | -        | 0.8  | V    |

| ViHs        | Input HIGH Voltage(2,6)           |                        | 3.0  | _     | 3.0      |      | V    |

| VILS        | Input LOW Voltage(1,2)            |                        | _    | 0.4   | <u> </u> | 0.4  | V    |

| Vinc        | Input HIGH Voltage(4,6)           |                        | 4.0  | _     | 4.0      |      | V    |

| VILC        | Input LOW Voltage(1,4)            |                        | _    | 0.4   |          | 0.4  | V    |

| CIN         | Input Capacitance <sup>(7)</sup>  |                        | -    | 10    | T -      | 10   | pF   |

| Соит        | Output Capacitance <sup>(7)</sup> |                        | l –  | 10    | _        | 10   | pF   |

| lcc         | Operating Current                 | Vcc = 5.0V, Ta = 70°C  |      | 525   | T -      | 600  | mA   |

| ₩Н          | Input HIGH Leakage <sup>(3)</sup> | VIH = VCC              | _    | 100   | 1 –      | 100  | μА   |

| lıL         | Input LOW Leakage <sup>(3)</sup>  | VIL = GND              | -100 | _     | -100     | T    | μА   |

| loz         | Output Tri-state Leakage          | VoH = 2.4V, VoL = 0.5V | -100 | 100   | -100     | 100  | μА   |

2873 tbl 07

### DC ELECTRICAL CHARACTERISTICS FOR IDT79R3010AE **COMMERCIAL TEMPERATURE RANGE** (TA = $0^{\circ}$ C to + $70^{\circ}$ C, Vcc = + $5.0 \text{ V} \pm 5\%$ )

|             |                                     |                        | 25.0     | 25.0 MHz |      | 33.33 MHz |      |

|-------------|-------------------------------------|------------------------|----------|----------|------|-----------|------|

| Symbol      | Parameter                           | Test Conditions        | Min.     | Max.     | Min. | Max.      | Unit |

| Vон         | Output HIGH Voltage                 | Vcc = Min, IoH = -4mA  | 3.5      | _        | 3.5  | _         | V    |

| <b>V</b> OL | Output LOW Voltage                  | Vcc = Min, lot = 4mA   | _        | 0.4      | _    | 0.4       | V    |

| VOLFP       | Output LOW Voltage <sup>(5)</sup>   | Vcc = Min, lot = 1.5mA |          | 0.5      | T -  | 0.5       | V    |

| ViH         | Input HIGH Voltage <sup>(6)</sup>   |                        | 2.0      | _        | 2.0  | _         | V    |

| VIL         | Input LOW Voltage <sup>(1)</sup>    |                        |          | 0.8      | _    | 0.8       | V    |

| Vins        | Input HIGH Voltage(2,6)             |                        | 3.0      | _        | 3.0  | _         | V    |

| Vils        | Input LOW Voltage(1,2)              |                        | _        | 0.4      | _    | 0.4       | V    |

| ViHC        | Input HIGH Voltage <sup>(4,6)</sup> |                        | 4.0      | T -      | 4.0  | _         | V    |

| VILC        | Input LOW Voltage(1,4)              |                        | <u> </u> | 0.4      | _    | 0.4       | V    |

| Cin         | Input Capacitance <sup>(7)</sup>    |                        | l –      | 10       |      | 10        | pF   |

| Соит        | Output Capacitance <sup>(7)</sup>   |                        |          | 10       | _    | 10        | pF   |

| lcc         | Operating Current                   | Vcc = 5.0V, Ta = 70°C  |          | 650      |      | 700       | mA   |

| lін         | Input HIGH Leakage <sup>(3)</sup>   | VIH = VCC              | _        | 100      | _    | 100       | μА   |

| li∟         | Input LOW Leakage <sup>(3)</sup>    | VIL = GND              | -100     | _        | -100 |           | μА   |

| loz         | Output Tri-state Leakage            | VoH = 2.4V, VoL = 0.5V | -100     | 100      | -100 | 100       | μА   |

- 1. VIL Min. = -3.0V for pulse width less than 15ns. VIL should not fall below -0.5V for larger periods.

- 2. VIHs and VILs apply to Clk2xSys, Clk2xSmp, Clk2xRd, Clk2xPhi, FpSysin, FpSync and Reset.

- These parameters do not apply to the clock inputs.

VIHC and VILC apply to Run, PIIOn and Exception.

- 5. VOLFP applies to the FPPresent pin only.

- 6. ViH and ViHs should not be held above Vcc + 0.5V.

- 7. Guaranteed by design.

6.1

2873 tbl 08

## DC ELECTRICAL CHARACTERISTICS FOR IDT79R3010AE

COMMERCIAL TEMPERATURE RANGE (Tc = 0°C to + 90°C, Vcc = + 5.0 V ± 5%)

|             |                                   |                        | 40   | MHz  | T., ., |

|-------------|-----------------------------------|------------------------|------|------|--------|

| Symbol      | Parameter                         | Test Conditions        | Min. | Max. | Unit   |

| <b>V</b> OH | Output HIGH Voltage               | Vcc = Min, IoH = -4mA  | 3.5  | _    | V      |

| <b>V</b> OL | Output LOW Voltage                | Vcc = Min, lot = 4mA   | _    | 0.4  | V      |

| VOLFP       | Output LOW Voltage <sup>(5)</sup> | Vcc = Min, lot = 1.5mA | _    | 0.5  | V      |

| Vін         | Input HIGH Voltage <sup>(6)</sup> |                        | 2.0  | _    | V      |

| VIL         | Input LOW Voltage <sup>(1)</sup>  |                        | _    | 0.8  | V      |

| Vins        | Input HIGH Voltage(2,6)           |                        | 3.0  | _    | V      |

| VILS        | Input LOW Voltage(1,2)            |                        |      | 0.4  | V      |

| Vihc        | Input HIGH Voltage(4,6)           |                        | 4.0  | _    | V      |

| VILC        | Input LOW Voltage(1,4)            |                        | _    | 0.4  | V      |

| Cin         | Input Capacitance <sup>(7)</sup>  |                        | _    | 10   | pF     |

| Соит        | Output Capacitance <sup>(7)</sup> |                        | _    | 10   | pF     |

| Icc         | Operating Current                 | Vcc = 5.0V, Tc = 90°C  |      | 750  | mA     |

| lн          | Input HIGH Leakage <sup>(3)</sup> | VIH = VCC              | _    | 100  | μА     |

| h∟          | Input LOW Leakage <sup>(3)</sup>  | VIL = GND              | -100 | _    | μА     |

| loz         | Output Tri-state Leakage          | VoH = 2.4V, VoL = 0.5V | -100 | 100  | μА     |

2873 tbl 09

#### NOTES:

- 1. V<sub>IL</sub> Min. = -3.0V for pulse width less than 15ns. V<sub>IL</sub> should not fall below -0.5V for larger periods. 2. V<sub>IHS</sub> and V<sub>ILS</sub> apply to Clk2xSys, Clk2xSmp, Clk2xRd, Clk2xPhi, FpSysin, FpSync and Reset.

- These parameters do not apply to the clock inputs.

VIHC and VILC apply to Run, PIIOn and Exception.

- 5. VOLFP applies to the FPPresent pin only.

- 6. Vih and Vihs should not be held above Vcc + 0.5V.

- 7. Guaranteed by design.

#### AC ELECTRICAL CHARACTERISTICS FOR IDT79R3010A<sup>(1, 3)</sup> **COMMERCIAL TEMPERATURE RANGE** (TA = $0^{\circ}$ C to +70°C, Vcc = +5.0V ± 5%)

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 16.67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7 MHz        | 20.0                |                    |           |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------|--------------------|-----------|

| Parameter                                     | Test Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Min.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Max.         | Min.                | Max.               | Unit      |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <del></del>  | <b>4</b>            |                    |           |

| Input Clock HIGH <sup>(2)</sup>               | Note 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _            | 10                  | _                  | ns        |

| Input Clock LOW(2)                            | Note 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _            | 10                  | _                  | ns        |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1000         | 25                  | 1000               | ns        |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              | _                   |                    | ns        |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |                     |                    | ns        |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | tcyc/4       | 7.0                 | 1 tcyc/4           | ns        |

|                                               | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | T            | <u> </u>            | 1 00               | T         |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <del> </del> | <del></del>         | <del></del>        | ns        |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              | _                   | <del></del>        | ns        |

|                                               | Load= 25pF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3.0          |                     | 3.0                | ns        |

| Reset Set-up                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _            | 15                  |                    | ns        |

| Data Set-up                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              | 8.0                 | I –                | ns        |

| Data Hold <sup>(3)</sup>                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _            | 2.5                 | _                  | ns        |

| Fp Condition                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 35           | _                   | 30                 | ns        |

| Fp Busy                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 15           | T -                 | 13                 | ns        |

| Fp Interrupt                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40           |                     | 35                 | ns        |

| Fp Move To                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 35           | I – –               | 30                 | ns        |

| Exception Set-up (Run Cycle)                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <u> </u>     | 12                  | <u> </u>           | ns        |

| Exception Set-up (Stall Cycle)                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _            | 10                  | _                  | ns        |

| Exception Hold                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | T -          | 0                   |                    | ns        |

| Run Set-up                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I -          | 15                  | _                  | ns        |

| Run Hold                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <u> </u>     | -2.0                | _                  | ns        |

| Stall Set-up                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _            | 10                  | _                  | ns        |

| Stall Hold                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -            | -2.0                | _                  | ns        |

| nitialization                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •            | •                   |                    |           |

| Reset Timing, Phase-lock on <sup>(4, 5)</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              | 3000                |                    | Тсус      |

| Reset Timing, Phase-lock off <sup>(5)</sup>   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I -          | 128                 | _                  | Tcyc      |

| ive Load Deration                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |                     | -                  |           |

| Load Derate <sup>(6)</sup>                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2.0          | 0.5                 | 1.0                | ns/25pi   |

|                                               | Input Clock HIGH <sup>(2)</sup> Input Clock LOW <sup>(2)</sup> Input Clock Period Clk2xSys to Clk2xSmp <sup>(5)</sup> Clk2xSmp to Clk2xRd <sup>(5)</sup> Clk2xSmp to Clk2xPhi <sup>(5)</sup> Paramters  Data Enable <sup>(3)</sup> Data Disable <sup>(3)</sup> Data Valid Reset Set-up Data Set-up Data Hold <sup>(3)</sup> Fp Condition Fp Busy Fp Interrupt Fp Move To Exception Set-up (Run Cycle) Exception Set-up (Stall Cycle) Exception Hold Run Set-up Stall Hold hitialization Reset Timing, Phase-lock on <sup>(4, 5)</sup> Reset Timing, Phase-lock off <sup>(5)</sup> Ive Load Deration | Input Clock HIGH <sup>(2)</sup> Note 7  Input Clock LOW <sup>(2)</sup> Note 7  Input Clock Period Clk2xSmy to Clk2xSmp <sup>(5)</sup> Clk2xSmy to Clk2xPhi <sup>(5)</sup> Paramters  Data Enable <sup>(3)</sup> Data Disable <sup>(3)</sup> Data Valid Load= 25pF  Reset Set-up Data Set-up Data Hold <sup>(3)</sup> Fp Condition Fp Busy Fp Interrupt Fp Move To Exception Set-up (Run Cycle) Exception Set-up (Stall Cycle) Exception Hold Run Set-up Stall Hold Stall Set-up Stall Hold Initialization Reset Timing, Phase-lock off <sup>(5)</sup> Ive Load Deration | Parameter    | Input Clock HIGH(2) | Parameter   Note 7 | Parameter |

- 1. All timings are referenced to 1.5V.

- 2. The clock parameters apply to all four 2xClocks: Clk2xSys, Clk2xSmp, Clk2xRd, and Clk2xPhi.

- 3. This parameter is guaranteed by design.

4. With PIIOn asserted, Reset must be asserted for the longer of 3000 clock cycles or 200 microseconds.

- 5. Toyc is one CPU clock cycle (two cycles of a 2x clock).

- 6. No two signals on a given device will derate for a given load by a difference greater than 15%.

- 7. Clock transition time < 5ns.

# AC ELECTRICAL CHARACTERISTICS FOR IDT79R3010AE<sup>(1, 3)</sup> COMMERCIAL TEMPERATURE RANGE (TA = $0^{\circ}$ C to +70°C, Vcc = +5.0V ± 5%)

|                          |                                             | **              | 25.0     | MHz      | 33.3 | 3 MHz  |         |

|--------------------------|---------------------------------------------|-----------------|----------|----------|------|--------|---------|

| Symbol                   | Parameter                                   | Test Conditions | Min.     | Max.     | Min. | Max.   | Unit    |

| Clock                    |                                             | •               |          |          | •    |        |         |

| TCkHigh                  | Input Clock High <sup>(2)</sup>             | Note 7          | 8.0      |          | 6.0  | _      | ns      |

| TCkLow                   | Input Clock Low(2)                          | Note 7          | 8.0      | _        | 6.0  | _      | ns      |

| TCkP                     | Input Clock Period                          |                 | 20       | 1000     | 15   | 1000   | ns      |

|                          | Clk2xSys to Clk2XSmp <sup>(5)</sup>         |                 | 0        | tcyc/4   | 0    | tcyc/4 | ns      |

|                          | Clk2xSmp to Clk2xRd <sup>(5)</sup>          |                 | 0        | tcyc/4   | 0    | tcyc/4 | ns      |

|                          | Clk2xSmp to Clk2xPhi(5)                     | l               | 5.0      | tcyc/4   | 3.5  | tcyc/4 | ns      |

|                          | Paramters                                   |                 |          |          |      |        |         |

| TDEn                     | Data Enable <sup>(3)</sup>                  |                 | <u> </u> | -1.5     | _    | -1.0   | ns      |

| TDDIs                    | Data Disable <sup>(3)</sup>                 |                 |          | -0.5     | _    | -0.5   | ns      |

| TDVal                    | Data Valid                                  | Load= 25pF      |          | 2.0      |      | 2.0    | ns      |

| TRSDS                    | Reset Set-up                                |                 | 10       |          | 10   | _      | ns      |

| Tos                      | Data Set-up                                 |                 | 6.0      | _        | 4.5  |        | ns      |

| TDH                      | Data Hold <sup>(3)</sup>                    |                 | -2.5     | _        | -2.5 | _      | ns      |

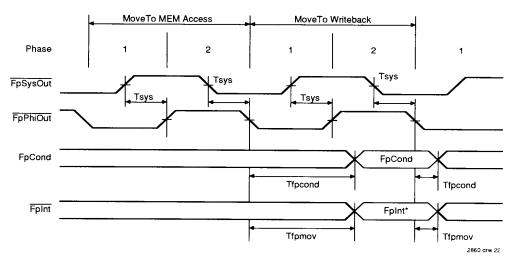

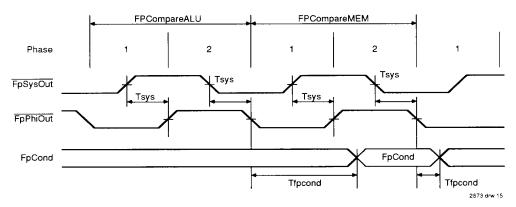

| TFpCond                  | Fp Condition                                |                 | _        | 25       | _    | 17     | ns      |

| TFpBusy                  | Fp Busy                                     |                 | _        | 10       | _    | 7.0    | ns      |

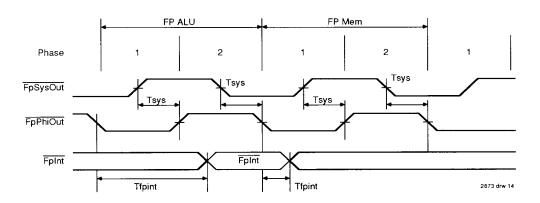

| TFpInt                   | Fp Interrupt                                |                 |          | 25       | _    | 18     | ns      |

| Тғрмоч                   | Fp Move To                                  |                 |          | 25       | _    | 16     | ns      |

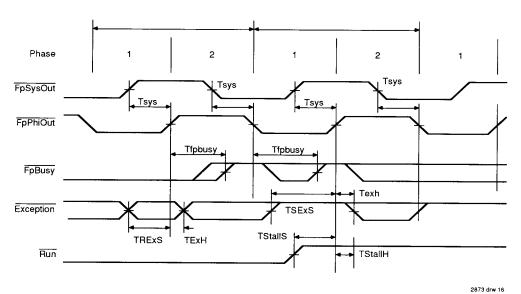

| TRExS                    | Exception Set-up (Run Cycle)                |                 | 11       | <b>—</b> | 9.0  |        | ns      |

| Tsexs                    | Exception Set-up (Stall Cycle)              |                 | 8.0      |          | 6.5  | _      | ns      |

| TExH                     | Exception Hold                              |                 | 0        | _        | 0    |        | ns      |

| TRunS                    | Run Set-up                                  |                 | 15       | L        | 12.5 |        | ns      |

| TRunH                    | Run Hold                                    |                 | -2.0     |          | -1.5 |        | ns      |

| TStallS                  | Stall Set-up                                |                 | 9.0      | _        | 7.0  | _      | ns      |

| TStallH                  | Stall Hold                                  |                 | -2.0     | 1        | -2.0 | _      | ns      |

| Reset in                 | nitialization                               |                 |          |          |      |        |         |

| TrstPLL.                 | Reset Timing, Phase-lock on(4, 5)           |                 | 3000     |          | 3000 | _      | Тсус    |

| Trst                     | Reset Timing, Phase-lock off <sup>(5)</sup> |                 | 128      |          | 128  | -      | Тсус    |

| Capacit                  | tive Load Deration                          |                 |          |          |      |        |         |

| CLD                      | Load Derate <sup>(6)</sup>                  |                 | 0.5      | 1.0      | 0.5  | 1.0    | ns/25pf |