## INTRODUCTION

The KA567 is monolithic phase locked loop system designed to provide a saturated transistor switch to GND, when an input signal is present within the passband. External components are used to independently set center frequency bandwidth and output delay.

## **FEATURES**

- Wide frequency range (0.01Hz ~ 500KHz).

Bandwidth adjustable from 0 to 14%.

- . Logic compatible output with 100mA current sinking capability.

- Inherent immunity to false signals.

- High rejection of out-of-band signals and noise.

- Frequency range adjustable over 20:1 range by an external resistor.

# **APPLICATIONS**

- · Touch Tone Decoder.

- Wireless Intercom.

- · Communications paging decoders.

- Frequency monitoring and control.

- Ultrasonic controls. (remote TV etc.)

- · Carrier current remote controls.

- · Precision oscillator.

# ORDERING INFORMATION

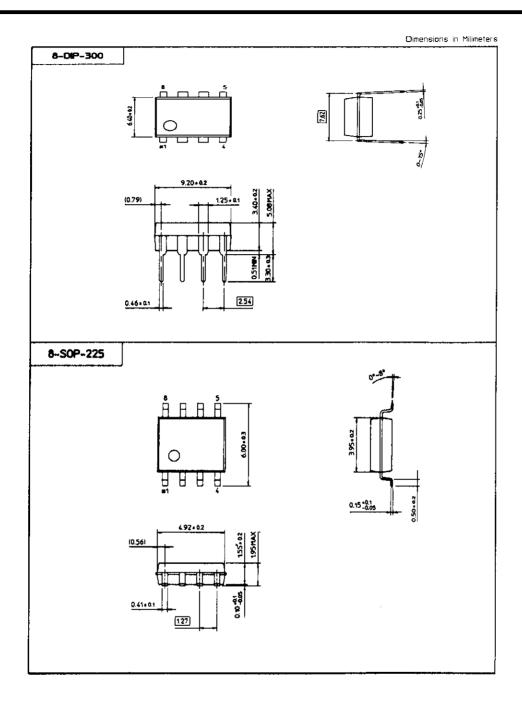

| Device | Package   | Operating Temperature |

|--------|-----------|-----------------------|

| KA567  | 8-DIP-300 | 0~+70℃                |

| KA567D | 8-SOP-225 | 0100                  |

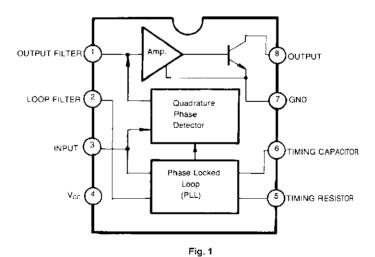

## **BLOCK DIAGRAM**

## ABSOLUTE MAXIMUM RATINGS (Ta = 25°C)

| Characteristic        | Symbol           | Value                       | Unit |  |

|-----------------------|------------------|-----------------------------|------|--|

| Supply Voltage        | Vcc              | 10                          | V    |  |

| Input Voltage         | V <sub>I</sub>   | -10 ~ V <sub>CC</sub> + 0.5 | V    |  |

| Output Voltage        | V <sub>o</sub>   | 15                          | V    |  |

| Power Dissipation     | P□               | 300                         | m₩   |  |

| Operating Temperature | Tope             | 0~+70                       | ొ    |  |

| Storage Temperature   | T <sub>STG</sub> | - 65 ~ + 150                | τ    |  |

# **ELECTRICAL CHARACTERISTICS**

( $V_{CC}$  = 5.0V, Ta = 25°C unless otherwise specified)

| Characteristic                | Symbol                            | Test Conditions                                   | Min  | Тур   | Max | Unit    |

|-------------------------------|-----------------------------------|---------------------------------------------------|------|-------|-----|---------|

| Operating Voltage Range       | V <sub>cc</sub>                   |                                                   | 4.75 | 5.0   | 9.0 | ٧       |

| Operating Current Quiescent   | Icc (0)                           | R <sub>1</sub> = 20K                              |      | 7     | 10  | mA      |

| Operating Current Activated   | Icc (A)                           | TIL LOTT                                          |      | 12    | 15  | mA      |

| Quiescent Power Dissipation   | P <sub>D (Q)</sub>                |                                                   |      | 35    |     | m₩      |

| High Center Frequency         | f <sub>HC</sub>                   | R <sub>L</sub> = 20K                              | 100  | 500   |     | KHz     |

| Center Frequency Stability    | f <sub>ST</sub>                   | 0°C to 70°C                                       |      | ⊥60   |     | ppm/fC  |

| Center Frequency Shift        | ∆f <sub>c</sub> /∆V <sub>cc</sub> |                                                   |      | 0.7   | 2   | %/√     |

| With Supply Voltage           |                                   |                                                   |      |       |     |         |

| Largest Detection Bandwidth   | BW <sub>DET</sub>                 |                                                   | 10   | 14    | 18  | % of fo |

| Largest Detection B.W Skew    | BW <sub>DET</sub>                 |                                                   |      | 2     | 3   | % of fo |

| Largest Detection Bandwidth   | ∆BW/∆V <sub>oc</sub>              |                                                   |      | ⊥2    | _5  | %/∨     |

| Variation With Supply Voltage |                                   |                                                   |      |       |     |         |

| Largest Detection Bandwidth   | _∆BW/∆T                           |                                                   |      | 0.1   |     | %/℃     |

| Variation With Temperature    |                                   |                                                   |      |       |     |         |

| Input Resistance              | Rı                                |                                                   |      | 20    |     | Kohm    |

| Smallest Detectable           | V <sub>L(SMALL)</sub>             | $I_L = 100 \text{mA}$ , fi = fo                   |      | 20    | 25  | mVrms   |

| Input Voltage                 |                                   |                                                   |      |       |     |         |

| Largest No Output             | V <sub>I (LARGE)</sub>            |                                                   | 10   | 15    |     | mVrms   |

| Input Voltage                 |                                   |                                                   |      |       |     |         |

| Greatest Simultaneous         | S1/SD                             | R <sub>L</sub> = 20K                              |      | +6    |     | dB      |

| Outband Signal To Inband      |                                   | $V_{IN} = 300 \text{mV}_{rms}$                    |      |       |     |         |

| Signal Ratio                  |                                   | fi = fo = 100KHz                                  |      |       |     |         |

| Minimum Input Signal to       | S2/SD                             | fi <sub>1</sub> = 140KHz                          |      | -6    |     | dB      |

| Wideband Noise Ratio          |                                   | fi <sub>2</sub> = 60KHZ                           |      |       |     |         |

| Fastest On-Off Cycling Rate   | C <sub>R (ON-OFF)</sub>           | R <sub>L</sub> = 20K                              |      | fo/20 |     |         |

| Output Leakage Current        | I <sub>O (LKG)</sub>              | $V_{IN} = 25 \text{mV}_{ms}$                      |      | 0.01  | 25  | μA      |

| Output Saturation Voltage     | V <sub>SAT1</sub>                 | I <sub>L</sub> = 300mA, V <sub>IN</sub> = 25mVrms |      | 0.2   | 0.4 | ٧       |

| Output Saturation Voltage     | V <sub>SAT2</sub>                 | $I_L$ = 100mA, $V_{IN}$ = 25mVrms                 |      | 0.6   | 1.0 | ٧       |

| Output Fall Time              | t <sub>F</sub>                    | R <sub>L</sub> = 50                               |      | 30    |     | nS      |

| Output Rise Time              | t <sub>R</sub>                    | R <sub>L</sub> = 50                               |      | 150   |     | nS      |

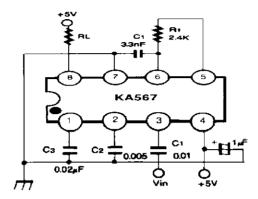

## **TEST CIRCUIT**

fi = 100KHz

Note: Adjust for fo = 100KHz

Fig. 2

# APPLICATION INFORMATION CIRCUIT DESCRIPTION

The KA567 monolithic tone decoder consists of a phase detector, low pass filter, and current controlled oscillator which comprise the basic phase-locked loop, plus an additional low pass filter and quadrature detector enabling detection on in-band signals. The device has a normally high open collector output capable of sinking 100 mA.

The input signal is applied to Pin 3 (20  $\,\mathrm{k}\Omega$  nominal input resistance). Free running frequency is controlled by an RC. network at Pin 5 and 6 and can typically reach 500 KHz. A capacitor on Pin 1 serves as the output filter and eliminates out-of-band triggering. PLL filtering is accomplished with a capacitor on Pin 2; bandwidth and skew are also dependant upon the circultry here. Bandwidth is adjustable from 0% to 14% of the center frequency. Pin 4 is  $\pm V_{CC}$  (4.75 to 9V norminal, 10V maximum); Pin 7 is ground; and Pin 8 is a open collector output, pulling low when an inband signal triggers the device.

## **DEFINITION OF KA567 PARAMETERS**

## 1. CENTER FREQUENCY fo

$f_O$  is the free-running frequency of the  $C_L$  controlled oscillator with no input signal. If is determined by resistor  $R_1$  between pins 5 and 6, and capacitor  $C_1$  from pin 6 to ground  $f_O$  can be approximated by

$$f_0 \approx \frac{1}{R_1C_1}$$

where R<sub>1</sub> is in ohms and C<sub>1</sub> is in farads.

## 2. LARGEST DETECTION BANDWIDTH

The largest detection bandwidth is the largest frequency range within which an input signal above the threshold voltage will cause a logical zero state at the output. The maximum detection bandwidth corresponds to the lock range of the PLL.

CD-ROM(Edition 3.0) This Data Sheet is subject to change without notice.

(C) 1996 Samsung Electronics Printed in Korea.

#### 3. DETECTION BANDWIDTH (BW)

The detection bandwidth is the frequency range centered about  $f_0$ , within which an input signal larger than the threshold voltage (typically 20mVrms) will cause a logic zero state at the output. The detection bandwidth corresponds to the capture range of the PLL and is determined by the low-pass bandwidth filter. The bandwidth of the filter, as a percent of  $f_0$ , can be determined by the approximation

BW = 1070

$$\sqrt{\frac{V_1}{f_0 C_2}}$$

where  $V_{i_1}$  is the input signal in volts, rms, and  $C_2$  is the capacitance at pin 2 in  $\ensuremath{\it \mu} F$ .

#### 4. DETECTION BAND SKEW

The detection band skew is a measure of how accurately the largest detection band is centered about the center frequency,  $f_O$ . It is defined as  $(f_{max} + f_{min} - 2f_O)/f_O$ , where  $f_{max}$  and  $f_{min}$ , are the frequencies corresponding to the edges of the detection band. If necessary, the detection band skew can be reduced to zero by an optional centering adjustment.

## PIN DESCRIPTION

## 1. OUTPUT FILTER-C3 (Pin 1)

Capacitor  $C_3$  connected from pin 1 to ground forms a simple low-pass post detection filter to eliminate spurious outputs due to out-of-band signals. The time constant of the filter can be expressed as  $T_3 = R_3C_3$ , where  $R_3$  (4.7k $\hat{\omega}$ ) is the internal impedance at pin 1.

The precise value of  $C_3$  is not entical for most applications. To eliminate the possibility of false triggering by spurious signals, it is recommended that  $C_3$  be  $\geq 2$   $C_2$ , where  $C_2$  is the loop filter capacitance at pin 2.

If the value of  $C_3$  becomes too large, the turn-on or turn-off time of the output stage will be delayed until the voltage change across  $C_3$  reaches the threshold voltage. In certain applications, the delay may be desirable as a means of suppressing spurious outputs. Conversely, if the value of  $C_3$  is too small, the beat rate at the output of the quadrature detector may cause a false logic level change at the output. (Pin 8)

The average voltage (during lock) at pin 1 is a function of the inband input amplitude in accordance with the given transfer characteristic.

## 2. LOOP FILTER-C<sub>2</sub> (Pin 2)

Capacitor  $C_2$  connected from pin 2 to ground serves as a single pole, low-pass filter for the PLL portion of the KA567. The filter time constant is given by  $T_2 = R_2C_2$ , where  $R_2(10 \text{ k}\Omega)$  is the impedance at pin 2.

The selection of  $C_2$  is determined by the detection bandwidth requirements. For additional information see the section on "Definition of KA567 Parameters."

The voltage at pin 2, the phase detector output, is a linear function of frequency over the range of 0.95 to 1.05  $f_0$ , with a slope of approximately 20 mV/% frequency deviation.

## 3. INPUT (Pin 3)

The input signal is applied to pin 3 through a coupling capacitor. This terminal is internally biased at a dc level 2 volts above ground, and has an input impedance level of approximately 20k\(\text{\text{\text{d}}}\).

## 4. TIMING RESISTOR R1 AND CAPACITOR C1 (Pins 5 and 6)

The center frequency of the decoder is set by resistor  $R_1$  between pins 5 and 6, and capacitor  $C_1$  from pin 6 to ground, as shown in Figure 2.

Pin 5 is the oscillator squarewave output which has a magnitude of approximately  $V_{\rm CC}=1.4V$  and an average dc level of  $V_{\rm CC}/2$ . A 1  $~\rm k\Omega$  load may be driven from this point. The voltage at pin 6 is an exponential triangle waveform with a peak-to-peak amplitude of 1 volt and an average dc level of  $V_{\rm CC}/2$ . Only high impedance loads should be connected to pin 6 to avoid disturbing the temperature stability or duty cycle of the oscillator.

#### 5. LOGIC OUTPUT (Pin 8)

Terminal 8 provides a binary logic output when an input signal is present within the pass-band of the decoder. The logic output is an uncommitted, "base-collector" power transistor capable of switching high current loads. The current level at the output is determined by an external load resistor  $R_L$ , connected trom pin 8 to the positive supply. When an in-band signal is present, the output transistor at pin 8 saturates with a collector voltage less than 1 volt (typically 0.6V) at full rated current of 100 mA. If large output voltage swings are needed,  $R_L$  can be connected to a supply voltage, V+, higher than the  $V_{CC}$  supply. For safe operation, V+  $\stackrel{<}{\sim}$  20 volts.

#### OPERATING INSTRUCTIONS

## **SELECTION OF EXTERNAL COMPONENTS**

A typical connection diagram for the KA567 is shown in Figure 2. For most applications, the following procedure will be sufficient for determination of the external components R1, C1, C2, and C3.

- 1.  $R_1$  and  $C_1$  should be selected for the desired center frequency by the expression  $f_0 = 1/R_1C_1$ . For optimum temperature stability, R<sub>1</sub> should be selected such that 2kΩ, and the R<sub>1</sub>C<sub>1</sub> product should have sufficient stability over the projected operating temperature range.

- 2. C2 is low-pass capacitor. If the input amplitude variation is known, the required  $f_0C_2$  product can be found to give the desired bandwidth. Capacitor C2 connected from pin 2 to ground serves as a single pole, low-pass filter for the PLL portion of the KA567

- 3. Capacitor C<sub>3</sub> sets the band edge of the low-pass filter which attenuates frequencies outside of the detection band and thereby eliminates spurious outputs. If C3 is too small, frequencies adjacent to the detection band may switch the output stage off and on at the beat frequency, or the output may pulse off and on during the turn-on transient, a typical minimum value of C3 is 2 C2.

Conversely, if C<sub>3</sub> is too large, turn-on and turn-off of the output stage will be delayed until the voltage across C<sub>3</sub> passes the threshold value.

## PRINCIPLE OF OPERATION

solely by the foCo product.

The KA567 is a frequency selective tone decoder system based on the phase-locked loop (PLL) principle, the system is comprised of a phase-locked loop, a quadrature AM detector, a voltage comparator, and an output logic driver. The four sections are internally interconnected as shown in Figure 1.

When an input tone is present within the pass-band of the circuit, the PLL synchronizes or "locks" on the input signal The quadrature detector serves as a lock indicator: when the PLL is locked on an input signal, the do voltage at the output of the detector is shifted. This do level shift is then converted to an output logic pulse by the amplifier and logic driver. The logic driver is a "bare collector" transistor stage capable of switching 100 mA loads.

The logic output at pin 8 is normally in a "high" state, until a tone that is within the capture range of the decoder is present at the input. When the decoder is locked on an input signal, the logic output at pin 8 goes to a "low" state.

The center frequency of the detector is set by the free-running frequency of the current-controlled oscillator in the PLL. This free-running frequency, fo, is determined by the selection of R<sub>1</sub> and C<sub>1</sub> connected to pins 5 and 6, as shown in Figure 3. The detection bandwidth is determined by the size of the PLL filter capacitor,  $C_2$ ; and the output response speed is controlled by the output filter capacitor, C3.

CD-ROM(Edition 3.0) This Data Sheet is subject to change without notice.

(C) 1996 Samsung Electronics Printed in Korea.