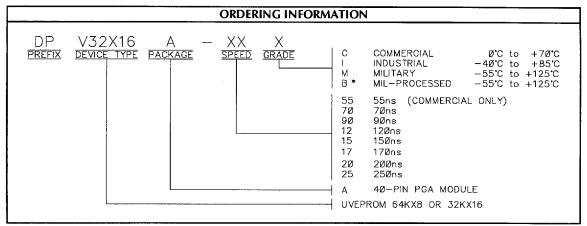

# 0.5 Megabit UVEPROM

DPV32X16A

#### DESCRIPTION:

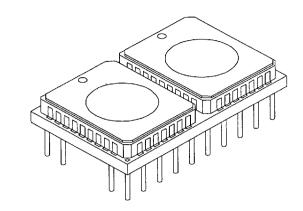

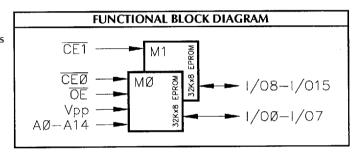

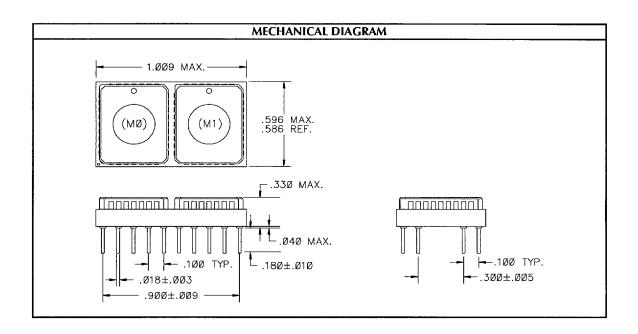

The DPV32X16A is a 40-pin Pin Grid Array (PGA) consisting of two 32K X 8 UVEPROM devices in ceramic LCC packages surface mounted on a co-fired ceramic substrate with matched thermal coefficients. The LCC's are mounted in a pattern resulting in the smallest possible module outline.

The pins have been arranged around a central 0.3" gap which can accommodate a heat rail, if desired. In this central gap is a cavity containing two 0.1 µf decoupling capacitors.

# **FEATURES:**

- Organizations Available: 64K x 8 or 32K x 16

- Access Times: 55\*, 70, 90, 120, 150, 170, 200, 250ns

- Fully Static Operation

- No clock or refresh required

- Programming Voltage 13.0 Vdc

- Simple Programming Requirements

- Three-State Outputs

- High Speed Programming Algorithm (1.0ms Pulses Typ.)

- Common Data Inputs and Outputs

- TTL-compatible Inputs and Outputs

- 40-Pin PGA (Pin Grid Array) Package

- \* Commercial only.

| P            | IN NAMES            |

|--------------|---------------------|

| A0 - A14     | Address Inputs      |

| I/O0 - I/O15 | Data In/Out         |

| CEO, CE1     | Chip Enables        |

| <u>OE</u>    | Output Enable       |

| $V_{DD}$     | Power (+ 5V)        |

| Vss          | Ground              |

| VPP          | Programming Voltage |

| N.C.         | No Connect          |

|      |            |       |    | PIN-OUT D  | DIAGRA | ٩M   |    |       |    |     |

|------|------------|-------|----|------------|--------|------|----|-------|----|-----|

|      | (TOP VIEW) |       |    |            |        |      |    |       |    |     |

| CEØ  | 1          | 1/06  | 11 | 1 11       | 21)    | (31) | 21 | 1/07  | 31 | VDD |

| Α9   | 2          | 1/05  | 12 | 2 12       | 22     | 32   | 22 | 1/02  | 32 | ΑØ  |

| A1Ø  | 3          | 1/04  | 13 | 3 3        | 23     | 33   | 23 | 1/01  | 33 | A1  |

| A11  | 4          | 1/03  | 14 | 4 4        | 24     | 34   | 24 | 1/00  | 34 | A2  |

| A12  | 5          | ŌĒ    | 15 | (5) (15)   | 25     | 35   | 25 | А3    | 35 | A4  |

| A13  | 6          | A14   | 16 | (B) (B)    | 26     | 38   | 26 | N.C.  | 36 | A5  |

| VPP  | 7          | 1/014 | 17 | <b>7 0</b> | 27     | 37   | 27 | 1/015 | 37 | A6  |

| N.C. | 8          | 1/013 | 18 | 8 18       | 28     | 38   | 28 | 1/01Ø | 38 | Α7  |

| N.C. | 9          | 1/012 | 19 | 9 19       | 29     | 39   | 29 | 1/09  | 39 | A8  |

| VSS  | 1Ø         | 1/011 | 2Ø | 19 29      | 39     | 40   | 30 | 1/08  | 4Ø | CE1 |

|      |            |       |    |            |        |      |    |       |    |     |

|      |            |       |    |            |        |      |    |       |    |     |

2759415 0001379 228

| ABSOLUTE MAXIMUM RATINGS <sup>1</sup> |                             |                 |      |  |  |  |  |  |

|---------------------------------------|-----------------------------|-----------------|------|--|--|--|--|--|

| Symbol                                | Parameter                   | Value           | Unit |  |  |  |  |  |

| TstG                                  | Storage Temperature         | -65 to +125     | °C   |  |  |  |  |  |

| TBIAS                                 | Temperature Under Bias      | -55 to +125     | °C   |  |  |  |  |  |

| $V_{DD}$                              | Supply Voltage <sup>2</sup> | -0.5 to +7.0    | V    |  |  |  |  |  |

| V <sub>1/O</sub>                      | Input/Output Voltage 2      | -0.5 to +7.0    | V    |  |  |  |  |  |

| VPP                                   | Programming Voltage 2       | -0.5 to $+14.0$ | V    |  |  |  |  |  |

| <b>AC TEST CONDITIONS:</b>     | Including Programming |

|--------------------------------|-----------------------|

| Input Pulse Levels             | 0V to 3.0V            |

| Input Pulse Rise and Fall Time | ≤ 20ns                |

| Input Timing Reference Levels  | 1.5V                  |

| Output Timing Reference Levels | 1.5V                  |

| R               | ECOMMENDED O                                | PERAT | ING  | RANGE <sup>2</sup> |      |

|-----------------|---------------------------------------------|-------|------|--------------------|------|

| Symbol          | Characteristic                              | Min.  | Тур. | Max.               | Unit |

| $V_{DD}$        | Supply Voltage⁴                             | 4.5   | 5.0  | 5.5                | ٧    |

| ViH             | Input HIGH Voltage                          | 2.2   |      | $V_{DD} + 1.0$     | V    |

| V <sub>IL</sub> | Input LOW Voltage                           | -0.2  |      | 0.8                | V    |

| $V_{PP}$        | V <sub>PP</sub> Supply Voltage <sup>5</sup> | 12.75 | 13.0 | 13.25              | ٧    |

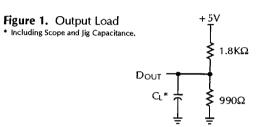

|                                          | Output Load |                     |  |  |  |  |  |

|------------------------------------------|-------------|---------------------|--|--|--|--|--|

| Float C <sub>L</sub> Parameters Measured |             |                     |  |  |  |  |  |

| 1                                        | 100 pF      | except tDF and tDFP |  |  |  |  |  |

| 2                                        | 5 pF        | tDF and tDFP        |  |  |  |  |  |

| CA               | CAPACITANCE <sup>3</sup> : $T_A = 25^{\circ}C$ , $F = 1.0MHz$ |      |      |               |  |  |  |  |

|------------------|---------------------------------------------------------------|------|------|---------------|--|--|--|--|

| Symbol           | Parameter                                                     | Max. | Unit | Condition     |  |  |  |  |

| CŒ               | Chip Enable                                                   | 15   | pF   |               |  |  |  |  |

| CADR             | Address Input                                                 | 35   |      | $V_{IN} = 0V$ |  |  |  |  |

| COE              | Output Enable                                                 | 35   |      | $V_{IN} = UV$ |  |  |  |  |

| C <sub>I/O</sub> | Data Input/Output                                             | 25   |      |               |  |  |  |  |

| Symbol           | Characteristics                               | Characteristics Test Conditions                                            |                                                                            |      |                   |      |                   |      |

|------------------|-----------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------|------|-------------------|------|-------------------|------|

| Symbol           | Characteristics Test Collations               |                                                                            |                                                                            |      |                   | Min. | Max.              | Unit |

| lin              | Input<br>Leakage Current                      | VIN - VDD                                                                  | -20                                                                        | 20   | -20               | 20   | μА                |      |

| lout             | Output<br>Leakage Current                     | CE = V <sub>IH</sub> , V <sub>IN</sub> =V <sub>DD</sub> or V <sub>SS</sub> | CE = V <sub>IH</sub> , V <sub>IN</sub> =V <sub>DD</sub> or V <sub>SS</sub> |      |                   |      | 10                | μА   |

|                  |                                               | 120-250ns                                                                  |                                                                            | 30   |                   | 50   |                   |      |

|                  | Current, Read                                 | Cycle = min., Duty = 100%                                                  | 55-90ns                                                                    |      | 90                |      | 110               | mA   |

| ISB1             | V <sub>DD</sub> Standby Current               |                                                                            | 120-250ns                                                                  |      | 6                 |      | 6                 |      |

|                  | IOUT = 0mA (TTL)                              | CE = VIH, VIN = VIH or VIL                                                 | 55-90ns                                                                    |      | 70                |      | 70                | mA   |

| I <sub>SB2</sub> | V <sub>DD</sub> Standby                       | $\overline{CE} = V_{DD} \pm 0.3V$ , $I_{OUT} = 0$ mA                       | 120-250ns                                                                  |      | 400               |      | 400               | μА   |

|                  | Current (CMOS)                                | $V_{IN} \ge V_{DD}$ -3.0V or $V_{IN} \le 0.3V$                             | 55-90ns                                                                    |      | 60                |      | 60                | mA   |

| I <sub>PP1</sub> | V <sub>PP</sub> Supply Current<br>Programming | CE, = VIL, OE = VIH                                                        |                                                                            |      | 30                |      | 60                | mΑ   |

| IPP3             | VPP Supply Current<br>Read <sup>4</sup>       | CE, OE - VIL, IOUT > 0mA                                                   |                                                                            |      | 40                |      | 40                | μА   |

| Vol              | Output LOW Voltage                            | IOUT = 2.1 mA                                                              |                                                                            |      | 0.45              |      | 0.45              | V    |

| V <sub>OH1</sub> | Output HIGH Voltage                           | I <sub>OUT</sub> = -400μA                                                  |                                                                            | 2.4  |                   | 2.4  |                   | V    |

| VıL              | Input LOW Level                               |                                                                            |                                                                            | -0.2 | 0.8               | -0.2 | 0.8               | V    |

| ViH              | Input HIGH Level                              |                                                                            |                                                                            | 2.2  | V <sub>DD+1</sub> | 2.2  | V <sub>DD+1</sub> | V    |

|                              | FUNCTIONS AND PIN CONNECTIONS |    |    |                 |                 |                |  |  |  |  |

|------------------------------|-------------------------------|----|----|-----------------|-----------------|----------------|--|--|--|--|

| Mode                         | Function                      | CE | ŌĒ | V <sub>PP</sub> | V <sub>DD</sub> | 1/00 - 1/015   |  |  |  |  |

| Read                         | Read                          | L  | L  |                 |                 | Data Out       |  |  |  |  |

|                              | Output Deselect               | Ĺ  | Н  | 5V              | 5V              | High Impedance |  |  |  |  |

| Operations                   | Standby                       | Н  | X  | 1               | ]               | High Impedance |  |  |  |  |

| Program                      | Program                       | L  | Н  |                 |                 | Data In        |  |  |  |  |

| Operations                   | Program Inhibit               | Н  | Н  | 13.0V           | 6.5V            | High Impedance |  |  |  |  |

| $(T_A = +25 \pm 5^{\circ}C)$ | Program Verify                | Н  | L  |                 |                 | Data Out       |  |  |  |  |

L = LOW, H = HIGH and X = Don't Care

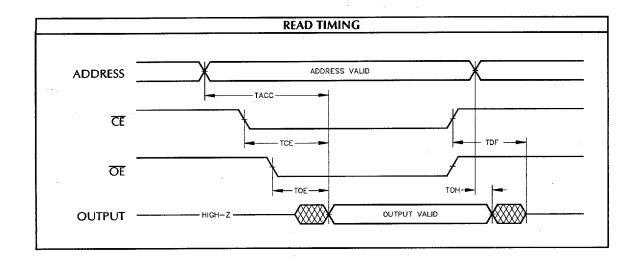

|         | AC OPERATING CONDITIONS AND CHARACTERISTICS - READ: Over operating ranges |                                          |       |      |      |      |      |      |       |      |      |

|---------|---------------------------------------------------------------------------|------------------------------------------|-------|------|------|------|------|------|-------|------|------|

| No.     | No. Symbol                                                                | Parameter                                | 55ns* |      | 70ns |      | 90ns |      | 120ns |      | Unit |

| oyinboi |                                                                           | Min.                                     | Max.  | Min. | Max. | Min. | Max. | Min. | Max.  | Unit |      |

| 1       | tacc                                                                      | Address Access Time 8                    |       | 55   |      | 70   |      | 90   |       | 120  | ns   |

| 2       | tcE                                                                       | Chip Enable to Output Valid <sup>7</sup> |       | 55   |      | 70   |      | 90   |       | 120  | ns   |

| 3       | toe                                                                       | Output Enable to Output Valid 7,8        |       | 25   |      | 30   |      | 30   |       | 50   | ns   |

| 4       | t <sub>DF</sub>                                                           | OE or CE HIGH to Output Float 3, 9       | 0     | 25   | 0    | 30   | 0    | 30   | 0     | 45   | ns   |

| 5       | tон                                                                       | Output Hold from Address Change          | 0     |      | 0    |      | 0    |      | 0     |      | ns   |

<sup>\*</sup> Commercial only.

| No. | No. Symbol      | Parameter                                | 150ns |      | 170ns |      | 200ns |      | 250ns |     | Unit |

|-----|-----------------|------------------------------------------|-------|------|-------|------|-------|------|-------|-----|------|

| 5,  | - unamerer      | Min.                                     | Max.  | Min. | Max.  | Min. | Max.  | Min. | Max.  | Ont |      |

| 1   | tacc            | Address Access Time 8                    |       | 150  |       | 170  |       | 200  |       | 250 | ns   |

| 2   | tce             | Chip Enable to Output Valid <sup>7</sup> |       | 150  |       | 170  |       | 200  |       | 250 | ns   |

| 3   | t <sub>OE</sub> | Output Enable to Output Valid 7,8        |       | 60   |       | 70   |       | 75   |       | 100 | ns   |

| 4   | tor             | OE or CE HIGH to Output Float 3, 9       | 0     | 50   | 0     | 50   | 0     | 55   | 0     | 60  | ns   |

| 5   | tон             | Output Hold from Address Change          | 0     |      | 0     |      | 0     |      | 0     |     | ns   |

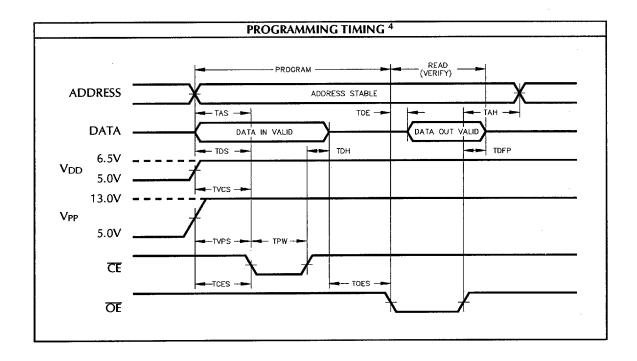

|     | A(               | PROGRAMMING CONDITIONS AND CHAR          | ACTERISTICS: Ove | r operating ranges |      |

|-----|------------------|------------------------------------------|------------------|--------------------|------|

| No. | Symbol           | Parameter                                | Min,             | Max.               | Unit |

| 6   | tas              | Address Set-up Time                      | 2                |                    | μs   |

| 7   | t <sub>CES</sub> | Chip Enable Set-up Time                  | 2                |                    | μѕ   |

| 8   | toes             | Output Enable Set-up Time                | 2                |                    | μs   |

| 9   | t <sub>DS</sub>  | Data Set-up Time                         | 2                |                    | μѕ   |

| 10  | tvcs             | V <sub>CC</sub> Set-up Time <sup>5</sup> | 2                |                    | μѕ   |

| 11  | tvps             | V <sub>PP</sub> Set-up Time <sup>5</sup> | 2                |                    | μs   |

| 12  | tан              | Address Hold Time                        | 0                |                    | μs   |

| 13  | tрн              | Data Hold Time                           | 2                |                    | μs   |

| 14  | t <sub>DFP</sub> | Output Enable HIGH Output Float Delay 3  | 0                | 130                | ns   |

| 15  | t <sub>PW</sub>  | Programming Pulse Width 10               | 95               | 105                | μѕ   |

194

**=** 2759415 0001382 812 **=**

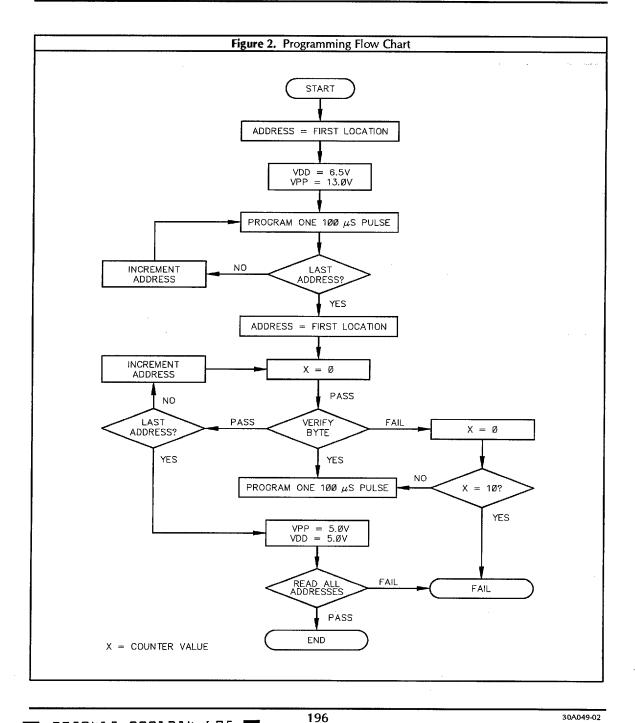

# PROGRAMMING AND ERASING INFORMATION

#### **PROGRAMMING**

Upon delivery from Dense-Pac, or after erasure (See Erasure section), the DPV32X16A contains "1's" in every location, and read data is in the high state. "0's" are written into the DPV32X16A through the procedure of programming. A  $0.1\mu F$  capacitor between Vpp and Vss is required to prevent excessive voltage transients during programming which could damage the device. Programming modes require +6.5V and +13.0V to be applied to VpD and Vpp respectively.

Individual bytes or address locations can be selected and programmed by using the programming algorithm shown in Figure 2. In the programming mode,  $\overline{OE}$  is set at  $V_{IH}$ ,  $V_{DD}$  is set at +6.5V, and then  $V_{PP}$  is set at +13.0V. After the applied address and input data signals are stable, programming is accomplished by a  $100\mu$ s  $V_{IL}$  pulse on the  $\overline{CE}$  pin (refer to the Programming Timing Diagram).

First program each address with a 100µs pulse on the CE without verification. Then return to first address and start a verification loop verifying each address. If an address location fails verification, apply up to 10 consecutive 100µs CE pulses with a verification after each pulse.

If the device fails to program after 10 attempts, the programming is considered failed. After the byte is verified, continue the algorithm through all the required addresses. Lower Vpp to 5.0V and then lower Vpp to +5.0V and compare the data programmed with the original data to determine if the device passes. A programming adapter for programming on standard EPROM programmers is available, contact Dense-Pac sales for more information.

#### **ERASURE**

To clear all locations of their programmed contents it is necessary to expose the DPV32X16A to an ultraviolet light source. A dosage of 15W-seconds/cm<sup>2</sup> is required to completely erase a DPV32X16A. This dosage can be obtained by exposure to an ultraviolet lamp [wavelength of 2537 Angstroms (A) with an intensity of 12,000μW/cm<sup>2</sup>] for 20 minutes.

The DPV32X16A and similar devices can be erased by light sources having wavelengths shorter than 4000Å. Although erasure time will be much longer than with UV sources at 2537Å, nevertheless the exposure to fluorescent light or sunlight will eventually erase the DPV32X16A. After programming, the package windows should be covered by an opaque label or substance, to prevent inadvertent erasure.

### NOTES:

- Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This

is stress rating only and functional operation of the device at these or any other conditions above those indicated in the

operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods

may affect reliability.

- 2. All voltages are with respect to Vss.

- 3. This parameter is guaranteed and not 100% tested.

- 4. VDD must be applied either coincident with or before VPP and removed either coincident with or after VPP.

- 5. VPP must not be greater than 14.0V including overshoot. Permanent device damage may occur if the device is taken out or put into socket with VPP = 13.0V. Also, during CE = VIL, VPP must not be switched from 5.0V to 13.0V or vice-versa.

- 6.  $t_A = -55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ ,  $V_{DD} = 5.0 \text{V} \pm 0.5 \text{V}$ , and  $V_{PP} = V_{DD}$  reading.  $t_A = +25^{\circ}\text{C} \pm 5^{\circ}\text{C}$ ,  $V_{DD} = 6.5 \pm 0.25 \text{V}$ ,  $V_{PP} = 13.0 \text{V} \pm 0.25 \text{V}$  programming.

- 7.  $\overline{OE}$  may be delayed up to  $t_{CE}$   $t_{OE}$  after the following edge of  $\overline{CE}$  without impact on  $t_{CE}$ .

- 8.  $\overline{OE}$  may be delayed up to t<sub>ACC</sub> t<sub>OE</sub> after the following Address is valid without impact on t<sub>ACC</sub>.

- 9. Top is specified from OE or CE, whichever occurs first.

- 10. Initial Program Pulse Width Tolerance is  $100 \mu s \pm 5\%$ .

# **■ 2759415 0001383 759 ■**

2759415 0001384 695

<sup>\*</sup> B grade modules are constructed with 883 devices.

# Dense-Pac Microsystems, Inc.

7321 Lincoln Way ◆ Garden Grove, California 92641-1428 (714) 898-0007 ◆ (800) 642-4477 (Outside CA) ◆ FAX: (714) 897-1772

30A049-02 REV. B 197

**=** 2759415 0001385 521 **==**