# **High Voltage Switching Regulator**

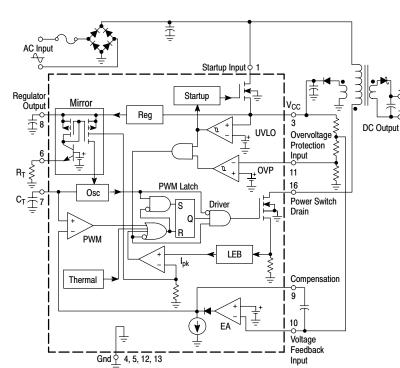

The MC33362 is a monolithic high voltage switching regulator that is specifically designed to operate from a rectified 120 VAC line source. This integrated circuit features an on-chip 500 V/2.0 A SenseFET power switch, 250 V active off-line startup FET, duty cycle controlled oscillator, current limiting comparator with a programmable threshold and leading edge blanking, latching pulse width modulator for double pulse suppression, high gain error amplifier, and a trimmed internal bandgap reference. Protective features include cycle-by-cycle current limiting, input undervoltage lockout with hysteresis, output overvoltage protection, and thermal shutdown. This device is available in a 16-lead dual-in-line and wide body surface mount packages.

- On-Chip 500 V, 2.0 A SenseFET Power Switch

- Rectified 120 VAC Line Source Operation

- On-Chip 250 V Active Off-Line Startup FET

- Latching PWM for Double Pulse Suppression

- Cycle-By-Cycle Current Limiting

- Input Undervoltage Lockout with Hysteresis

- Output Overvoltage Protection Comparator

- Trimmed Internal Bandgap Reference

- Internal Thermal Shutdown

This device contains 221 active transistors.

Figure 1. Simplified Application

#### ON Semiconductor™

http://onsemi.com

#### MARKING DIAGRAMS

PDIP-16 P SUFFIX CASE 648E

SO-16W DW SUFFIX CASE 751N

A = Assembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

#### PIN CONNECTIONS

#### **ORDERING INFORMATION**

| Device      | Package | Shipping         |

|-------------|---------|------------------|

| MC33362DW   | SO-16W  | 47 Units/Rail    |

| MC33362DWR2 | SO-16W  | 1000 Tape & Reel |

| MC33362P    | PDIP-16 | 25 Units/Rail    |

#### MAXIMUM RATINGS (Note 1.)

| Rating                                                                                                                                                                                                                                                                                                                                               | Symbol                                                                           | Value                    | Unit   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------|--------|

| Power Switch (Pin 16) Drain Voltage Drain Current                                                                                                                                                                                                                                                                                                    | V <sub>DS</sub>                                                                  | 500<br>2.0               | V<br>A |

| Startup Input Voltage (Pin 1, Note 2.) Pin 3 = Gnd Pin 3 ≤ 1000 µF to ground                                                                                                                                                                                                                                                                         | V <sub>in</sub>                                                                  | 250<br>400               | V      |

| Power Supply Voltage (Pin 3)                                                                                                                                                                                                                                                                                                                         | V <sub>CC</sub>                                                                  | 40                       | V      |

| Input Voltage Range Voltage Feedback Input (Pin 10) Compensation (Pin 9) Overvoltage Protection Input (Pin 11) R <sub>T</sub> (Pin 6) C <sub>T</sub> (Pin 7)                                                                                                                                                                                         | V <sub>IR</sub>                                                                  | -1.0 to V <sub>reg</sub> | V      |

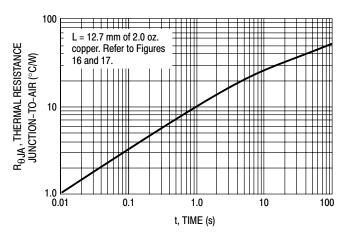

| Thermal Characteristics P Suffix, Dual–In–Line Case 648E Thermal Resistance, Junction–to–Air Thermal Resistance, Junction–to–Case (Pins 4, 5, 12, 13) DW Suffix, Surface Mount Case 751N Thermal Resistance, Junction–to–Air Thermal Resistance, Junction–to–Case (Pins 4, 5, 12, 13) Refer to Figures 16 and 17 for additional thermal information. | R <sub>θ</sub> JA<br>R <sub>θ</sub> JC<br>R <sub>θ</sub> JA<br>R <sub>θ</sub> JC | 80<br>15<br>95<br>15     | °C/W   |

| Operating Junction Temperature                                                                                                                                                                                                                                                                                                                       | TJ                                                                               | - 25 to +150             | °C     |

| Storage Temperature                                                                                                                                                                                                                                                                                                                                  | T <sub>stg</sub>                                                                 | - 55 to +150             | °C     |

**ELECTRICAL CHARACTERISTICS** ( $V_{CC}$  = 20 V,  $R_T$  = 10 k,  $C_T$  = 390 pF,  $C_{Pin~8}$  = 1.0  $\mu$ F, for typical values  $T_J$  = 25°C, for min/max values  $T_J$  is the operating junction temperature range that applies (Note 3.), unless otherwise noted.)

| Characteristic                                                                                                                                                                                                                                                                                                                                             | Symbol                | Min                    | Тур                   | Max                    | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------|-----------------------|------------------------|------|

| REGULATOR (Pin 8)                                                                                                                                                                                                                                                                                                                                          | ·                     |                        |                       |                        |      |

| Output Voltage (I <sub>O</sub> = 0 mA, T <sub>J</sub> = 25°C)                                                                                                                                                                                                                                                                                              | V <sub>reg</sub>      | 5.5                    | 6.5                   | 7.5                    | V    |

| Line Regulation (V <sub>CC</sub> = 20 V to 40 V)                                                                                                                                                                                                                                                                                                           | Reg <sub>line</sub>   | -                      | 30                    | 500                    | mV   |

| Load Regulation (I <sub>O</sub> = 0 mA to 10 mA)                                                                                                                                                                                                                                                                                                           | Reg <sub>load</sub>   | -                      | 44                    | 200                    | mV   |

| Total Output Variation over Line, Load, and Temperature                                                                                                                                                                                                                                                                                                    | V <sub>reg</sub>      | 5.3                    | -                     | 8.0                    | V    |

| OSCILLATOR (Pin 7)                                                                                                                                                                                                                                                                                                                                         | ·                     |                        | •                     |                        |      |

| Frequency $\begin{split} &C_T=390 \text{ pF} \\ &T_J=25^{\circ}\text{C (V}_{CC}=20 \text{ V}) \\ &T_J=T_{low} \text{ to } T_{high} \text{ (V}_{CC}=20 \text{ V to } 40 \text{ V}) \\ &C_T=2.0 \text{ nF} \\ &T_J=25^{\circ}\text{C (V}_{CC}=20 \text{ V}) \\ &T_J=T_{low} \text{ to } T_{high} \text{ (V}_{CC}=20 \text{ V to } 40 \text{ V}) \end{split}$ | fosc                  | 260<br>255<br>60<br>59 | 285<br>-<br>67.5<br>- | 310<br>315<br>75<br>76 | kHz  |

| Frequency Change with Voltage (V <sub>CC</sub> = 20 V to 40 V)                                                                                                                                                                                                                                                                                             | Δf <sub>OSC</sub> /ΔV | _                      | 0.1                   | 2.0                    | kHz  |

- This device series contains ESD protection and exceeds the following tests: Human Body Model 2000 V per MIL-STD-883, Method 3015.

Machine Model Method 200 V.

- 2. Maximum power dissipation limits must be observed.

- 3. Tested junction temperature range for the MC33362:

$$T_{low} = -25$$

°C  $T_{high} = +125$ °C

**ELECTRICAL CHARACTERISTICS** ( $V_{CC}$  = 20 V,  $R_T$  = 10 k,  $C_T$  = 390 pF,  $C_{Pin~8}$  = 1.0  $\mu$ F, for typical values  $T_J$  = 25°C, for min/max values  $T_J$  is the operating junction temperature range that applies (Note 4.), unless otherwise noted.)

| Characteristic                                                                                                                                | Symbol                                     | Min          | Тур          | Max         | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------|--------------|-------------|------|

| ERROR AMPLIFIER (Pins 9, 10)                                                                                                                  | <del> </del>                               | •            |              |             | ···  |

| Voltage Feedback Input Threshold                                                                                                              | $V_{FB}$                                   | 2.52         | 2.6          | 2.68        | V    |

| Line Regulation (V <sub>CC</sub> = 20 V to 40 V, T <sub>J</sub> = 25°C)                                                                       | Reg <sub>line</sub>                        | -            | 0.6          | 5.0         | mV   |

| Input Bias Current (V <sub>FB</sub> = 2.6 V)                                                                                                  | I <sub>IB</sub>                            | _            | 20           | 500         | nA   |

| Open Loop Voltage Gain (T <sub>J</sub> = 25°C)                                                                                                | A <sub>VOL</sub>                           | _            | 82           | _           | dB   |

| Gain Bandwidth Product (f = 100 kHz, T <sub>J</sub> = 25°C)                                                                                   | GBW                                        | _            | 1.0          | _           | MHz  |

| Output Voltage Swing<br>High State ( $I_{Source}$ = 100 $\mu$ A, $V_{FB}$ < 2.0 V)<br>Low State ( $I_{Sink}$ = 100 $\mu$ A, $V_{FB}$ > 3.0 V) | V <sub>OH</sub><br>V <sub>OL</sub>         | 4.0          | 5.3<br>0.2   | _<br>0.35   | V    |

| OVERVOLTAGE DETECTION (Pin 11)                                                                                                                |                                            | <del>'</del> | <del>'</del> | <del></del> | h    |

| Input Threshold Voltage                                                                                                                       | $V_{th}$                                   | 2.47         | 2.6          | 2.73        | V    |

| Input Bias Current (V <sub>in</sub> = 2.6 V)                                                                                                  | I <sub>IB</sub>                            | _            | 100          | 500         | nA   |

| PWM COMPARATOR (Pins 7, 9)                                                                                                                    |                                            |              |              |             |      |

| Duty Cycle Maximum (V <sub>FB</sub> = 0 V) Minimum (V <sub>FB</sub> = 2.7 V)                                                                  | DC <sub>(max)</sub><br>DC <sub>(min)</sub> | 48<br>-      | 50<br>0      | 52<br>0     | %    |

| POWER SWITCH (Pin 16)                                                                                                                         |                                            | <del>'</del> | ·            | ·           |      |

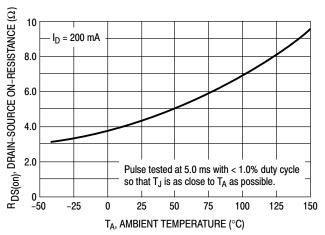

| Drain–Source On–State Resistance ( $I_D$ = 200 mA)<br>$T_J$ = 25°C<br>$T_J$ = $T_{low}$ to $T_{high}$                                         | R <sub>DS(on)</sub>                        |              | 4.4<br>-     | 6.0<br>12   | Ω    |

| Drain–Source Off–State Leakage Current (V <sub>DS</sub> = 500 V)                                                                              | I <sub>D(off)</sub>                        | -            | 0.2          | 50          | μΑ   |

| Rise Time                                                                                                                                     | t <sub>r</sub>                             | -            | 50           | _           | ns   |

| Fall Time                                                                                                                                     | t <sub>f</sub>                             | -            | 50           | _           | ns   |

| OVERCURRENT COMPARATOR (Pin 16)                                                                                                               | 1                                          | 1            | 1            |             |      |

| Current Limit Threshold (R <sub>T</sub> = 10 k)                                                                                               | I <sub>lim</sub>                           | 0.7          | 0.9          | 1.1         | Α    |

| STARTUP CONTROL (Pin 1)                                                                                                                       |                                            |              |              |             |      |

| Peak Startup Current ( $V_{in} = 200 \text{ V}$ )<br>$V_{CC} = 0 \text{ V}$<br>$V_{CC} = (V_{th(on)} - 0.2 \text{ V})$                        | I <sub>start</sub>                         | _<br>_       | 55<br>26     | _<br>_      | mA   |

| Off–State Leakage Current (V <sub>in</sub> = 50 V, V <sub>CC</sub> = 20 V)                                                                    | I <sub>D(off)</sub>                        | -            | 40           | 200         | μΑ   |

| UNDERVOLTAGE LOCKOUT (Pin 3)                                                                                                                  | 1                                          | 1            | ı            | ı           | 1    |

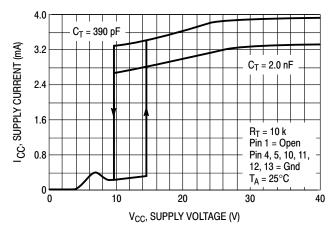

| Startup Threshold (V <sub>CC</sub> Increasing)                                                                                                | V <sub>th(on)</sub>                        | 11           | 14.5         | 18          | V    |

| Minimum Operating Voltage After Turn-On                                                                                                       | V <sub>CC(min)</sub>                       | 7.5          | 9.5          | 11.5        | V    |

| TOTAL DEVICE (Pin 3)                                                                                                                          | · · · · · · · · · · · · · · · · · · ·      | <del>'</del> | • • • • •    | • • • • •   |      |

| Power Supply Current Startup (V <sub>CC</sub> = 10 V, Pin 1 Open) Operating                                                                   | Icc                                        | _<br>_       | 0.3<br>3.6   | 0.5<br>5.0  | mA   |

|                                                                                                                                               | l                                          | <u> </u>     | 1            | I .         | 1    |

<sup>4.</sup> Tested junction temperature range for the MC33362:  $T_{low} = -25^{\circ}C \qquad T_{high} = +125^{\circ}C$

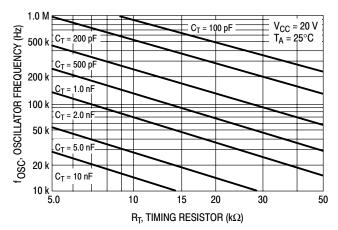

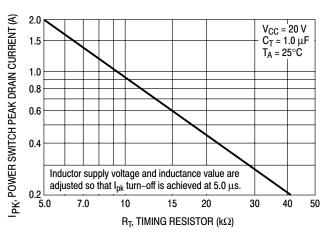

Figure 2. Oscillator Frequency versus Timing Resistor

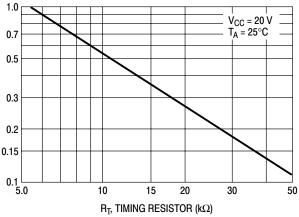

Figure 3. Power Switch Peak Drain Current versus Timing Resistor

Figure 4. Oscillator Charge/Discharge Current versus Timing Resistor

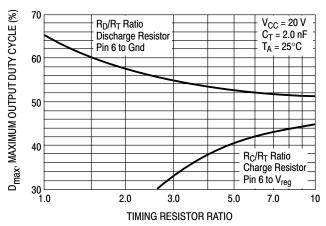

Figure 5. Maximum Output Duty Cycle versus Timing Resistor Ratio

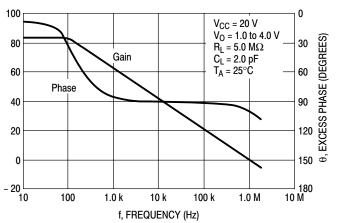

Figure 6. Error Amp Open Loop Gain and Phase versus Frequency

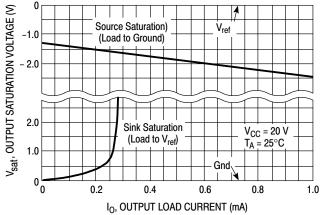

Figure 7. Error Amp Output Saturation Voltage versus Load Current

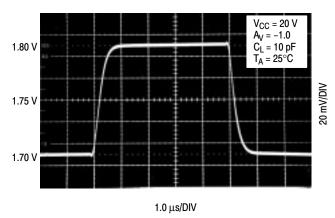

Figure 8. Error Amplifier Small Signal Transient Response

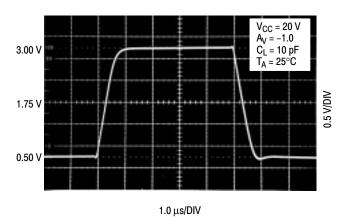

Figure 9. Error Amplifier Large Signal Transient Response

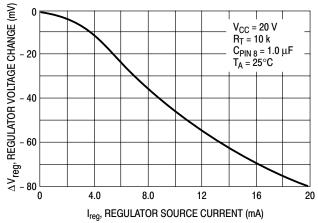

Figure 10. Regulator Output Voltage Change versus Source Current

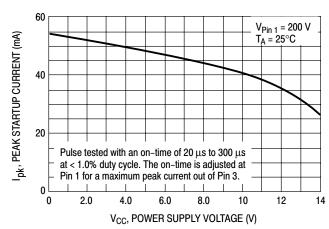

Figure 11. Peak Startup Current versus Power Supply Voltage

Figure 12. Power Switch Drain-Source On-Resistance versus Temperature

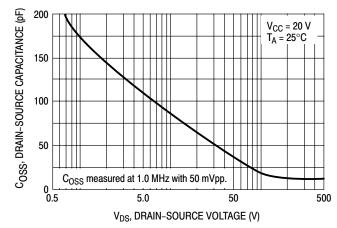

Figure 13. Power Switch

Drain-Source Capacitance versus Voltage

Figure 14. Supply Current versus Supply Voltage

Figure 15. DW and P Suffix Transient Thermal Resistance

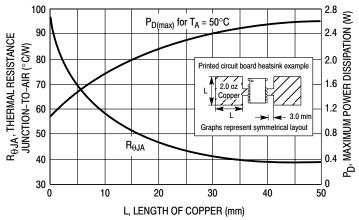

Figure 16. DW Suffix (SOP-16L) Thermal Resistance and Maximum Power Dissipation versus P.C.B. Copper Length

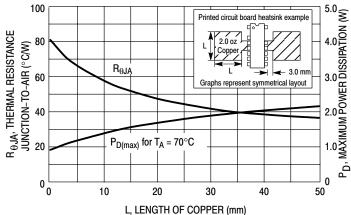

Figure 17. P Suffix (DIP-16) Thermal Resistance and Maximum Power Dissipation versus P.C.B. Copper Length

#### PIN FUNCTION DESCRIPTION

| Pin          | Function                        | Description                                                                                                                                                                                                                                                                                                 |

|--------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | Startup Input                   | This pin connects directly to the rectified ac line voltage source. Internally Pin 1 is tied to the drain of a high voltage startup MOSFET. During startup, the MOSFET supplies internal bias, and charges an external capacitor that connects from the V <sub>CC</sub> pin to ground.                      |

| 2            | -                               | This pin has been omitted for increased spacing between the rectified AC line voltage on Pin 1 and the $V_{\rm CC}$ potential on Pin 3.                                                                                                                                                                     |

| 3            | V <sub>CC</sub>                 | This is the positive supply voltage input. During startup, power is supplied to this input from Pin 1. When $V_{CC}$ reaches the UVLO upper threshold, the startup MOSFET turns off and power is supplied from an auxiliary transformer winding.                                                            |

| 4, 5, 12, 13 | Ground                          | These pins are the control circuit grounds. They are part of the IC lead frame and provide a thermal path from the die to the printed circuit board.                                                                                                                                                        |

| 6            | R <sub>T</sub>                  | Resistor $R_T$ connects from this pin to ground. The value selected will program the Current Limit Comparator threshold and affect the Oscillator frequency.                                                                                                                                                |

| 7            | Ст                              | Capacitor $C_T$ connects from this pin to ground. The value selected, in conjunction with resistor $R_T$ , programs the Oscillator frequency.                                                                                                                                                               |

| 8            | Regulator Output                | This 6.5 V output is available for biasing external circuitry. It requires an external bypass capacitor of at least 1.0 µF for stability.                                                                                                                                                                   |

| 9            | Compensation                    | This pin is the Error Amplifier output and is made available for loop compensation. It can be used as an input to directly control the PWM Comparator.                                                                                                                                                      |

| 10           | Voltage Feedback<br>Input       | This is the inverting input of the Error Amplifier. It has a 2.6 V threshold and normally connects through a resistor divider to the converter output, or to a voltage that represents the converter output.                                                                                                |

| 11           | Overvoltage<br>Protection Input | This input provides runaway output voltage protection due to an external component or connection failure in the control loop feedback signal path. It has a 2.6 V threshold and normally connects through a resistor divider to the converter output, or to a voltage that represents the converter output. |

| 14, 15       | _                               | These pins have been omitted for increased spacing between the high voltages present on the Power Switch Drain, and the ground potential on Pins 12 and 13.                                                                                                                                                 |

| 16           | Power Switch Drain              | This pin is designed to directly drive the converter transformer and is capable of switching a maximum of 500 V and 2.0 A.                                                                                                                                                                                  |

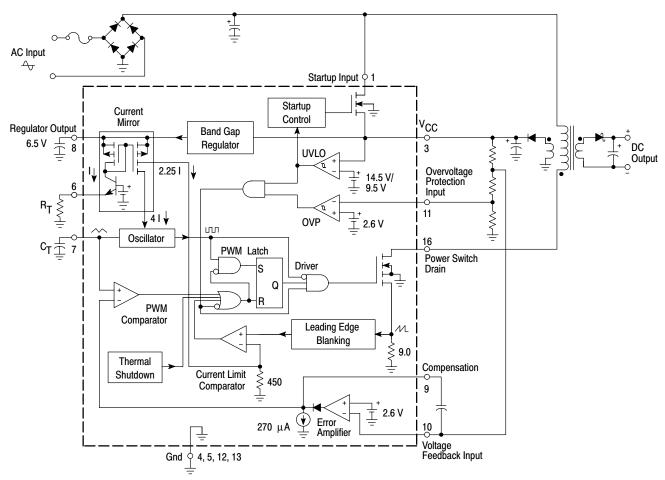

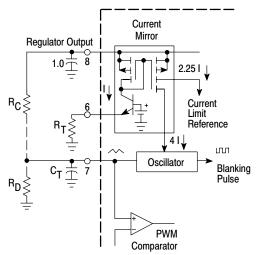

Figure 18. Representative Block Diagram

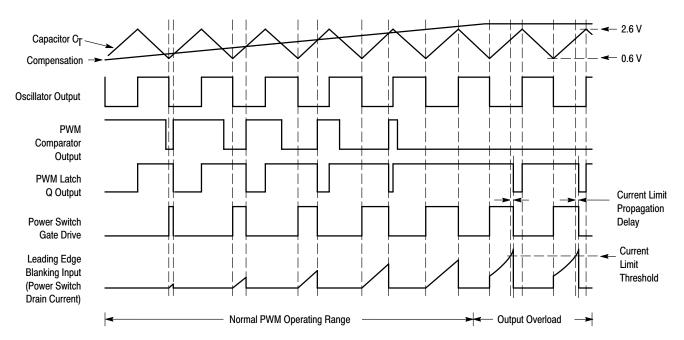

Figure 19. Timing Diagram

#### **OPERATING DESCRIPTION**

#### Introduction

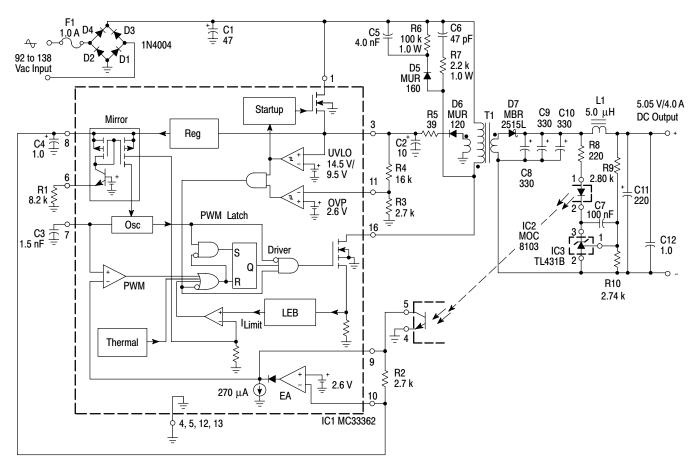

The MC33362 represents a new higher level of integration by providing all the active high voltage power, control, and protection circuitry required for implementation of a flyback or forward converter on a single monolithic chip. This device is designed for direct operation from a rectified 120 VAC line source and requires a minimum number of external components to implement a complete converter. A description of each of the functional blocks is given below, and the representative block and timing diagrams are shown in Figures 18 and 19.

#### Oscillator and Current Mirror

The oscillator frequency is controlled by the values selected for the timing components R<sub>T</sub> and C<sub>T</sub>. Resistor R<sub>T</sub> programs the oscillator charge/discharge current via the Current Mirror 4 I output, Figure 4. Capacitor C<sub>T</sub> is charged and discharged by an equal magnitude internal current source and sink. This generates a symmetrical 50 percent duty cycle waveform at Pin 7, with a peak and valley threshold of 2.6 V and 0.6 V respectively. During the discharge of C<sub>T</sub>, the oscillator generates an internal blanking pulse that holds the inverting input of the AND gate Driver high. This causes the Power Switch gate drive to be held in a low state, thus producing a well controlled amount of output deadtime. The amount of deadtime is relatively constant with respect to the oscillator frequency when operating below 1.0 MHz. The maximum Power Switch duty cycle at Pin 16 can be modified from the internal 50% limit by providing an additional charge or discharge current path to C<sub>T</sub>, Figure 20. In order to increase the maximum duty cycle, a discharge current resistor R<sub>D</sub> is connected from Pin 7 to ground. To decrease the maximum duty cycle, a charge current resistor R<sub>C</sub> is connected from Pin 7 to the Regulator Output. Figure 5 shows an obtainable range of maximum output duty cycle versus the ratio of either R<sub>C</sub> or  $R_D$  with respect to  $R_T$ .

Figure 20. Maximum Duty Cycle Modification

The formula for the charge/discharge current along with the oscillator frequency are given below. The frequency formula is a first order approximation and is accurate for  $C_T$  values greater than 500 pF. For smaller values of  $C_T$ , refer to Figure 2. Note that resistor  $R_T$  also programs the Current Limit Comparator threshold.

$$I_{chg/dscg} = \frac{5.4}{R_T}$$

$f \approx \frac{I_{chg/dscg}}{4C_T}$

#### **PWM Comparator and Latch**

The pulse width modulator consists of a comparator with the oscillator ramp voltage applied to the non–inverting input, while the error amplifier output is applied into the inverting input. The Oscillator applies a set pulse to the PWM Latch while  $C_T$  is discharging, and upon reaching the valley voltage, Power Switch conduction is initiated. When  $C_T$  charges to a voltage that exceeds the error amplifier output, the PWM Latch is reset, thus terminating Power Switch conduction for the duration of the oscillator ramp—up period. This PWM Comparator/Latch combination prevents multiple output pulses during a given oscillator clock cycle. The timing diagram shown in Figure 19 illustrates the Power Switch duty cycle behavior versus the Compensation voltage.

#### **Current Limit Comparator and Power Switch**

The MC33362 uses cycle-by-cycle current limiting as a means of protecting the output switch transistor from overstress. Each on-cycle is treated as a separate situation. Current limiting is implemented by monitoring the output switch current buildup during conduction, and upon sensing an overcurrent condition, immediately turning off the switch for the duration of the oscillator ramp-up period.

The Power Switch is constructed as a SenseFET allowing a virtually lossless method of monitoring the drain current. It consists of a total of 3770 cells, of which 50 are connected to a 9.0  $\Omega$  ground–referenced sense resistor. The Current Sense Comparator detects if the voltage across the sense resistor exceeds the reference level that is present at the inverting input. If exceeded, the comparator quickly resets the PWM Latch, thus protecting the Power Switch. The current limit reference level is generated by the 2.25 I output of the Current Mirror. This current causes a reference voltage to appear across the 450  $\Omega$  resistor. This voltage level, as well as the Oscillator charge/discharge current are both set by resistor R<sub>T</sub>. Therefore when selecting the values for  $R_T$  and  $C_T$ ,  $R_T$  must be chosen first to set the Power Switch peak drain current, while C<sub>T</sub> is chosen second to set the desired Oscillator frequency. A graph of the Power Switch peak drain current versus R<sub>T</sub> is shown in Figure 3 with the related formula below.

$$I_{pk} = 12.3 \left(\frac{R_{T}}{1000}\right) - 1.115$$

The Power Switch is designed to directly drive the converter transformer and is capable of switching a maximum of 500 V and 2.0 A. Proper device voltage snubbing and heatsinking are required for reliable operation.

A Leading Edge Blanking circuit was placed in the current sensing signal path. This circuit prevents a premature reset of the PWM Latch. The premature reset is generated each time the Power Switch is driven into conduction. It appears as a narrow voltage spike across the current sense resistor, and is due to the MOSFET gate to source capacitance, transformer interwinding capacitance, and output rectifier recovery time. The Leading Edge Blanking circuit has a dynamic behavior in that it masks the current signal until the Power Switch turn—on transition is completed. The current limit propagation delay time is typically 233 ns. This time is measured from when an overcurrent appears at the Power Switch drain, to the beginning of turn—off.

#### **Error Amplifier**

An fully compensated Error Amplifier with access to the inverting input and output is provided for primary side voltage sensing, Figure 18. It features a typical dc voltage gain of 82 dB, and a unity gain bandwidth of 1.0 MHz with 78 degrees of phase margin, Figure 6. The noninverting input is internally biased at 2.6 V ±3.1% and is not pinned out. The Error Amplifier output is pinned out for external loop compensation and as a means for directly driving the PWM Comparator. The output was designed with a limited sink current capability of 270 µA, allowing it to be easily overridden with a pull-up resistor. This is desirable in applications that require secondary side voltage sensing, Figure 21. In this application, the Voltage Feedback Input is connected to the Regulator Output. This disables the Error Amplifier by placing its output into the sink state, allowing the optocoupler transistor to directly control the PWM Comparator.

#### **Overvoltage Protection**

An Overvoltage Protection Comparator is included to eliminate the possibility of runaway output voltage. This condition can occur if the control loop feedback signal path is broken due to an external component or connection failure. The comparator is normally used to monitor the primary side  $V_{\rm CC}$  voltage. When the 2.6 V threshold is exceeded, it will immediately turn off the Power Switch, and protect the load from a severe overvoltage condition. This input can also be driven from external circuitry to inhibit converter operation.

#### **Undervoltage Lockout**

An Undervoltage Lockout comparator has been incorporated to guarantee that the integrated circuit has sufficient voltage to be fully functional before the output stage is enabled. The UVLO comparator monitors the  $V_{\rm CC}$  voltage at Pin 3 and when it exceeds 14.5 V, the reset signal is removed from the PWM Latch allowing operation of the

Power Switch. To prevent erratic switching as the threshold is crossed, 5.0 V of hysteresis is provided.

#### **Startup Control**

An internal Startup Control circuit with a high voltage enhancement mode MOSFET is included within the MC33362. This circuitry allows for increased converter efficiency by eliminating the external startup resistor, and its associated power dissipation, commonly used in most off–line converters that utilize a UC3842 type of controller. Rectified ac line voltage is applied to the Startup Input, Pin 1. This causes the MOSFET to enhance and supply internal bias as well as charge current to the V<sub>CC</sub> bypass capacitor that connects from Pin 3 to ground. When V<sub>CC</sub> reaches the UVLO upper threshold of 14.5 V, the IC commences operation and the startup MOSFET is turned off. Operating bias is now derived from the auxiliary transformer winding, and all of the device power is efficiently converted down from the rectified ac line.

The startup MOSFET will provide an initial peak current of 55 mA, Figure 11, which decreases rapidly as  $V_{\rm CC}$  and the die temperature rise. The steady state current will self limit in the range of 12 mA with  $V_{CC}$  shorted to ground. The startup MOSFET is rated at a maximum of 250 V with  $V_{\rm CC}$  shorted to ground, and 400 V when charging a  $V_{\rm CC}$  capacitor of 1000  $\mu F$  or less.

#### Regulator

A low current 6.5 V regulated output is available for biasing the Error Amplifier and any additional control system circuitry. It is capable of up to 10 mA and has short–circuit protection. This output requires an external bypass capacitor of at least 1.0  $\mu F$  for stability.

#### Thermal Shutdown and Package

Internal thermal circuitry is provided to protect the Power Switch in the event that the maximum junction temperature is exceeded. When activated, typically at 155°C, the Latch is forced into a 'reset' state, disabling the Power Switch. The Latch is allowed to 'set' when the Power Switch temperature falls below 145°C. This feature is provided to prevent catastrophic failures from accidental device overheating. It is not intended to be used as a substitute for proper heatsinking.

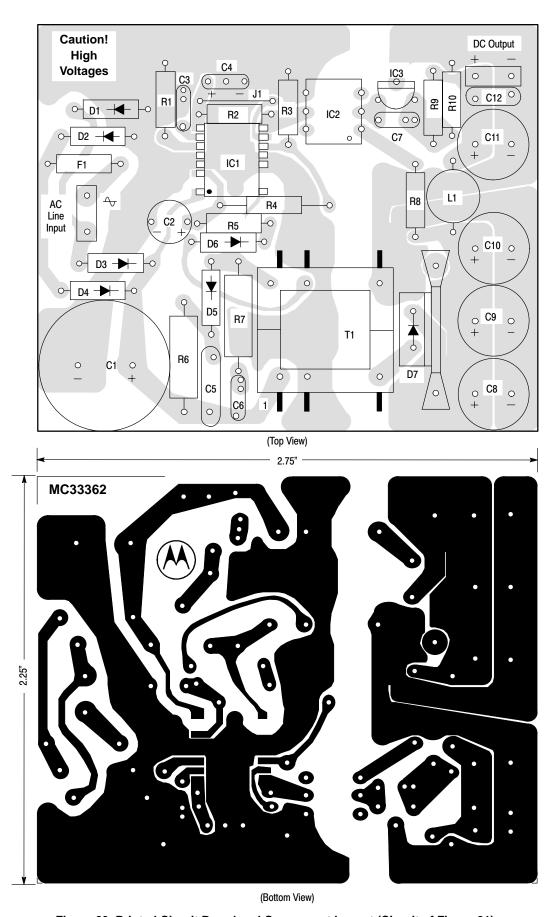

The MC33362 is contained in a heatsinkable plastic dual—in—line package in which the die is mounted on a special heat tab copper alloy lead frame. This tab consists of the four center ground pins that are specifically designed to improve thermal conduction from the die to the circuit board. Figures 16 and 17 show a simple and effective method of utilizing the printed circuit board medium as a heat dissipater by soldering these pins to an adequate area of copper foil. This permits the use of standard layout and mounting practices while having the ability to halve the junction to air thermal resistance. The examples are for a symmetrical layout on a single—sided board with two ounce per square foot of copper. Figure 23 shows a practical example of a printed circuit board layout

that utilizes the copper foil as a heat dissipater. Note that a jumper was added to the layout from Pins 8 to 10 in order to enhance the copper area near the device for improved thermal

conductivity. The application circuit requires two ounce copper foil in order to obtain 20 watts of continuous output power at room temperature.

Figure 21. 20 W Off-Line Converter

| Test            | Conditions                                                 | Results                                 |

|-----------------|------------------------------------------------------------|-----------------------------------------|

| Line Regulation | V <sub>in</sub> = 92 Vac to 138 Vac, I <sub>O</sub> 4.0 A  | $\Delta$ = 1.0 mV                       |

| Load Regulation | V <sub>in</sub> = 115 Vac, I <sub>O</sub> = 1.0 A to 4.0 A | $\Delta$ = 9.0 mV                       |

| Output Ripple   | V <sub>in</sub> = 115 Vac, I <sub>O</sub> = 4.0 A          | Triangular = 10 mVpp<br>Spike = 60 mVpp |

| Efficiency      | V <sub>in</sub> = 115 Vac, I <sub>O</sub> = 4.0 A          | 78.4%                                   |

This data was taken with the components listed below mounted on the printed circuit board shown in Figure 23. For high efficiency and small circuit board size, the Sanyo Os-Con capacitors are recommended for C8, Č9, C10 and C11. C8, C9, C10 = Sanyo Os-Con #6SA330M, 330 μF 6.3 V.

C11 = Sanyo Os-Con #10SA220M, 220 µF 10 V.

D7 = MBR2515L mounted on Aavid #592502B03400 heatsink.

L1 = Coilcraft S5088–A, 5.0  $\mu$ H, 0.11  $\Omega$ .

T1 = Coilcraft S5069-A

Primary: 58 turns of # 26 AWG, Pin 1 = start, Pin 8 = finish.

Two layers 0.002" Mylar tape.

Secondary: 4 turns of # 18 AWG, 2 strands bifiliar wound, Pin 5 = start, Pin 4 = finish.

Two layers 0.002" Mylar tape

Auxiliary: 10 turns of # 26 AWG wound in center of bobbin, Pin 2 = start, Pin 7 = finish.

Two layers 0.002" Mylar tape.

Gap: 0.014" total for a primary inductance (LP) of 330 μH.

Core and Bobbin: Coilcraft PT1950, E187, 3F3 material.

Figure 22. Converter Test Data

Figure 23. Printed Circuit Board and Component Layout (Circuit of Figure 21)

#### **PACKAGE DIMENSIONS**

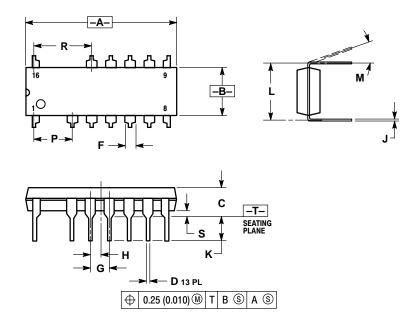

#### PDIP-16 **P SUFFIX** CASE 648E-01 ISSUE O

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL.

4. DIMENSION A AND B DOES NOT INCLUDE MOLD PROTRUSION.

5. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.25 (0.010).

6. ROUNDED CORNER OPTIONAL.

|     | INCHES    |       | MILLIN   | IETERS |

|-----|-----------|-------|----------|--------|

| DIM | MIN       | MAX   | MIN      | MAX    |

| Α   | 0.740     | 0.760 | 18.80    | 19.30  |

| В   | 0.245     | 0.260 | 6.23     | 6.60   |

| С   | 0.145     | 0.175 | 3.69     | 4.44   |

| D   | 0.015     | 0.021 | 0.39     | 0.53   |

| F   | 0.050     | 0.070 | 1.27     | 1.77   |

| G   | 0.100 BSC |       | 2.54 BSC |        |

| Н   | 0.050     | BSC   | 1.27 BSC |        |

| J   | 0.008     | 0.015 | 0.21     | 0.38   |

| K   | 0.120     | 0.140 | 3.05     | 3.55   |

| L   | 0.295     | 0.305 | 7.50     | 7.74   |

| M   | 0 °       | 10°   | 0 °      | 10°    |

| P   | 0.200 BSC |       | 5.08 BSC |        |

| R   | 0.300 BSC |       | 7.62 BSC |        |

| S   | 0.015     | 0.035 | 0.39     | 0.88   |

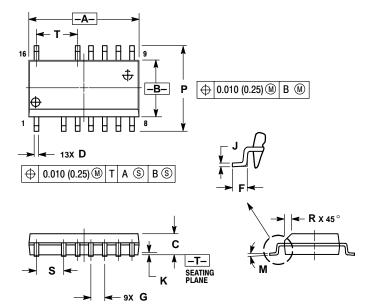

#### SO-16W **DW SUFFIX** CASE 751N-01 ISSUE O

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

- 5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR

PROTRUSION. ALLOWABLE DAMBAR

PROTRUSION SHALL BE 0.13 (0.005) TOTAL IN

EXCESS OF D DIMENSION AT MAXIMUM

MATERIAL CONDITION.

|     | MILLIMETERS |       | INCHES     |       |

|-----|-------------|-------|------------|-------|

| DIM | MIN         | MAX   | MIN        | MAX   |

| Α   | 10.15       | 10.45 | 0.400      | 0.411 |

| В   | 7.40        | 7.60  | 0.292      | 0.299 |

| С   | 2.35        | 2.65  | 0.093      | 0.104 |

| D   | 0.35        | 0.49  | 0.014      | 0.019 |

| F   | 0.50        | 0.90  | 0.020      | 0.035 |

| G   | 1.27 BSC    |       | 0.050 BSC  |       |

| J   | 0.25        | 0.32  | 0.010 0.01 |       |

| K   | 0.10        | 0.25  | 0.004      | 0.009 |

| M   | 0 °         | 7 °   | 0 °        | 7°    |

| P   | 10.05       | 10.55 | 0.395      | 0.415 |

| R   | 0.25        | 0.75  | 0.010      | 0.029 |

| S   | 2.54 BSC    |       | 0.100 BSC  |       |

| T   | 3.81 BSC    |       | 0.150 BSC  |       |

## **Notes**

## **Notes**

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### **PUBLICATION ORDERING INFORMATION**

#### NORTH AMERICA Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

**Phone**: 303–675–2175 or 800–344–3860 Toll Free USA/Canada **Fax**: 303–675–2176 or 800–344–3867 Toll Free USA/Canada

Email: ONlit@hibbertco.com

Fax Response Line: 303-675-2167 or 800-344-3810 Toll Free USA/Canada

#### N. American Technical Support: 800-282-9855 Toll Free USA/Canada

EUROPE: LDC for ON Semiconductor - European Support

German Phone: (+1) 303–308–7140 (Mon–Fri 2:30pm to 7:00pm CET)

Email: ONlit-german@hibbertco.com

French Phone: (+1) 303–308–7141 (Mon–Fri 2:00pm to 7:00pm CET)

Email: ONlit-french@hibbertco.com

English Phone: (+1) 303–308–7142 (Mon–Fri 12:00pm to 5:00pm GMT)

Email: ONlit@hibbertco.com

#### EUROPEAN TOLL-FREE ACCESS\*: 00-800-4422-3781

\*Available from Germany, France, Italy, UK, Ireland

#### CENTRAL/SOUTH AMERICA:

Spanish Phone: 303-308-7143 (Mon-Fri 8:00am to 5:00pm MST)

Email: ONlit-spanish@hibbertco.com

Toll-Free from Mexico: Dial 01-800-288-2872 for Access -

then Dial 866-297-9322

ASIA/PACIFIC: LDC for ON Semiconductor – Asia Support

**Phone**: 1–303–675–2121 (Tue–Fri 9:00am to 1:00pm, Hong Kong Time)

Toll Free from Hong Kong & Singapore:

001-800-4422-3781 Email: ONlit-asia@hibbertco.com

JAPAN: ON Semiconductor, Japan Customer Focus Center 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–0031

**Phone**: 81–3–5740–2700 **Email**: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local

Sales Representative.