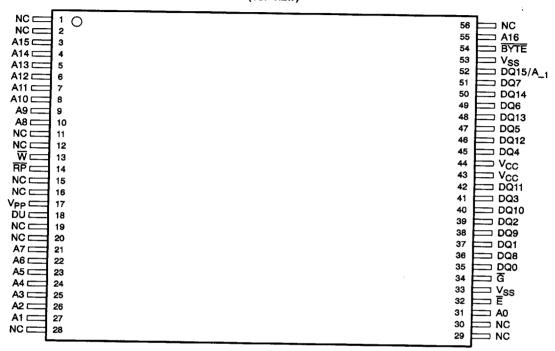

| Organization     Two 8K-Byte Parameter Blocks                                               | DBJ PACKAGE<br>(TOP VIEW)                                             |

|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| <ul> <li>One 96K-Byte Main Block</li> <li>One 128K-Byte Main Block</li> </ul>               | V <sub>PP</sub> [1 44] <del>RP</del><br>NC [2 43] W                   |

| <ul> <li>One 16K-Byte Protected Boot Block</li> <li>Top or Bottom Boot Locations</li> </ul> | NC 03 421 A8<br>A7 04 411 A9                                          |

| All Inputs/Outputs TTL Compatible     All Inputs/Outputs TTL Compatible                     | A6 0 5 40 0 A10<br>A5 0 6 39 0 A11<br>A4 0 7 38 0 A12                 |

| ● Maximum Access/Minimum Cycle Time  VCC ± 5% VCC ± 10%                                     | A4 [ 7 38 ] A12<br>A3 [ 8 37 ] A13<br>A2 [ 9 36 ] A14                 |

| '28F200BZ-6-x 60 ns<br>'28F200BZ-70-x 70 ns                                                 | A1 ( 10 35 ) A15<br>A0 ( 11 34 ) A16                                  |

| '28F200BZ-80-x 80 ns<br>'28F200BZ-90-x 90 ns                                                | Ē (12 33) <u>BYTĒ</u><br>V <sub>SS</sub> (13 32) V <sub>SS</sub>      |

| 100000 and 10000 Program/Erase Cycle<br>Versions                                            | G ( 14 31 ) DQ15/A <sub>-1</sub> DQ0 ( 15 30 ) DQ7 DQ8 ( 16 29 ) DQ14 |

| Three Temperature Ranges Commercial 0°C to 70°C                                             | DQ1 (17 28) DQ6<br>DQ9 (18 27) DQ13                                   |

| <ul><li>Extended 40°C to 85°C</li><li>Automotive 40°C to 125°C</li></ul>                    | DQ2 0 19 26 0 DQ5<br>DQ10 0 20 25 0 DQ12                              |

| ● Low Power Dissipation (V <sub>CC</sub> = 5.5 V)  - Active Write 330 mW (Byte Write)       | DQ3 (21 24) DQ4<br>DQ11 (22 23) V <sub>CC</sub>                       |

| - Active Read 330 mW (Byte Read)                                                            | DIN NOMENCI ATURE                                                     |

| ı |          | PIN NOMENCLATURE                    |

|---|----------|-------------------------------------|

| l | A0-A16   | Address Inputs                      |

| ۱ | BYTE     | Byte Enable                         |

| ١ | DQ0-DQ14 | Data In/Out                         |

| ļ | DQ15/A_1 | Data In/Out (word-wide mode),       |

| ١ |          | Low-Order Address (byte-wide mode)  |

| ı | DU       | Do Not Use                          |

| ļ | Ē        | Chip Enable                         |

| ١ | G        | Output Enable                       |

| ı | NC       | No Internal Connection              |

| į | RP       | Reset/Deep Power-Down               |

| I | Vcc      | 5-V Power Supply                    |

| 1 | VPP      | 12-V Power Supply for Program/Erase |

|   | Vss      | Ground                              |

| l | ₩        | Write Enable                        |

|   |          |                                     |

#### description

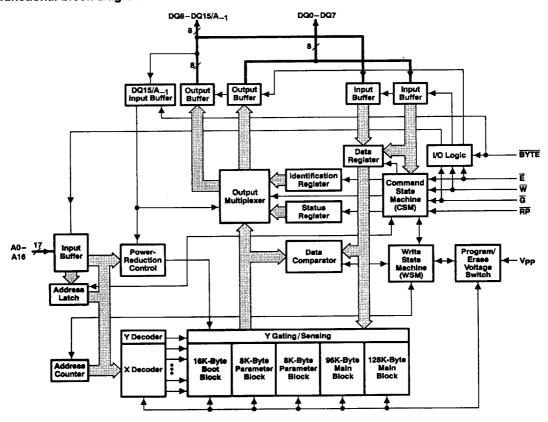

The TMS28F200BZx is a 2097152-bit, boot-block flash memory that can be electrically block erased and reprogrammed. The TMS28F200BZx is organized in a blocked architecture consisting of one 16K-byte protected boot block, two 8K-byte parameter blocks, one 96K-byte main block, and one 128K-byte main block. The device can be ordered with either a top or bottom boot-block configuration. Operation as a 256K-byte (8-bit) or a 128K-word (16-bit) organization is user-definable.

Embedded program and block-erase functions are fully automated by an on-chip write state machine (WSM), simplifying these operations and relieving the system microcontroller of these secondary tasks. WSM status can be monitored by an on-chip status register to determine progress of program/erase tasks. The device features user-selectable block erasure.

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

Active Write . . . 358 mW (Word Write)

Active Read . . . 330 mW (Word Read)

- Standby . . . 0.55 mW (CMOS-Input

Deep Power-Down Mode . . . 0.0066 mW

Fully Automated On-Chip Erase and Word/Byte Program Operations

Write Protection for Boot Block

Command State Machine (CSM)

Erase Suspend/Resume

Algorithm-Selection Identifier

- Block Erase . . . 165 mW

Levels)

Copyright © 1995, Texas Instruments Incorporated

7-87

#### description (continued)

The TMS28F200BZx flash memory is offered in a 44-pin PSOP and a 56-pin TSOP package. It is available in three temperature ranges:  $0^{\circ}$ C to  $70^{\circ}$ C,  $-40^{\circ}$ C to  $85^{\circ}$ C, and  $-40^{\circ}$ C to  $125^{\circ}$ C.

#### DBR PACKAGE (TOP VIEW)

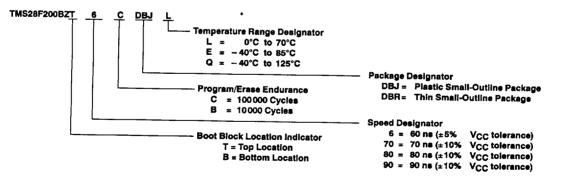

#### device symbol nomenclature

POST OFFICE BOX 1443 \* HOUSTON, TEXAS 77251-1443

8961725 0085582 035 🗖

7-88

Powered by ICminer.com Electronic-Library Service CopyRight 2003

ADVANCE INFORMATION

#### functional block diagram

#### architecture

The TMS28F200BZx uses a blocked architecture to allow independent erasure of selected memory blocks. Any address within a block address range selects that block for the required read, program, or erase operation.

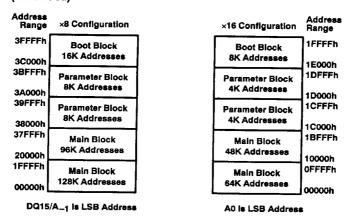

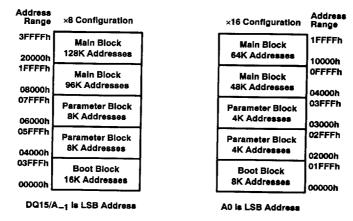

#### block memory maps

The TMS28F200BZx is available with the block architecture mapped in either of two configurations: the boot block located at the top or at the bottom of the memory array, as required by different microprocessors. The TMS28F200BZB (bottom boot block) is mapped with the 16K-byte boot block located at the low-order address range (00000h to 01FFFh). The TMS28F200BZT (top boot block) is inverted with respect to the TMS28F200BZB with the boot block located at the high-order address range (1E000h to 1FFFFh). Both of these address ranges are for word-wide mode. Figure 2 and Figure 3 show the memory maps for these configurations.

POST OFFICE BOX 1443 \* HOUSTON, TEXAS 77251-1443

#### block memory maps (continued)

Figure 1. TMS28F200BZT (Top Boot Block) Memory Map

Figure 2. TMS28F200BZB (Bottom Boot Block) Memory Map

#### boot-block data protection

The 16K-byte boot block is used to store key system data that is seldom changed in normal operation. To protect data within this memory sector, the  $\overline{RP}$  terminal can be used to provide a lockout to eliminate accidental erase or program operations. When  $\overline{RP}$  is operated with normal TTL/CMOS logic levels, the contents of the boot block cannot be erased or reprogrammed. Changes to the contents of the boot block can be made only when  $\overline{RP}$  is at  $V_{HH}$  (nominally 12 V) during normal write/erase operations.

#### parameter block

7-90

Two parameter blocks of 8K bytes each can be used like a scratch pad to store frequently updated data. Alternately, the parameter blocks can be used for additional boot- or main-block data. If a parameter block is used to store additional boot-block data, caution should be exercised because the parameter block does not have the boot-block data-protection safety feature.

POST OFFICE BOX 1443 \* HOUSTON, TEXAS 77251-1443

8961725 0085584 908 🖿

## **ADVANCE INFORMATION**

Primary memory on the TMS28F200BZx is located in two main blocks. One of the blocks has storage capacity of 128K bytes and the other block has storage capacity of 96K bytes.

#### command state machine (CSM)

The CSM is the interface between an external microprocessor and the write state machine and status register on the memory chip. When the WSM has completed a task, the WSM status (WSMS) bit (SB7) is set to a logic high (1), allowing the CSM to respond to the full command set.

#### status register (SR)

The status register provides a means of determining whether the state of a program/erase operation is pending or complete. The status register is read by writing a read-status command to the CSM and reading the resulting status code on I/O terminals DQ0—DQ7. This is valid for operation in either the byte- or word-wide mode. When the device is operating in the word-wide mode, the high order I/Os (DQ8—DQ15) are set to 00h when performing a read-status operation.

After a read-status command has been given, the data appearing on DQ0-DQ7 remains as the status register data until a new command is issued to the CSM. To return the device to other modes of operation, a new command must be issued to the CSM.

Register data is updated on the falling edge of  $\overline{G}$  or  $\overline{E}$ . The latest falling edge of either of these two signals updates the latch within a given read cycle. Latching data prevents errors from occurring should the register input change during a status-register read. To assure that the status-register output contains updated status data,  $\overline{E}$  or  $\overline{G}$  must be toggled for each subsequent status read.

The status register provides the internal state of the WSM to the external microprocessor. During periods when the WSM is active, the status register can be polled to determine the WSMS. Table 1 defines the status register bits and their functions.

#### status register (SR) (continued)

Table 1. Status Register Bit Definitions and Functions

| STATUS<br>BIT | FUNCTION                      | DATA                                                         | COMMENTS                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|-------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |                               | 1 = Ready<br>0 = Busy                                        | If SB7 = 0, the WSM has not completed an erase or programming operation. If SB7 = 1 (ready), other polling operations can be performed. SB7 does not automatically update WSM status at the completion of a WSM task. If the WSM status bit shows busy (0), the user must periodically toggle $\overline{\bf E}$ or $\overline{\bf G}$ to determine when the WSM has completed an operation (SB7 = 1). |

| SB6           | Erase-suspend status<br>(ESS) | 1 = Erase suspended<br>0 = Erase in progress or<br>completed | When an erase-suspend command is issued, the WSM halts execution and sets the ESS bit high (SB6 = 1) indicating that the erase operation has been suspended. The WSMS bit is also set high (SB7 = 1) indicating that the erase-suspend operation has been successfully completed. The ESS bit remains at a high level until an erase-resume command is input to the CSM (code Doh).                    |

| SB5           | Erase status<br>(ES)          | 1 = Block erase error<br>0 = Block erase good                | SB5 = 0 indicates that a successful block erasure has occurred. SB5 = 1 indicates that an erase error has occurred. In this case, the WSM has completed the maximum allowed erase pulses determined by the internal algorithm, but this was insufficient to completely erase the device.                                                                                                               |

| SB4           | Program status<br>(PS)        | 1 = Byte/word program error<br>0 = Byte/word program good    | SB4 = 0 indicates successful programming has occurred at the addressed block location. SB4 = 1 indicates that the WSM was unable to correctly program the addressed block location.                                                                                                                                                                                                                    |

| SB3           | Vpp status<br>(Vpps)          | 1 = Program abort:<br>Vpp too low<br>0 = Vpp good            | SB3 provides information on the status of Vpp during programming. If Vpp is too lowafter a program or erase command has been issued, SB3 is set to a 1 indicating that the programming operation is aborted. The Vpp status bit is not assured to give accurate feedback between VppH and VppL.                                                                                                        |

| SB2-<br>SB0   | Reserved                      |                                                              | These bits should be masked out when reading the status register.                                                                                                                                                                                                                                                                                                                                      |

#### operation

Device operations are selected by entering standard JEDEC 8-bit command codes with conventional microprocessor timing into an on-chip command state machine (CSM) through I/O terminals DQ0-DQ7. When the device is powered up, internal reset circuitry initializes the chip to a read-array mode of operation. Changing the mode of operation requires a command code to be entered into the CSM. Table 2 lists the CSM codes for all modes of operation.

The on-chip status register allows the progress of various operations to be monitored. The status register is interrogated by entering a read-status-register command into the CSM (cycle 1) and reading the register data on I/O terminals DQ0-DQ7 (cycle 2). Status-register bits SB0 through SB7 correspond to DQ0 through DQ7.

TEXAS INSTRUMENTS POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251-1443

7-92

8961725 0085586 780

#### operation (continued)

Table 2. Command State Machine Codes for Device Mode Selection

| COMMAND<br>CODE ON<br>DQ0-DQ7 <sup>†</sup> | DEVICE MODE                      |

|--------------------------------------------|----------------------------------|

| 00h                                        | Invalid/Reserved                 |

| 10h                                        | Alternate Program Setup          |

| 20h                                        | Block-Erase Setup                |

| 40h                                        | Program Setup                    |

| 50h                                        | Clear-Status Register            |

| 70h                                        | Read-Status Register             |

| 90h                                        | Algorithm Selection              |

| Boh                                        | Erase Suspend                    |

| DOh                                        | Erase Resume/Block-Erase Confirm |

| FFh                                        | Read Array                       |

<sup>†</sup> DQ0 is the least significant bit. DQ8 - DQ15 are any valid 2-state level.

#### command definition

Once a specific command code has been entered, the WSM executes an internal algorithm generating the necessary timing signals to program, erase, and verify data. See Table 3 for the CSM command definitions and data for each of the bus cycles.

Following the read-algorithm-selection-code command, two read cycles are required to access the manufacturer-equivalent code and the device-equivalent code as shown in Table 4 and Table 5.

**Table 3. Command Definitions**

|                                           | BUS    | FIRS      | T BUS CYCL | SECOND BUS CYCLE |           |         |                |

|-------------------------------------------|--------|-----------|------------|------------------|-----------|---------|----------------|

| COMMAND                                   | CYCLES | OPERATION | ADDRESS    | CSM<br>INPUT     | OPERATION | ADDRESS | DATA<br>IN/OUT |

| · · · · · · · · · · · · · · · · · · ·     |        | Read O    | perations  |                  |           |         |                |

| Read Array                                | 1 1    | Write     | X          | FFh              | Read      | Х       | Data Out       |

| Read Algorithm-Selection Code             | 3      | Write     | Х          | 90h              | Read      | A0      | M/D            |

| Read-Status Register                      | 2      | Write     | X          | 70h              | Read      | Х       | SRB            |

| Clear-Status Register                     | 1      | Write     | Х          | 50h              |           |         |                |

|                                           |        | Progra    | m Mode     |                  |           |         |                |

| Program Setup/Program (byte/word)         | 2      | Write     | PA         | 40h or 10h       | Write     | PA      | PD             |

|                                           |        | Erase C   | perations  |                  |           |         |                |

| Block-Erase Setup/<br>Block-Erase Confirm | 2      | Write     | BEA        | 20h              | Write     | BEA     | DOh            |

| Erase Suspend/<br>Erase Resume            | 2      | Write     | ×          | B0h              | Write     | x       | DOh            |

#### Legend:

BEA Block-erase address. Any address selected within a block selects that block for erase.

M/D Manufacturer-equivalent/device-equivalent code

PA Address to be programmed

PD Data to be programmed at PA

SRB Status-register data byte that can be found on DQ0-DQ7

POST OFFICE BOX 1443 \* HOUSTON, TEXAS 77251-1443

7-93

8961725 0085587 617

#### byte-wide or word-wide mode selection

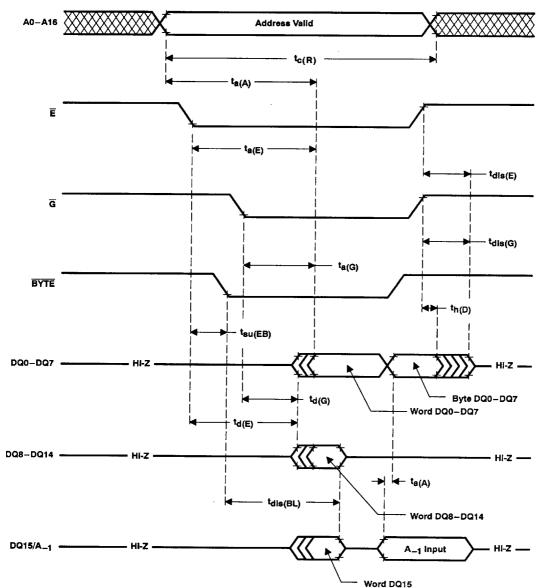

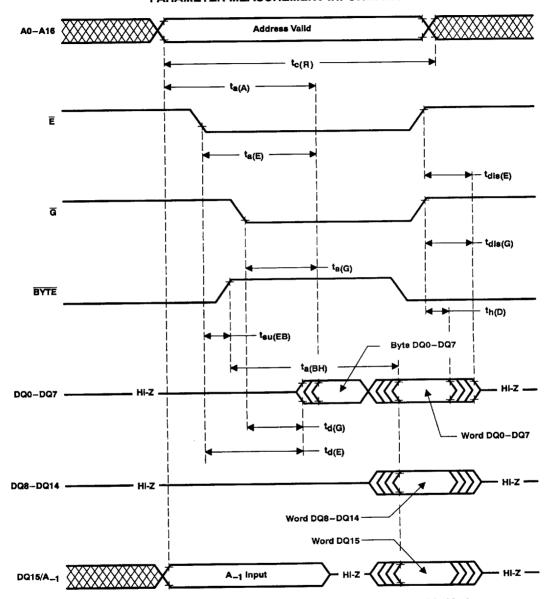

The memory array is divided into two parts: an upper half byte that outputs data through I/Os DQ8-DQ15, and a lower half byte that outputs data through DQ0-DQ7. Device operation in either byte-wide or word-wide mode is user-selectable and is determined by the logic state of BYTE. When BYTE is at a logic high level, the device is in the word-wide mode and data is written to or read from I/Os DQ0-DQ15. When BYTE is at a logic low, the device is in the byte-wide mode and data is written to or read from I/Os DQ0-DQ7. In the byte-wide mode, I/Os DQ8-DQ14 are placed in the high-impedance state and DQ15/A\_1 becomes the low-order address terminal and selects either the upper or lower half of the array. Array data from the upper half (DQ8-DQ15) and the lower half (DQ0-DQ7) are multiplexed and appear on DQ0-DQ7. Table 4 and Table 5 summarize operations for word-wide mode and byte-wide mode.

Table 4. Operation Modes for Word-Wide Mode ( $\overline{BYTE} = V_{IH}$ )

| MODE                     | Ē                | G               | RP            | W     | A9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | A0  | Vpp                                     | DQ0-DQ15                                            |

|--------------------------|------------------|-----------------|---------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------|-----------------------------------------------------|

| Read                     | V <sub>IL</sub>  | V <sub>IL</sub> | ViH           | ViH   | ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ×   | ×                                       | Data out                                            |

|                          | _V <sub>IL</sub> | VIL             | VIH           | VIH   | VID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VIL | X                                       | Manufacturer-equivalent code 0089h                  |

| Algorithm-selection mode | V <sub>IL</sub>  | VIL             | ViH           | VIH   | VID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |                                         | Device-equivalent code 2274h<br>(top boot block)    |

|                          |                  | · 1L            | VIII          | VIH . | \ \dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymbol{\dolsymb | VIH |                                         | Device-equivalent code 2275h<br>(bottom boot block) |

| Output disable           | V <sub>IL</sub>  | VIH             | VIH           | VIH   | X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | X   | X                                       | High impedance                                      |

| Standby                  | VIH              | Х               | VIH           | х     | Х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Х   | X                                       | High impedance                                      |

| Reset/deep power down    | Х                | X               | VIL           | х     | Х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Х   | ×                                       | High Impedance                                      |

| Write (see Note 1)       | VIL              | VIH             | VIH or<br>VHH | VIL   | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ×   | V <sub>PPL</sub> or<br>V <sub>PPH</sub> |                                                     |

Table 5. Operation Modes for Byte-Wide Mode (BYTE = VIL)

| MODE                     | Ē               | Ğ   | RP                        | W               | A9              | A0   | Vpp                | DQ15/A_1 | DQ8-DQ14 | DQ0~DQ7                                           |                                                |

|--------------------------|-----------------|-----|---------------------------|-----------------|-----------------|------|--------------------|----------|----------|---------------------------------------------------|------------------------------------------------|

| Read lower byte          | VIL             | VIL | VIH                       | VIH             | Х               | X    | ×                  | VIL      | Hi-Z     | Data out                                          |                                                |

| Read upper byte          | VIL             | VIL | VIH                       | V <sub>IH</sub> | Х               | Х    | Х                  | VIH      | Hi-Z     | Data out                                          |                                                |

|                          | VIL             | VIL | VIH                       | VIH             | V <sub>ID</sub> | VIL  | х                  | х        | Hi-Z     | Manufacturer-equivalent code 89h                  |                                                |

| Algorithm-selection mode | V <sub>IL</sub> | VIL | ViH                       | VIH             | VID             | V    | ViH                | ×        | x        |                                                   | Device-equivalent code<br>74h (top boot block) |

|                          |                 | 16  |                           | - 111           | טוי             | VIII |                    |          | Hi-Z     | Device-equivalent code<br>75h (bottom boot block) |                                                |

| Output disable           | VIL             | VIH | VIH                       | VIH             | X               | Х    | Х                  | х        | Hi-Z     | High impedance                                    |                                                |

| Standby                  | ViH             | X   | ViH                       | Х               | Х               | ×    | Х                  | Х        | Hi-Z     | High impedance                                    |                                                |

| Reset/deep power down    | x               | X   | VIL                       | х               | х               | х    | х                  | ×        | Hi-Z     | High impedance                                    |                                                |

| Write (see Note 1)       | VIL             | ۸iH | V <sub>IH</sub> or<br>VHH | V <sub>IL</sub> | x               | X    | VPPH<br>Or<br>VPPL | x        | Hi-Z     | Data in                                           |                                                |

mmands to the '28F200BZx, Vpp must be VppH for block-erase or program commands to be executed and RP must be held at VHH for the entire boot block program or erase operation.

POST OFFICE BOX 1443 \* HOUSTON, TEXAS 77251-1443

8961725 0085588 553

#### command state machine (CSM) operations

The CSM decodes instructions for read, read algorithm-selection code, read status register, clear status register, program, erase, erase suspend, and erase resume. The 8-bit command code is input to the device on DQ0—DQ7 (see Table 2 for CSM codes). During a program or erase cycle, the CSM informs the WSM that a program or erase cycle has been requested. During a program cycle, the WSM controls the program sequences and the CSM responds only to status reads.

During an erase cycle, the CSM responds to status reads and erase suspend. When the WSM has completed its task, the WSM status bit (SB7) is set to a logic high and the CSM responds to the full command set. The CSM stays in the current command state until the microprocessor issues another command.

The WSM successfully initiates an erase or program operation only when  $V_{PP}$  is within its correct voltage range  $(V_{PPH})$ . For data protection, it is recommended that  $\overline{RP}$  be held at a logic low during a CPU reset.

#### read operations

There are three read operations available: read array, read algorithm-selection code, and read status register.

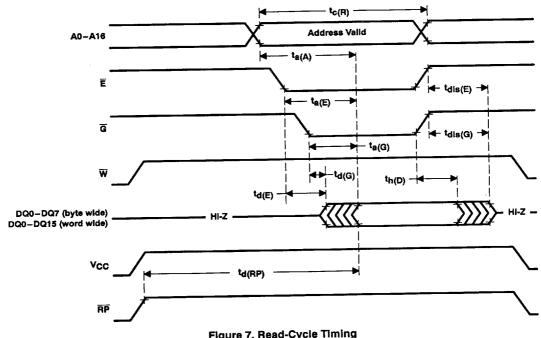

#### read array

The array is read by entering the command code FFh on DQ0-DQ7. Control terminals  $\overline{E}$  and  $\overline{G}$  must be at a logic low (V<sub>IL</sub>) and  $\overline{W}$  and  $\overline{RP}$  must be at a logic high (V<sub>IH</sub>) to read data from the array. Data is available on DQ0-DQ15 (word-wide mode) or DQ0-DQ7 (byte-wide mode). Any valid address within any of the blocks selects that block and allows data to be read from the block.

#### read algorithm-selection code

Algorithm-selection codes are read by entering command code 90h on DQ0-DQ7. Two bus cycles are required for this operation: the first to enter the command code and a second to read the device-equivalent code. Control terminals  $\overline{E}$  and  $\overline{G}$  must be at a logic low  $(V_{IL})$  and  $\overline{W}$  and  $\overline{RP}$  must be at a logic high  $(V_{IH})$ . Two identifier bytes are accessed by toggling A0. The manufacturer-equivalent code is obtained on DQ0-DQ7 with A0 at a logic low  $(V_{IL})$ . The device-equivalent code is obtained when A0 is set to a logic high  $(V_{IH})$ . Alternately, the manufacturer- and device-equivalent codes can be read by applying  $V_{ID}$  (nominally 12 V) to A9 and selecting the desired code by toggling A0 high or low. All other addresses are don't care (see Table 3, Table 4, and Table 5).

#### read status register

The status register is read by entering the command code 70h on DQ0-DQ7. Control terminals  $\overline{E}$  and  $\overline{G}$  must be at a logic low (V<sub>IL</sub>) and  $\overline{W}$  and  $\overline{W}$  must be at a logic high (V<sub>IH</sub>). Two bus cycles are required for this operation: one to enter the command code and a second to read the status register. In a given read cycle, status register contents are updated on the falling edge of  $\overline{E}$  or  $\overline{G}$ , whichever occurs last within the cycle.

#### clear status register

The internal circuitry can set only the V<sub>PP</sub> status (SB3), the program status (SB4), and the erase status (SB5) bits of the status register. The clear-status-register command (50h) allows the external microprocessor to clear these status bits and synchronize to internal operations. When the status bits are cleared, the device returns to the read array mode.

#### boot-block programming/erasing

Should changes to the boot block be required,  $\overline{RP}$  must be set to  $V_{HH}$  (12 V) and  $V_{PP}$  to the programming voltage level ( $V_{PPH}$ ). If an attempt is made to write, erase, or erase suspend the boot block without  $\overline{RP}$  at  $V_{HH}$ , an error signal is generated on SB4 (program-status bit) or SB5 (erase-status bit).

A program-setup command can be aborted by writing FFh (in byte-wide mode) or FFFFh (in word-wide mode) during the second cycle. After writing FFh or FFFFh during the second cycle, the CSM responds only to status reads. When the WSM status bit (SB7) is set to a logic high, signifying termination of the nonprogram operation is terminated, all commands to the CSM become valid again.

POST OFFICE BOX 1443 \* HOUSTON, TEXAS 77251-1443

7-95

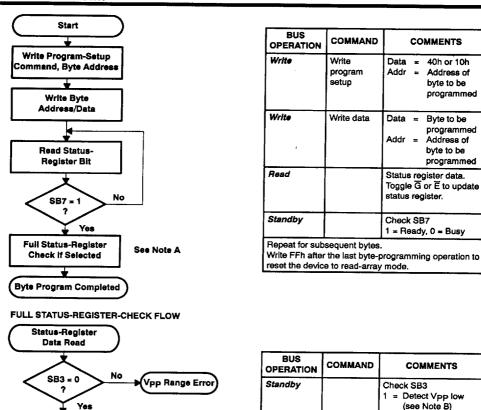

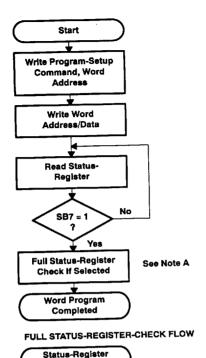

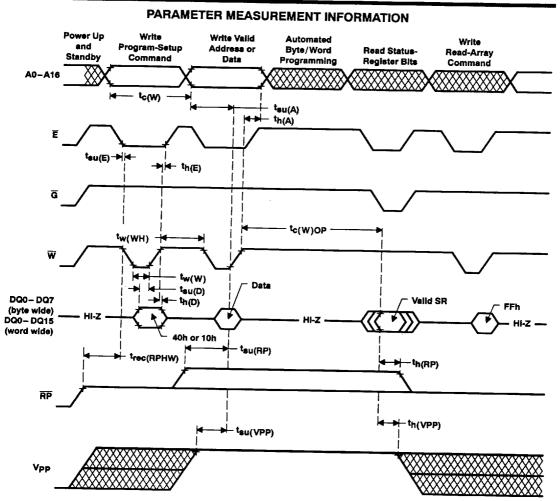

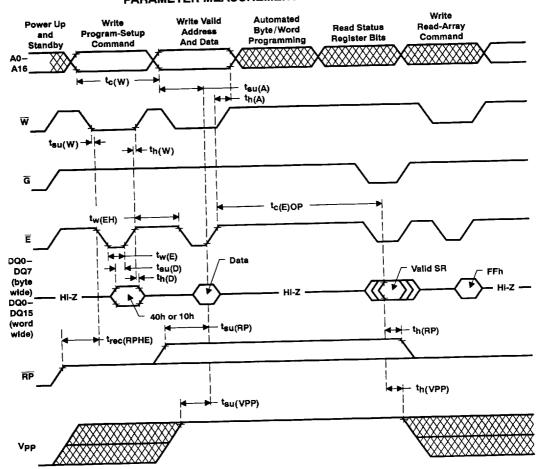

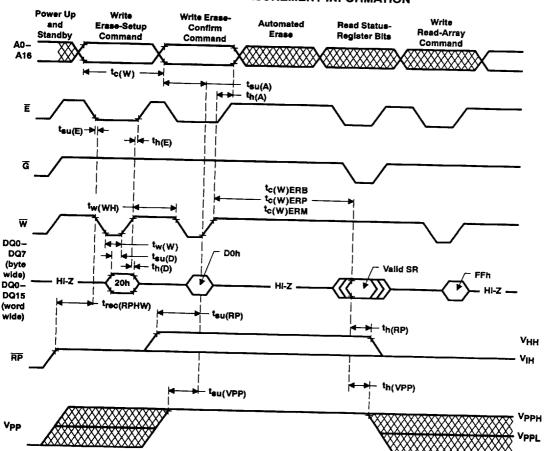

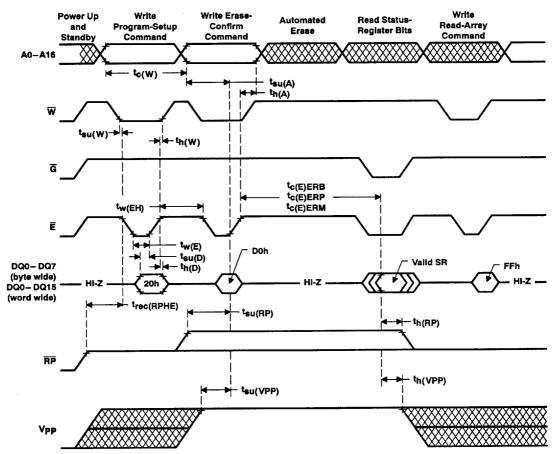

#### normai programming

There are two CSM commands for programming: program setup and alternate program setup (see Table 2 on page 7). After the desired command code is entered, the WSM takes over and correctly sequences the device to complete the program operation. During this time, the CSM responds only to status reads until the program operation has been completed, after which all commands to the CSM become valid again. Once a program command has been issued, the WSM cannot normally be interrupted until the program algorithm is completed (see Figure 4 and Figure 4). Taking  $\overline{\text{RP}}$  to  $\text{V}_{\text{IL}}$  during programming aborts the program operation. During programming,  $\text{V}_{\text{PP}}$  must remain at  $\text{V}_{\text{PPH}}$ . Only 0s are written and compared during a program operation. If 1s are programmed, the memory cell contents do not change and no error occurs.

A program-setup command can be aborted by writing FFh (in byte-wide mode) or FFFFh (in word-wide mode) during the second cycle. After writing all 1s during the second cycle, the CSM responds only to status reads. When the WSM status bit (SB7) is set to a logic high, signifying the nonprogram operation is terminated, all commands to the CSM become valid again.

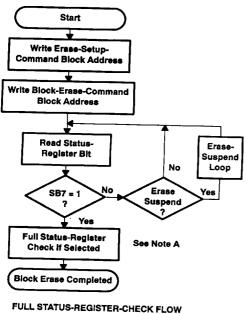

#### erase operations

There are two erase operations that can be performed by the TMS28F200BZx devices: block erase and erase suspend/erase resume. An erase operation must be used to initialize all bits in an array block to 1s. After block-erase confirm is issued, the CSM responds only to status reads or erase-suspend commands until the WSM completes its task.

#### block erasure

Block erasure inside the memory array sets all bits within the addressed block to logic 1s. Erasure is accomplished only by blocks; data at single address locations within the array cannot be individually erased. Any valid address within the parameter or main blocks acts as a block selector and allows that block to be erased.  $\overline{\text{RP}}$  must be at  $V_{\text{HH}}$  for changing the data content of the boot block. Block erasure is initiated by a command sequence to the CSM: block-erase setup (20h) followed by block-erase confirm (D0h). A two-command erase sequence protects against accidental erasure of memory contents.

Erase setup and confirm commands are latched on the rising edge of  $\overline{\mathbb{E}}$  or  $\overline{\mathbb{W}}$ , whichever occurs first. Block addresses are latched during the block-erase-confirm command on the rising edge of  $\overline{\mathbb{E}}$  or  $\overline{\mathbb{W}}$  (see Figure 5). When the block-erase-confirm command is complete, the WSM automatically executes a sequence of events to complete the block erasure. During this sequence, the block is programmed with logic 0s, data is verified, all bits in the block are erased, and finally, verification is performed to assure that all bits are correctly erased. Monitoring of the erase operation is possible through the status register (see read status register).

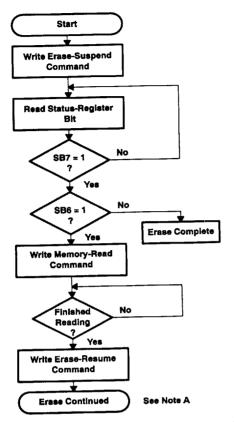

#### erase suspend/erase resume

During the execution of an erase operation, the erase-suspend command (B0h) can be entered to direct the WSM to suspend the erase operation. Once the WSM has reached the suspend state, it allows the CSM to respond only to the read-array, read-status-register, and erase-resume commands. During the erase-suspend operation, array data should be read from a block other than the one being erased. To resume the erase operation, an erase-resume command (D0h) must be issued to cause the CSM to clear the suspend state previously set (see Figure 5 and Figure 10).

#### automatic power-saving mode

Substantial power savings can be realized during periods when the array is not being read. During this time, the device switches to the automatic power-saving mode. When the device switches to this mode,  $I_{CC}$  is typically reduced from 40 mA to 1 mA ( $I_{OUT}$  = 0 mA). The low level of power is maintained until another read operation is initiated. In this mode, the I/O terminals retain the data from the last memory address read until a new address is read. This mode is entered automatically if no address or control pins toggle within a 200-ns time-out period. At least one transition on  $\overline{E}$  must occur after power up to activate this mode.

7-96

POST OFFICE BOX 1443 \* HOUSTON, TEXAS 77251-1443

8961725 0085590 101 ■

### reset/deep power-down mode

Very low levels of power consumption can be attained by using a special terminal,  $\overline{RP}$ , that disables internal device circuitry. When  $\overline{RP}$  is at a CMOS logic low of 0.0 V  $\pm$  0.2 V, an I<sub>CC</sub> value on the order of 0.2  $\mu$ A (or 1  $\mu$ W of power) is achievable. This is important in portable applications where extended battery life is of major concern.

A recovery time is required when exiting from deep power-down mode. For a read-array operation, a minimum of 300 ns is required before data is valid, and a minimum of 215 ns in deep power-down mode is required before data input to the CSM can be recognized. With  $\overline{RP}$  at ground, the WSM is reset and the status register is cleared, effectively eliminating accidental programming to the array during system reset. After restoration of power, the device does not recognize any operation command until  $\overline{RP}$  is returned to a  $V_{IH}$  or  $V_{HH}$  level.

Should  $\overline{\mathsf{RP}}$  become low during a program or erase operation, the device becomes nonfunctional (is in a power-down state) and data being written or erased is invalid or indeterminate, requiring that the operation be performed again after power restoration.

COMMENTS

40h or 10h

Address of

byte to be programmed

Byte to be programmed

Address of

programmed

byte to be

Status register data. Toggle G or E to update

1 = Ready, 0 = Busy

COMMENTS

(see Note B)

(see Note C)

= Byte program error

Check SB3 1 = Detect Vpp low

Check SB4

status register.

Check SB7

Data

Data

Addr

NOTES: A. Full status-register check can be done after each word or after a sequence of words.

No

SB4 = 0

Byte Program Passed

Yes

B. SB3 must be cleared before attempting additional program/erase operations. C. SB4 is cleared only by the clear-status-register command, but it does not prevent additional program operation attempts.

Standby

Byte Program

Falled

Figure 3. Automated Byte-Programming Flowchart

7-98

POST OFFICE BOX 1443 \* HOUSTON, TEXAS 77251-1443

8961725 OO85592 T84 🖿

**Word Program Passed**

| BUS<br>OPERATION | COMMAND                   | COMMENTS                                                                         |

|------------------|---------------------------|----------------------------------------------------------------------------------|

| Write            | Write<br>program<br>setup | Data = 40h or 10h Addr = Address of word to be programmed                        |

| Write            | Write data                | Data = Word to be<br>programmed<br>Addr = Address of<br>word to be<br>programmed |

| Read             |                           | Status register data. Toggle G or E to update status register.                   |

| Standby          |                           | Check SB7<br>1 = Ready, 0 = Busy                                                 |

Write FFh after the last word-programming operation to reset the device to read-array mode.

| s-Register<br>ta Read         | BUS     |

|-------------------------------|---------|

| <b>大</b>                      | OPERAT  |

| SB3 = 0 Vpp Range Error       | Standby |

| Yes                           | Standby |

| SB4 = 0   Word Program Failed |         |

| BUS<br>OPERATION | COMMAND | COMMENTS                                                |

|------------------|---------|---------------------------------------------------------|

| Standby          |         | Check SB3<br>1 = Detect Vpp low<br>(see Note B)         |

| Standby          |         | Check SB4<br>1 = Word program<br>failed<br>(see Note C) |

NOTES: A. Full status-register check can be done after each word or after a sequence of words.

B. SB3 must be cleared before attempting additional program/erase operations.

C. SB4 is cleared only by the clear-status-register command, but it does not prevent additional program operation attempts.

Figure 4. Automated Word-Programming Flowchart

POST OFFICE BOX 1443 \* HOUSTON, TEXAS 77251-1443

| BUS<br>OPERATION                                         | COMMAND              | СОММЕ                                                 | NTS                                           |

|----------------------------------------------------------|----------------------|-------------------------------------------------------|-----------------------------------------------|

| Write                                                    | Write erase<br>setup | Data = 20h<br>Block Addr =                            | Address<br>within<br>block to<br>be<br>erased |

| Write                                                    | Erase                | Data = D0h<br>Block Addr =                            | Address<br>within<br>block to<br>be<br>erased |

| Read                                                     |                      | Status register<br>Toggle G or E t<br>status register | data.<br>o update                             |

| Standby                                                  |                      | Check SB7<br>1 = Ready, 0 =                           | Busy                                          |

| Repeat for subs<br>Write FFh after t<br>device to read-a | he last block-ei     | rase operation to                                     | resetthe                                      |

Status-Register Data Read SB3 = 0 No **Vpp Range Error** Yes SB4 = 1 Yes Command Sequence SB5 = 1Error No SB5 = 0 No Block Erase Failed Yes **Block Erase Passed**

| BUS<br>OPERATION | COMMAND | COMMENTS                                              |

|------------------|---------|-------------------------------------------------------|

| Standby          |         | Check SB3<br>1 = Detect Vpp low<br>(see Note B)       |

| Standby          |         | Check SB4 and SB5<br>1 = Block-erase<br>command error |

| Standby          |         | Check SB5 1 = Block-erase failed (see Note C)         |

- NOTES: A. Full status-register check can be done after each word or after a sequence of words.

- B. SB3 must be cleared before attempting additional program/erase operations.

- C. SB5 is cleared only by the clear-status-register command in cases where multiple blocks are erased before full status is checked.

Figure 5. Automated Block-Erase Flowchart

7-100

POST OFFICE BOX 1443 \* HOUSTON, TEXAS 77251-1443

8961725 0085594 857 🖿

| BUS<br>OPERATION | COMMAND          | COMMENTS                                                       |

|------------------|------------------|----------------------------------------------------------------|

| Write            | Erase<br>suspend | Data = B0h                                                     |

| Read             |                  | Status register data. Toggle G or E to update status register. |

| Standby          |                  | Check SB7<br>1 = Ready                                         |

| Standby          |                  | Check SB6<br>1 = Suspended                                     |

| Write            | Read<br>memory   | Data = FFh                                                     |

| Read             |                  | Read data from block other than that being erased.             |

| Write            | Erase resume     | Data = D0h                                                     |

NOTE A: Refer to block-erase flowchart for complete erasure procedure.

Figure 6. Erase-Suspend/Resume Flowchart

TEXAS

INSTRUMENTS

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251-1443

7-101

ADVANCE INFORMATION

| sheetute marimum at                                                                                            |                                         |

|----------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| absolute maximum ratings over operating free-air tempera                                                       | ture range (unless ethanular and        |

| Supply voltage range, V <sub>CC</sub> (see Note 2) Supply voltage range, V <sub>DC</sub> (see Note 2)          | range (milless ofuetwise noted)         |

|                                                                                                                |                                         |

| Supply voltage range, Vpp (see Note 2)                                                                         |                                         |

| Supply voltage range, Vpp (see Note 2) Input voltage range: All inputs except A9, RP RP. A9 (see Note )        | ····· – 0.6 V to 14 V                   |

|                                                                                                                | 001/4-1/ 41/                            |

| nr, A9 (see Note )                                                                                             | -0.6 V to 13.5 V                        |

|                                                                                                                |                                         |

| Output voltage range (see Note 4) Operating free-air temperature range, T <sub>A</sub> , during read/erase/pro | ······ – 0.6 V to V <sub>CC</sub> + 1 V |

| TA, during read/erase/pro                                                                                      | gram: L sumix 0°C to 70°C               |

|                                                                                                                | E suffix 40°C to 85°C                   |

|                                                                                                                | O                                       |

| Storage temperature range, T <sub>stg</sub>                                                                    | 4 January 125°C                         |

|                                                                                                                | - 65°C to 150°C                         |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 2. All voltage values are with respect to VSS.

#### recommended operating conditions

|                  | <del></del>                            | T                                     |               | MIN                   | NOM | MAX                   | UNIT         |

|------------------|----------------------------------------|---------------------------------------|---------------|-----------------------|-----|-----------------------|--------------|

| Vcc              | Supply voltage                         | During write/read/erase/erase suspend | '28F200BZ-x-6 | 4.75                  | 5   | 5.25                  | -            |

|                  |                                        |                                       | All others    | 4.5                   | 5   | 5.5                   | V            |

| Vpp              | Supply voltage                         | During read only (VPPL)               |               | 0                     |     | 6.5                   | V            |

|                  | During write/erase/erase suspend (VPPH |                                       |               | 11.4                  | 12  | 12.6                  | V            |

| VIH              |                                        |                                       | TTL           | 2                     |     | V <sub>CC</sub> + 0.5 | V            |

|                  |                                        |                                       | CMOS          | V <sub>CC</sub> - 0.5 |     | V <sub>CC</sub> + 0.5 | V            |

| VIL              | Low-level dc inpu                      | rt voltage                            | TTL           | - 0.5                 |     | 0.8                   | v            |

| V <sub>LKO</sub> | Voc look out val                       |                                       | смоѕ          | V <sub>SS</sub> - 0.2 |     | V <sub>SS</sub> + 0.2 | <del>-</del> |

| VHH              | RP unlock voltage                      | age from write/erase                  |               | 2                     |     |                       | V            |

| -1114            | . II DINOCK VORAGI                     |                                       |               | 11.5                  | 12  | 13                    | V            |

### word/byte-write and block-erase performance, $T_A = 25$ °C, $V_{PP} = 12$ V (see Note 5)

|                          |              |         |     |               |      | ~   | -, -,         | L    | 100 | C 110(1       | 3 J) |       |      |

|--------------------------|--------------|---------|-----|---------------|------|-----|---------------|------|-----|---------------|------|-------|------|

| PARAMETER                | '28F200BZx-6 |         |     | '28F200BZx-70 |      |     | '28F200BZx-80 |      |     | '28F200BZx-90 |      |       | Г —  |

|                          | MIN          | TYP     | MAX | MIN           | TYP  | MAX | MIN           | TYP  | MAX | MIN           | TYP  | MAX   | UNIT |

| Main-block erase time    |              | 2.2     |     |               | 2.2  |     |               | 2.2  |     |               |      | MIACA |      |

| Main-block byte-program  |              |         |     |               |      |     |               | 2.2  |     |               | 2.2  |       | 8    |

| time                     |              | 3.2     | ĺ   |               | 3.2  | - 1 |               | 3.2  | i   |               | 3.2  |       | 8    |

| Main-block word-program  |              |         |     |               |      |     |               |      |     |               |      |       |      |

| time                     |              | 1.6     | - 1 |               | 1.6  | - 1 |               | 1.6  | }   |               | 1.6  |       |      |

| Parameter/boot-block     |              |         | +   |               |      |     |               |      | 1.6 |               |      | S     |      |

| erase time               |              | 0.32    | ı   |               | 0.32 |     |               | 0.32 | ľ   |               | 0.32 |       | s    |

| OTE 5: Excludes exetem I | aval avas    | h = = d |     |               |      |     |               |      |     |               | J.JL | - 1   | 3    |

7-102

POST OFFICE BOX 1443 \* HOUSTON, TEXAS 77251-1443

8961725 0085596 62T **=**

<sup>3.</sup> The voltage on any input can undershoot to  $-2\,\mathrm{V}$  for periods less than 20 ns.

<sup>4.</sup> The voltage on any output can overshoot to 7 V for periods less than 20 ns.

# ADVANCE INFORMATION

## electrical characteristics over recommended ranges of supply voltage and operating free-air temperature using test conditions given in Table 6 (unless otherwise noted)

|          | ature using test c                | METER                 |                    | TEST C                                              | ONDITIONS                                        | MIN                          | MAX  | UNIT |

|----------|-----------------------------------|-----------------------|--------------------|-----------------------------------------------------|--------------------------------------------------|------------------------------|------|------|

|          |                                   |                       |                    | V <sub>CC</sub> = 4.5 V <sub>i</sub>                | I <sub>OH</sub> = - 2.5 mA                       | 2.4                          |      | ٧    |

| ОН       | High-level output voltage         |                       |                    | V <sub>CC</sub> = 4.5 V,                            | I <sub>OL</sub> = 5.8 mA                         |                              | 0.45 | ٧    |

| OL       | Low-level output voltage          |                       |                    |                                                     |                                                  | 11.5                         | 13   | V    |

| ID       | A9 selection code voltag          |                       | A9 = ViD           | V <sub>CC</sub> = 5.5 V,                            | V <sub>i</sub> = 0 V to 5.5 V                    |                              | ±1   | μΑ   |

|          | Input current (leakage),          |                       | 73 - 11D           | A9 = VID                                            |                                                  |                              | 500  | μΑ   |

| D        | A9 selection code curre           |                       |                    |                                                     |                                                  |                              | 500  | μΑ   |

| RP       | RP boot-block unlock cu           |                       |                    | V <sub>CC</sub> = 5.5 V,                            | Vo = 0 V to Vcc                                  |                              | ±10  | μΑ   |

| <u> </u> | Output current (leakage           |                       |                    | V <sub>PP</sub> ≤ V <sub>CC</sub>                   |                                                  |                              | 10   | μA   |

| PPS      | Vpp standby current (st           | andby)                |                    | RP = Vss ± 0.                                       | 2 V                                              |                              | 5    | μA   |

| PPL      | Vpp supply current (res           |                       | (n mode)           | VPP > VCC                                           |                                                  |                              | 200  | μΑ   |

| PP1      | Vpp supply current (rea           | nd)                   |                    | VPP = VPPH                                          |                                                  |                              |      | mA   |

| PP2      | Vpp supply current (ac            | tive byte write)      |                    | Programming                                         | in progress                                      |                              | 30   | MA   |

| PP3      | Vpp supply current (ac            | tive word write)      |                    | Vpp = VppH,<br>Programming                          |                                                  |                              | 40   | mA   |

| iPP4     | Vpp supply current (bk            |                       |                    | Vpp = VppH,<br>Block erase in                       |                                                  |                              | 30   | mA   |

| IPP5     | Vpp supply current (er            |                       |                    | Vpp = VppH,<br>Block erase s                        |                                                  |                              | 200  | μΑ   |

| 113      |                                   | TTL-input level       |                    | V <sub>CC</sub> = 5.5 V,                            | E = RP = VIH                                     |                              | 1.5  | mA   |

| lccs     | VCC supply current (standby)      | CMOS-input level      |                    | V <sub>CC</sub> = 5.5 V,                            |                                                  |                              | 100  | μΑ   |

|          |                                   | <u> </u>              | 0°C to 70°C        |                                                     |                                                  | 30<br>40<br>30<br>200<br>1.5 |      | μА   |

| ICCL     | VCC supply current (re            | set/deep power-       | - 40°C to 85°C     | RP = VSS ± 0                                        | ).2 V                                            | <b></b>                      | 8    | μА   |

|          | down mode)                        | TTL-input level       | - 40°C to 125°C    | V <sub>CC</sub> = 5.5 V,<br>f = 10 MHz,             | E = V <sub>IL</sub> ,<br>I <sub>OUT</sub> = 0 mA | 1                            | 60   | mA   |

| ICC1     | VCC supply current (active read)  | CMOS-input level      |                    | V <sub>CC</sub> = 5.5 V,<br>f = 10 MHz,             |                                                  |                              | 55   | mA   |

| ICC2     | VCC supply current (a             | ctive byte write) (se | e Notes 10 and 11) | V <sub>CC</sub> = 5.5 V <sub>r</sub><br>Programming |                                                  |                              | 60   | m/   |

| ICC3     | V <sub>CC</sub> supply current (a |                       |                    | VCC = 5.5 V<br>Programmin                           | ,<br>g in progress                               |                              | 65   | m/   |

| ICC4     | V <sub>CC</sub> supply current (t |                       |                    | V <sub>CC</sub> = 5.5 V<br>Block erase              | ,<br>in progress                                 |                              | 30   | ) m/ |

| ICC5     | VCC supply current (              |                       |                    | V <sub>CC</sub> = 5.5 V<br>Block erase              | ′, Ē = V¡Ḥ,<br>suspended                         |                              | 10   | m.   |

NOTES: 6. Not 100% tested; characterization data available

#### Table 6. AC Test Conditions

| SPEED DESIGNATOR | loL      | Іон  | Vz†      | VOL | VOH | V <sub>IL</sub> | V <sub>IH</sub><br>(V) | CLOAD<br>(pF) | t <sub>f</sub><br>(ns) | t <sub>r</sub><br>(ns) | TEMPERATURE     |

|------------------|----------|------|----------|-----|-----|-----------------|------------------------|---------------|------------------------|------------------------|-----------------|

| OF LIED BEGINS   | (11.0.4) | (mA) | <u> </u> | 15  | 1.5 | ,,              | 3.0                    | 30            | <10                    | <10                    | 0°C to 70°C     |

| -6               | 5.8      | -2.5 | 1.5      | 0.8 | 2.0 | 0.45            | 2.4                    | 100           | <10                    | <10                    | - 40°C to 125°C |

TVZ is the measured value used to detect high impedance.

8961725 0085597 566

POST OFFICE BOX 1443 <sup>●</sup> HOUSTON, TEXAS 77251-1443

<sup>7.</sup> All ac current values are RMS unless otherwise noted.

## capacitance over recommended ranges of supply voltage and operating free-air temperature, f = 1 MHz, $V_{\parallel}$ = 0 V

| PARAMETER                        | TEST CONDITIONS |     |     |      |

|----------------------------------|-----------------|-----|-----|------|

| C <sub>i</sub> Input capacitance | TEST CONDITIONS | MIN | MAX | UNIT |

| Co Output capacitance            |                 |     | 8   | pF   |

|                                  | VO = 0 V        |     | 12  | ηE   |

## switching characteristics over recommended ranges of supply voltage and operating free-air

| l                   | PARAMETER                                                              | ALT.                                   | '28F200 | BZx-6 | '28F200 | BZx-70 | '28F200I | 3Zx-80 | '28F200 | 3Zx-90 | T —  |

|---------------------|------------------------------------------------------------------------|----------------------------------------|---------|-------|---------|--------|----------|--------|---------|--------|------|

| 1                   | A                                                                      | SYMBOL                                 | MIN     | MAX   | MiN     | MAX    | MIN      | MAX    | MIN     | MAX    | UNIT |

| ta(A)               | Access time from A0-A16                                                | tAVQV                                  |         | 60    |         | 70     |          | 80     |         | 90     | +    |