## ATAPI CD-ROM Decoder and uP8032

Draft Rev. 0.7

### **Headquarters**

No. 4, Creation Rd. III

Science-Based Industrial Park

Hsinchu, Taiwan

TEL: 886-35-770066

FAX: 886-35-789467

www: http://www.winbond.com.tw/

**Taipei Office**

Talper Office 11F, No. 115, Sec. 3, Min-Sheng East Rd. Taipei, Taiwan TEL: 886-2-7190505 FAX: 886-2-7197502 TLX: 16485 WINTPE

Winbond Electronics (H.K.) Ltd. Rm. 803, World Trade Square, Tower II 123 Hoi Bun Rd., Kwun Tong Kowloon, Hong Kong TEL: 852-27516023-7 FAX: 852-27552064

**Winbond Electronics** (North America) Corp. 2730 Orchard Parkway San Jose, CA 95134 U.S.A. TEL: 1-408-9436666 FAX: 1-408-9436668

Note: All data and specifications are subject to change without

## W88227F/W88227QD Data Sheet Revision History

|    | Pages                                                | Dates      | Rev. | Version on Web | Main Contents                        |

|----|------------------------------------------------------|------------|------|----------------|--------------------------------------|

| 1  | N/A                                                  | 04/1999    | 0.40 | on web         | First published, without DC/AC spec. |

| 2  | 3, 8, 9, 12, 15,<br>34, 57, 63, 73,<br>75, 98-101    | 05/18/1999 | 0.50 |                | With DC/AC spec.                     |

| 3  | 12, 17, 18, 25,<br>26, 33, 42, 50,<br>60, 62, 86, 87 | 7/1999     | 0.60 |                | Erroneous content/figure fix         |

| 4  |                                                      | 10/1/1999  | 0.70 |                | Add Diagram of Equivalent Circuit    |

|    |                                                      |            |      |                | Add Absolute Maximum Ratings         |

|    |                                                      |            |      |                | Add AC Timing                        |

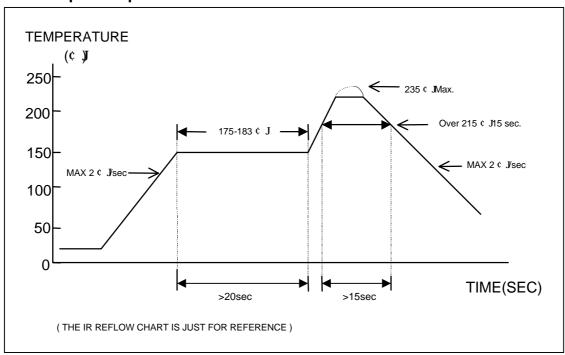

|    |                                                      |            |      |                | Add IR Re-flow Profile               |

|    |                                                      |            |      |                | Remove Application Circuit           |

|    |                                                      |            |      |                | Add W88227QD package                 |

| 5  |                                                      |            |      |                |                                      |

| 6  |                                                      |            |      |                |                                      |

| 7  |                                                      |            |      |                |                                      |

| 8  |                                                      |            |      |                |                                      |

| 9  |                                                      |            |      |                |                                      |

| 10 |                                                      |            |      |                |                                      |

Please note that all data and specifications are subject to change without notice. All the trade marks of products and companies mentioned in this datasheet belong to their respective owners.

## LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Winbond customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Winbond for any damages resulting from such improper use or sales.

## TABLE OF CONTENTS

| 1.  | OVERVIEW                                             | 1        |

|-----|------------------------------------------------------|----------|

| 1.1 | Features                                             | 1        |

| 1.2 | Pin Map                                              | 2        |

| 1.3 | Pin Arrangement                                      | 4        |

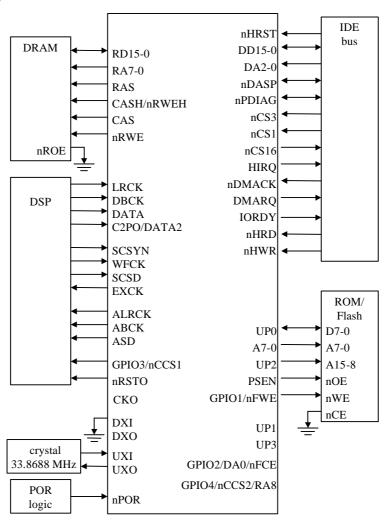

| 1.4 | Basic Configuration                                  | 8        |

| 2.  | FUNCTIONAL DESCRIPTION                               | 9        |

| 2.1 | Global Function                                      | 9        |

|     | 1.1 Decoder Register Access                          | 9        |

|     | 1.2 Reset Source                                     | 9        |

|     | 1.3 Clock Source and Power Management                | 10       |

|     | 1.4 Multi-function Pins                              | 11       |

|     | 2.1.4.1 GPIO1/nFWE Configuration                     | 11       |

|     | 2.1.4.2 GPIO2/DAOUT/nFCE Configuration               | 11       |

|     | 2.1.4.3 GPIO3/nCCS1 Configuration                    | 11       |

|     | 2.1.4.4 GPIO4/nCCS2/RA8 Configuration                | 12       |

|     | 2.1.4.5 UP32/UP33 Configuration                      | 12       |

|     | 2.1.4.6 ASD/nROE Configuration                       | 12       |

|     | 2.1.4.7 CASH/nWREH Configuration                     | 12       |

|     | 1.5 IDE Programming Mode<br>2.1.5.1 Pin Mapping      | 13<br>13 |

|     | 2.1.5.1 Thi Mapping 2.1.5.2 IDE Programming Sequence | 13       |

|     | 2.1.5.3 Initiation Key                               | 14       |

|     | 2.1.5.4 IDE Programming Registers                    | 14       |

|     | 1.6 Power-On Setting                                 | 15       |

| 2.1 | 1.7 External uP (EUP) Mode                           | 16       |

|     | 1.8 uP Test (UPT) Mode                               | 16       |

| 2.2 | Decoder Function                                     | 17       |

|     | 2.1 DRAM Interface                                   | 17       |

|     | 2.2.1.1 Memory Layout                                | 17       |

|     | 2.2.1.2 Block Configuration                          | 18       |

|     | 2.2.1.3 Linear Transfer Address Counter              | 19       |

|     | 2.2.1.4 Linear Address v.s. Block-Offset Address     | 20       |

|     | 2.2 Microcontroller Interface                        | 21       |

|     | 2.2.2.1 Programmable System Clock                    | 21       |

|     | 2.3 Host Interface                                   | 22       |

|     | 2.2.3.1 Ultra DMA Mode Setting                       | 22       |

|     | 2.2.3.2 Ultra DMA Error Handling                     | 22       |

|     | 2.2.3.3 Ultra DMA Data-out                           | 23       |

|     | 2.2.3.4 BSY flag control                             | 24       |

|     | 2.2.3.5 Pin HIRQ control                             | 24       |

# W88227F

| 2   | .2.4     | Decoder Logic                                     | 25  |

|-----|----------|---------------------------------------------------|-----|

|     | 2.2.4.1  | Sync Detection/Insertion                          | 25  |

|     | 2.2.4.2  | Descramble                                        | 25  |

|     | 2.2.4.3  | Disk-Monitor Mode                                 | 25  |

|     | 2.2.4.4  | Parallel ECC Correction                           | 25  |

|     | 2.2.4.5  | EDC Checking                                      | 26  |

|     | 2.2.4.6  | Real Time EDC Checking                            | 26  |

|     | 2.2.4.7  | Disc Format Selection                             | 26  |

|     | 2.2.4.8  | DSP Main Data Format                              | 26  |

|     | 2.2.4.9  | CD-DA data & Q-channel Extraction                 | 27  |

|     | 2.2.4.10 | Target Search                                     | 28  |

|     | 2.2.4.11 | Automatic Header Comparison                       | 28  |

|     | 2.2.4.12 | Status Collection                                 | 28  |

|     | 2.2.4.13 | Buffer-Independent-Correction                     | 28  |

|     | 2.2.4.14 | Remove Frequent SRIb & Automatic Cache Management | 28  |

| 2   |          | Audio-playback                                    | 31  |

|     | 2.2.5.1  | Configuration Phase                               | 31  |

|     |          | Playback Phase                                    | 31  |

|     | 2.2.5.3  | IEC-958 Digital Audio Output                      | 31  |

| 2   | .2.6     | Function Differences Between W88227 and W88113CF  | 32  |

| 2   | .2.7     | Decoder Register Map                              | 33  |

|     |          |                                                   |     |

| 2.3 |          | 32 Function                                       | 93  |

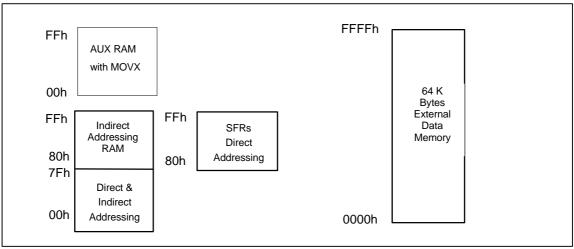

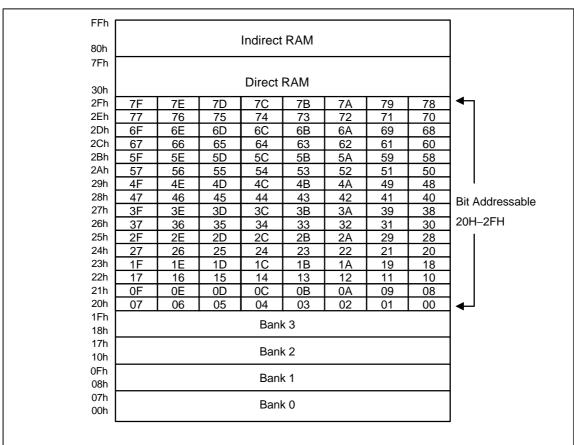

|     |          | Data Memory                                       | 93  |

|     |          | RAM and AUX_RAM                                   | 93  |

|     |          | AUX_ROM Mode and uP Programming Flash             | 95  |

| 2   | .3.4     | Special Function Register (SFR)                   | 95  |

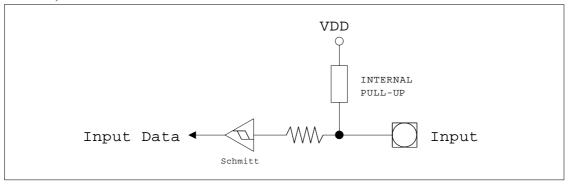

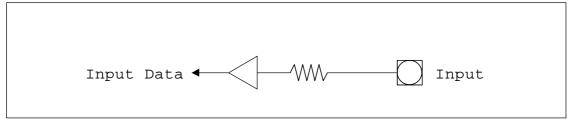

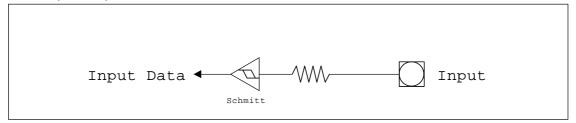

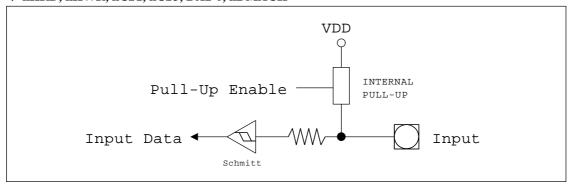

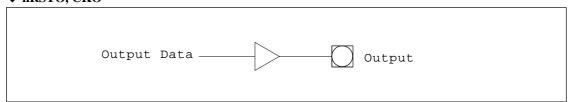

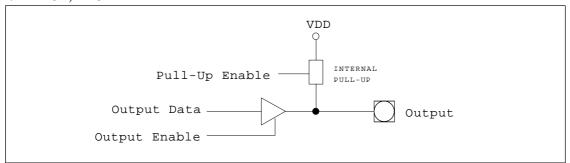

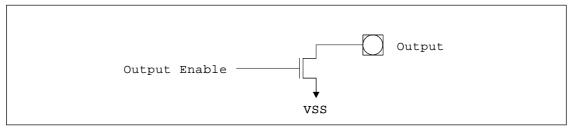

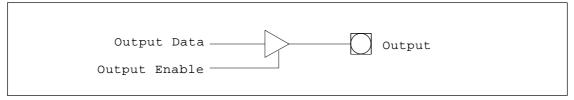

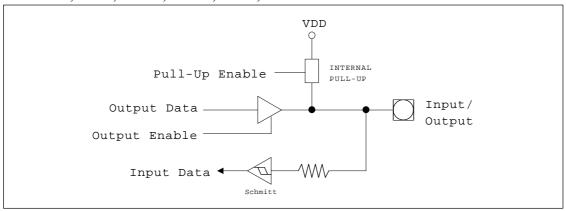

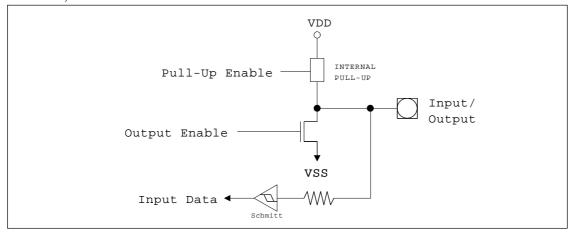

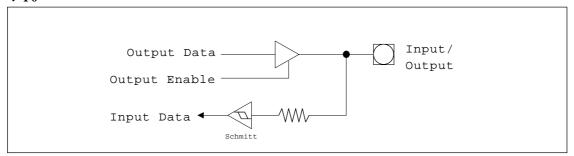

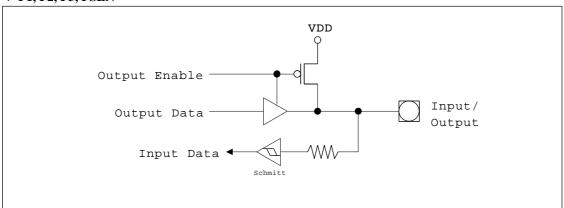

| 3.  | DIAG     | RAM OF EQUIVALENT CIRCUIT IN INPUT/OUTPUT PORT    | 99  |

| 4.  | ELEC     | TRONIC CHARACTERISTICS                            | 103 |

|     |          |                                                   |     |

| 4.1 | Abso     | lute Maximum Ratings                              | 103 |

| 4.2 | DC (     | Characteristics                                   | 103 |

| 4.3 | AC (     | Characteristics                                   | 104 |

| 5.  | ORDE     | CRING INSTRUCTION                                 | 109 |

| 6.  | ном      | TO READ THE TOP MARKING                           | 109 |

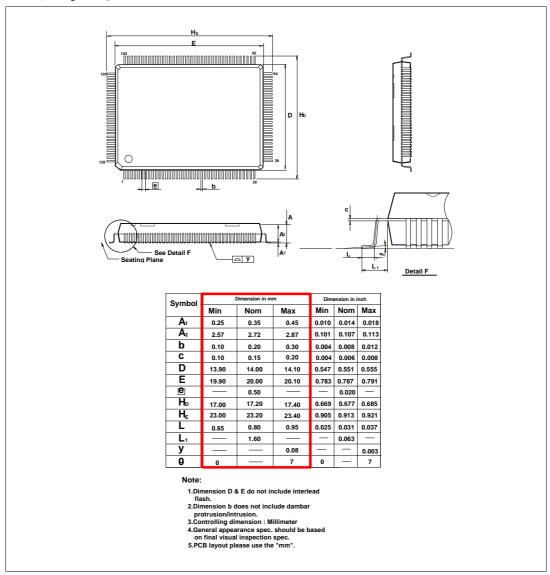

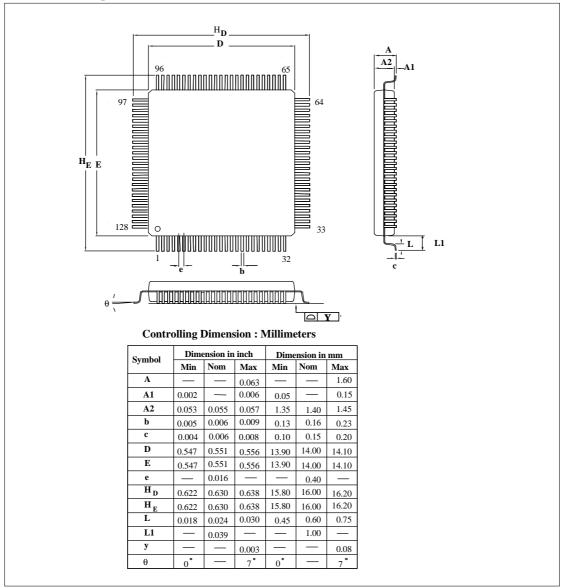

| 7.  | PACK     | AGE DIMENSION                                     | 110 |

| 8.  | EXAM     | IPLE TEMPERATURE PROFILE FOR INFRARED REFLOW      | 112 |

Preliminary/Confidential Subject to change without notice

## 1. Overview

#### 1.1 Features

#### **Decoder**

- ⇒ Supports ATAPI CD-ROM standard (SFF 8020)

- ⇒ Supports CD-ROM, CD-ROM/XA, CD-I, Video-CD, Photo-CD, CD-Plus, and i-trax formats

- ⇒ Supports drive speed up to 60-fold

- ⇒ Supports various types of DSPs

- ⇒ Supports various types of industry-standard DRAMs (256K\*16 ~ 64K\*16, 256K\*8, 128K\*8)

- ⇒ Supports real-time correction and buffer-independent-correction

- ⇒ Supports automatic repeated error correction

- ⇒ 32-byte FIFO to improve IDE interface throughput

- ⇒ Support data transfer to host in PIO, DMA, and UDMA/66 mode

- ⇒ Support block-offset-address-transfer and linear-address-transfer

- ⇒ Support automatic ATAPI hardware macro

- ⇒ Support automatic target header search and header comparison

- ⇒ Support automatic cache buffer management and transfer

- ⇒ Support Q-channel data extraction

- ⇒ Support high-speed CAV audio playback from DRAM buffer

- ⇒ Support left and right channels routing and muting

- ⇒ Support IEC-958 digital audio output

- ⇒ Programmable system clock for decoder operation

- ⇒ Support flash programming through IDE interface

## Micro-controller

- $\Rightarrow$  Up to DC-40MHz operation for built-in  $\mu$ P8032

- ⇒ 512 bytes of on-chip scratchpad RAM (including 256 bytes re-addressable AUX\_RAM)

- ⇒ AUX\_RAM can also be dynamically programmed as an AUX\_ROM ,which can be used as an internal rom to support flash programming by uP

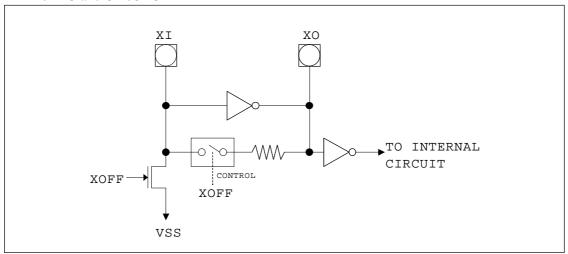

- ⇒ Internal crystal loop off in power-down mode to save more power

- ⇒ Support programmable wake-up from Power-Down Mode

#### Miscellaneous

- ⇒ Glue logic circuit saving (built-in 74373)

- ⇒ External ROM/Flash chip enable pin to save power in Power-Down Mode

- ⇒ Support hardware and firmware controlled reset output

- ⇒ Programmable decoder and servo chip-select base address

- ⇒ Controllable clock output

- ⇒ Multi-level power management

- ⇒ 128-pin PQFP/ LQFP

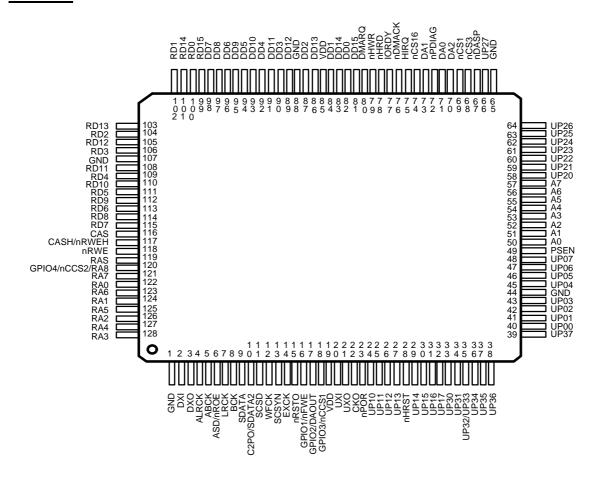

## 1.2 Pin Map

## **W88227F**

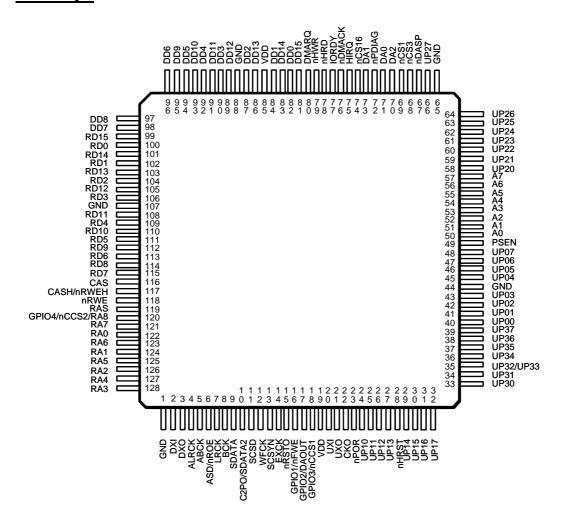

## W88227QD

## 1.3 Pin Arrangement

| Number | Symbol | Type | Description                          | Remark                     |

|--------|--------|------|--------------------------------------|----------------------------|

| 1      | GND    | P    | Ground                               |                            |

| 2      | DXI    | I    | Decoder crystal in                   | Connect to GND if not used |

| 3      | DXO    | О    | Decoder crystal out                  |                            |

| 4      | ALRCK  | I/OZ | Audio playback left/right clock      | 6mA, PU                    |

| 5      | ABCK   | OZ   | Audio playback bit clock             | 6mA, PU                    |

| 6      | ASD    | OZ   | Audio playback serial data           | 6mA, PU                    |

|        | nROE   | О    | DRAM read enable, active low         |                            |

| 7      | LRCK   | I    | DSP left/right clock                 | CMOS level input           |

| 8      | BCK    | I    | DSP bit clock                        | CMOS level input           |

| 9      | SDATA  | I    | DSP serial data                      | CMOS level input           |

| 10     | C2PO   | I    | DSP C2 flag                          | CMOS level input           |

|        | SDATA2 | I    | DSP serial data 2                    |                            |

| 11     | SCSD   | I    | Subcode serial data                  |                            |

| 12     | WFCK   | I    | Subcode write frame clock            |                            |

| 13     | SCSYN  | I    | Subcode sync                         |                            |

| 14     | EXCK   | I/O  | Subcode external clock               | 6mA, PU                    |

| 15     | nRSTO  | О    | Reset output, active low             | 6mA                        |

| 16     | GPIO1  | I/O  | General purpose IO                   | 6mA, PU                    |

|        | nFWE   | О    | Flash Write Enable, active low       |                            |

| 17     | GPIO2  | I/O  | General purpose IO                   | 6mA, PU                    |

|        | DAOUT  | О    | Digital audio output                 |                            |

|        | nFCE   | О    | ROM/Flash Chip Enable, active low    |                            |

| 18     | GPIO3  | I/O  | General purpose IO                   | 6mA, PU                    |

|        | nCCS1  | О    | Configurable chip select, active low |                            |

| 19     | VDD    | P    | Power                                |                            |

| 20     | UXI    | I    | uP crystal in                        |                            |

| 21     | UXO    | О    | uP crystal out                       |                            |

| 22     | CKO    | О    | clock output                         | 6mA                        |

| 23     | nPOR   | I    | power on reset, acitve low           | PU                         |

| 24     | UP10   | I/O  | uP port 1                            | 4mA, PU                    |

| 25     | UP11   | I/O  | uP port 1                            | 4mA, PU                    |

| 26     | UP12   | I/O  | uP port 1                            | 4mA, PU                    |

| 27     | UP13   | I/O  | uP port 1                            | 4mA, PU                    |

| 28     | nHRST  | I    | host reset input, active low         | PU                         |

| 29     | UP14   | I/O  | uP port 1                            | 4mA, PU                    |

| 30     | UP15   | I/O  | uP port 1                            | 4mA, PU                    |

| 31     | UP16   | I/O  | uP port 1                            | 4mA, PU                    |

| 32     | UP17   | I/O  | uP port 1                            | 4mA, PU                    |

| 33     | UP30   | I/O  | uP port 3 (RXD)                      | 4mA, PU                    |

| 34 | UP31   | I/O  | uP port 3 (TXD)                  | 4mA, PU  |

|----|--------|------|----------------------------------|----------|

| 35 | UP32   | I/O  | uP port 2 (INT0)                 | 4mA, PU  |

|    | UP33   | I/O  | uP port 3 (INT1)                 |          |

| 36 | UP34   | I/O  | uP Port 3 (T0)                   | 4mA, PU  |

| 37 | UP35   | I/O  | uP port 3 (T1)                   | 4mA, PU  |

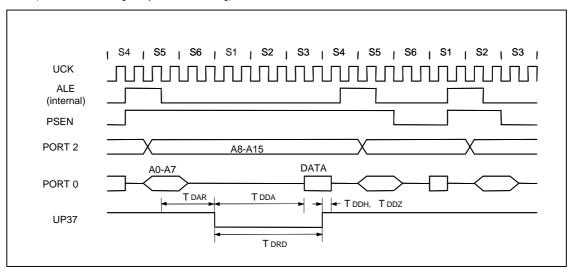

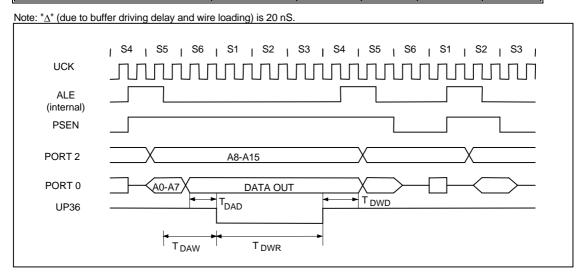

| 38 | UP36   | I/O  | uP port 3 (nWR)                  | 4mA, PU  |

| 39 | UP37   | I/O  | uP port 3 (nRD)                  | 4mA, PU  |

| 40 | UP00   | I/O  | uP port 0                        | 8mA      |

| 41 | UP01   | I/O  | uP port 0                        | 8mA      |

| 42 | UP02   | I/O  | uP port 0                        | 8mA      |

| 43 | UP03   | I/O  | uP port 0                        | 8mA      |

| 44 | GND    | P    | Ground                           |          |

| 45 | UP04   | I/O  | uP port 0                        | 8mA      |

| 46 | UP05   | I/O  | uP port 0                        | 8mA      |

| 47 | UP06   | I/O  | uP port 0                        | 8mA      |

| 48 | UP07   | I/O  | uP port 0                        | 8mA      |

| 49 | PSEN   | I/O  | program store enable, acitve low | 8mA, PU  |

| 50 | A0     | О    | external ROM address             | 4mA      |

| 51 | A1     | О    | external ROM address             | 4mA      |

| 52 | A2     | О    | external ROM address             | 4mA      |

| 53 | A3     | О    | external ROM address             | 4mA      |

| 54 | A4     | О    | external ROM address             | 4mA      |

| 55 | A5     | О    | external ROM address             | 4mA      |

| 56 | A6     | I/O  | external ROM address             | 4mA, PU  |

| 57 | A7     | I/O  | external ROM address             | 4mA, PU  |

| 58 | UP20   | I/O  | uP port 2                        | 4mA, PU  |

| 59 | UP21   | I/O  | uP port 2                        | 4mA, PU  |

| 60 | UP22   | I/O  | uP port 2                        | 4mA, PU  |

| 61 | UP23   | I/O  | uP port 2                        | 4mA, PU  |

| 62 | UP24   | I/O  | uP port 2                        | 4mA, PU  |

| 63 | UP25   | I/O  | uP port 2                        | 4mA, PU  |

| 64 | UP26   | I/O  | uP port 2                        | 4mA, PU  |

| 65 | GND    | P    | Ground                           |          |

| 66 | UP27   | I/O  | uP port 2                        | 4mA, PU  |

| 67 | nDASP  | I/OD | drive active, active low         | 12mA, PU |

| 68 | nCS3   | I    | host chip select 1, active low   | PU       |

| 69 | nCS1   | I    | host chip select 0, active low   | PU       |

| 70 | DA2    | I    | host address 2                   | PU       |

| 71 | DA0    | I    | host address 0                   | PU       |

| 72 | nPDIAG | I/OD | passed diagnostics, active low   | 12mA, PU |

| 73 | DA1    | I    | host address 1                   | PU       |

| 74 | nCS16  | OD   | 16-bit IO select, active low     | 24mA     |

| 75  | HIRQ   | OZ  | host interrupt                | 12mA     |

|-----|--------|-----|-------------------------------|----------|

| 76  | nDMACK | I   | DMA acknowledge, active low   | PU       |

| 77  | IORDY  | OZ  | IO channel ready              | 24mA     |

| 78  | nHRD   | I   | host read strobe, active low  | PU       |

| 79  | nHWR   | I   | host write strobe, active low | PU       |

| 80  | DMARQ  | OZ  | dam request                   | 12mA     |

| 81  | DD15   | I/O | host data                     | 12mA, PU |

| 82  | DD0    | I/O | host data                     | 12mA, PU |

| 83  | DD14   | I/O | host data                     | 12mA, PU |

| 84  | DD1    | I/O | host data                     | 12mA, PU |

| 85  | VDD    | P   | Power                         |          |

| 86  | DD13   | I/O | host data                     | 12mA, PU |

| 87  | DD2    | I/O | host data                     | 12mA, PU |

| 88  | GND    | P   | Ground                        |          |

| 89  | DD12   | I/O | host data                     | 12mA, PU |

| 90  | DD3    | I/O | host data                     | 12mA, PU |

| 91  | DD11   | I/O | host data                     | 12mA, PU |

| 92  | DD4    | I/O | host data                     | 12mA, PU |

| 93  | DD10   | I/O | host data                     | 12mA, PU |

| 94  | DD5    | I/O | host data                     | 12mA, PU |

| 95  | DD9    | I/O | host data                     | 12mA, PU |

| 96  | DD6    | I/O | host data                     | 12mA, PU |

| 97  | DD8    | I/O | host data                     | 12mA, PU |

| 98  | DD7    | I/O | host data                     | 12mA, PU |

| 99  | RD15   | I/O | DRAM data                     | 6mA, PU  |

| 100 | RD0    | I/O | DRAM data                     | 6mA, PU  |

| 101 | RD14   | I/O | DRAM data                     | 6mA, PU  |

| 102 | RD1    | I/O | DRAM data                     | 6mA, PU  |

| 103 | RD13   | I/O | DRAM data                     | 6mA, PU  |

| 104 | RD2    | I/O | DRAM data                     | 6mA, PU  |

| 105 | RD12   | I/O | DRAM data                     | 6mA, PU  |

| 106 | RD3    | I/O | DRAM data                     | 6mA, PU  |

| 107 | GND    | P   | Ground                        |          |

| 108 | RD11   | I/O | DRAM data                     | 6mA, PU  |

| 109 | RD4    | I/O | DRAM data                     | 6mA, PU  |

| 110 | RD10   | I/O | DRAM data                     | 6mA, PU  |

| 111 | RD5    | I/O | DRAM data                     | 6mA, PU  |

| 112 | RD9    | I/O | DRAM data                     | 6mA, PU  |

| 113 | RD6    | I/O | DRAM data                     | 6mA, PU  |

| 114 | RD8    | I/O | DRAM data                     | 6mA, PU  |

| 115 | RD7    | I/O | DRAM data                     | 6mA, PU  |

| 116 | CAS    | OZ  | DRAM column address strobe    | 8mA      |

| 117 | CASH  | OZ  | DRAM column address strobe           | 8mA     |

|-----|-------|-----|--------------------------------------|---------|

|     | nRWEH | OZ  | DRAM write enable, active low        |         |

| 118 | nRWE  | OZ  | DRAM write enable, active low        | 8mA     |

| 119 | RAS   | OZ  | DRAM row address strobe              |         |

| 120 | GPIO4 | I/O | General purpose IO                   | 6mA, PU |

|     | nCCS2 | О   | Configurable chip select, active low | 6mA     |

|     | RA8   | О   | DRAM address                         | 6mA     |

| 121 | RA7   | I/O | DRAM address                         | 6mA, PU |

| 122 | RA0   | I/O | DRAM address                         | 6mA, PU |

| 123 | RA6   | I/O | DRAM address                         | 6mA, PU |

| 124 | RA1   | I/O | DRAM address                         | 6mA, PU |

| 125 | RA5   | I/O | DRAM address                         | 6mA, PU |

| 126 | RA2   | I/O | DRAM address                         | 6mA, PU |

| 127 | RA4   | I/O | DRAM address                         | 6mA, PU |

| 128 | RA3   | I/O | DRAM address                         | 6mA, PU |

## 1.4 Basic Configuration

## 2. Functional Description

## 2.1 Global Function

## 2.1.1 Decoder Register Access

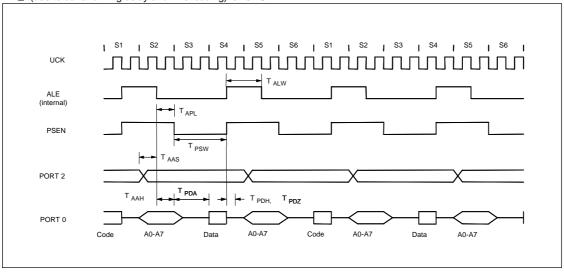

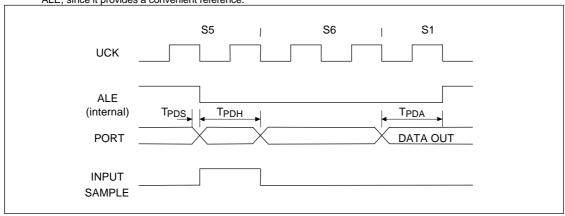

The Decoder Index Register is latched from uP Port-0 by the built-in 74373 at the falling edge of internal *ALE* signal. The high byte address of decoder register is defined by *CCSA0 (40h)* with default value 40h.

<example>: decoder register read (read VER)

MOV DPTR,#0401Ah

MOVX A,@DPTR

<example>: decoder register write (set CCSA1 as 0xC0h)

MOV A,#0C0h

MOV DPTR,#04041h

MOVX @DPTR,A

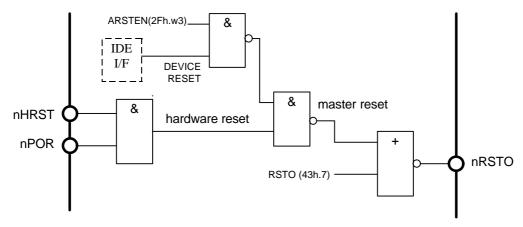

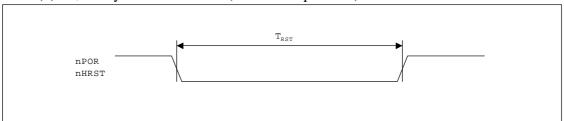

#### 2.1.2 Reset Source

The chip will be reset when master reset, including:

- (1) power on reset,

- (2) host reset or

- (3) reception of DEVICE RESET command (opcode 08h) if ARSTEN (2Fh.w3) is high.

The output of pin nRSTO can be controlled either by master reset or firmware. The state of *pin nRSTO* is the inverse value of control bit *RSTO* (43h.7).

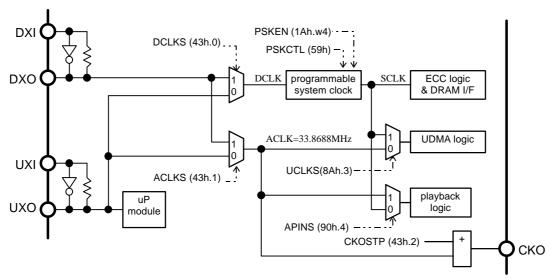

## 2.1.3 Clock Source and Power Management

If the frequency on UXI is 33.8688 MHz, then the crystal on DXI can be saved. If the frequency on UXI is not 33.8688 MHz, then the input frequency on DXI must be 33.8688 MHz to support audio playback. A clock output pin CKO can be used as clock source. If *CKOSTP* (43h.2) is set high, the output of pin CKO holds a "high" status so that the external device is in idle mode. Note that DXI should be connected to ground if not used.

### **Decoder Idle Mode**

Setting CKSTP (19h.w7) stop the clock of decoder. The decoder exits idle mode on reset or host command.

### **UP8032 Idle Mode**

Setting the *IDL* (*PCON.0*) high stop the clock of uP8032. The peripherals and the interrupt logic continue to be clocked. The processor will exit idle mode when either an interrupt or a reset occurs.

#### Power-Down Mode

When *PD* (*PCON.1*) is set high, the chip enters the power-down mode. In this mode, the crystal feedback loop between UXI and UXO can be closed by setting *PD* (*PCON.1*) high, and that between DXI and DXO can be closed by setting *XOFF* (8Ah.7) high. In two-crystal case, *XOFF* should be set before *PD*. These two loops resume on the following conditions.

| EA | EHWK | EIWK | HIIEN | ARSTIEN | wake-up event                       |

|----|------|------|-------|---------|-------------------------------------|

| X  | X    | X    | X     | X       | power on reset or host reset        |

| 1  | 1    | X    | 1     | X       | software reset by setting SRST high |

| 1  | 1    | X    | X     | 1       | DEVICE RESET command                |

| 1  | X    | 1    | X     | X       | interrupt on INT0 or INT1           |

Before entering power-down mode, internal pull-up resistors can be closed by setting PUCTL (98h).

Preliminary/Confidential Subject to change without notice

## 2.1.4 Multi-function Pins

The state of general-purpose I/O pins can be controlled through register GIOCTL (5Fh).

## 2.1.4.1 GPIO1/nFWE Configuration

If the *IDE Programming Ready Signature (E8)* is high by executing the IDE programming sequence, this pin is used as nFWE. Otherwise, this pin is used as GPIO1.

## 2.1.4.2 GPIO2/DAOUT/nFCE Configuration

| G2CF (5Dh.3) | DAOEN (87h.7) | pin function | Remark    |

|--------------|---------------|--------------|-----------|

| 0b           | 0b            | nFCE         | (default) |

| 1b           | 0b            | GPIO2        |           |

| х            | 1b            | DAOUT        |           |

This pin is configured as nFCE and output "low" after master reset. It holds "high" when uP enter power-down mode by setting *PD* (*PCON.1*) high and returns to low active status when:

- 1. Hardware reset,

- 2. Software reset if HIIEN (2Eh.w7) is set high,

- 3. or DEVICE RESET command if ARSTIEN (2Fh.w1) is set high.

This function can be utilized to save power of external ROM in Sleep mode.

If a pull-down resistor is connected to pin RA4, the pin is configured as GPIO2 after master reset. If *DAOEN* (87h.7) is set high, this pin is used as DAOUT, digital audio output.

## 2.1.4.3 GPIO3/nCCS1 Configuration

The value of CCSA1 (41h) is 00h after master reset.

| G3CF (5Dh.2-0) | Function | nCCS1 active (low) condition            | Remark  |

|----------------|----------|-----------------------------------------|---------|

| 0xxb           | GPIO3    | n/a                                     | Default |

| 100b           | nCCS1    | (P2 = CCSA1)                            |         |

| 101b           | nCCS1    | (P2 = CCSA1) & (P36 = "L")              |         |

| 110b           | nCCS1    | (P2 = CCSA1) & (P37 = "L")              |         |

| 111b           | nCCS1    | (P2 = CCSA1) & (P36 = "L" or P37 = "L") |         |

Preliminary/Confidential Subject to change without notice

## 2.1.4.4 GPIO4/nCCS2/RA8 Configuration

The value of CCSA2 (42h) is 00h after master reset.

|                | 1        |                                                                                    |         |

|----------------|----------|------------------------------------------------------------------------------------|---------|

| G4CF (5Dh.7-4) | Function | nCCS2 active (low) condition                                                       | Remark  |

| 0xxxb          | RA8      | output is tri-state after master reset and is<br>enabled when RTC (2Ah.2-0) ≠ 000b | Default |

| 10xxb          | GPIO4    | n/a                                                                                |         |

| 1100b          | nCCS2    | (P2 = CCSA2)                                                                       |         |

| 1101b          | nCCS2    | (P2 = CCSA2) & (P36 = "L")                                                         |         |

| 1110b          | nCCS2    | (P2 = CCSA2) & (P37 = "L")                                                         |         |

| 1111b          | nCCS2    | (P2 = CCSA2) & (P36 = "L" or P37 = "L")                                            |         |

## 2.1.4.5 UP32/UP33 Configuration

| UP323S (43h.4) | Pin UP32/UP33 | Internal Decoder Interrupt | Remark  |

|----------------|---------------|----------------------------|---------|

| 0b             | INT0          | INT1                       | Default |

| 1b             | INT1          | INT0                       |         |

## 2.1.4.6 ASD/nROE Configuration

This pin is used as nROE after master reset. It is configured as ASD (audio playback serial data) when setting *APOUT* (90h.1-0) as 01b.

## 2.1.4.7 CASH/nWREH Configuration

This pin is tri-state after master reset. It is configured as output when RTC (2Ah,2-0) is 10xb. It is used as CASH when TWES (2Ah,3) is low and as nRWEH when TWES (2AH,3) is high.

Preliminary/Confidential Subject to change without notice

## 2.1.5 IDE Programming Mode

This chip enters *IDE Programming Mode* when the last initiation key is written to Control Port. The status can be verified by read *IDE Programming Ready Signature (E8h)* from Feature Port.

## 2.1.5.1 Pin Mapping

| Flash Pin Name | W88227 Pin Name  | Function     |

|----------------|------------------|--------------|

| A15-8          | UP27-UP20        | Address High |

| A7-0           | A7-0             | Address Low  |

| DQ7-0          | UP07-UP00        | Data         |

| CEN            | GPIO2/DAOUT/nFCE | Chip Enable  |

| OEN            | OEN PSEN C       |              |

| WEN            | GPIO1/nFWE       | Write Enable |

## 2.1.5.2 IDE Programming Sequence

The following sequence is only an example. Please properly adjust it to fit the specification of different Flash.

- 1. Select the drive

- 2. Write Initiation Key to 1F3h/173h

- 3. Read 1F3h/173h to verify IDE Programming Ready Signature (E8h)

- 4. Write address to 1F4h/174h and 1F5h/175h

- 5. Write data to 1F1h/171h

- 6. Activates NFCE by writing 04h to 1F2h/172h

- 7. Activates NFWE by writing 05h to 1F2h/172h

- 8. Releases NFWE by writing 04h to 1F2h/172h

- 9. Go back to step 4 until all data are written

- 10. Write address to 1F4h/174h and 1F5h/175h

- 11. Activates NFOE by writing 06h to 1F2h/172h

- 12. Read from 1F1h/171h to verify data

- 13. Releases NFOE by writing 04h to 1F2h/172h

- 14. Go back to step 10 until all data are verified

- 15. DEVICE RESET (re-start uP program counter from 0) or Re-boot

Preliminary/Confidential Subject to change without notice

## 2.1.5.3 Initiation Key

The exact sequence for the initiation key in hexadecimal notation is:

4C, 26, 93, 49, A4, 52, A9, D4,

6A, B5, DA, ED, F6, FB, 7D, BE,

DF, 6F, 37, 1B, 0D, 86, C3, 61,

B0, 58, 2C, 16, 8B, 45, A2, D1

## 2.1.5.4 IDE Programming Registers

| Port Name    | Address   |     | Bit7               | Bit6 | Bit5  | Bit4  | Bit3    | Bit2 | Bit1 | Bit0 |

|--------------|-----------|-----|--------------------|------|-------|-------|---------|------|------|------|

| Data         | 1F1h/171h | r/w |                    |      |       | Flash | data    |      |      |      |

| Control      | 1F2h/172h | w   | X                  | X    | X     | X     | X       | fce  | foe  | fwe  |

| Feature      | 1F3h/173h | r/w |                    |      | Progr | ammin | g signa | ture |      |      |

| Address Low  | 1F4h/174h | w   | Flash low address  |      |       |       |         |      |      |      |

| Address High | 1F5h/175h | w   | Flash high address |      |       |       |         |      |      |      |

Preliminary/Confidential Subject to change without notice

## 2.1.6 Power-On Setting

Pin RA7-0 are input with weak pull-up during master reset or when RTC (2Ah.2-0) is 000b. RA7-5 are used as power-on setting and RA4-0 can be used as general input when RTC (2Ah.2-0) is 000b. The status of RA7-0 can be read from RASTA (2Dh,r).

| pin RA7                  | Operation Mode | remark  |

|--------------------------|----------------|---------|

| 4.7 K $\Omega$ pull-down |                |         |

|                          |                |         |

| no                       | Normal mode    | default |

| pin RA6          | decoder chip select | remark  |

|------------------|---------------------|---------|

| 4.7 KΩ pull-down | base address        |         |

| no               | 40xxh               | default |

| yes              | C0xxh               |         |

| pin RA5          | Operation Mode | remark                |

|------------------|----------------|-----------------------|

| 4.7 KΩ pull-down |                |                       |

| no               | normal mode    | default               |

| yes              | uP test mode   | for factory test only |

Preliminary/Confidential Subject to change without notice

## 2.1.7 External uP (EUP) Mode

If a 4.7K pull-down is connected to pin RA7 during power-on, this chip enters the External uP (EUP) mode. In EUP mode, the internal uP do not work and some pins are redefined by the following table to work with an external uP. This testing mode is specially designed for firmware debug using ICE. Note that one TTL is needed to support external uP reset signal in EUP mode.

| Normal    | I/O | EUP mode | I/O | Remark                                  |

|-----------|-----|----------|-----|-----------------------------------------|

| P0        | I/O | UD       | I/O |                                         |

| P1        | I/O | n/a      | Z   |                                         |

| P2        | I/O | n/a      | I   | Be used to generate internal UCSb       |

| A7-0      | О   | A7-0     | О   |                                         |

| UP30      | I/O | n/a      | Z   |                                         |

| UP31      | I/O | n/a      | Z   |                                         |

| UP33/UP32 | I/O | UINTb    | О   | One 0 ohm option resistor may be needed |

| UP34      | I/O | n/a      | Z   |                                         |

| UP35      | I/O | n/a      | Z   |                                         |

| UP36      | I/O | UWRB     | I   |                                         |

| UP37      | I/O | URDB     | I   |                                         |

| PSEN      | О   | ALEIN    | I   | One 0 ohm option resistor may be needed |

## 2.1.8 uP Test (UPT) Mode

If a 4.7K pull-down is connected to pin RA5 during power-on, this chip enters the uP test (UPT) mode. In UPT mode, some pins are redefined by the following. This mode is for factory test only.

| Normal  | I/O | UPT mode | I/O | Remark |

|---------|-----|----------|-----|--------|

| P32/P33 | I/O | P32      | I/O |        |

| A7      | O   | P33      | I/O |        |

| A6      | О   | ALE      | О   |        |

## 2.2 Decoder Function

## 2.2.1 DRAM Interface

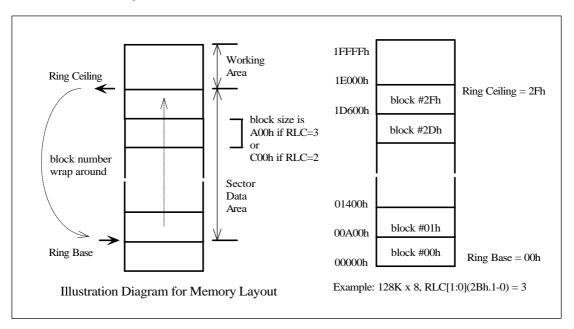

#### 2.2.1.1 Memory Layout

The whole DRAM can be divided into Sector *Data Area* and *Working Area*. Sectors from DSP are buffered into Sector Data Area and then are retrieved for ECC/EDC operation. Some information is stored in working area for transfer to host on request, for example, TOC.

Sector data buffering is a block-based ring operation. If the decoded-block-number in DDBH/L (29h/28h) is N-1, the sector is buffered into block with number N. The decoded-block-number is automatically incremented by one at each sync. When the decoded-block-number equals the value in WBRCH/L (57h/56h), the sector is buffered into the block with number specified by WBRBH/L (55h/54h).

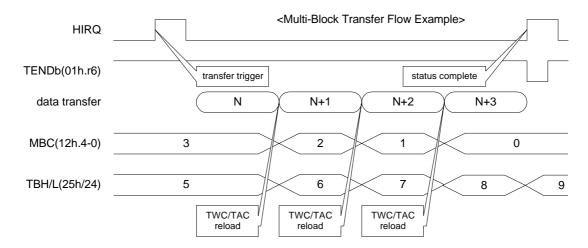

The data transfer is also a block-based ring operation if multi-block-transfer is used. The transfer ring is controlled by *DTRCH/L* (53h/52h) and *DTRBH/L* (51h/50h). The buffer ring and transfer ring are usually defined in the same range.

Preliminary/Confidential Subject to change without notice

## 2.2.1.2 Block Configuration

The configuration of each memory block depends on the data format. The following tables show the recommended configuration of block whose size is A00h and C00h, respectfully.

■ If BIA (09h/08h) = 000Ch and RLC (2Bh.1-0) = 3, block size is A00h.

| Item      | Mode 1      | Mode 2      | Mode2 Form1 | Mode2 Form2 | CD-DA       |

|-----------|-------------|-------------|-------------|-------------|-------------|

| Sync      | 000h (12)   | 000h (12)   | 000h (12)   | 000h (12)   | N/A         |

| Header    | 00Ch (4)    | 00Ch (4)    | 00Ch (4)    | 00Ch (4)    | N/A         |

| Subheader | N/A         | N/A         | 010h (8)    | 010h (8)    | N/A         |

| User Data | 010h (2048) | 010h (2336) | 018h (2048) | 018h (2324) | 000h (2352) |

| ECC & EDC | 810h (288)  | N/A         | 818h (280)  | 92Ch (4)    | N/A         |

| Subcode   | 980h (96)   |

| Q-channel | 9E0h (12)   |

**Note**: Table format: Starting offset address (No. of bytes)

■ If BIA (09h/08h) = 000Ch and RLC (2Bh.1-0) = 2, block size is C00h.

| Item      | Mode 1      | Mode 2      | Mode2 Form1 | Mode2 Form2 | CD-DA       |

|-----------|-------------|-------------|-------------|-------------|-------------|

| Sync      | 000h (12)   | 000h (12)   | 000h (12)   | 000h (12)   | N/A         |

| Header    | 00Ch (4)    | 00Ch (4)    | 00Ch (4)    | 00Ch (4)    | N/A         |

| Subheader | N/A         | N/A         | 010h (8)    | 010h (8)    | N/A         |

| User Data | 010h (2048) | 010h (2336) | 018h (2048) | 018h (2324) | 000h (2352) |

| ECC & EDC | 810h (288)  | N/A         | 818h (280)  | 92Ch (4)    | N/A         |

| C2 flag   | A00h (294)  |

| Subcode   | B80h (96)   |

| Q-channel | BE0h (12)   |

Preliminary/Confidential Subject to change without notice

The rule for configuration is that the first byte of the sector is stored at:

BIAH/L(09h/08h,w) - 0Ch

And the following byte is stored into the incremented offset address. If the offset address reaches the block limit, the next offset address is wrap around to zero. For example, the byte following that at offset 9FFh is at 000h if block limit is A00h. By this mechanism and following example settings, the first byte of user data is always located at 000h.

The Subcode (980h/B80h) and Q-channel (9E0h/BE0h) data are stored at fixed address if its associated function is enabled. But the 2352 bytes sector data (including sync, header, user data, ECC, EDC for Mode 1 sector) can be re-arranged to any other area in the block.

#### 2.2.1.3 Linear Transfer Address Counter

When LATXF (03h.w7) is high, the address defined by RACU/H/L (2Dh/1Dh/1Ch,w) is loaded to a internal Linear Transfer Address Counter at the begin of data transfer. This separate counter leaves RACU/H/L (2Dh/1Dh/1Ch,w) free for uP to DRAM access after the transfer is triggered. The uP can access DRAM data defined by RACU/H/L (2Dh/1Dh/1Ch,w) regardless the setting of LATXF (03h.w7).

# Winbond Electronics Corp.

## W88227F/W88227QD

Preliminary/Confidential Subject to change without notice

#### 2.2.1.4 Linear Address v.s. Block-Offset Address

The microprocessor can write/read external RAM through register *RAWR/RAMRD* (*1Eh*) based on linear address defined by *RACU/H/L* (*2Dh/1Dh/1Ch*,*w*). But the operation of data transfer from DRAM to host can base on block-offset address or linear address. The following equation defines the relation between these two types of address.

linear address = (block number × block size) + address offset

<Example 1> Data Transfer in Working Area

Conditions: 64 bytes of TOC data are stored starting from linear address 3EA00h at disc initialization and TOC is requested by host (block size is A00h).

- A) Sequence at disc initialization:

- a) set RACL (1Ch) as 00h

- b) set RACH (1Dh) as EAh

- c) set RACU (2Dh) as 03h

- d) wait UTBY (1Fh.7) low

- e) write data to register RAMWR (1Eh)

- f) goto step e) until all 64 bytes are written to DRAM

- B1) Setting for *block-offset address* transfer:

- set TBH/L (25h/24h) as 0064h

- set TACH/L (05h/04h) as 0200h

- set TWCH/L (03h/02h) as 001Fh

- B2) Setting for linear address transfer:

- set RACL (1Ch) as 00h

- set RACH (1Dh) as EAh

- set RACU (2Dh) as 03h

- set TWCH/L (03h/02h) as 801Fh

<Example 2> Data Transfer in User Area

Case 1: The 2048 bytes of user data are requested by host.

- set TBH/L (25h/24h) as 001Fh

- set TWCH/L (03h/02h) as 03FFh

- set TACH/L (05h/04h) as 0010h

Case 2: The 288 bytes of EDC&ECC data are request by host.

- set TBH/L (25h/24h) as 001Fh

- set TWCH/L (03h/02h) as 008Fh

- set TACH/L (05h/04h) as 0810h

If the requested data is not stored continuously in DRAM, e.g., header and EDC&ECC data, more than one transfer has to be triggered.

Preliminary/Confidential Subject to change without notice

## 2.2.2 Microcontroller Interface

## 2.2.2.1 Programmable System Clock

The internal system frequency is controlled by *CCTL1* (*1Ah,w*) and *PSKCTL* (*59h,w*). Register *PSKCTL* (*59h,w*) should be set before the programmable system clock is enabled by setting *PSKEN* (*1Ah.w4*) high. If both *PSKEN* (*1Ah.w4*) and *PSKSEL* (*59h,w*7) are high, *PSK5-0* (*59h.5-0*) are used to controlled the internal system frequency. Register *PSKCTL* (*59h,w*) should be set before the programmable system clock is enabled by setting *PSKEN* (*1Ah.w4*) high. The equation is:

frequency of system clock = frequency of ACLK  $\times$  (PSK[5:0] + 2)  $\div$  16 The variation of the resultant system frequency is normally less than 5%.

<example> If the frequency of ACLK is 33.8688 MHz, PSKEN (1Ah.w4) and PSKSEL (59h.w7) are high:

| PSK5-0 | System Frequency | Remark |

|--------|------------------|--------|

| 0Fh    | 36 MHz           |        |

| 11h    | 40.2 MHz         |        |

| 13h    | 44.4 MHz         |        |

| 15h    | 48.7 MHz         |        |

| 17h    | 53 MHz           |        |

| 19h    | 57.2 MHz         |        |

| 1Bh    | 61.4 MHz         |        |

Preliminary/Confidential Subject to change without notice

#### 2.2.3 Host Interface

The host interface is a standard ATAPI interface with enhanced Ultra DMA support. The Ultra DMA protocol could double the current burst transfer rate of 16.6MB/sec to 66MB/sec without hardware changes such as termination devices or different cabling.

## 2.2.3.1 Ultra DMA Mode Setting

This decoder is capable of supporting Ultra DMA Mode 4. Device firmware could claim that *Ultra DMA mode 4 and below are supported* in IDENTIFY DEVICE information.

The value of *UDT1-0* (8Ah,5-4) defines the Ultra DMA Timing Factor, *udtf*, which control the timing of Ultra DMA transfer.

$$Tcyc = (2 + udtf) \times Tudma$$

where Tudma is clock period depends on setting of *UDTA* (8Ah.6) and *UCLKS* (8Ah.3) and Tcyc is Ultra DMA cycle time (from DSTROBE edge to DSTROBE edge)

Device firmware should set *udtf* according to the clock source and the assigned Ultra DMA transfer mode after host issues SET FEATURE command. If there are frequent CRC errors in data-in bursts, device firmware may switch system to slower Ultra DMA mode by increasing *udtf* to improve data integrity.

*Example*: If *UCLKS* (8Ah.3) is high and frequency of ACLK is 33.8688MHz, the *udtf* should be the following value to abide by the determined Ultra DMA mode.

| Ultra DMA | T2cyc Min. Spec. | T2cyc   | udta | udtf |

|-----------|------------------|---------|------|------|

| Mode 0    | 230 ns           | 236 ns  | 0    | 2    |

| Mode 1    | 154 ns           | 177 ns  | 0    | 1    |

| Mode 2    | 115 ns           | 118 ns  | 0    | 0    |

| Mode 3    | 86 ns            | 88.6 ns | 1    | 1    |

| Mode 4    | 57 ns            | 60 ns   | 1    | 0    |

## 2.2.3.2 Ultra DMA Error Handling

Flag *UCRCOKb* (30h.r3) is used to determine if a CRC error event has occurred during latest Ultra DMA burst. If *AUCRCEN* (18h.2) and *ASCEN* (18h.5) are both set high, the automatic status complete logic would not be triggered if *UCRCOKb* (30h.r3) is high. Therefore, firmware should check *UCRCOKb* (30h.r3) flag after each Ultra DMA burst. If a CRC error has occurred, firmware should set *CHK* (37h.0) to one and manually trigger status complete.

Preliminary/Confidential Subject to change without notice

#### 2.2.3.3 Ultra DMA Data-out

The programming of Ultra DMA transfer is similar to that of Multi-word DMA transfer. One thing should be noted is that *device should prepare to receive one additional word at the end of a data out burst.* Since 12-byte Packet FIFOs are used to receive data in Ultra DMA data-out transfer, the value of registers TWCH/L (03h/02h) should be set 4 instead of 5. Then firmware should repeatedly read register PFAR (00h,r) after Transfer End Interrupt asserts until flag PFNEb (01h.r7) becomes one.

<example> data-out transfer sequence:

- 1. TENDEN (01h.w6)  $\leftarrow$  1

- 2. ASCTRL (18h,w)  $\leftarrow$  58h

- 3. HICTL0 (1Fh.w)  $\leftarrow$  0Bh // UDMA data-out

- 4. TWC  $(03h/02h,w) \leftarrow \min(0004h, byte\_cnt/2-1)$

- 5. ADTT (17h.w2)  $\leftarrow$  1 // automatic data transfer trigger

- 6. wait TENDb (01h.r6) = 0 and TDIR (30h.r5) = 1 and FPKT (30h.r1) = 1

- 7. TACK  $(07h,w) \leftarrow FFh$

- 8. read PFAR (00h,r); byte\_cnt =byte\_cnt 1

- 9. if PFNEb (01h.r7) is low, repeat step (8)

- 10. if (byte\_cnt  $\neq$  0) goto step (4)

- 11. SCT (17h.0)  $\leftarrow$  1 // status complete trigger

Preliminary/Confidential Subject to change without notice

## 2.2.3.4 BSY flag control

BSY is bit-7 of ATAPI Status Register.

| BSY set                                                                 | BSY clear                                                                      |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Chip reset                                                              | Set CLRBSY (20h.w4) if APKT (30h.r0) is low                                    |

| Host reset                                                              | Set DRQT (17h.w1) if PIO (1Fh.2) is high                                       |

| Set bit SRST in ATAPT Device Control Register                           | Host issue ATAPI Command (opcode A0h) if <i>APKTEN</i> (18h.7) is high         |

| Set SETBSY (20h.w3) if APKT (30h.r0) is low                             | Automatic Status Completion sequence, enabled by SCT (17h.w0) or ASCEN (18h.5) |

| Host issues Execute Diagnostics Command (opcode 90h)                    | DFRDYb (01h.r1) becomes low after ADTT (17h.w2) is set, if PIO (1Fh.2) is high |

| Host issue ATA Command when drive is selected                           |                                                                                |

| Transfer end if ADCEN (18h.6) is enabled                                |                                                                                |

| Set ADTT (17h.w2)                                                       |                                                                                |

| Set DSCT (17h.w5) if ABYEN (18h.1) is enabled - lasting 3 system clocks |                                                                                |

#### 2.2.3.5 Pin HIRQ control

*Pin HIRQ* is set or clear by the following conditions if the drive is selected and *nIEN* is enabled in the ATAPI Device Control Register.

HIRQ is activated by the following events:

- Automatic Packet Transfer sequence, enabled by APKTEN (18h.7)

- Automatic Status Completion sequence, enabled by SCT (17h.w0) or ASCEN (18h.5)

- Write MISC0 (2Eh) with bit-3 high

HIRQ is de-activated by the following events:

- Chip reset or host reset or firmware rest

- Set bit SRST in the ATAPI Device Control Register high

- Host issue ATA command while the drive is selected

- Host read ATAPI Status Register while the drive is selected

- Write MISCO (2Eh) with bit-3 low

Preliminary/Confidential Subject to change without notice

## 2.2.4 Decoder Logic

## 2.2.4.1 Sync Detection/Insertion

The sync field of CD-ROM data is recorded as following: 1 (00h) bytes, 10 (FFh) bytes and 1 (00h) byte. This sync field is detected for sector synchronization if *SDEN* (0Bh.w6) is enabled. To prevent loss of synchronization caused by broken sync, an internal counter can provide inserted sync signal if *SIEN* (0Bh.7) is enabled. There are no sync bytes in CD-DA format, so *SDEN* (0Bh.w6) should not be set.

#### 2.2.4.2 Descramble

Bytes 12 to 2351 of each CD-ROM sector is scrambled in decoding. Setting *DSCREN* (*0Bh.5*) high enables the descramble logic. Descramble logic should be disabled while reading of CD-DA data.

#### 2.2.4.3 Disk-Monitor Mode

The decoder logic is in disk-monitor mode if *CTRLO* (0Ah,w) is set as 80h. In disc-monitor mode, no ECC correction and EDC checking is carried. The sector ready interrupt flag *SRIb* (01h.r5) is immediately generated when the header bytes are available in *HEADO-3* (04h-07h,r). The header bytes in disc-monitor mode are less trustworthy than that in buffer-correction mode.

## 2.2.4.4 Parallel ECC Correction

The error correction of the CD-ROM sector is carried by a Reed-Solomon Product-Like Code (RSPC). The RSPC is a product code over  $GF(2^8)$  field which is generated by the primitive polynomial

$$P(x) = x^8 + x^4 + x^3 + x^2 + 1$$

The primitive element  $\alpha$  of  $GF(2^8)$  is

$$\alpha = (00000010)$$

where the right-most bit is the least significant bit.

The data is divided into high byte plane and low byte plane before decoding. The RSPC decoding, operating on bytes, is then applied twice, once to the high byte plane, once to the low byte plane.

To improve the efficiency of RSPC decoding, a parallel ECC correction logic is implemented on chip. After sync detection and descramble, the parallel ECC correction is carried on high byte plane and low byte plane simultaneously. This correction scheme is about 33% faster than conventional decoder.

The Q-code correction and P-code correction are enabled by *QCEN* (*0Ah.w1*) and *PCEN* (*0Ah.w0*) respectively. If both correction operations are enabled, Q-code correction is executed first. The corrected data are written back to external RAM if *CWEN* (*0Bh.w4*) is high.

Preliminary/Confidential Subject to change without notice

## 2.2.4.5 EDC Checking

The EDC checking logic carry 32-bit CRC checking on error corrected data according to its mode. The checking result can be monitored through flag CRCOK (OCh.r7). If the result is error, the errors in sector may exceed the capacity of correction logic and some data might be miscorrected.

## 2.2.4.6 Real Time EDC Checking

If real time EDC checking logic is enabled by setting *RTEDC* (0Ah.w6) high, the remainder of serial data is calculated while the sector is being buffered into DRAM. The sector ready interrupt flag *SRIb* (01h.r5) is immediately activated at next sync if the resultant remainder is zero, i.e., no EDC error. If there is error, the specified error correction is then applied to the buffered data. This function should not be enabled in disk-monitor mode.

#### 2.2.4.7 Disc Format Selection

Before enable decoder logic through register *CTRL0* (*0Ah*,*w*), appropriate value should be set to register *CTRL1* (*0Bh*,*w*) according to different disc format. If *ACEN* (*0Ah*,*w*4) and *M2RQ* (*0Bh*,*w*3) are both high, the type of error correction is automatically determined by FORM bit in the subheader byte rather than setting of *F2RQ* (*0Bh*,*w*2). The value of *ACEN* (*0Ah*,*w*4) does not affect the yellow-book mode-1 correction.

| disc format        | SIEN<br>(0Bh.7) | SDEN<br>(0Bh.6) | DESCREN<br>(0Bh.5) | CWEN<br>(0Bh.4) | M2RQ<br>(0Bh.3) | F2RQ<br>(0Bh.2) |

|--------------------|-----------------|-----------------|--------------------|-----------------|-----------------|-----------------|

| CD-DA              | 1               | 0               | 0                  | 0               | 0               | 0               |

| yellow book Mode 1 | 1               | 1               | 1                  | 1               | 0               | 0               |

| yellow book Mode 2 | 1               | 1               | 1                  | 0               | 0               | 0               |

| CD-ROM XA M2F1     | 1               | 1               | 1                  | 1               | 1               | 0               |

| CD-ROM XA M2F2     | 1               | 1               | 1                  | X               | 1               | 1               |

#### 2.2.4.8 DSP Main Data Format

If D2EN (1Bh.w3) is set high, pin C2PO/SDATA2 is used as second serial data input pin. The two-bit format can dramatically reduce the frequency on DSP main data interface and improve EMI.

| DSPSL | DSP Data Format  |  |

|-------|------------------|--|

| 07h   | Toshiba          |  |

| 0Bh   | Winbond two-bit  |  |

| 24h   | Sanyo            |  |

| A3h   | Sony 48-bit slot |  |

| C3h   | C3h Philip       |  |

Preliminary/Confidential Subject to change without notice

#### 2.2.4.9 CD-DA data & Q-channel Extraction

There are no sync bytes in CD-DA format, so absolute MSF bytes of *Mode 1Data-Q* (ADR = 0001) should be utilized as synchronization when reading CD-DA data. Q-channel extraction can be enabled by setting both *QEN* (80h.w5) and SCEN (2Ch.w6) high. Once decoder and Q-channel extraction are both enabled, the extracted Q-channel bytes are written into the DRAM starting from offset 9E0h of each block regardless of what mode of data is set.

The first byte of Q-channel (CONTROL and ADR) can be retrieved from offset 9E0h. When *QSIGEN* (21h.4) is set high, a signature 0xFFh will be placed in offset 9E0h if CRC checking of Q-code is erroneous.

The absolute MSF information can be retrieved from offset 9E7h, 9E8h and 9E9h of each block.

There is an alternative way to access MSF of Q-channel information. If control bit *QMSF* (80h.w4) is set high, the corresponding MSF bytes in Q-channel information would be automatically loaded into *HEAD0-2* (04h-06h,r) when each byte is ready from DSP. The register *HEAD3* (07h,r) hold first byte of *DATA-Q*, (CONTROL and ADR) or 0xFFh if CRC checking of Q-channel is erroneous.

If Q-channel extraction is enabled, device firmware can check flag *QCRCOK* (22h.r4) to see if there is a CRC error in the latest Q-channel information.

<example> SMD1 format setting:

- BIAH/L (09h/08h) = 000Ch

- CTRLW (10h.w) = 30h

- SICTL0 (21h) = 30h

- SICTL1 (2Ch,w) = 55h (SMD1 mode)

- QEN (80h.w5) = 1 and QMSF (80h.w4) = 1

- SDBS (88h.w4) = 1 and SBCK (88h.w3) = 1

- CTRL1 (0Bh.w) = 80h

- CTRL0 (0Ah.w) = 84h

- SCIb (01h.r0)

- SUBSTA (22h.r)

Following the above setting, there is no need to set SICTL (21h.w), SCBH/L (27h/26h,w) and SCTC (5Ah,w). In order to transfer the whole sector to host, 2352 bytes, the value in TWCH/L (03h/02h) should be 0497h and the value in TACH/L (05h/04h) should be 0000h.

Preliminary/Confidential Subject to change without notice

### 2.2.4.10 Target Search

The target search logic is initialized by: (1) setting Search Limit, (2) setting Target and (3) setting TARGEN (80h.w7) high. After the decoding is triggered through CTRLO (0Ah,w), the first sector ready interrupt is generated when: i) the target sector is found, ii) header is larger than target or iii) search limit is reached. If event ii) or iii) occurs, the microprocessor may read out HEADO-2 (04h-06,r) to determine the current distance from target. Setting LTTIEN (80h.w2) and TNFEN (80h.w1) high can generate the associated interrupt flag on SRIb (01h.r5) before the target is found.

#### 2.2.4.11 Automatic Header Comparison

The automatic header comparison logic is enabled by setting *TARGEN* (80h.w7) and *HCEEN* (80h.w0) high. After the first target is found, the value in *TARGET* (84h-86h) increases from (T - 1) to T. And the decoder is changed from disk-monitor mode to buffer-correction mode. Then *HEADO-2* (04h-06h,r) are compare with *TARGET* (84h-86h) and generate flag *HCEI* (80h.r0) at the end of EDC-checking. Unless flag *STAERR* (80h.r6) or *HCEI* (80h.r0) is generated, the value in *TARGET* (84h-86h) is automatically incremented by one and ready to be compared with next sector.

#### 2.2.4.12 Status Collection

The status collection logic is enabled if any bit in the *Status-Mask-Register* (8Ch-8Fh,w) is set high. At the end of EDC-checking, flag STAERR (80h.r6) becomes high if any status bit error that is enabled by its associating mask bit occurs. The microprocessor can reduce the system overhead by checking STAERR (80h.r6) rather than reading out STAT (0Ch-0Fh,r).

## 2.2.4.13 Buffer-Independent-Correction

Buffer-Independent-Correction (BIC) is enabled if BICEN (9Ah.7) is high. In BIC mode, the correction is triggered when the sectors not decoded in buffer is larger than one. In BIC mode, the DDBH/L (29h/28h) controls the decoding block and increments at the end of EDC-checking, except erroneous sectors. Meanwhile, the buffering block (internal) increments at each sync. Because of the independence of the buffering block and decoding block, the automatic repeat correction can be enabled by setting RCLIM3-0 (9Ch.3-0) the maximum rounds of repeat correction.

## 2.2.4.14 Remove Frequent SRIb & Automatic Cache Management

Control bit *RMSRI* (5Ch.0) should be set when entering buffer mode and be disabled in decoder\_off routine. When *RMSRI* (5Ch.0) is high, flag *SRIb* (01h.r5) is generated only by *STAERR* (80h.r6), *LASTBK* (80h.r3) or *HCEI* (80h.r0).

So after the target is found and buffer-correction mode is enabled, the first interrupt is generated by *LASTBK* (80h.r3) if there is no decoding error. Setting *RMSRI* (5Ch.0) high can reduce the overhead of microcontroller while the automatic cache management is used.

Preliminary/Confidential Subject to change without notice

Since the *SRIb* (01h.r5) interrupt is removed except for erroneous sectors, the cache management should be implemented through *TCC* (9Dh). If *TCINCEN* (9Ch.5) is high, *TCC* (9Dh) increments at the end of EDC-checking if there is no *STAERR* (80h.r6) or *HCEI* (80h.r0) error. If *ACMEN* (9Ch.6) is high, *TCC* (9Dh) decrements at the end of each data-in block transfer. The transfer of working area data should be implemented as linear transfer to prevent error.

Writing value to SKIPC (9Eh) can be used to implement the cache-partial-hit event. For the cache-miss event, TCC (9Dh) should be set 0.

The stop of DSP buffering is implemented by following setting ininitialization to prevent buffer wrap-around:

- $BICCTL(9Ah) \leftarrow B0h$

- BUFLIM (9Bh)  $\leftarrow$  cache\_limit

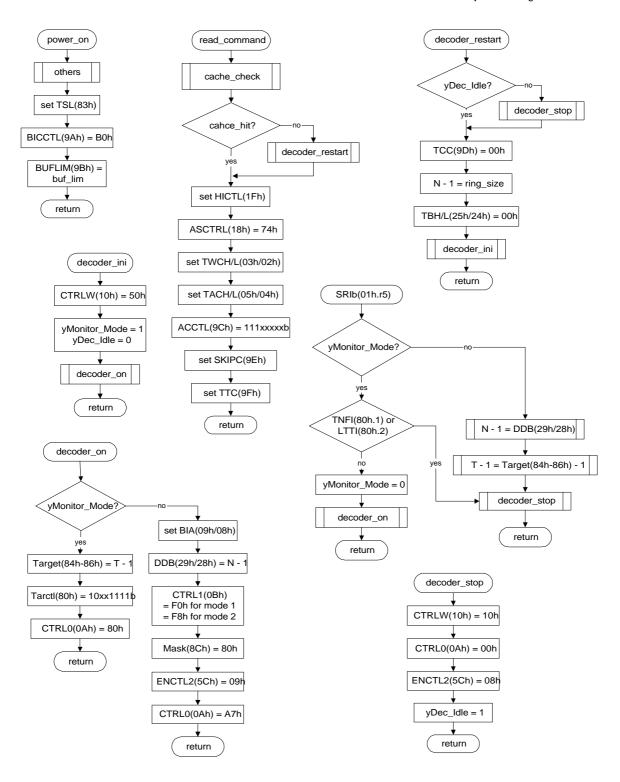

The following figure shows an example flowchart under following conditions:

- Buffer-Independent-Correction is enabled

- Remove frequent SRIb is enabled in buffer mode

- Automatic transfer and cache management is enabled

- Linear address transfer for working area data is enabled

In this case, the flag *TENDb* (01h.r6) is generated only when the last block is transferred to host, i.e., *TTC* (9Fh) is zero.

Preliminary/Confidential Subject to change without notice

## 2.2.5 Audio-playback

## 2.2.5.1 Configuration Phase

- 1. Configure input/output pin for Audio-playback through APCNF (90h).

- Bit 6: Audio Playback Interrupt Enable

- Bit 4: Audio Reference Clock Select

- Bit 3,2: Audio Input Reference Clock Setting

- Bit 1:0: Audio Data Output Setting

- 2. Select Audio-playback output format through APFMT (91h).

After configuration, pin ABCK becomes active but data pin keep "mute."

## 2.2.5.2 Playback Phase

If the desired data sectors are buffered in DRAM, the following steps can trigger audio playback:

- 1. Set Audio-playback start block through APBKH/L (93h/92h).

- 2. Enable Audio-playback by setting APEN (90h.7) high.

- 3. Wait for interrupt or polling flag APIb (01h.r2).

- 4. If APIEN (90h.6) is enabled, write APACK (97h,w) to deactivate audio-playback-interrupt.

- 5. If buffer is not empty or end of command, go to step 3.

- 6. Disable Audio-playback by setting APEN (90h.7) low.

The status of playback is directly controlled by the setting of *APEN (90h.7)*. So the buffer should be carefully managed to prevent noise or broken song.

## 2.2.5.3 IEC-958 Digital Audio Output

The digital output function complies with the IEC-958 standard. This internal function is automatically enabled after configuration of audio playback function. The digital audio signal is output to *pin GPIO2/DAOOUT/nFCE* when *DAOEN (87h.7)* is set high after master reset.

Preliminary/Confidential Subject to change without notice

## 2.2.6 Function Differences Between W88227 and W88113CF

| W88227                                                                                                                         | W88113CF                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Internal Linear Address Transfer Counter is added                                                                              | RAC(1Ch,1Dh,2Dh) can not be accessed during linear address transfer                         |

| TARGET (84h-86h) decrement by setting TARDEC (16h.w0) high                                                                     | TARGET decrement must be performed by uP                                                    |

| Host write to Packet FIFO generate Automatic Status<br>Completion only if ASCEN (18h.w5) is high and<br>PFFACB (01h.w3) is low | Host write to Packet FIFO generate Automatic Status<br>Completion if ASCEN (18h.w5) is high |

| TCC (9Dh) update source is controlled by TCCCTL (58h.3-0)                                                                      | , n/a                                                                                       |

| Also support 2 nRWE DRAM                                                                                                       | Support 2 CAS DRAM only                                                                     |

| CTRL0 can read from 0Ah                                                                                                        | CTRL0 is write only to 0Ah                                                                  |

| CTRL1 can read from 0Bh                                                                                                        | CTRL1 is write only to 0Bh                                                                  |

| TARCTL can read from 10h                                                                                                       | TARCTL is write only to 80h                                                                 |

| INTCTL can read from 11h                                                                                                       | INTCTL is write only to 01h                                                                 |

| SICTL0 cand read from 21h                                                                                                      | SICTL1 is write only to 21h                                                                 |

| MEMCF can read from 2Bh                                                                                                        | MEMCF is write only to 2Bh                                                                  |

| SICTL1 can read from 2Ch                                                                                                       | SICTL1 is write only to 2Ch                                                                 |

| New control bit PFFACB (01h.w3)                                                                                                | n/a                                                                                         |

| New control bit TARDEC (16h.w0)                                                                                                | n/a                                                                                         |

| New control bit TARINC (16h.w1)                                                                                                | n/a                                                                                         |

| New control bit TARINC7 (16h.w2)                                                                                               | n/a                                                                                         |

| New control bit D2EN (1Ah.w3)                                                                                                  | n/a                                                                                         |

| New control bit ASCEND (21h.6)                                                                                                 | n/a                                                                                         |

| New control bit QSIGEN (21h.5)                                                                                                 | n/a                                                                                         |

| New control bit TWES (2Bh.3)                                                                                                   | n/a                                                                                         |

| New register RASTA (2Dh,r)                                                                                                     | n/a                                                                                         |

| Control bits (2Fh.w3-2) are re-defined                                                                                         | Control bits (2Fh.w3-2) as ARSTS                                                            |

| New global control registers (40h-43h)                                                                                         | n/a                                                                                         |

| New register TCCCTL (58h)                                                                                                      | n/a                                                                                         |

| New control bit DSPDW (5Bh.2)                                                                                                  | n/a                                                                                         |

| New control bit UDTA (8Ah.6)                                                                                                   | n/a                                                                                         |

| New control bit APACENB (93h.5)                                                                                                | n/a                                                                                         |

| HRSTS (2Fh.w5-4) are obsolete                                                                                                  | available                                                                                   |

| ALRT (5Bh.3) is obsolete                                                                                                       | available                                                                                   |

| ASRIT (5Bh.6) is obsolete                                                                                                      | available                                                                                   |

| ALE2 (5Ch.3) is obsolete                                                                                                       | available                                                                                   |

| LSTA (48h-4Bh), LHD (4Ch-4Fh) are obsolete                                                                                     | available                                                                                   |

Preliminary/Confidential Subject to change without notice

# 2.2.7 Decoder Register Map

| index         type         name         bit7         bit6         bit5         bit4         bit3         bit2         bit1         bit9           -         r'w         IR         -         -         index         bot         b5         b4         B3         b2         b1         b0           00h         r         PPAR         b7         b6         b5         b4         b3         b2         b1         b0           01h         r         INTREA         pfnee         tende         srib         hcib         tbsyb         apib         dirdyb         scib           02h         r/w         TWCI         b7         b6         b5         b4         b3         b2         b1         b0           03h         r/w         TWCH         latx         x         x         x         b1         b1         b0         b8           04h         r         TXCL         47         a6         a5         a4         a3         a2         a1         a0           05h         r         TACH         a15         a14         a13         a12         a11         a10         a9         a8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |      |        |         |                    |        |             |             |         |        |        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|--------|---------|--------------------|--------|-------------|-------------|---------|--------|--------|

| Online   O | index | type |        | bit7    | bit6               | bit5   | bit4        | bit3        | bit2    | bit1   | bit0   |

| Online                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -     | r/w  | IR     |         |                    |        | inc         | lex         |         |        |        |