## 1. INTRODUCTION

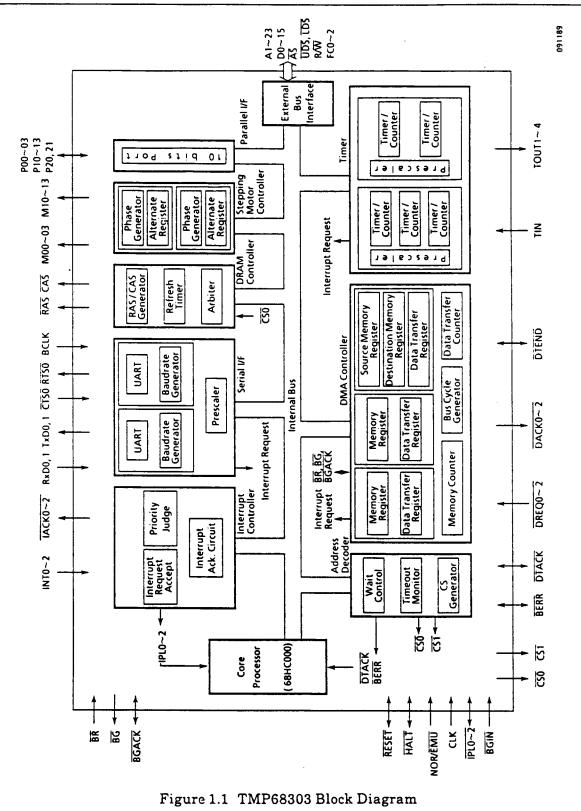

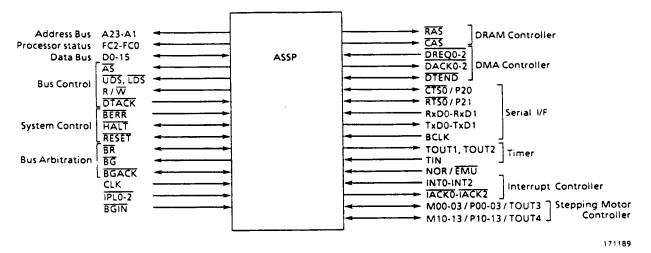

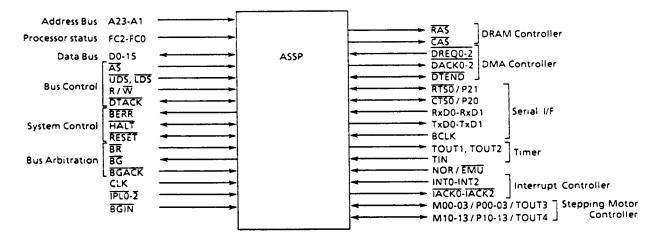

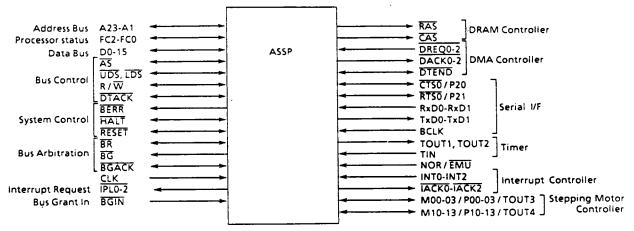

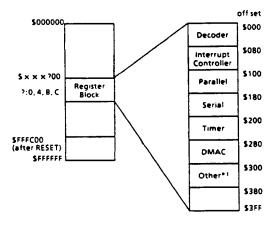

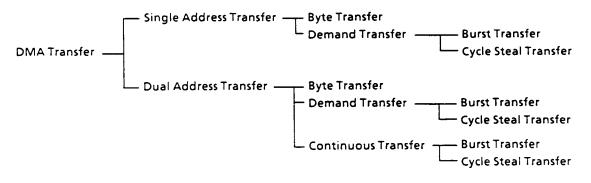

This product is an ASSP (Application Specific Standard product) with a 68HC000 MPU core and built-in serial I/F, parallel I/F, timer, interrupt controller, address decoder, DMA controller, DRAM controller and stepping motor controller as peripheral devices.

Features

Core : 68HC000

System clock : 16MHz max. (target)

- 17 32-bit register

- 16 M-byte direct addressing

- 56 powerful basic instructions

- 14 addressing modes

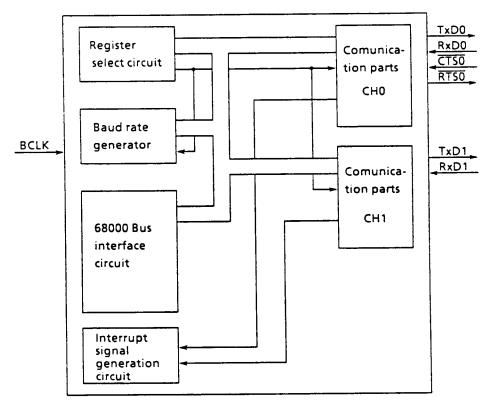

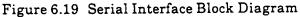

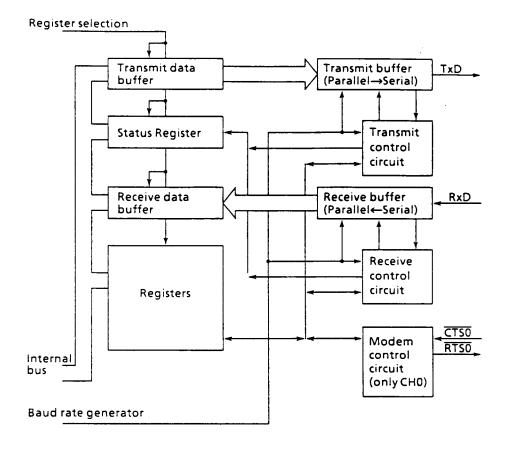

- Serial I/F : 2-channel (UART)

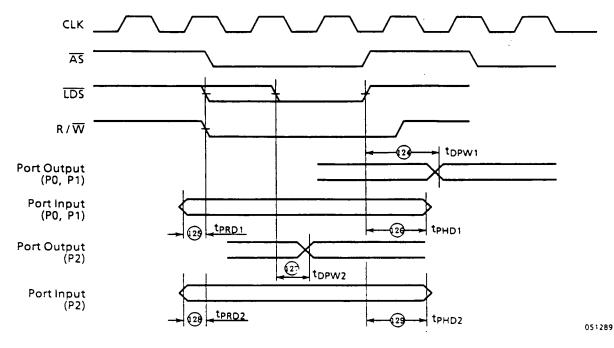

- Parallel I/F: 10-bit I/O

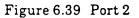

- Timer : 5-channel (include built-in watchdog timer)

- Interrupt controller : 12-channel (external : 3 channels, internal : 9 channels)

- Address decoder : built-in

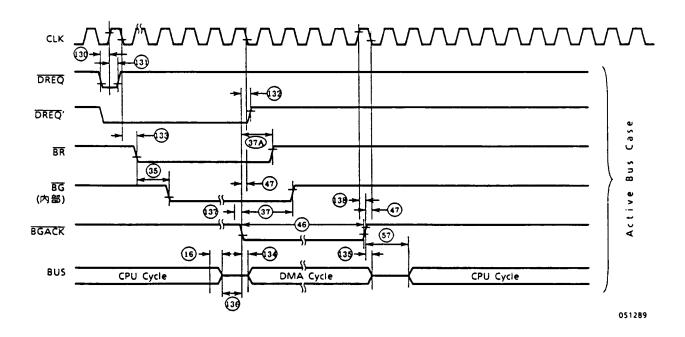

- DMA controller : 3-channel

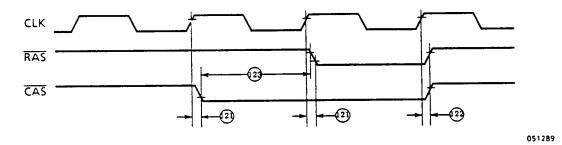

- DRAM controller : RAS, CAS, multiplexed address, A1~A9 (A10)

- Stepping motor controller : 2-channel, 4-phase

- Chip Select Signal : CS0, CS1

- Automatic wait state insertion

- Bus error detection

- Low power consumption (CMOS)

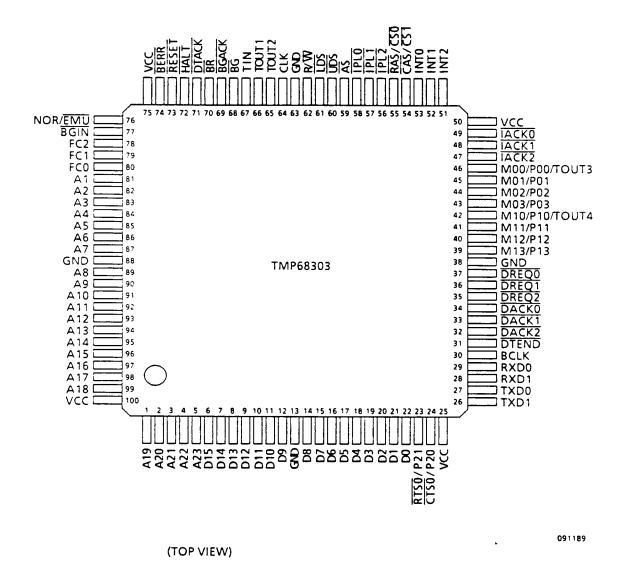

Figure 1.1 shows TMP68303 configuration.

TMP68303 has two operation modes. One is the normal operation mode and the other is the emulation mode for using 68000 development tools (ICE). In the emulation mode, the 68HC000 core does not operate and the built-in peripheral devices are operated by external address/data control signal.

The 68HC000 core is the same as the TMP68HC000, except that the 8-bit peripheral devices control signals E,  $\overline{VPA}$  and  $\overline{VMA}$  are not used. Those already familiar with the TMP68HC000 should read the following items related to peripheral devices.

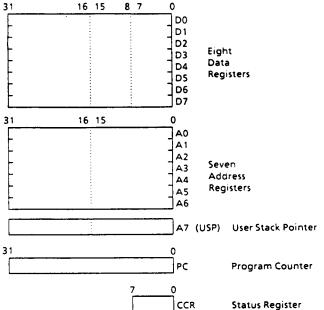

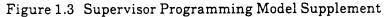

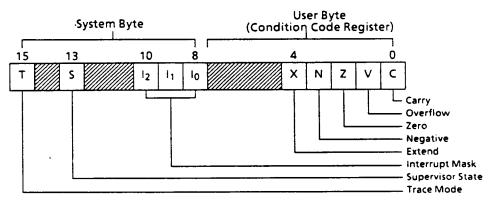

As shown in the programming models (Figures 1.2 and 1.3), the TMP68303 has seventeen 32-bit registers, a 32-bit programming counter and a 16-bit status register (the lower bits are the condition code register).

The first 8 registers (D0-D7) shown in Figure 1.2 are data registers and can be used as byte (8-bit), word (16-bit) and long word(32-bit) operands. The next 7 registers(A0-A6) and user stack pointer (USP) can be used as the software stack pointer and base address register. In addition, these registers can be used as word and long word operands. All 16 registers are used as index registers.

MPU-2

Powered by ICminer.com Electronic-Library Service CopyRight 2003

TOSHIBA

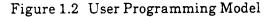

In the supervisor mode, the upper bytes of status register and the supervisor stack pointer (SSP) can be freely used (Figure 1.3).

The status register (Figure 1.4) contains the extend (X) flag, negative sign (N) flag, zero (Z) flag, overflow (V) flag and carry (C) flag as well as the mask bit (8 possible levels). Trace mode (T) and supervisor state (S) bits are also provided as status bits.

### 1.1 DATA TYPES AND ADDRESSING MODES

Five basic data types are supported. These data types are:

- Bits

- BCD Digits (4 bits)

- Bytes (8 bits)

- Words (16 bits)

- Long Words (32 bits)

In addition, operations on other data types such as memory addresses, status word data, etc., are provided in the instruction set.

The 14 address modes, shown in Table 1.1, include six basic types:

- Register Direct

- Register Indirect

- Absolute

- Program Counter Relative

- Immediate

- Implied

Included in the register indirect addressing modes is the capability to do postincrementing, predecrementing, offsetting, and indexing. The program counter relative mode can also be modified via indexing and offsetting.

| Register Direct Addressing<br>Data Register Direct<br>Address Register Direct<br>Absolute Data Addressing<br>Absolute Short<br>Absolute Long | Dn<br>An<br>Abs.W |

|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Address Register Direct<br>Absolute Data Addressing<br>Absolute Short                                                                        | An                |

| Absolute Data Addressing<br>Absolute Short                                                                                                   |                   |

| Absolute Short                                                                                                                               | Abs.W             |

| Absolute Short                                                                                                                               | Abs.W             |

| Absolute Long                                                                                                                                |                   |

|                                                                                                                                              | Abs.L             |

| Program Counter Relative Addressing                                                                                                          |                   |

| Relative with Offset                                                                                                                         | d16 (PC)          |

| Relative with Index Offset                                                                                                                   | d8 (PC, Xn)       |

| Register Indirect Addressing                                                                                                                 |                   |

| Register Indirect                                                                                                                            | (An)              |

| Postincrement Register Indirect                                                                                                              | (An) +            |

| Predecrement Register Indirect                                                                                                               | - (An)            |

| Register Indirect with Offset                                                                                                                | d16 (An)          |

| Indexed Register Indirect with Offset                                                                                                        | d8 (An, Xn)       |

| Immediate Data Addressing                                                                                                                    |                   |

| Immediate                                                                                                                                    | #xxx              |

| Quick Immediate                                                                                                                              | #1~#8             |

| Table 1.1 | Addressi | ng Modes |

|-----------|----------|----------|

|-----------|----------|----------|

- Notes : Dn = Data Register

- An = Address Register

- Xn = Address or Data Register used as Index Register

- SR = Status Register

- PC = Program Counter

- SP = Stack Pointer

- USP = User Stack Pointer

- () = Effective Address

- = 8-Bit Offset (Displacement) d8

- d16 = 16-Bit Offset (Displacement)

- #xxx =Immediate Data

#### 1.2 INSTRUCTION SET OVERVIEW

The TMP68303 instruction set is shown in Table 1.2. Some additional instructions are variations, or subsets, of these and they appear in Table 1.3. Special emphasis has been given to the instruction set's support of structured high-level languages to facilitate ease of programming. Each instruction, with few exceptions, operates on bytes, words, and long words and most instructions can use any of the 14 addressing modes. Combining instruction types, data types, and addressing modes, over 1000 useful instructions are provided. These instructions include signed and unsigned, multiply and divide, "quick"arithmetic operations, BCD arithmetic, and expanded operations (through traps).

| Mnemonic | Description                          |

|----------|--------------------------------------|

| ABCD     | Add Decimal with Extend              |

| ADD      | Add                                  |

| AND      | Logical And                          |

| ASL      | Arithmetic Shift Left                |

| ASR      | Arithmetic Shift Right               |

| Bcc      | Branch Conditionally                 |

| BCHG     | Bit Test and Change                  |

| BCLR     | Bit Test and Clear                   |

| BRA      | Branch Always                        |

| BSET     | Bit Test and Set                     |

| BSR      | Branch to Subroutine                 |

| BTST     | Bit Test                             |

| CHK      | Check Register Against Bounds        |

| CLR      | Clear Operand                        |

| CMP      | Compare                              |

| DBcc     | Test Condition, Decrement and Branch |

| DIVS     | Signed Divide                        |

| DIVU     | Unsigned Divide                      |

| EOR      | Exclusive Or                         |

| EXG      | Exchange Registers                   |

| EXT      | Sign Extend                          |

| JMP      | Jump                                 |

| JSR      | Jump to Subroutine                   |

| LEA      | Load Effective Address               |

| LINK     | Link Stack                           |

| LSL      | Logical Shift Left                   |

| LSR      | Logical Shift Right                  |

Table 1.2Instruction Set Summary (1/2)

| Mnemonic | Description                  |

|----------|------------------------------|

| MOVE     | Move                         |

| MOVEM    | Move Multiple Registers      |

| MOVEP    | Move Peripheral Data         |

| MULS     | Signed Multiply              |

| MULU     | Unsigned Multiply            |

| NBCD     | Negate Decimal with Extend   |

| NEG      | Negate                       |

| NOP      | No Operation                 |

| NOT      | One's Complement             |

| OR       | Logical OR                   |

| PEA      | Push Effective Address       |

| RESET    | Reset External Devices       |

| ROL      | Rotate Left without Extend   |

| ROR      | Rotate Right without Extend  |

| ROXL     | Rotate Left with Extend      |

| ROXR     | Rotate Right with Extend     |

| RTE      | Return from Exception        |

| RTR      | Return and Restore           |

| RTS      | Return from Subroutine       |

| SBCD     | Subtract Decimal with Extend |

| Scc      | Set Conditional              |

| STOP     | Stop                         |

| SUB      | Subtract                     |

| SWAP     | Swap Data Register Halves    |

| TAS      | Test and Set Operand         |

| TRAP     | Trap                         |

| TRAPV    | Trap on Overflow             |

| TST      | Test                         |

| UNLK     | Unlink                       |

Table 1.2 Instruction Set Summary (2/2)

|                     | 1                                                                               | rations of flist action Types                                                                                                                    |

|---------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction<br>Type | Variation                                                                       | Description                                                                                                                                      |

| ADD                 | ADD<br>ADDA<br>ADDQ<br>ADDI<br>ADDX                                             | Add<br>Add Address<br>Add Quick<br>Add Immediate<br>Add with Extend                                                                              |

| AND                 | AND<br>ANDI<br>ANDI to CCR<br>ANDI to SR                                        | Logical And<br>AND Immediate<br>AND Immediate to Condition Codes<br>AND Immediate to Status Register                                             |

| СМР                 | СМР<br>СМРА<br>СМРМ<br>СМРІ                                                     | Compare<br>Compare Address<br>Compare Memory<br>Compare Immediate                                                                                |

| EOR                 | EOR<br>EORI<br>EORI to CCR<br>EORI to SR                                        | Exclusive OR<br>Exclusive OR Immediate<br>Exclusive OR Immediate to Condition Codes<br>Exclusive OR Immediate to Status Register                 |

| MOVE                | MOVE<br>MOVEA<br>MOVEQ<br>MOVE from SR<br>MOVE to SR<br>MOVE to CCR<br>MOVE USP | Move<br>Move Address<br>Move Quick<br>Move from Status Register<br>Move to Status Register<br>Move to Condition Codes<br>Move User Stack Pointer |

| NEG                 | NEG<br>NEGX                                                                     | Negate<br>Negate with Extend                                                                                                                     |

| OR                  | OR<br>ORI<br>ORI to CCR<br>ORI to SR                                            | Logical OR<br>OR Immediate<br>OR Immediate to Condition Codes<br>OR Immediate to Status Register                                                 |

| SUB                 | SUB<br>SUBA<br>SUBI<br>SUBQ<br>SUBX                                             | Subtract<br>Subtract Address<br>Subtract Immediate<br>Subtract Quick<br>Subtract with Extend                                                     |

Table 1.3 Variations of Instruction Types

## TOSHIBA

# 2. DATA ORGANIZATION AND ADDRESSING CAPABILITIES

This section contains a description of the registers and the data organization of the TMP68303.

#### 2.1 OPERAND SIZE

Operand sizes are defined as follows: a byte equals 8 bits, a word equals 16 bits, and a long word equals 32 bits. The operand size for each instruction is either explicitly encoded in the instruction or implicitly defined by the instruction operation. Implicit instructions support some subset of all three sizes.

## 2.2 DATA ORGANIZATION IN REGISTERS

The eight data registers support data operands of 1, 8, 16, or 32 bits. The seven address registers together with the stack pointers support address operadnds of 32 bits.

#### 2.2.1 Data Registers

Each data register is 32 bits wide. Byte operadns occupy the low order 8 bits, word operands the low order 16 bits, and long word operands the entire 32 bits. The least significant bit is addressed as bit zero; the most significant bit is addressed as bit 31.

When a data register is used as either a source or destination operand, only the appropriate low order portion is changed; the remaining high order portion is neither used nor changed.

#### 2.2.2 Address Registers

Each address register and the stack pointer is 32 bits wide and holds a full 32-bit address. Address registers do not support the sized operands. Therefore, when an address register is used as a source operand, either the low order word or the entire long word operand is used depending upon the operation size. When an address register is used as the destination operand, the entire register is affected regardless of the operation size. If the operation size is word, any other operands are sign extended to 32 bits before the operation is performed.

#### 2.3 DATA ORGANIZATION IN MEMORY

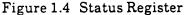

Bytes are individually addressable with the high order byte having an even address the same as the word, as shown in Figure 2.1. The low order byte has an odd address that is one count higher than the word address. Instructions and multibyte data are accessed only on word (even byte) boundaries. If a long word datum is located at address n (n even), then the second word of that datum is located at address n+2.

Figure 2.1 Word Organization in Memory

The data types supported by the TMP68303 are: bit data, integer data of 8, 16, or 32 bits, 32-bit addresses and binary coded decimal data. Each of these data types is put in memory, as shown in Figure 2.2. The numbers indicate the order in which the data accessed from the core processor.

|         |                 |          |            |                           | 1       | Bit E<br>Byte   |               | its       |       |                         |          |        |          |          |

|---------|-----------------|----------|------------|---------------------------|---------|-----------------|---------------|-----------|-------|-------------------------|----------|--------|----------|----------|

|         |                 |          | 7          | 6                         | 5       | 4               | 3             | 2         | 1     | 0                       |          | ,      |          |          |

|         |                 |          |            |                           |         |                 |               |           |       |                         |          |        |          |          |

|         |                 |          |            |                           | In<br>1 | itege<br>Byte : | r Da<br>= 8 B | ta<br>its |       |                         |          |        |          |          |

| 15 14   | 13              | 12       | 11         | 10                        | 9       | 8               | 7             | 6         | 5     | 4                       | 3        | 2      | 1        | 0        |

| MSB     |                 | Byte     | 0          |                           |         |                 |               |           |       | Byte                    |          |        |          | LSB      |

|         |                 | Byte     |            |                           |         |                 |               |           |       | Byte                    |          |        |          |          |

|         |                 |          |            |                           | 1 1.0   | /ord :          | 10            | D:44      |       |                         |          |        |          |          |

| 15 14   | 13              | 12       | 11         | 10                        | 9       | 70ra :<br>8     | 7             | 6         | 5     |                         | 2        | 7      | •        | 0        |

| MSB     | 15              | 12       |            | _10                       |         | o<br>Word       |               | 0         | 5     | 4                       | 3        | 2      | 1        | 0<br>LSB |

|         |                 |          |            |                           |         | Word            |               |           |       |                         |          |        |          | 230      |

|         |                 |          |            |                           |         | Word            |               | <u> </u>  |       |                         |          |        |          |          |

| ·       |                 |          |            |                           |         |                 |               |           |       |                         |          |        |          |          |

| 15 14   |                 |          |            |                           | -       | g Wo            |               |           |       |                         | _        | _      |          | _        |

|         |                 | 12       |            | 10                        | 9       | 8               | 7             |           |       | 4                       | 3        | 2      | 1        |          |

| MSB L   | ong.            | Wor      | <u>a u</u> | ••••••                    | •••••   |                 | yn O<br>w Or  | rder      | ••••• |                         | •••••••• | •••••  | ••••     | 150      |

|         | 200             | Wor      | d 1        |                           |         | - 10            | <u>~ 01</u>   | uer       |       |                         |          |        |          | LSB      |

|         | 2.1. <b>9</b> . | ••••     | <u></u>    | •••••••••                 | •••••   | •••••           |               | •••••     |       | ••••••                  | ••••••   | •••••  | •••••    | •••••    |

| L       | ong             | Wor      | d 2        |                           |         |                 |               |           |       |                         |          |        |          |          |

|         |                 |          |            | • • • • • • • • • • • • • | •••••   |                 | •••••         |           |       | •••••                   |          | •••••  | •••••    |          |

|         |                 |          |            | 1                         |         | Addr<br>dress   |               |           |       |                         |          |        |          |          |

| 15 14   | 13              | 12       | 11         | 10                        | 9       | 8               | 7             | 6         | 5     | 4                       | 3        | 2      | 1        | 0        |

| MSB A   | ddre            | ess O    |            |                           |         |                 | h O           |           |       |                         |          |        |          |          |

|         |                 |          |            |                           |         | Lov             | v Or          | der       |       |                         |          |        |          | LSB      |

| A       | ddre            | ess 1    |            |                           | <b></b> |                 |               |           |       |                         |          |        |          | ]        |

|         |                 |          |            |                           |         |                 |               |           |       | _                       |          |        |          |          |

| A       | ddre            | ess 2    |            | • • • • • • • • • • • • • | •••••   |                 |               |           |       | · · · · • • • • • • • • |          | ·····  | <b>.</b> |          |

|         |                 | <u> </u> |            |                           |         |                 |               |           |       | <u> </u>                |          |        |          |          |

| MSB = N | lost            | Sign     | itica      | nt Bit                    |         |                 |               | L         | .SB = | Leas                    | it Sig   | Initio | cant     | BIT      |

|         |                 | 2        | Bina       | ry Co                     |         | ecima<br>l Dec  |               |           | its = | 1 Byt                   | e        |        |          |          |

| 15 14   | 13              | 12       | 11         | 10                        | 9       | 8               | 7             | 6         | 5     | 4                       | 3        | 2      | 1        | 0        |

| MSD B   | CD0             |          |            | BCD1                      | **      | LSD             |               | BC        | D2    |                         |          |        | D3       |          |

| В       | CD4             |          |            | BCD5                      |         |                 |               | BC        | _     |                         |          |        | D7       |          |

|         |                 | -        |            | -                         |         |                 |               |           |       |                         |          |        |          |          |

Figure 2.2 Memory Data Organization

LSD = Least Significant Digit

MPU-11

MSD = Most Significant Digit

## TOSHIBA

## 2.4 ADDRESSING

Instructions for the TMP68303 contain two kinds of information: the type of function to be performed and the location of the operand(s) on which to perform that function. The methods used to locate (address) the operand(s) are explained in the following paragraphs.

Instructions specify an operand location in one of three ways:

| Register Specification | - | the number of the register is given in the register field of their instruction. |

|------------------------|---|---------------------------------------------------------------------------------|

| Effective Address      | - | use of the different effective addressing modes.                                |

| Implicit Reference     | - | the definition of certain instructions implies the use of specific registers.   |

## 2.5 INSTRUCTION FORMAT

Instructions are from one to five words in length as shown in Figure 2.3. The length of the instruction and the operation to be performed is specified by the first word of the instruction which is called the operation word. The remaining words further specify the operands. These words are either immediate operands or extensions to the effective address mode specified in the operation word.

| 15                                                            | 0     |

|---------------------------------------------------------------|-------|

| Operation Word (First Word Specifies Operation and Modes)     |       |

| Immediate Operand (If Any, One or Two Words)                  |       |

| Source Effective Address Extension (If Any, One or Two Words) |       |

| Destination Effective Address Extension (If Any, One or Two W | ords) |

Figure 2.3 Instruction Operation Word General Format

## 2.6 PROGRAM/DATA REFERENCES

The TMP68303 separates memory references into two classes: program references and data references. Program references, as the name implies, are references to that section of memory that contains the program being executed. Data references refer to that section of memory that contains data. Operand reads are from the data space except in the case of the program counter relative addressing mode. All operand writes are to the data space.

## 2.7 REGISTER SPECIFICATION

The register field within an instruction specifies the register to be used. Other fields within the instruction specify whether the register selected is an address or data register and how the register is to be used.

### 2.8 EFFECTIVE ADDRESS

Most instructions specify the location of an operand by using the effective address field in the operation word. For example, Figure 2.4 shows the general format of the single-effective-address instruction operation word. The effective address is composed of two 3-bit fields: the mode field and the register field. The Value in the mode field selects the different address modes. The register field contains the number of a register.

The effective address field may require additional information to fully specify the operand. This additional information, called the effective address extension, is contained in the following word or words and is considered part of the instruction, as shown in Figure 2.3. The effective address modes are grouped into three categories: register direct, memory addressing, and special.

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4    | 3 | 2  | 1     | 0  |

|----|----|----|----|----|----|---|---|---|---|---|------|---|----|-------|----|

| ×  | ×  | ×  | ×  | ×  | ×  | × | × | × | × | 1 | Mode |   | Re | egist | er |

|    |    |    |    |    |    |   |   |   |   | L |      |   | 1  |       |    |

Effective Address

Figure 2.4 Single Effective Address Instruction Operation Word

2.8.1 Register Direct Modes

These effective addressing modes specify that the operand is in one of 16 multifunction registers.

2.8.1.1 Data Register Direct

The operand is in the data register specified by the effective address register field.

2.8.1.2 Address Register Direct

The operand is in the address register specified by the effective address register field.

2.8.2 Memory Address Modes

These effective addressing modes specify that the operand is in memory and provide the specific address of the operand.

### 2.8.2.1 Address Register Indirect

The address of the operand is in the address register specified by the register field. The reference is classified as a data reference with the exception of the jump and jumpto-subroutine instructions.

### 2.8.2.2 Address Register Indirect with Postincrement

The address of the operand is in the address register specified by the register field. After the operand address is used, it is incremented by one, two, or four depending upon whehter the size of the operand is byte, word, or long word. If the address register is the stack pointer and the operand size is byte, the address is incremented by two rather than one to keep the stack pointer on a word boundary. The reference is classified as a data reference.

2.8.2.3 Address Register Indirect with Predecrement

The address of the operand is in the address register specified by the register field. Before the operand address is used, it is decremented by one, two, or four depending upon whether the operand size is byte, word, or long word. If the address register is the stack pointer and the operand size is byte, the address is decremented by two rather than one to keep the stack pointer on a word boundary. The reference is classified as a data reference.

## 2.8.2.4 Address Register Indirect with Displacement

This addressing mode requires one word of extension. The address of the operand is the sum of the address in the address register and the sign-extended 16-bit displacement integer in the extension word. The reference is classified as a data reference with the exception of the jump and jump-to-subroutine instructions.

2.8.2.5 Address Register Indirect with Index

This addressing mode requires one word of extension. The address of the operand is the sum of the address in the address register, the sing-extended displacement integer in the low order eight bits of the extension word, and the contents of the index register. The reference is classified as a data reference with the exception of the jump and jumpto-subroutine instructions.

## 2.8.3 Special Address Modes

The special address modes use the effective address register field to specify the special addressing mode instead of a register number.

### 2.8.3.1 Absolute Short Address

This addressing mode requires one word of extension. The address of the operand is the extension word. The 16-bit address is sign extended before it is used. The reference is classified as a data reference with the exception of the jump and jump-to-subroutine instructions.

### 2.8.3.2 Absolute Long Address

This addressing mode requires two words of extension. The address of the operand is developed by the concatenation of the extension words. The high order part of the address is the first extension word; the low order part of the address is the second extension word. The reference is classified as a data reference with the exception of the jump and jump-to-subroutine instruction.

## 2.8.3.3 Program Counter with Displacement

This addressing mode requires one word of extension. The address of the operand is the sum of the address in the program counter and the sign-extended 16-bit displacement integer in the extension word. The value in the program counter is the address of the extension word. The reference is classified as a program reference.

#### 2.8.3.4 Program Counter with Index

This addressing mode requires one word of extension. The address is the sum of the address in the program counter, the sign-extended displacement integer in the lower eight bits of the extension word, and the contents of the index register. The value in the program counter is the address of the extension word. This reference is classified as a program reference.

#### 2.8.3.5 Immediate Data

This addressing mode requires either one or two words of extension depending on the size of the operation.

| Byte Operation      | : | operand is low order byte of extension word                   |

|---------------------|---|---------------------------------------------------------------|

| Word Operation      | : | operand is extension word                                     |

| Long Word Operation | : | operand is in the two extension words, high order 16 bits     |

|                     |   | are in the first extension word, low order 16 bits are in the |

|                     |   | second extension word                                         |

#### 2.8.3.6 Implicit Reference

Some instructions make implicit reference to the program counter (PC), the system stack pointer (SP), the supervisor stack pointer (SSP), the user stack pointer (USP), or the status register (SR). A selected set of instructions may reference the status register by means of the effective address field. These are:

ANDI to CCR ANDI to SR EORI to CCR EORI to SR ORI to CCR ORI to SR MOVE to CCR MOVE to SR MOVE to SR

## TOSHIBA

## 2.9 EFFECTIVE ADDRESS ENCODING SUMMARY

Table 2.1 is a summary of the effective addressing modes discussed in the previous paragraphs.

| Addressing Mode                                 | Mode | Register        |

|-------------------------------------------------|------|-----------------|

| Data Register Direct                            | 000  | Register Number |

| Address Register Direct                         | 001  | Register Number |

| Address Register Indirect                       | 010  | Register Number |

| Address Register Indirect with<br>Postincrement | 011  | Register Number |

| Address Register Indirect with<br>Predecrement  | 100  | Register Number |

| Address Register Indirect with Displacement     | 101  | Register Number |

| Address Register Indirect with Index            | 110  | Register Number |

| Absolute Short                                  | 111  | 000             |

| Absolute Long                                   | 111  | 001             |

| Program Counter with Displacement               | 111  | 010             |

| Program Counter with Index                      | 111  | 011             |

| Immediate                                       | 111  | 100             |

## 2.10 SYSTEM STACK

The system stack is used implicitly by many instructions; user stacks and queues may be created and maintained through the addressing modes. Address register seven (A7) is the system stack pointer (SP). The system stack pointer is either the supervisor stack pointer (SSP) or the user stack pointer (USP), depending on the state of the S bit in the status register. If the S bit indicates supervisor state, SSP is the active system stack pointer and the USP cannot be referenced as an address register. If the S bit indicates user state, the USP is the active system stack pointer, and the SSP cannot be referenced. Each system stack fills from high memory to low memory.

## TOSHIBA

## 3. INSTRUCTION SET SUMMARY

This section contains an overview of the form and structure of the TMP68303 instruction set. The instructions form a set of tools that include all the machine functions to perform the following operations:

Data Movement Integer Arithmetic Logical Shift and Rotate Bit Manipulation Binary Coded Decimal Program Control System Control

The complete range of instruction capabilities combined with the flexible addressing modes described previously provide a very flexible base for program development.

#### 3.1 DATA MOVEMENT OPERATIONS

The basic method of data acquisition (transfer and storage) is provided by the move (MOVE) instruction. The move instruction and the effective addressing modes allow both address and data manipulation. Data move instructions allow byte, word, and long word operands to be transferred from memory to memory, memory to register, register to memory, and register to register. Address move instructions allow word and long word operand transfers and ensure that only legal address manipulations are executed. In addition to the general move instruction there are several special data movement instructions: move multiple registers (MOVEM), move peripheral data (MOVEP), exchange registers (EXG), load effective address (LEA), push effective address (PEA), link stack (LINK), unlink stack (UNLK), and move quick (MOVEQ). Table 3.1 is a summary of the data movement operations.

| Instruction | Operand Size          | Operation                                                                            |  |

|-------------|-----------------------|--------------------------------------------------------------------------------------|--|

| EXG         | 32                    | Xx⇔Xy                                                                                |  |

| LEA         | 32                    | EA→An                                                                                |  |

| LINK        | -                     | $An \rightarrow - (SP)$<br>$SP \rightarrow An$<br>$SP + displacement \rightarrow SP$ |  |

| MOVE        | 8, 16, 32             | s →d                                                                                 |  |

| MOVEM       | 16, 32                | (EA)→An,Dn<br>An,Dn →(EA)                                                            |  |

| MOVEP       | 16, 32                | (EA)→Dn<br>Dn→(EA)                                                                   |  |

| MOVEQ       | 8                     | #xxx→Dn                                                                              |  |

| PEA         | 32 EA→ – (SP)         |                                                                                      |  |

| SWAP        | 32 Dn[31:16]↔Dn[15:0] |                                                                                      |  |

| UNLK        | -                     | $An \rightarrow SP$<br>(SP) + $\rightarrow An$                                       |  |

Table 3.1 Data Movement Operations

```

Notes: s = source

```

-() = indirect with predecrement

d = destination

() + = indirect with postincrement

[] = bit number

()+ = indirect with postincrem #xxx = immediate data

-----

## 3.2 INTEGER ARITHMETIC OPERATIONS

The arithmetic operations include the four basic operations of add (ADD), subtract (SUB), multiply (MUL), and divide (DIV) as well as arithmetic compare (CMP), clear (CLR), and negate (NEG). The add and subtract instructions are available for both address and data operations, with data operations accepting all operand sizes. Address operations are limited to legal address size operands (16 or 32 bits). Data, address, and memory compare operations are also available. The clear and negate instructions may be used on all sizes of data operands.

The multiply and divide operations are available for signed and unsigned operands using word multiply to produce a long word product, and a long word dividend with word divisor to produce a word quotient with a word remainder.

Multiprecision and mixed size arithmetic can be accomplished using a set of extended instructions. These instructions are: add extended (ADDX), subtract extended (SUBX), sign extend (EXT), and negate binary with extend (NEGX).

A test operand (TST) instruction that will set the condition codes as a result of a compare of the operand with zero is also available. Test and set (TAS) is a synchronization instruction useful in multiprocessor systems. Table 3.2 is a summary of the integer arithmetic operations.

| Instruction             | <b>Operand Size</b> | Operation                                                                            |  |

|-------------------------|---------------------|--------------------------------------------------------------------------------------|--|

| 8,16,32<br>ADD<br>16,32 |                     | Dn + (EA) →Dn<br>(EA) + Dn →(EA)<br>(EA) + $\#xxx \rightarrow$ (EA)<br>An + (EA) →An |  |

| ADDX                    | 8,16,32<br>16,32    | $Dx + Dy + X \rightarrow Dx$<br>- (Ax) + - (Ay) + X $\rightarrow$ (Ax)               |  |

| CLR                     | 8,16,32             | 0 →(EA)                                                                              |  |

| СМР                     | 8,16,32             | Dn – (EA)<br>(EA) – #xxx<br>(Ax) + – (Ay) +<br>An – (EA)                             |  |

| DIVS                    | 32 ÷ 16             | Dn ÷ (EA)→Dn                                                                         |  |

| DIVU                    | 32 ÷ 16             | Dn ÷ (EA)→Dn                                                                         |  |

| EXT                     | 8→16<br>16→32       | (Dn) <sub>8</sub> →Dn <sub>16</sub><br>(Dn) <sub>16</sub> →Dn <sub>32</sub>          |  |

| MULS                    | 16 × 16→32          | Dn × (EA) →Dn                                                                        |  |

| MULU                    | 16 × 16→32          | Dn x (EA) →Dn                                                                        |  |

| NEG                     | 8,16,32             | 0 – (EA)→(EA)                                                                        |  |

| NEGX                    | 8,16,32             | 0 – (EA) – X→(EA)                                                                    |  |

| 8,16,32<br>SUB<br>16,32 |                     | Dn – (EA) →Dn<br>(EA) – Dn →(EA)<br>(EA) – $\#xxx \rightarrow$ (EA)<br>An – (EA) →An |  |

| SUBX                    | 8,16,32             | $Dx - Dy - X \rightarrow Dx$<br>- (Ax) (Ay) - X $\rightarrow$ (Ax)                   |  |

| TAS                     | 8                   | (EA) - 0,1→EA[7]                                                                     |  |

| TST                     | 8,16,32             | 8,16,32 (EA) – 0                                                                     |  |

Table 3.2 Integer Arithmetic Operations

Notes: [] = bit number -() = indirect with predecrement

()+ = indirect with postincrement #xxx = immediate data

#### TOSHIBA

#### 3.3 LOGICAL OPERATIONS

Logical operation instructions AND, OR, EOR, and NOT are available for all sizes of integer data operands. A similar set of immediate instructions (ANDI, ORI, and EORI) provide these logical operations with all sizes of immediate data. Table 3.3 is a summary of the logical operations.

| Instruction | Operand Size | Operation                                    |  |

|-------------|--------------|----------------------------------------------|--|

| AND         | 8, 16, 32    | Dn^(EA)→Dn<br>(EA)^Dn→(EA)<br>(EA)^#xxx→{EA} |  |

| OR          | 8, 16, 32    | Dn∨(EA)→Dn<br>(EA)∨Dn→(EA)<br>(EA)∨#xxx→(EA) |  |

| EOR         | 8, 16, 32    | (EA)⊕Dy→(EA)<br>(EA)⊕#xxx→(EA)               |  |

| NOT         | 8, 16, 32    | ~(EA)→(EA)                                   |  |

Table 3.3 Logical Operations

Notes: ~

✓ = logical OR

⊕ = logical exclusive OR

#### 3.4 SHIFT AND ROTATE OPERATIONS

= invert

Shift operations in both directions are provided by the arithmetic instructions ASR and ASL and logical shift instructions LSR and LSL. The rotate instructions (with and without extend) available are ROXR, ROXL, ROR, and ROL. All shift and rotate operations can be performed in either registers or memory. Register shifts and rotates support all operand sizes and allow a shift count specified in a data register.

Memory shifts and rotates are for word operands only and allow only single-bit shifts or rotates.

MPU-20

#### 🛚 9004697 0953005 922 🎟

| Instruction Operand Size |           | Operation |

|--------------------------|-----------|-----------|

| ASL                      | 8, 16, 32 | X/C 0     |

| ASR                      | 8, 16, 32 | → → X/C   |

| LSL                      | 8, 16, 32 | X/C 0     |

| LSR                      | 8, 16, 32 | 0 →→ X/C  |

| ROL                      | 8, 16, 32 |           |

| ROR                      | 8, 16, 32 |           |

| ROXL                     | 8, 16, 32 | C + X +   |

| ROXR                     | 8, 16, 32 |           |

#### Table3.4 Shift and Rotate Operations

## 3.5 BIT MANIPULATION OPERATIONS

Bit manipulation operations are accomplished using the following instruction: bit test (BTST), bit test and set (BSET), bit test and clear (BCLR), and bit test and change (BCHG). Table 3.5 is a summary of the bit manipulation operations. (Z is bit 2 of the status register.)

| Instruction | Operand Size | Operation                                  |  |

|-------------|--------------|--------------------------------------------|--|

| BTST        | 8, 32        | ~bit of (EA) →Z                            |  |

| BSET 8, 32  |              | ~bit of (EA) →Z<br>1 →bit of EA            |  |

| BCLR        | 8, 32        | ~bit of (EA) →Z<br>0 →bit of EA            |  |

| вснд        | 8, 32        | ~bit of (EA) →Z<br>~bit of (EA) →bit of EA |  |

Table 3.5 Bit Manipulation Operations

Note:  $\sim = invert$

## 3.6 BINARY CODED DECIMAL OPERATIONS

Multiprecision arithmetic operations on binary coded decimal numbers are accomplished using the following instructions: add decimal with extend (ABCD), subtract decimal with extend (SBCD), and negate decimal with extend (NBCD). Table 3.6 is a summary of the binary coded decimal operations.

| Instruction | Operand Size | Operation                                                                                |  |

|-------------|--------------|------------------------------------------------------------------------------------------|--|

| ABCD        | 8            | $Dx_{10} + Dy_{10} + X \rightarrow Dx$<br>- (Ax)_{10} + - (Ay)_{10} + X \rightarrow (Ax) |  |

| SBCD        | 8            | $Dx_{10} - Dy_{10} - X \rightarrow Dx$<br>- $(Ax)_{10} (Ay)_{10} - X \rightarrow (Ax)$   |  |

| NBCD        | 8            | 0 - (EA) <sub>10</sub> - X→(EA)                                                          |  |

| Table 3.6 Binary Coded Decimal Op | perations |

|-----------------------------------|-----------|

|-----------------------------------|-----------|

Note: -( ) = indirect with predecrement

#### 3.7 PROGRAM CONTROL OPERATIONS

Program control operations are accomplished using a series of conditional and unconditional branch instructions and return instructions. These instructions are summarized in Table 3.7.

The conditional instructions provide setting and branching for the following conditions:

| CC            | carry clear      | LS | low or same |

|---------------|------------------|----|-------------|

| CS            | carry set        | LT | less than   |

| EQ            | equal            | MI | minus       |

| F             | never true       | NE | not equal   |

| GE            | greater or equal | PL | plus        |

| $\mathbf{GT}$ | greater than     | Т  | always true |

| HI            | high             | VC | no overflow |

| LE            | less or equal    | VS | overflow    |

|               |                  |    |             |

| Instruction          | Operation                                                         |  |

|----------------------|-------------------------------------------------------------------|--|

| Conditional<br>Bcc   | Branch Conditionally (14 Conditions)<br>8-and 16-Bit Displacement |  |

| DBcc                 | Test Condition, Decrement, and Branch<br>16-Bit Displacement      |  |

| Scc                  | Set Byte Conditionally (16 Conditions)                            |  |

| Unconditional<br>BRA | Branch Always<br>8-and 16-Bit Displacement                        |  |

| BSR                  | Branch to Subroutine<br>8-and 16-Bit Displacement                 |  |

| JMP                  | Jump                                                              |  |

| JSR                  | Jump to Subroutine                                                |  |

| Reterns<br>RTR       | Return and Restore Condition Codes                                |  |

| RTS                  | Return from Subroutine                                            |  |

Table 3.7 Program Control Operations

## 3.8 SYSTEM CONTROL OPERATIONS

System control operations are accomplished by using privileged instructions, trap generating instructions, and instructions that use or modify the status register. These instructions are summarized in Table 3.8.

| Table 3.8 System | em Control | l Operations |

|------------------|------------|--------------|

|------------------|------------|--------------|

| Instruction                                                                                              | Operation                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Privileged<br>ANDI to SR<br>EORI to SR<br>MOVE EA to SR<br>MOVE USP<br>ORI to SR<br>RESET<br>RTE<br>STOP | Logical AND to Status Register<br>Logical EOR to Status Register<br>Load New Status Register<br>Move User Stack Pointer<br>Logical OR to Status Register<br>Reset External Devices<br>Return from Exception<br>Stop Program Execution |

| Trap Generating<br>CHK<br>TRAP<br>TRAPV                                                                  | Check Data Register Against Upper Bounds<br>Trap<br>Trap on Overflow                                                                                                                                                                  |

| Status Register<br>ANDI to CCR<br>EORI to CCR<br>MOVE EA to CCR<br>MOVE SR to EA<br>ORI to CCR           | Logical AND to Condition Codes<br>Logical EOR to Condition Codes<br>Load New Condition Codes<br>Store Status Register<br>Logical OR to Condition Codes                                                                                |

# 4. SIGNAL AND BUS OPERATION DESCRIPTION

This section contains a brief description of the input and output signals. A discussion of bus operation during the various machine cycles and operations is also given.

Note: The terms "assertion" and "negation" will be used extensively. This is done to avoid confusion when dealing with a mixture of "active-low" and "active-high" signals. The term assert or assertion is used to indicate that a signal is active or true, independent of whether that level is represented by a high or low voltage. The term negate or negation is used to indicate that a signal is inactive or false.

## 4.1 SIGNAL DESCRIPTION

The input and output signals can be functionally organized into the groups and the pin assignments is shown in Figure 4.1. The following paragraphs provide a brief description of the signals and a reference (if applicable) to other paragraphs that contain more detail about the function being performed.

Figure 4.1 Input and Output Signals Pin Assignments

Figure 4.2 Normal Mode Signals Input/Output as Bus Master

Figure 4.3 Normal Mode Signals Input/Output as not Bus Master

171189

Figure 4.4 Emulation Mode Signals Input/Output

The following are brief explanations of the signals.

4.1.1 A1~A23: [Address Bus] (Output / [Input], Tristate)

This 23-bit bus can address up to 8M-words of data. Addresses are output for bus operation in all cycles except the interrupt acknowledge cycle. In the interrupt acknowledge cycle, A1~A3 indicate the interrupt service level and A4~A23 are all at high level. The signal changes to input when the bus is released and in the emulation mode.

4.1.2 D0~D15: [Data Bus] (Input / Output, Tristate)

This is a 16-bit general-purpose data bus that can transfer data in byte or word units. In an interrupt acknowledge cycle, the external device sends vector numbers to  $D0\sim D7$ . The data transfer direction is reversed in the emulation mode.

4.1.3 Asynchronous Bus Control Signals

4.1.3.1 AS: [Address Strobe] (Output / [Input], Low Active, Tristate)

This signal indicates that there is a valid address on the address bus. The signal changes to input in the emulation mode.

4.1.3.2 R/W: [Read/Write] (Output / [Input], Tristate)

This signal indicates whether the data bus transfer is a read (High) or written (Low). As shown in Table 4.1, this signal is used in combination with UDS and LDS. The signal changes to input in the emulation mode.

4.1.3.3 UDS, LDS: [Upper and Lower Data Strobes] (Output / [Input], Low Active, Tristate)

These signals control the flow of data on the data bus. The processor reads from the data bus when R/W is High and the core processor writes to the data bus when R/W is Low. The signal changes to input in the emulation mode.

4.1.3.4 DTACK: [Data Transfer Acknowledge] (Input / [Output], Low Active)

This signal indicates the end of a data transfer. When the assertion of DTACK during the core processor read cycle is acknowledged, data is latched and the bus cycle ends. When DTACK is recognized during the write cycle, the bus cycle ends. (See 4.4 Asynchronous and synchronous operation.)

4.1.4 Bus Arbitration Control (Interrupt Request Output)

These three signals are used by the bus arbitration circuit to determine which device will be a bus master. In the emulation mode, interrupt requests are output by the interrupt controller.

4.1.4.1 BR : [Bus Request] (Input / [Output], Low Active)

This signal is wire ORed connected with all other devices which could become the bus masters. This input signal indicates another device desire to become the bus master.

| UDS  | LDS  | R∕₩  | D8~D15                  | D0~D7                    |

|------|------|------|-------------------------|--------------------------|

| High | High | -    | No Valid Data           | No Valid Data            |

| Low  | Low  | High | Valid Data Bits<br>8~15 | Valid Data Bits<br>0~7   |

| High | Low  | High | No Valid Data           | Valid Data Bits<br>0~7   |

| Low  | High | High | Valid Data Bits<br>8~15 | No Valid Data            |

| Low  | Low  | Low  | Valid Data Bits<br>8~15 | Valid Data Bits<br>0~7   |

| High | Low  | Low  | Valid Data Bits<br>0~7* | Valid Data Bits<br>0~7   |

| Low  | High | Low  | Valid Data Bits<br>8~15 | Valid Data Bits<br>8~15* |

Table 4.1 Data Strobe Control of Data Bus

\* : These conditions are result of current implementation and may not appear on future devices.

### 4.1.4.2 BG : [Bus Grant] (Output, Low Active)

This signal indicates to all other devices which could become the bus master that the core processor will release the bus control at the end of the current bus cycle.

4.1.4.3 BGACK : [Bus Grant Acknowledge] (Input / [Output], Low Active)

This signal indicates that another device has become the bus master. The signal should not asserted unless the following four conditions are satisfied.

- (1)  $\overline{BG}$  is asserted.

- (2)  $\overline{AS}$  is not asserted (that is, the core processor is not using the bus).

- (3) DTACK is not asserted (that is, the memory and peripheral devices are not using the bus).

- (4) BGACK is not asserted (no other device is requesting the bus).

- 4.1.5 System Control

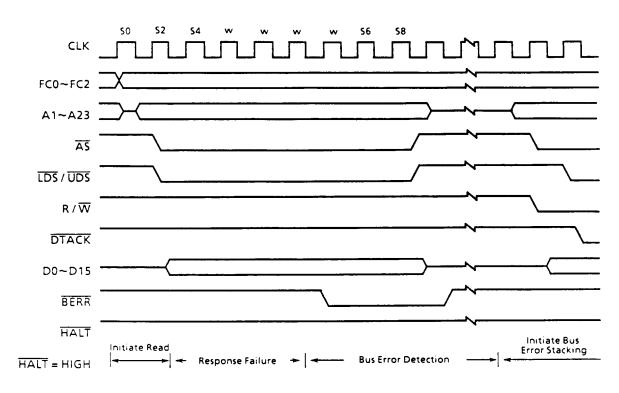

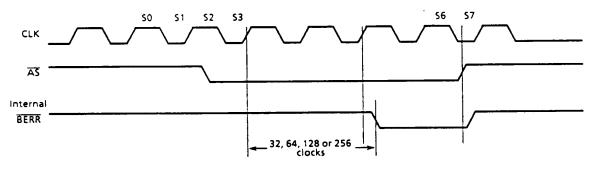

4.1.5.1 BERR: [Bus Error] (Input/[Output], Low Active)

This signal reports to the core processor that there is a problem in the current cycle in the following cases.

- (1) There is no response from a device.

- (2) Interrupt vector number acquisition failure.

- (3) An invalid access request determined by a memory management unit is made.

(4) Other errors (differs according to the application).

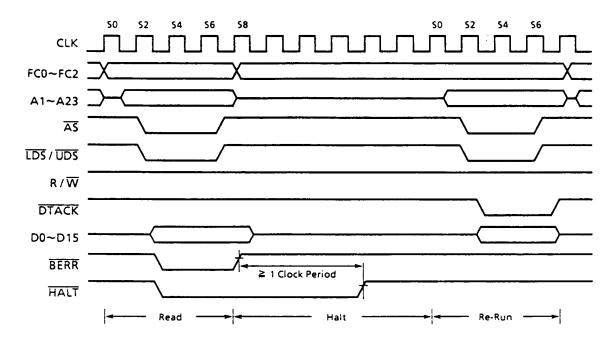

BERR, together with HALT, determines whether exception processing should be performed or the current bus cycle is re-executed. (See item 4.2.4 Bus error and halt operation.)

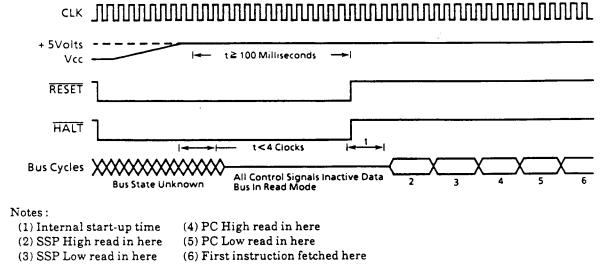

4.1.5.2 **RESET**: [Reset] (Input/Output, Low Active, Open Drain)

This signal resets the core processor (starts the system initialization sequence) in response to an external reset signal. In response to an internally generated reset (result of a RESET instruction), this signal also operates as an external device reset signal but does not change the internal status of the core processor. A total system resets (core processor and external devices) is applied by asserting both HALT and RESET at the same time from the outside. (See item 4.2.5 Reset operation.)

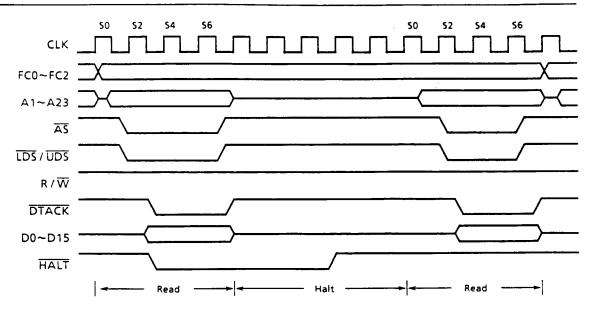

4.1.5.3 HALT: [Halt] (Input/Output, Low Active, Open Drain)

When asserted from an external device, this signal halts the core processor when the current bus cycle ends. Using this input signal to halt the core processor negates all control signals from the core processor and sets all tristate signals to high impedance. (See item 4.2.4 Bus errors and halt operation concerning the relationship to <u>BERR</u>.)

When the core processor halts the execution of an instruction such as in a double bus fault condition (see item 4.2.4.4 Double bus faults), HALT is driven to Low level by the core processor and the fact that the core processor has halted is reported to the external device.

4.1.6 FC0, FC1, FC2: [Function Code] (Output/[Input], High Active, Tristate)

These three signals indicate the core processor state (user or supervisor) and the current cycle type as shown in Table 4.2. The data indicated by these signals are valid when  $\overline{AS}$  is asserted.

| FC2  | FC1  | FC0  | Cycle Type            |  |  |

|------|------|------|-----------------------|--|--|

| Low  | Low  | Low  | (Undefined, Reserved) |  |  |

| Low  | Low  | High | User Data             |  |  |

| Low  | High | Low  | User Program          |  |  |

| Low  | High | High | (Undefined, Reserved) |  |  |

| High | Low  | Low  | (Undefined, Reserved) |  |  |

| High | Low  | High | Supervisor Data       |  |  |

| High | High | Low  | Supervisor Program    |  |  |

| High | High | High | Interrupt Acknowledge |  |  |

Table 4.2 Function Code Outputs

The signals change to input in the emulation mode.

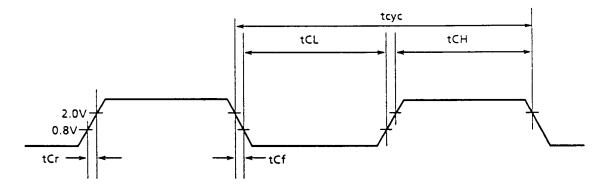

4.1.7 CLK: [Clock] (Input, High Active)

This signal is TTL compatible and is buffered internally for use in creating internal clocks. Clock input must not be gated off any time and the maximum and minimum pulse width conditions must be satisfied.

- 4.1.8 Peripheral Signals

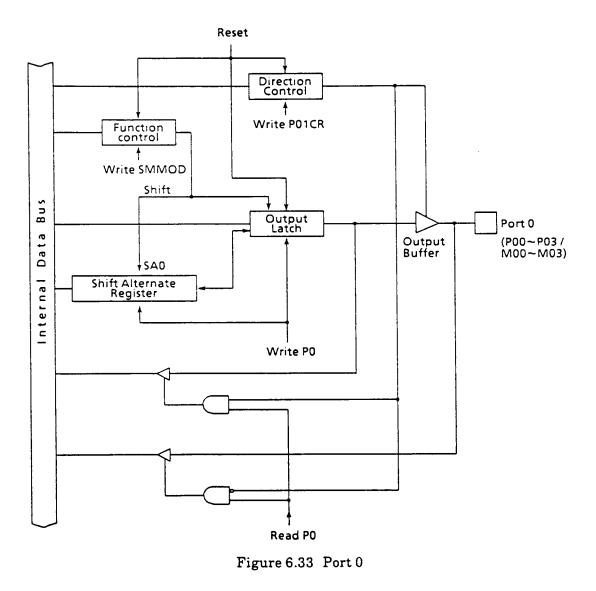

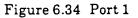

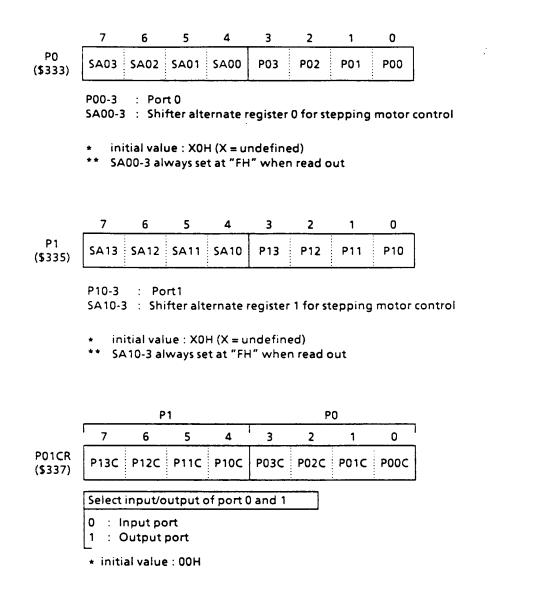

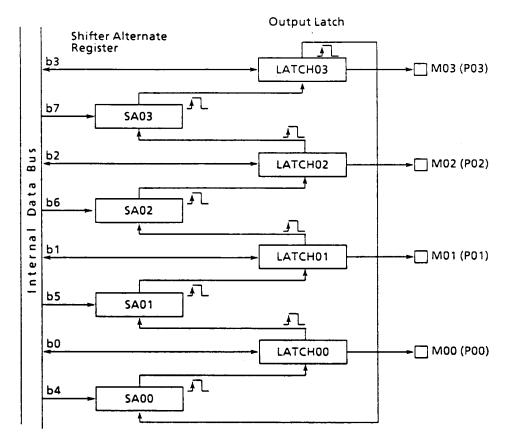

- 4.1.8.1 P00~P03/M00~M03/TOUT3 [I/O Port] (Input/Output)

These are output signals from the 4-bit general-purpose I/O port or stepping motor control port 0. POO is also used for the timer channel 3 output signal.

```

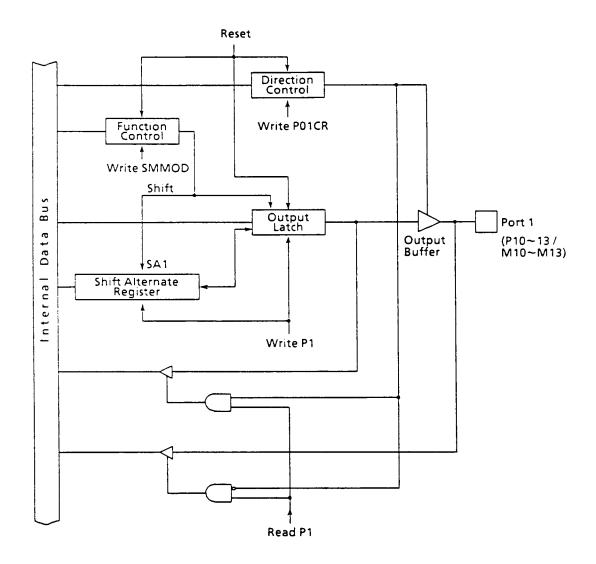

4.1.8.2 P10~P13/M10~M13/TOUT4 [I/O Port] (Input/Output)

```

These are output signals from the 4-bit general-purpose I/O port or stepping motor control port 1. P10 is also used for the timer channel 4 output signal.

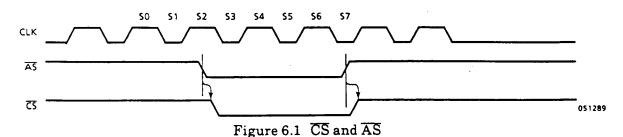

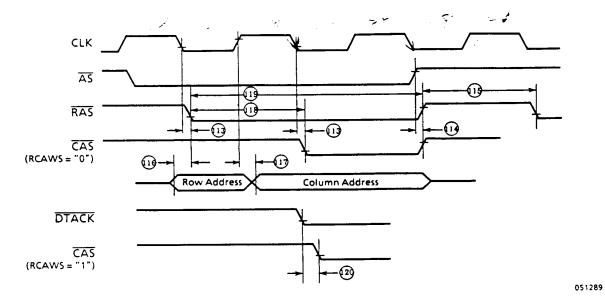

4.1.8.3 RAS / CSO [Row Address Strobe / chip select 0] (Output, Low Active)

This is the row address strobe to the DRAM or address decoder signal.

4.1.8.4 CAS / CSI [Column Address Strobe/ chip select 1] (Output, Low Active)

This is the column address strobe to the DRAM or address decoder signal.

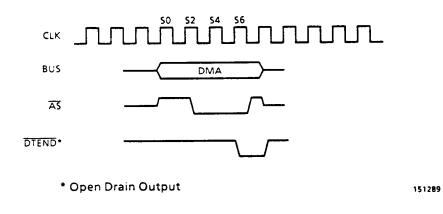

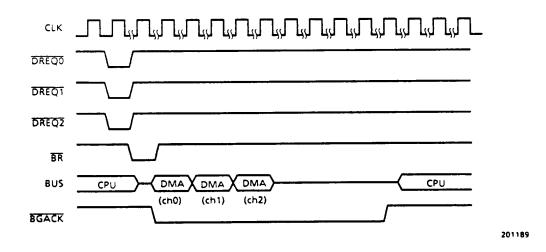

4.1.8.5 DREQ0~2 [DMA Request] (Low Active)

Request signals which are input to start DMAC.

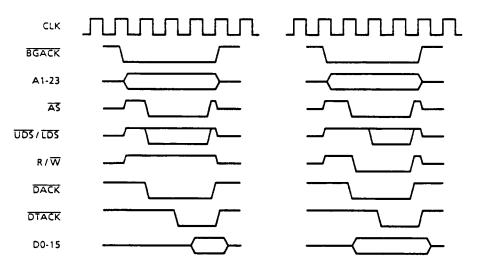

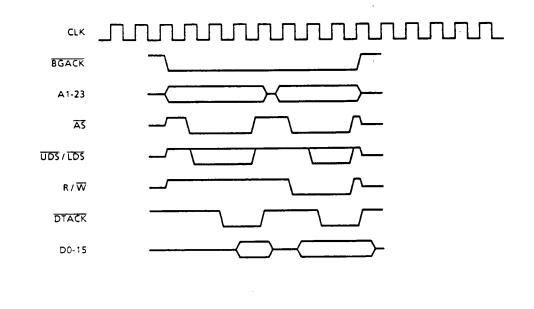

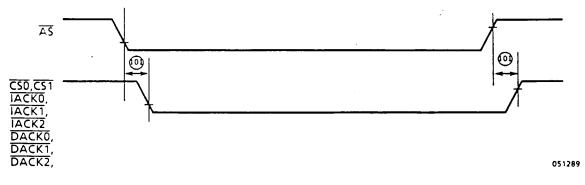

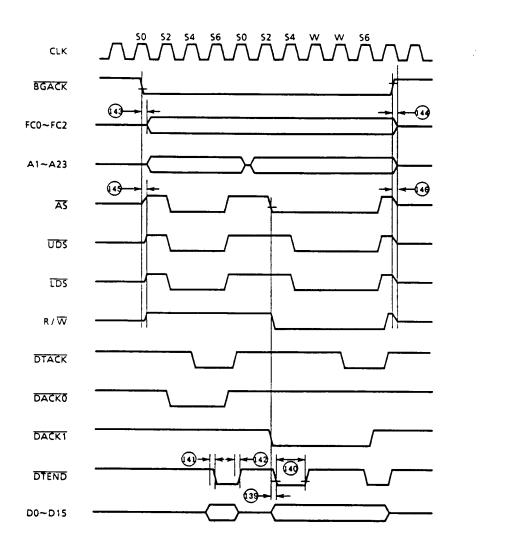

4.1.8.6 DACK0-2 [DMA Acknowledge] (Output, Low Active)

Acknowledge signals output by DMAC to specify I/O devices.

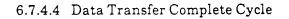

4.1.8.7 DTEND [DMA End] (Input / Output, Low Active, Open Drain)

The input signal of prohibition for channel request, the end signal input to compulsorily end DMA operation or the output signal that show transfer complete.

4.1.9.8 IPLO, IPLI, IPL2 [Interrupt Priority Level] (Input, Low Active)

These pins are not connected in the normal mode. In the emulation mode, however, these pins are used to output interrupt requests from the interrupt controller.

4.1.8.9 TOUT1, TOUT2 [Timer Output] (Output)

The timer channels 1 and 2 output signals.

4.1.8.10 TIN [Timer Input] (Input, Low Active)

Input signals to 0,1 and 2 timer channels.

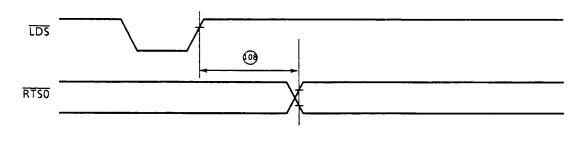

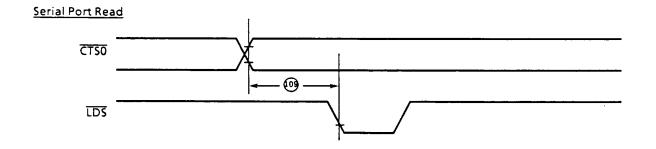

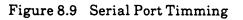

4.1.8.11 RTS0/P21 [I/O Port] (Input/Output)

Used as the serial interface channel 0 request-to-send output signal pins and generalpurpose I/O port pins.

## 4.1.8.12 CTS0/P20 [I/O Port] (Input/Output)

Used as the serial interface channel 0 clear-to-send input signal pins and generalpurpose I/O port pins.

4.1.8.13 RxD0, RxD1, [Receive Data] (Input)

The serial interface data inputs.

4.1.8.14 TxD0, TxD1, [Send Data] (Output)

The serial interface data outputs.

4.1.8.15 BCLK [Baud Rate, Clock] (Input)

The clock used to generate the serial interface baud rates.

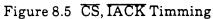

4.1.8.16 INT0, INT1, INT2 [Interrupt Request] (Input)

Interrupt requests.

4.1.8.17 IACK0, IACK1, IACK2 [Interrupt Acknowledge] (Output, Low Active)

Indicates IACK cycles.

4.1.9 NOR/EMU [Mode Switch] (Input)

The signal used to switch between the normal and emulation mode.

4.1.10 BGIN (Bus Grant In] (Input)

This signal is  $\overline{BG}$  of CPU output which built-in DMAC accept at emulation mode.

## 4.1.11 Signal Summary

Table 4.3 is a summary of all the signals discussed in the previous paragraphs.

|                                 |                        | Input/Output                      | Active<br>State        | 3 State | Hi-Z            |                 |

|---------------------------------|------------------------|-----------------------------------|------------------------|---------|-----------------|-----------------|

| Signal Name                     | Mnemonic               |                                   |                        |         | On HALT         | On BG           |

| Address Bus                     | A1~A23                 | Output (input)                    | High                   | Yes     | Yes             | Yes             |

| Data Bus                        | D0~D15                 | Input / Output<br>(Outpu / Input) | High                   | Yes     | Yes             | Yes             |

| Address Strobe                  | AS                     | Output (Input)                    | Low                    | Yes     | No              | Yes             |

| Read / Write                    | R/₩                    | Output (input)                    | Read-High<br>Write-Low | Yes     | No              | Yes             |

| Upper and Lower<br>Data strobes | UDS, LDS               | Output (input)                    | Low                    | Yes     | No              | Yes             |

| Data Transfer<br>Acknowledge    | DTACK                  | input (Output)                    | Low                    | No      | No <sup>1</sup> | No <sup>1</sup> |

| Bus Request                     | BR                     | input (Output)                    | Low                    | No      | No1             | No <sup>1</sup> |

| Bus Grant                       | BG                     | Output                            | Low                    | No      | No              | No              |

| Bus Grant<br>Acknowiedge        | BGACK                  | input (Output)                    | Low                    | No      | No۱             | No <sup>1</sup> |

| Interrupt Priority Level        | IPLO, IPL1, IPL2       | Input (Output)                    | Low                    | Yes     | No              | No              |

| Bus Error                       | BERR                   | Input (Output)                    | Low                    | No      | No <sup>1</sup> | No <sup>1</sup> |

| Reset                           | RESET                  | Input (Output)                    | . Low                  | Yes     | No1             | No <sup>1</sup> |

| Halt                            | HALT                   | Input (Output)                    | Low                    | Yes     | No1             | No1             |

| Function Code Output            | FCO, FC1, FC2          | Output (Input)                    | High                   | Yes     | No              | Yes             |

| Clock                           | CLK                    | Input                             | High                   | No      | No              | No              |

| Power Input                     | Vcc                    | Input                             | -                      | -       | —               | -               |

| Ground                          | GND                    | Input                             | -                      | - 1     | -               | -               |

| Row Address Strobe              | RAS                    | Output                            | Low                    | -       | -               | -               |

| Column Address Strobe           | CAS                    | Output                            | Low                    | -       | -               | -               |

| DMA Request                     | DREQ0~2                | Input                             | Low                    | -       | -               | -               |

| DMA Acknowledge                 | DACK0~2                | Output                            | Low                    | -       | -               | -               |

| DMA End                         | DTEND                  | Input/Output                      | Low                    | -       | No <sup>1</sup> | No1             |

| Clear to Send                   | CTSO                   | Input                             | Low                    | Yes     | -               | -               |

| Request to Send                 | RTSO                   | Output                            | Low                    | Yes     | -               | -               |

| Receive Data                    | RxD0-1                 | Input                             |                        | -       |                 | -               |

| Transfer Date                   | TxD0-1                 | Output                            | -                      | -       |                 |                 |

| Baudrate clock                  | BCLK                   | Input                             | -                      | -       |                 | -               |

| I/O Port                        | P00~03,10~13,20,<br>21 | Input / Output                    |                        | Yes     | -               | -               |

| Timer Output                    | Tout 1~4               | Output                            |                        | -       | -               | -               |

| Timer Input                     | TIN                    | Input                             | Low                    | -       | -               | -               |

| Mode change                     | NOR / EMU              | Input                             | -                      | -       |                 | -               |

| Interrupt Request               | INT0~2                 | Input                             | High                   | _       | -               |                 |

| Interrupt Acknowledge           | IACK0~2                | Output                            | Low                    |         | -               | -               |

| SMC Output                      | M00~03,10~13           | Output                            |                        | -       | -               | -               |

| Bus Grant In                    | BGIN                   | Input                             | Low                    | Yes     | No              | No              |

Table 4.3 Signal Summary

Note :1. Open drain ( ) Emulation Mode

## 4.2 BUS OPERATION

The following paragraphs explain control signal and bus operation during data transfer operations, bus arbitration, bus error and halt conditions, and reset operation.

## 4.2.1 Data Transfer Operations

Transfer of data between devices involves the following leads:

- 1. address bus A1~A23

- 2. data bus D0~D15

- 3. control signals

The address and data buses are separate parallel buses used to transfer data using an asynchronous bus structure. In all cycles, the bus master assumes responsibility for deskewing all signals it issues at both the start and end of a cycle. In addition, the bus master is responsible for deskewing the acknowledge and data signals from the slave device.

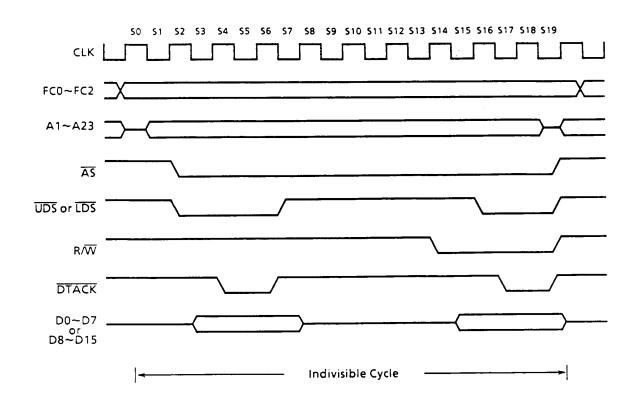

The following paragraphs explain the read, write, and read-modify-write cycles. The indivisible read-modify-write cycle is the method used by the TMP68303 for interlocked multiprocessor communications.

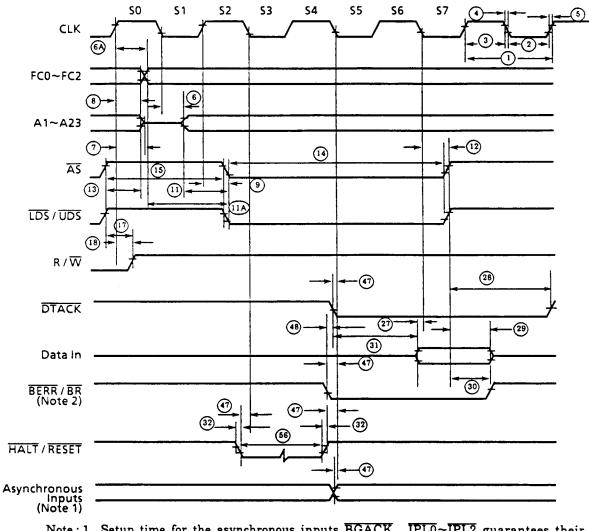

## 4.2.1.1 Read Cycle

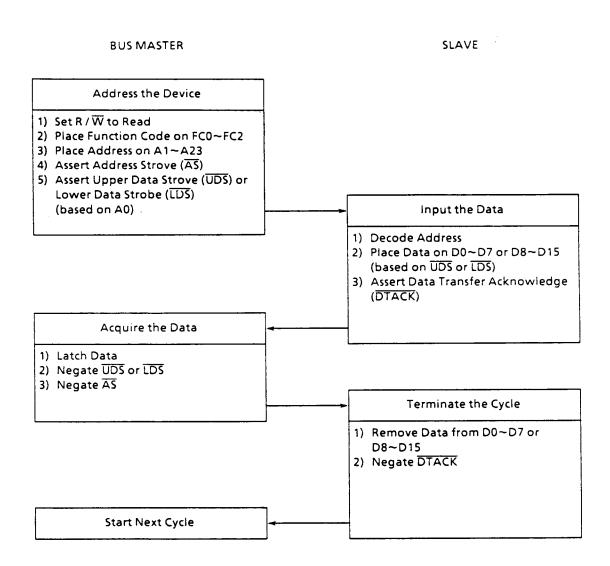

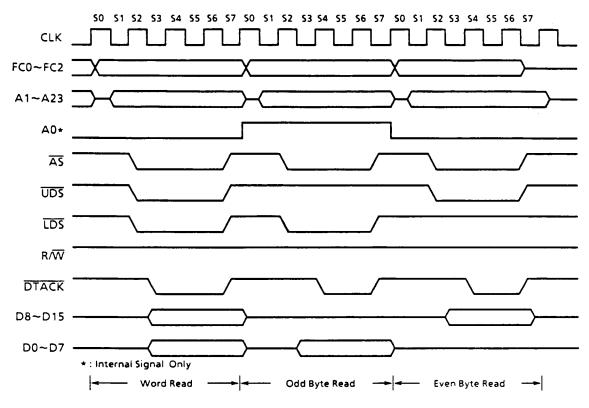

During a read cycle, the core processor receives data from the memory or a peripheral device. The core processor reads bytes of data in all cases. If the instruction specifies a word (or double word) operation, the core processor reads both upper and lower both simultaneously by asserting both upper and lower data strobes. When the instruction specifies byte operation, the core processor uses an internal A0 bit to determine which byte to read and then issues the data strobe required for that byte. For byte operations, when the A0 bit equals zero, the upper data strobe is issued. When the A0 bit equals one, the lower data strobe is issued. When the data is received, the core processor correctly positions it internally.

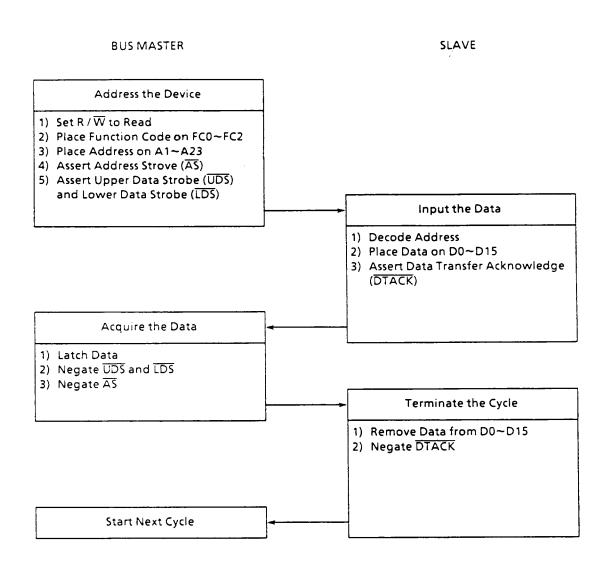

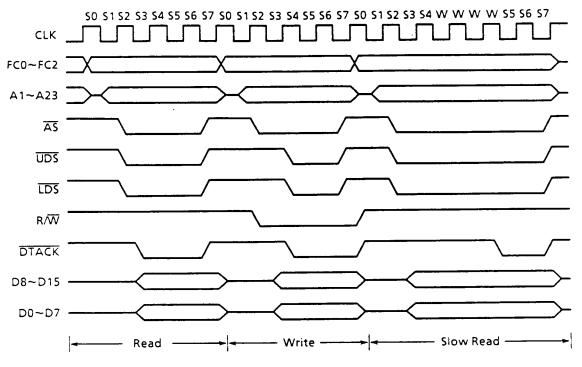

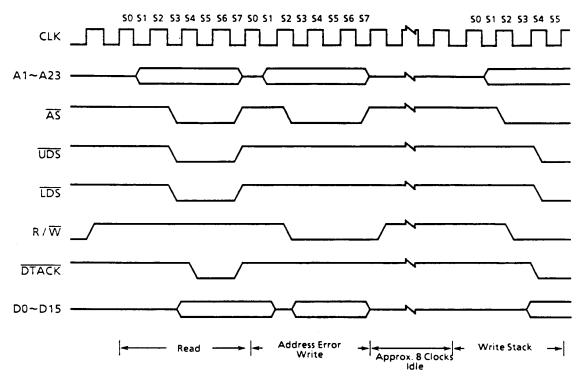

A word read cycle flowchart is given in Figure 4.2. A byte read cycle flowchart is given in Figure 4.3. Read cycle timing is given in Figure 4.4. Figure 4.5 details word and byte read cycle operations.

## Figure 4.2 Word Read Cycle Flowchart

### Figure 4.3 Byte Read Cycle Flowchart

#### MPU-36

Powered by ICminer.com Electronic-Library Service CopyRight 2003

Figure 4.4 Read and Write Cycle Timing Diagram

$Figure \ 4.5 \ \ Word \ and \ Byte \ Read \ Cycle \ Timing \ Diagram$

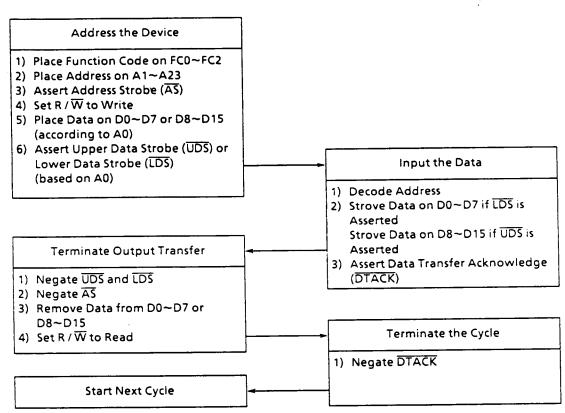

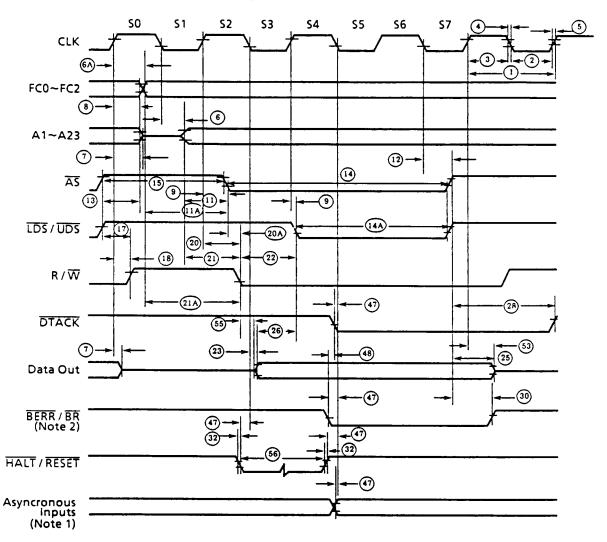

### 4.2.1.2 Write Cycle

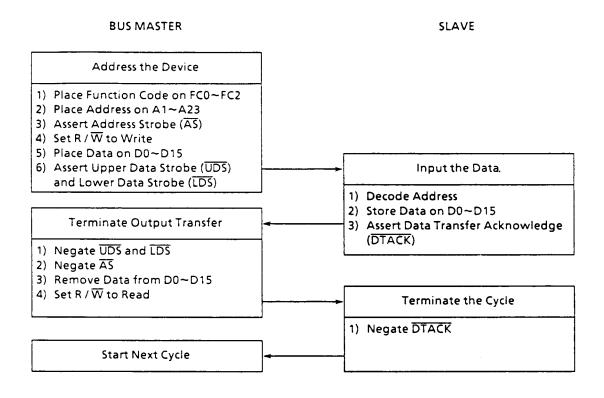

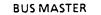

During a write cycle, the core processor sends data to either the memory or a peripheral device. The core processor writes bytes of data in all cases. If the instruction specifies a word operation, the core processor writes both bytes. When the instruction specifies a byte operation, the core processor uses an internal A0 bit to determine which byte to write and then issues the data strobe required for that byte. For byte operations, when the A0 bit equals zero, the upper data strobe is issued. When the A0 bit equals one, the lower data strobe is issued. A word write flowchart is given in Figure 4.6. A byte write cycle flowchart is given in Figure 4.7. Write cycle timing is given in Figure 4.4. Figure 4.8 details word and byte write cycle operation.

Figure 4.6 Word Write Cycle Flowchart

SLAVE

Figure 4.7 Byte Write Cycle Flowchart

Figure 4.8 Word and Byte Write Cycle Timing Diagram

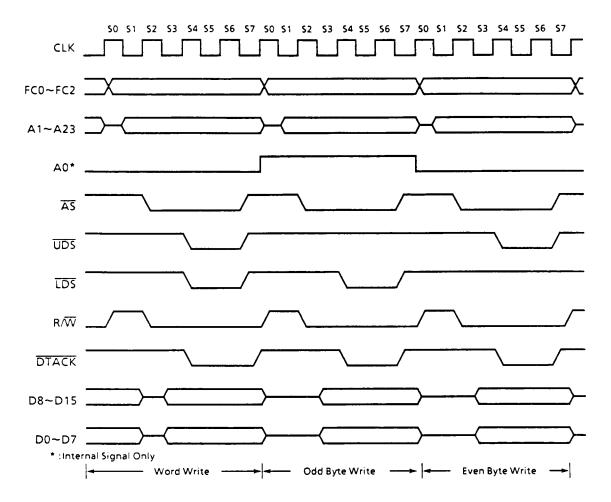

## 4.2.1.3 Read-Modify-Write Cycle

The read-modify-write cycle performs a read, modifies the data in the arithmetic-logic unit, and writes the data back to the same address. In the TMP68303, this cycle is indivisible in that the address strobe is asserted throughout the entire cycle. The test and set (TAS) instruction uses this cycle to provide meaningful communication between processors in a multiple processor environment. This instruction is the only instruction that uses the read-modify-write cycles and since the test and set instruction only operates on bytes, all read-modify-write cycles are byte operations. A read-modify-write flowchart is given in Figure 4.9 and a timing diagram is given in Figure 4.10.

-

| BUS MASTER                                                                                                                                                                                                                | SLAVE                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Address the Device                                                                                                                                                                                                        |                                                                                                         |

| <ol> <li>Set R / W to Read</li> <li>Place Function Code on FC0~FC2</li> <li>Place Address on A1~A23</li> <li>Assert Address Strobe (AS)</li> <li>Assert Upper Data Strobe (UDS) or<br/>Lower Data Strobe (LDS)</li> </ol> | Input the Data          1) Decode Address         2) Place Data on D0~D7 or D8~D15                      |

| Acquire the Data                                                                                                                                                                                                          | 3) Assert Data Transfer Acknowledge<br>(DTACK)                                                          |

| <ol> <li>Latch Data</li> <li>Negate UDS or LDS</li> <li>Start Data Modification</li> </ol>                                                                                                                                | Terminate the Cycle                                                                                     |

| Start Output Transfer                                                                                                                                                                                                     | 1) Remove Data from D0∼D7 or<br>D8∼D15<br>2) Negate DTACK                                               |

| <ol> <li>Set R / W to Write</li> <li>Place Data on D0~D7 or D8~D15</li> <li>Assert Upper Data Strobe (UDS) or<br/>Lower Data Strobe (LDS)</li> </ol>                                                                      | input the Data                                                                                          |

| Terminate Output Transfer                                                                                                                                                                                                 | <ol> <li>Store Data on D0~D7 or D8~D15</li> <li>Assert Data Transfer Acknowledge<br/>(DTACK)</li> </ol> |

| <ol> <li>Negate UDS or LDS</li> <li>Negate AS</li> <li>Remove Data from D0~D7 or<br/>D8~D15</li> </ol>                                                                                                                    |                                                                                                         |

| 4) Set $R / \overline{W}$ to Read                                                                                                                                                                                         | Terminate the Cycle                                                                                     |

| Start Next Cycle                                                                                                                                                                                                          | 1) Negate DTACK                                                                                         |

Figure 4.9 Read-Modify-Write Cycle Flowchart

Figure 4.10 Read-Modify-Write Cycle Timing Diagram

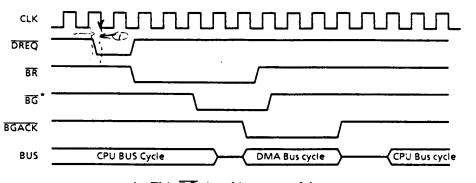

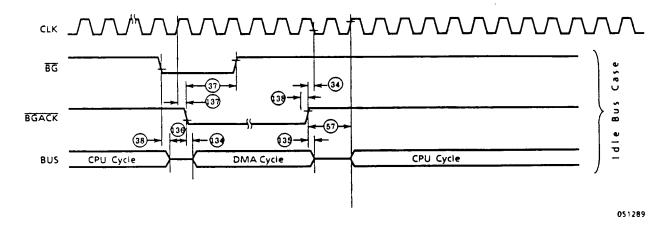

### 4.2.2 Bus Arbitration

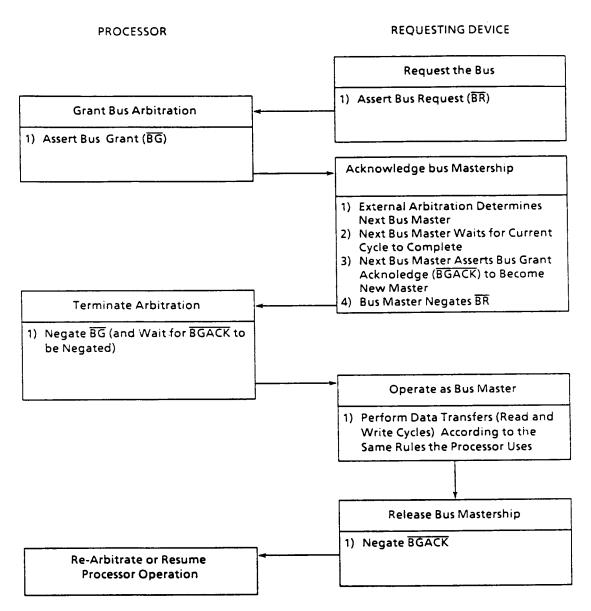

Bus arbitration is technique used by master-type devices to request, be granted, and acknowledge bus mastership. In its simplest form, it consists of the following:

- 1. asserting a bus mastership request

- 2. receiving a grant that the bus is available at the end of the current cycle

- 3. acknowledging that mastership has been assumed

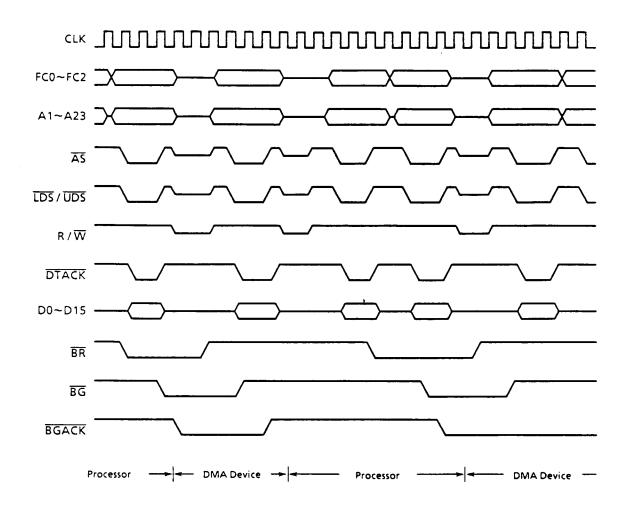

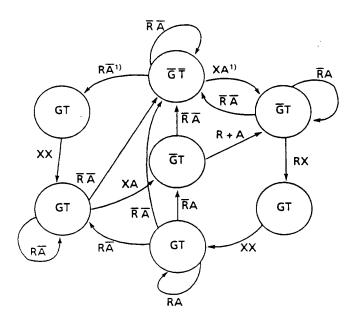

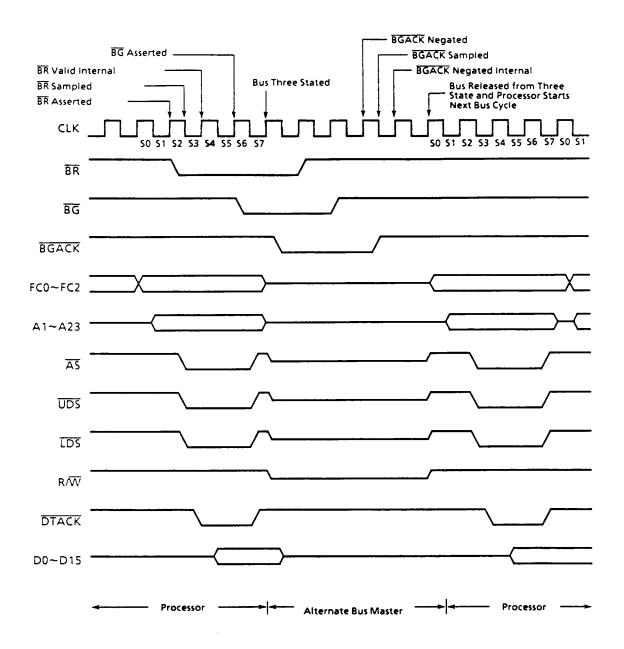

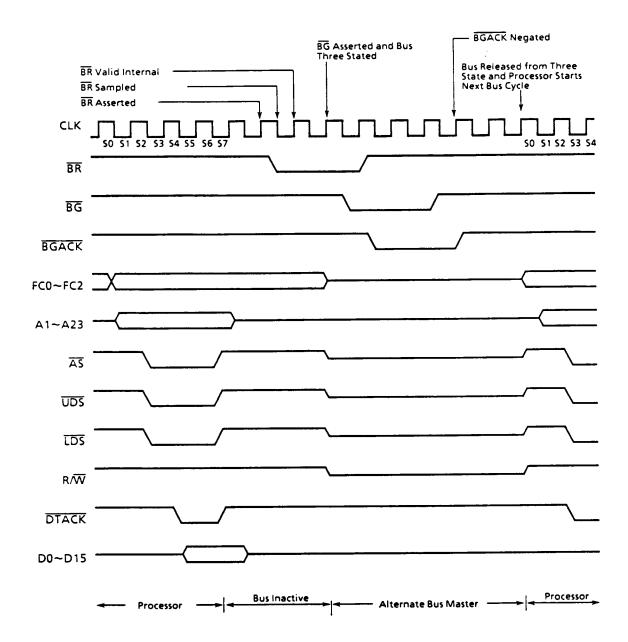

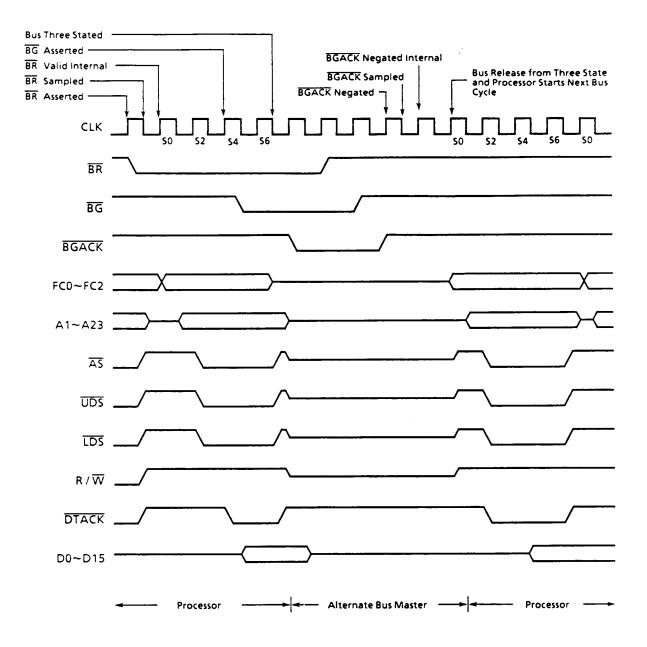

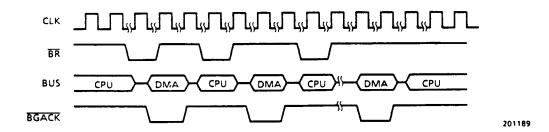

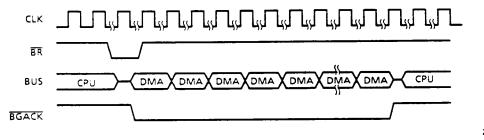

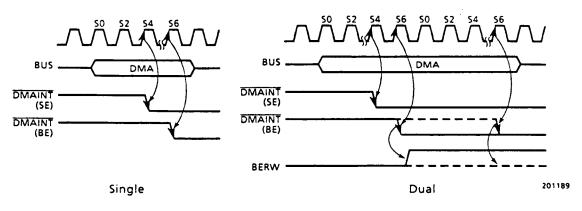

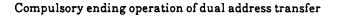

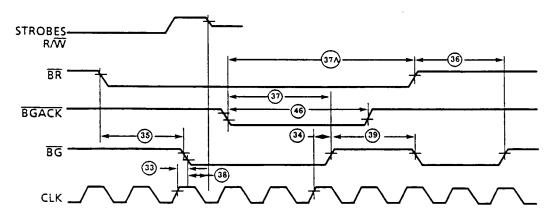

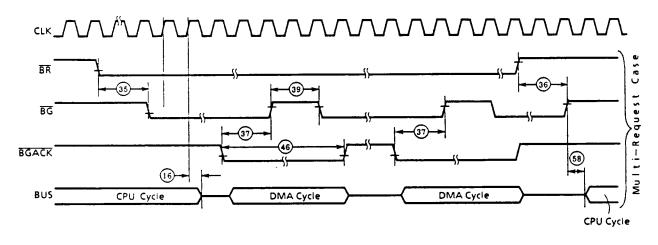

Figure 4.11 is a flowchart showing the detail involved in a request from a single device. Figure 4.12 is a timing diagram for the same operation. This technique allows processing of bus requests during data transfer cycles. The timing diagram shows that the bus request is negated at the time that an acknowledge is asserted. This type of operation would be true for a system consisting of the core processor and one device capable of bus mastership. In systems having a number of devices capable of the busmastership, the bus request line from each device is wire ORed to the processor. In this system, it is easy to see that there could be more than one bus request being made. The timing diagram shows that the bus grant signal is negated a few clock cycles after the transition of the acknowledge (BGACK) signal.

Figure 4.11 Bus Arbitration Cycle Flowchart

MPU-44

Figure 4.12 Bus Arbitration Cycle Timing Diagram

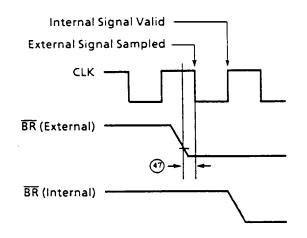

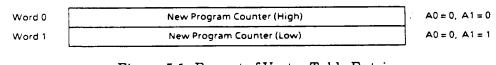

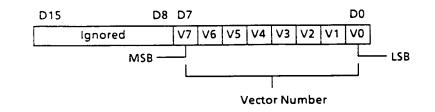

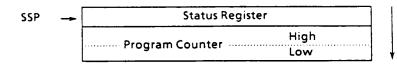

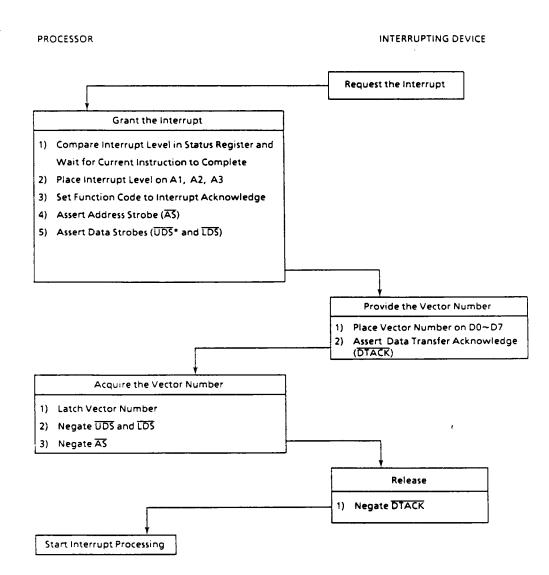

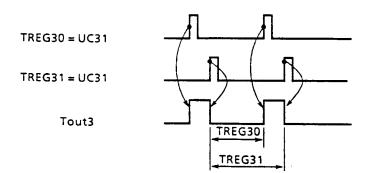

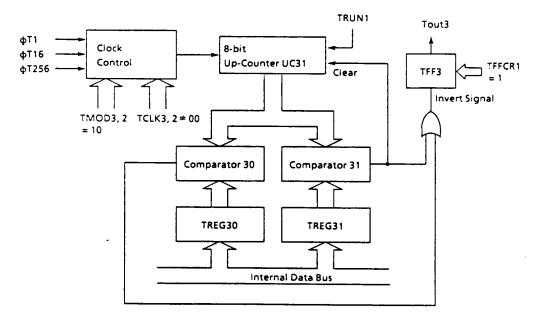

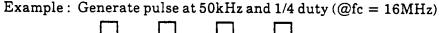

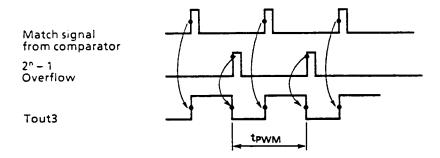

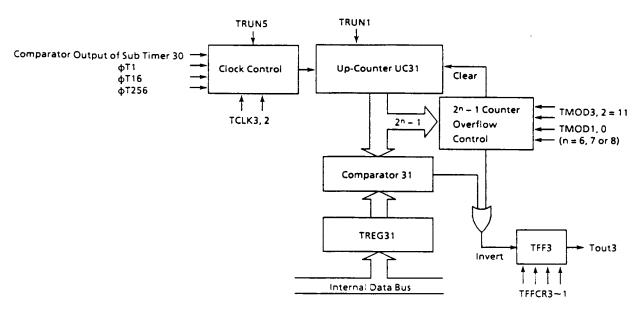

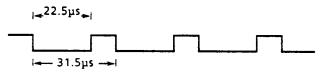

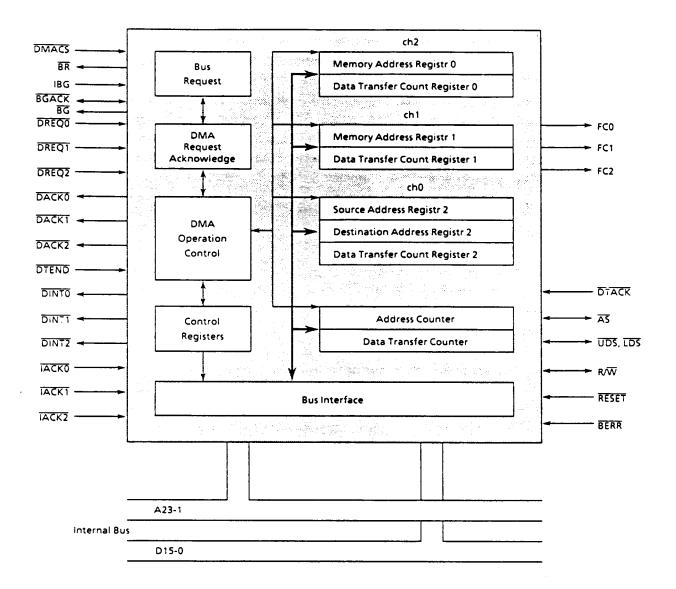

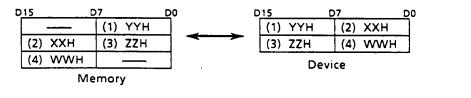

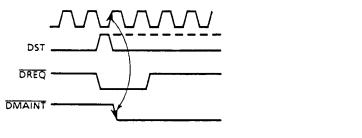

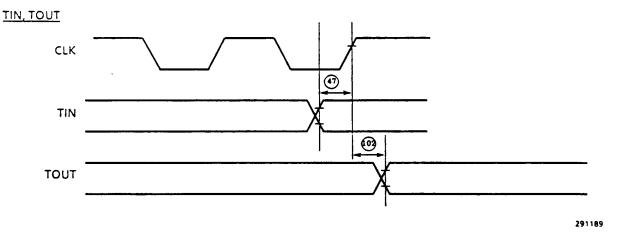

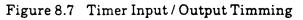

# 4.2.2.1 Requesting the Bus