|         |                                      |     |      | <u>-</u>   |    |     |                                                         |            |       |     | RE                        | VISK     | ONS                  | ;   |             | •••• |              |          |           |             |                             |      |          |          | ··········· |    |

|---------|--------------------------------------|-----|------|------------|----|-----|---------------------------------------------------------|------------|-------|-----|---------------------------|----------|----------------------|-----|-------------|------|--------------|----------|-----------|-------------|-----------------------------|------|----------|----------|-------------|----|

| LTR     |                                      |     |      |            |    |     | C                                                       | DESC       | RIPT  | 10N |                           |          |                      |     |             |      |              |          | DAT       | E (YR       | MO-D                        | M)   | Al       | PPRO     | WED         |    |

|         |                                      |     |      |            |    |     |                                                         |            | THE I |     |                           |          |                      |     |             |      |              |          |           | = (411-     |                             |      | Al       |          |             |    |

| REV     |                                      |     |      |            |    |     |                                                         |            |       |     |                           |          |                      |     |             |      |              |          |           |             |                             |      |          |          |             |    |

| SHEE    | T                                    |     |      |            |    |     |                                                         |            |       |     |                           |          |                      |     |             |      |              |          |           |             |                             |      |          |          |             |    |

| REV     |                                      |     |      |            |    |     |                                                         |            |       |     |                           |          |                      |     |             |      |              |          |           |             |                             |      |          |          |             |    |

| SHEET   |                                      | 22  |      |            | 25 | 26  | 27                                                      | 28         | 29    | 30  | 31                        | 32       | 33                   |     | 1           |      | <b> </b>     | <u> </u> |           | <u> </u>    | _                           | _    | <u> </u> | _        |             |    |

| REV S   |                                      | -   | RE   |            |    |     |                                                         |            |       | _   | <u> </u>                  | <u> </u> | $\vdash$             | _   |             | _    |              | _        | _         | <u> </u>    | <u> </u>                    | _    | -        | <u> </u> |             |    |

| PMIC    |                                      |     | SH   | EET        |    |     |                                                         | 3<br>ED BY |       | 5   | 6<br><b>&amp;</b>         | 7        | 8                    | 9   | 10          | DE   | 12<br>FENS   | E ELI    | ECTF      | PONK        | cs s                        | UPPI |          |          |             | 21 |

| P       | NDAI<br>MILIT<br>DRAW                | AR' | Y    | D          |    | CHE | CHECKED BY  Ray Monnin  APPROVED BY  Villian X. Zkalmon |            |       |     |                           | ı        | MICR<br>MICR<br>MEMO | 000 | <b>NTRO</b> | T, [ | DIGI<br>R WI | TAL,     | NM<br>K B | OS,<br>YTES | DS, 16-BIT<br>YTES OF EPROM |      |          |          |             |    |

| FOR USE | RAWING<br>BY ALL<br>DAGENO<br>RTMENT | DEF | ARTI | MENT<br>IE | rs | i.  | DRAWING APPROVAL DATE 1 AUGUST 1989                     |            |       |     | SIZE CAGE CODE 67268 5962 |          |                      |     | 62          | -86  | 80           | 9        |           |             |                             |      |          |          |             |    |

| AMS     | C N/A                                |     |      |            |    | ne1 | REVISION LEVEL                                          |            |       |     |                           | SHEET OF |                      |     |             |      |              |          | OF        |             |                             |      |          |          |             |    |

• U.S. GOVERNMENT PRINTING OFFICE: 1987 — 748-129/60911 5962-E1250

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

1.3 Absolute maximum ratings.

| Storage temperature                                           | -65°C to +150°C             |

|---------------------------------------------------------------|-----------------------------|

| Voltage on any_pin with respect to V <sub>SS</sub> or ANGND - | -0.3 V to +7 V              |

| Voltage from EA or Vpp to VSS or ANGND                        | -0.3 V to +13 V             |

| Power dissipation $(P_D)$                                     | 1.5 W                       |

| Lead temperature (soldering, 10 seconds)                      | 300°C                       |

| Thermal resistance, junction-to-case (O <sub>JC</sub> ):      | •                           |

| Case Y                                                        | 9°C/W 2/                    |

| Case Z                                                        | See MIL-M-38510, appendix C |

| Junction temperature (T <sub>J</sub> )                        | 175°C                       |

1.4 Recommended operating conditions.

| Case operating temperature range (T <sub>C</sub> ) | 3/ | -55°C to +125°C |

|----------------------------------------------------|----|-----------------|

| Digital supply voltage $(V_{CC})$                  |    | 4.5 V to 5.5 V  |

| Analog supply voltage (VREF)                       |    | 4.5 V to 5.5 V  |

| Power down supply voltage (VpD)                    |    | 4.5 V to 5.5 V  |

| Oscillator frequency (FOSC)                        |    | 6 MHz to 12 MHz |

1/ Lid shall be transparent to permit ultraviolet light erasure.

2/ When a thermal resistance value is included in MIL-M-38510, appendix C, it shall supersede the value herein.

3/ Case temperatures are instant on.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                |   | 5962-86809 |  |

|------------------------------------------------------|-----------|----------------|---|------------|--|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | • | SHEET 2    |  |

DESC FORM 193A SEP 87

± U. S. GOVERNMENT PRINTING OFFICE: 1988--549-904

#### 2. APPLICABLE DOCUMENTS

2.1 Government specification and standard. Unless otherwise specified, the following specification and standard, of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

**SPECIFICATION**

**MILITARY**

MIL-M-38510

Microcircuits, General Specification for.

**STANDARD**

**MILITARY**

MIL-STD-883

Test Methods and Procedures for Microelectronics.

(Copies of the specification and standard required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

- 2.2 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

- 3. REQUIREMENTS

- 3.1 Item requirements. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein.

- 3.2 Design, construction, and physical dimensions. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 and herein.

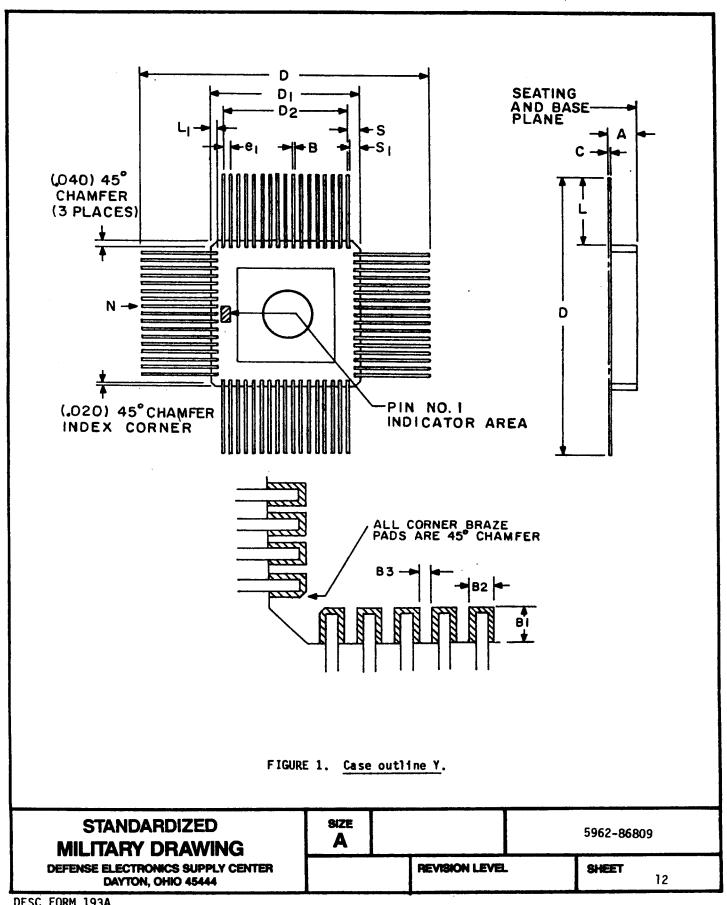

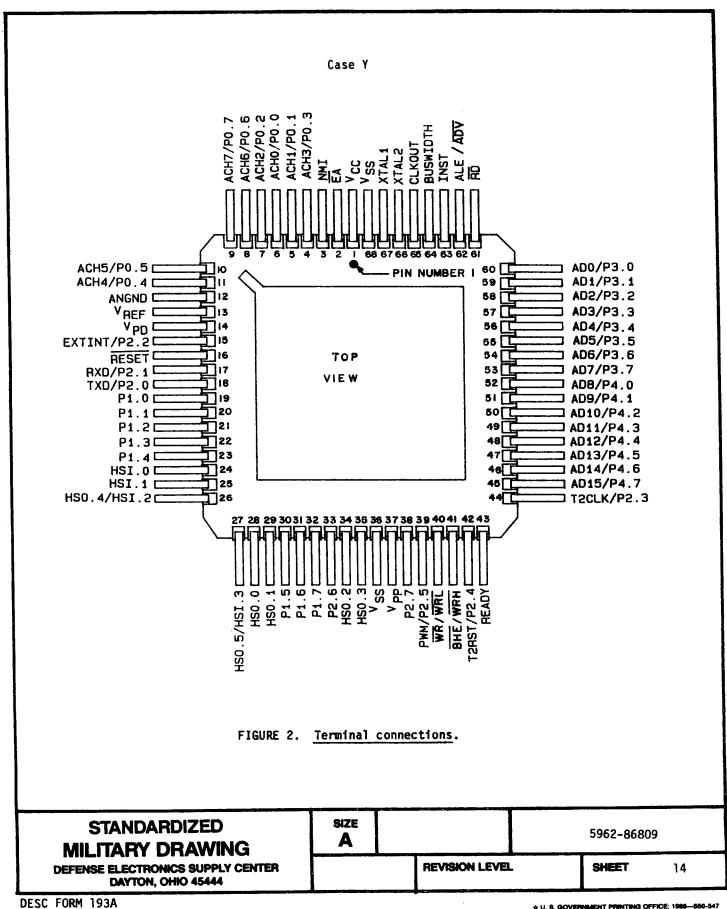

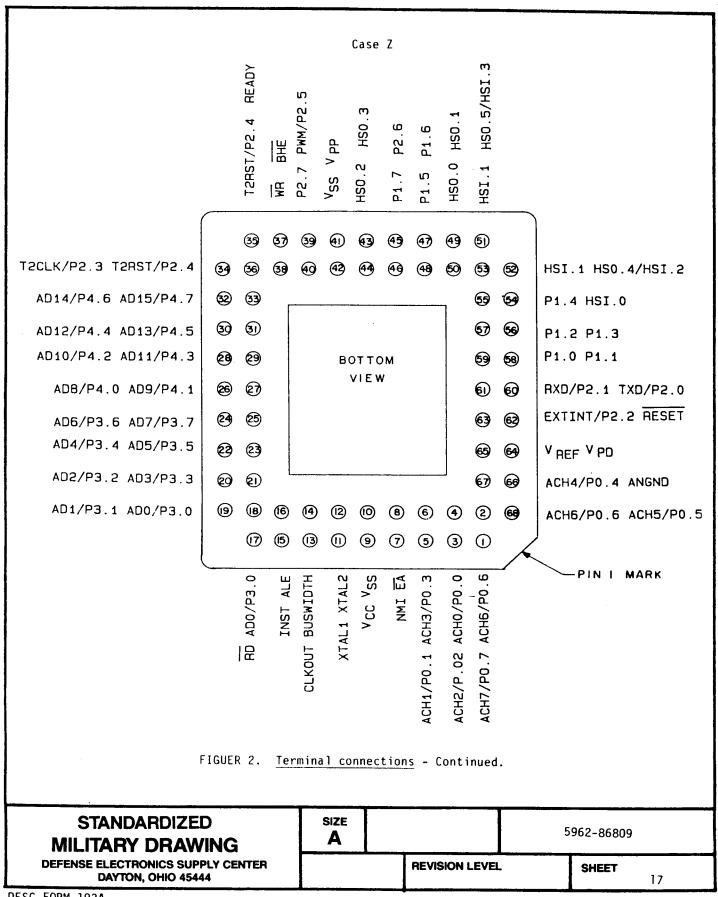

- 3.2.1 Terminal connections. The terminal connections shall be as specified on figure 2.

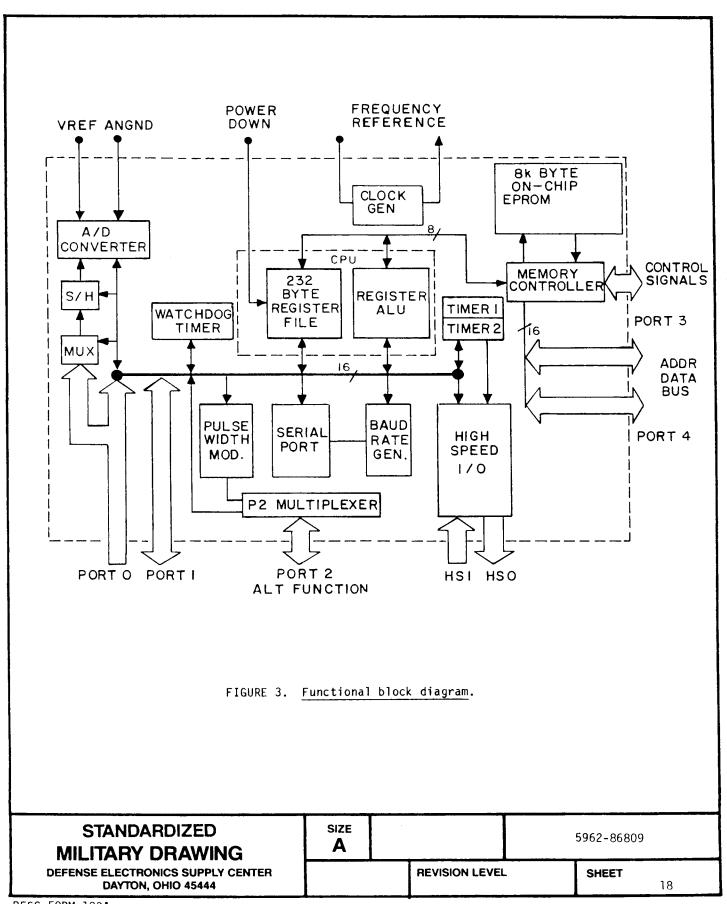

- 3.2.2 Functional block diagram. The functional block diagram shall be as specified on figure 3.

- 3.2.3 Instruction set. The instruction set summary shall be as specified on figure 4.

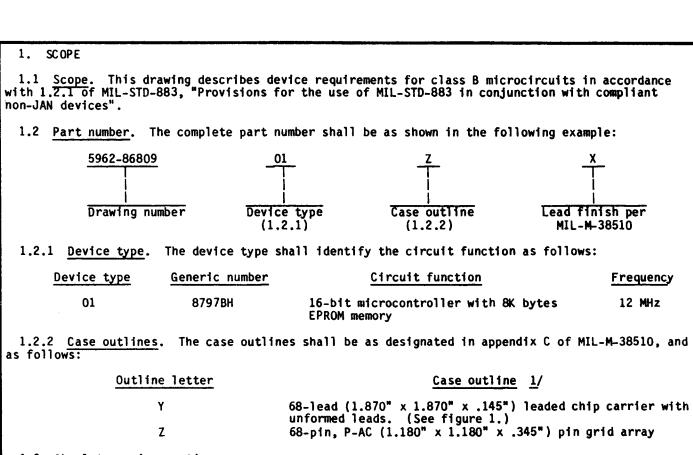

- 3.2.4 Case outlines. The case outlines shall be in accordance with 1.2.2 herein.

- 3.3 Electrical performance characteristics. Unless otherwise specified, the electrical performance characteristics are as specified in table I and apply over the full operating temperature range.

- 3.4 Marking. Marking shall be in accordance with MIL-STD-883 (see 3.1 herein). The part shall be marked with the part number listed in 1.2 herein. In addition, the manufacturer's part number may also be marked as listed in 6.5 herein.

| STANDARDIZED MILITARY DRAWING                           | SIZE<br>A |              |    | 5962-86809 |  |

|---------------------------------------------------------|-----------|--------------|----|------------|--|

| DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 |           | REVISION LEV | EL | SHEET 3    |  |

DESC FORM 193A SEP 87

# U. 8. GOVERNMENT PRINTING OFFICE: 1988-549-904

| Test                                                                      | C<br> Symbol -55°C |                     | onditions 1/                                                                                       | <br> <br> Group A    | Device       | Limits         |                      | Unit                   |

|---------------------------------------------------------------------------|--------------------|---------------------|----------------------------------------------------------------------------------------------------|----------------------|--------------|----------------|----------------------|------------------------|

| 1630                                                                      |                    | YSS =               | $< T_C < +125$ C<br>$/P_D = 5 V \pm 10\%$<br>ANGND = 0 V<br>= 6.0 to 12 MHz<br>otherwise specified | sub-<br> groups      | type         | Min            | Max                  | <br> <br> <br>         |

| Supply current                                                            | ICC                | All outpo           | uts disconnected 2/                                                                                | 1, 2, 3              | A11          | <br>           | 275                  | l mA                   |

| V <sub>PD</sub> supply current                                            | I <sub>PD</sub>    | Normal or   down    | peration and power-                                                                                | 1, 2, 3              | A11<br>      | <br> <br> <br> | 1                    | l mA                   |

| V <sub>REF</sub> supply current                                           | IREF               | İ                   | <u>2</u> /                                                                                         | 1, 2, 3              | All          | i<br> <br>     | 8                    | l mA                   |

| Input low voltage<br>(except RESET)                                       | V <sub>IL</sub>    | Ţ                   |                                                                                                    | 1, 2, 3              | A11          | -0.3           | 0.8                  | V                      |

| Input low voltage<br>RESET                                                | V <sub>IL1</sub>   | †<br> <br>          |                                                                                                    | 1, 2, 3              | A11          | -0.3           | 0.7                  | <br>  Y<br>            |

| Input high voltage<br>(except RESET, NMI<br>and XTAL1)                    | V <sub>IH</sub>    | †<br> <br> -<br> -  | •                                                                                                  | 1, 2, 3              | A11          | 2.0            | Y <sub>CC</sub> +0.5 | V                      |

| Input high voltage, RESET rising                                          | V <sub>IH1</sub>   |                     |                                                                                                    | 1, 2, 3              | A11<br> <br> | 2.4            | V <sub>CC</sub>      | V                      |

| Input high voltage<br>RESET falling<br>hysteresis                         | V <sub>IH2</sub>   |                     |                                                                                                    | 1, 2, 3              | A11          | 2.1            | Y <sub>CC</sub> +0.5 | \<br>  \               |

| Input high voltage<br>NMI, XTAL1                                          | I <sub>V</sub> IH3 | T<br> <br>          |                                                                                                    | 1, 2, 3              | A11          | 2.2            | V <sub>CC</sub> +0.5 | \<br>  \<br>           |

| Input leakage current<br>to each pin of HSI<br>Port 3, Port 4 and<br>P2.1 | ILI                | V <sub>IN</sub> = 0 | to Vcc<br>2/                                                                                       | 1, 2, 3              | All          | †<br>!<br>!    | ±10                  | μ.                     |

| D.C. input leakage<br>current to each pin<br>of Port 0                    | ILI1               | V <sub>IN</sub> = 0 | to VCC                                                                                             | 1, 2, 3              | A11          |                | 3                    | <del>ا</del><br>لاير ا |

| See footnotes at end o                                                    | f table.           |                     |                                                                                                    |                      |              |                |                      |                        |

| STANDARD                                                                  |                    | G                   | SIZE A                                                                                             |                      |              | 5962-          | 86809                |                        |

| MILITARY DRAWING  DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444    |                    |                     | RE                                                                                                 | REVISION LEVEL SHEET |              |                |                      |                        |

± U. S. GOVERNMENT PRINTING OFFICE: 1988-549-90

| TABL                                                                                                  | E I. <u>Ele</u>                                    | ctrical p                           | erformance                                                                                                | chara                 | cteristi             | <u>:s</u> -                   | Continued              |              |              |            |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------|----------------------|-------------------------------|------------------------|--------------|--------------|------------|

| Test                                                                                                  | Symbo1                                             |                                     | Conditions 1/ 1<br>C < T <sub>C</sub> < +125°C   1<br>V <sub>PD</sub> = 5 V ±10%   1<br>= ANGND = 0 V   1 |                       | i<br>  Grou<br>  sub |                               | <br>  Device<br>  type | Lim          | Unit         |            |

|                                                                                                       |                                                    |                                     | ANGND = 0<br>= 6.0 to 1<br>otherwise                                                                      | 2 MHz                 | l grou               |                               |                        | Min<br> <br> | Max<br> <br> | <br> <br>  |

| Input high current<br>to EA                                                                           | IIH                                                | <br> V <sub>IH</sub> = 2.4<br>      | 2/<br>2/                                                                                                  |                       | 1, 2                 | , 3                           | <br>  A11<br>          |              | 100          | μΑ         |

| Input low current<br>to Port 1, and P2.6,<br>P2.7                                                     | IIL                                                | <br> V <sub>IL</sub> = 0.4<br> <br> | 15 V<br>2/                                                                                                |                       | 1, 2                 | 2, 3                          | A11                    | <br>         | -125         | μ <b>A</b> |

| Input low current<br>to RESET                                                                         | I IL1                                              | V <sub>IL</sub> = 0.4               | 15 V<br>2/                                                                                                |                       | 1, 2                 | 3                             | <br>  A11<br>          | -0.25        | -2           | mA         |

| Input low current<br>P2.2, P2.3, P2.4,<br>READY, BUSWIDTH                                             | I <sub>IL2</sub>                                   | V <sub>IL</sub> = 0.4               | 15 V<br>2/                                                                                                |                       | 1, 2                 | 2, 3                          | ATT                    | <br>         | -50          | µА         |

| Output low voltage on<br>Quasi-Bidirectional<br>port pins and<br>Port 3, Port 4<br>when used as ports | V <sub>OL</sub>                                    | I <sub>OL</sub> = 0.8               | 3 mA<br>2/ 3/                                                                                             |                       | 1, 2                 | 2, 3                          | A11<br>                | <br>         | 0.45         | V          |

| Output low voltage on<br>Quasi-Bidirectional<br>port pins and<br>Port 3, Port 4<br>when used as ports | V <sub>OL1</sub>                                   | I <sub>OL</sub> = 2.(               | 0 mA<br>2/ <u>3</u> / <u>4</u>                                                                            | <u>5</u> /            | 1, 2                 | 2, 3                          | A11                    |              | 0.75         | V          |

| Output low voltage on standard output pins, RESET and Bus/control pins                                | V <sub>OL2</sub>                                   | I <sub>OL</sub> = 2.0               | 0 mA<br>2/3/4                                                                                             | <u>5/ 5/ 6</u>        | / 1, 2               | 2, 3                          | i A11                  | <br>         | 0.45         | V          |

| Output high voltage on<br>Quasi-bidirectional<br>pins                                                 | v <sub>OH</sub>                                    | I I OH = -20                        | Ο μ <b>Α</b> <u>3</u>                                                                                     | <u>2</u> / <u>3</u> / | 1, 2                 | 2, 3                          | <br>  A11<br>          | 2.4          |              | V          |

| Output high voltage on standard output pins and Bus/control pins                                      | V <sub>OH1</sub>                                   | I <sub>OH</sub> = -20               | )Ο μA <u>2</u>                                                                                            | <u>2</u> / <u>3</u> / | 1, 2                 | 2, 3                          | All                    | 2.4          |              | V          |

| See footnotes at end of                                                                               | table.                                             | <u> </u>                            | <del></del>                                                                                               |                       |                      |                               | <u> </u>               |              |              |            |

| STANDARDI                                                                                             | _                                                  |                                     | SIZE                                                                                                      |                       |                      |                               |                        | E060 0       | 06000        |            |

|                                                                                                       | MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER |                                     |                                                                                                           |                       | REVISION             | 5962-86809  ON LEVEL SHEET  5 |                        |              | -            |            |

★ U. 8, GOVERNMENT PRINTING OFFICE: 1988—549-904

| Test                                                                   | Symbol   -55°C             |                                                | < Tr < +1                              | Conditions 1/<br>°C < T <sub>C</sub> < +125°C (<br>= V <sub>PD</sub> = 5 V ±10% |                     |      | Lim                   | its               | Un1            |

|------------------------------------------------------------------------|----------------------------|------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------|---------------------|------|-----------------------|-------------------|----------------|

|                                                                        |                            | VSS =                                          | ANGND = 0<br>= 6.0 to 1<br>otherwise   | ) V<br>.2 MHz                                                                   | sub-<br> groups<br> | type | Min                   | Max               | <br> <br> <br> |

| Output high current<br>on RESET                                        | 1 0H3                      | V <sub>OH</sub> = 2.4                          | 4 V<br><u>2</u> /                      |                                                                                 | 1, 2, 3             | ATT  | -50<br>               |                   | μ <b>Α</b>     |

| Pin capacitance                                                        | C <sub>S</sub>             | <br> f = 1.0 N<br> See 4.3.2                   |                                        | 2/                                                                              | 4                   | All  |                       | 10                | l pF           |

| Functional tests                                                       |                            | See 4.3.                                       | le                                     | 2/                                                                              | 7,8                 | All  | †                     |                   |                |

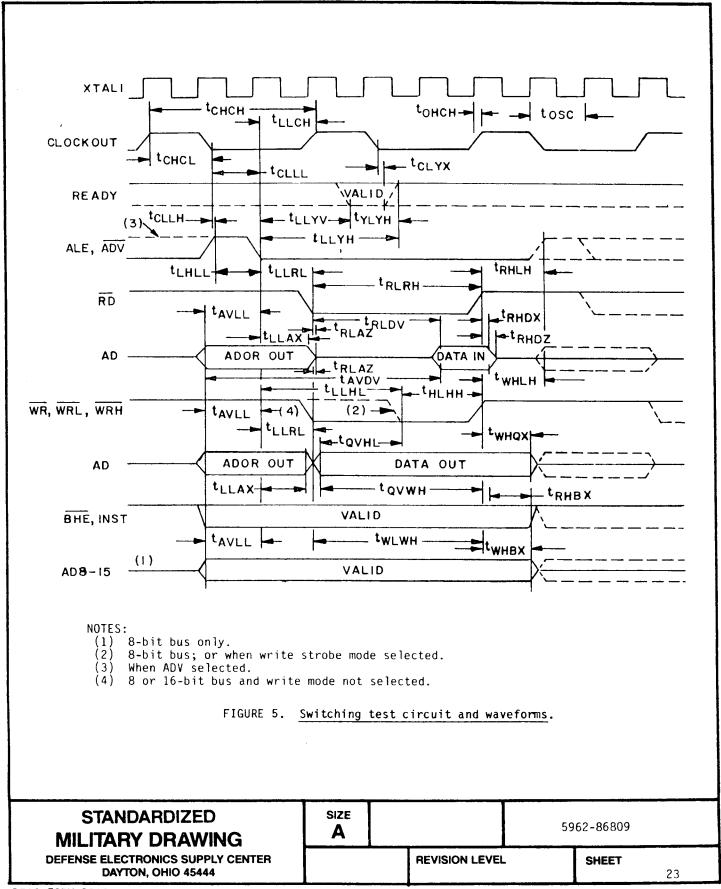

| READY hold after<br>CLKOUT edge                                        | t <sub>CLYX</sub>          | (system o                                      | equirement<br>components<br>se specifi | must                                                                            | 9,10,11             | All  | 0                     |                   | ns             |

| End of ALE/ADV to<br>READY valid                                       | t <sub>LLY</sub> y         | TSee figu<br> f <sub>OSC</sub> = 10<br> <br> - |                                        |                                                                                 | 9,10,11             | All  |                       | 2t <sub>0SC</sub> | ns<br>I        |

| End of ALE/ADV to<br>READY high                                        | <b>ቲ</b> LYH               | <u> </u><br> <br>                              |                                        |                                                                                 | 9,10,11             | A11  | 2t <sub>OSC</sub> +40 | 4t <sub>0SC</sub> | l ns           |

| Non-Ready time                                                         | tyLYH                      |                                                |                                        |                                                                                 | 9,10,11             | A11  |                       | 1000              | ns             |

| Address valid to input data valid 7/                                   | t <sub>AVDV</sub>          | <br> <br> <br> -                               |                                        |                                                                                 | 9,10,11             | A11  | <br> <br>             | 5t <sub>0SC</sub> | l ns           |

| RD active to input<br>data valid                                       | t <sub>RLDV</sub>          |                                                |                                        |                                                                                 | 9,10,11             | A11  |                       | 3t <sub>0SC</sub> | l ns           |

| Data hold after RD<br>inactive                                         | t <sub>RHDX</sub>          | <br> <br> -                                    |                                        |                                                                                 | 9,10,11             | All  | 0                     |                   | l ns           |

| RD inactive to input<br>data float                                     | <br> t <sub>RHDZ</sub><br> |                                                |                                        |                                                                                 | 9,10,11             | A11  | 0                     | t <sub>OSC</sub>  | l ns           |

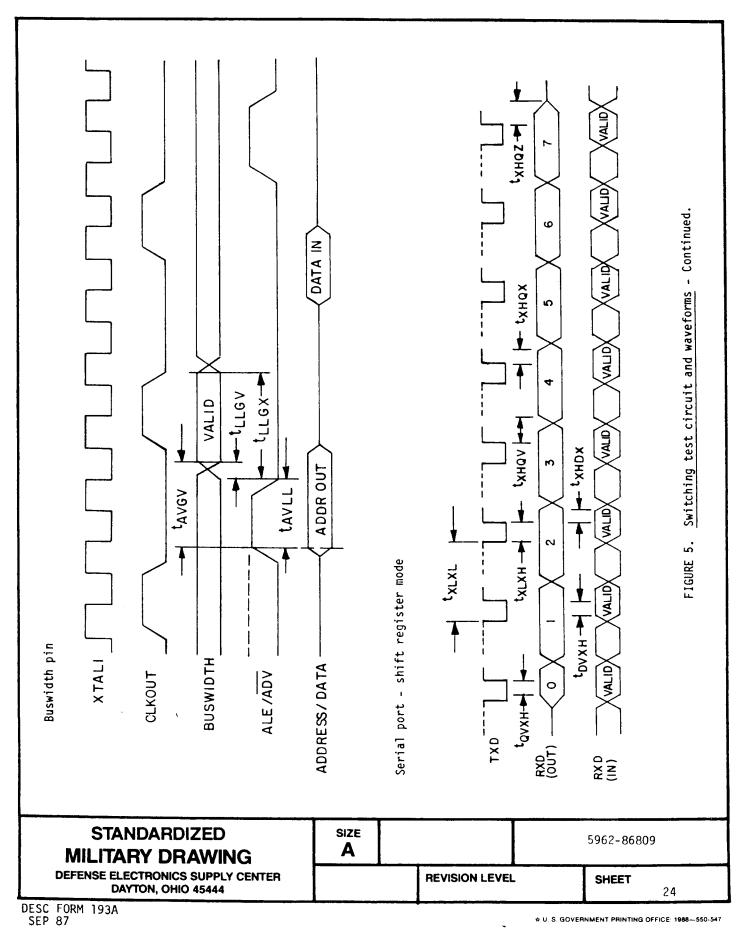

| Address valid to<br>BUSWIDTH valid <u>7</u> /                          | t <sub>AVGV</sub>          |                                                |                                        |                                                                                 | 9,10,11             | All  |                       | 2t <sub>0SC</sub> | ns             |

| See footnotes at end of                                                | table.                     |                                                |                                        |                                                                                 |                     |      |                       |                   |                |

| STANDARD                                                               | _                          |                                                | SIZE<br>A                              |                                                                                 | ··-·-               |      | 5962                  | 86809             |                |

| MILITARY DRAWING  DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                            | REVISION LEVEL                                 |                                        |                                                                                 | <del></del>         |      |                       |                   |                |

# U. S. GOVERNMENT PRINTING OFFICE: 1988--549-904

| Test                                            | <br> Symbol       | -55°C                                              | nditions 1/<br>< T <sub>C</sub> < +125 C<br>PD = 5 V ±10% |                          | Device             | Limits                         |                   | l<br>  Unit<br> |  |

|-------------------------------------------------|-------------------|----------------------------------------------------|-----------------------------------------------------------|--------------------------|--------------------|--------------------------------|-------------------|-----------------|--|

|                                                 |                   | Vcc =                                              | ANGND = 0 V<br>6.0 to 12 MHz<br>therwise specified        | sub-<br> groups<br> <br> | type<br> <br> <br> | Min                            | Max               | !<br>!<br>!     |  |

| BUSWIDTH hold after<br>ALE/ADV low              | tLLGX             | component<br> specifica                            |                                                           | 9,10,11                  | A11                | t <sub>OSC</sub> +40           |                   | l<br>l ns<br>l  |  |

| ALE/ADV low to<br>BUSWIDTH valid                | t <sub>LLGV</sub> | See figur<br>  fosc = 10<br>                       | e 5.<br>MHz                                               | <br> 9,10,11<br>         | All                | <br> <br> <br>                 | tosc<br>-75       | l ns            |  |

| Oscillator frequency                            | fosc              | See figur                                          | e 5                                                       | 9,10,11                  | A11                | 6.0                            | 12.0              | MHz             |  |

| Oscillator period                               | tosc              | -<br> <br>                                         |                                                           | 9,10,11                  | ATT                | 83                             | 166               | l ns            |  |

| XTAL1 Rising edge to<br>clockout rising<br>edge | t <sub>OHCH</sub> | See figur                                          | e 5<br>MHz                                                | 9,10,11                  | A11                | 0                              | 120               | ns              |  |

| CLKOUT period <u>6</u> /                        | t <sub>CHCH</sub> | 1                                                  |                                                           | 9,10,11                  | <br>  A11          | 3tosc                          | 3t <sub>OSC</sub> | l ns            |  |

| CLKOUT high time                                | tchcl             |                                                    |                                                           | 9,10,11                  | A11                | 3t <sub>0SC</sub>   -35        | 3t <sub>0SC</sub> | ns              |  |

| CLKOUT low to ALE high                          | tCLLH             | -<br> <br> <br>                                    |                                                           | 9,10,11                  | All                | -20                            | +25               | ns              |  |

| ALE/ADV low to CLKOUT high                      | tLLCH             | -i<br> <br>                                        |                                                           | 9,10,11                  | All                | tosc                           | tosc<br>+45       | ns              |  |

| ALE/ADV high time                               | t <sub>LHLL</sub> | -<br> <br> <br> <br> <br> <br>                     |                                                           | 9,10,11                  | A11                | tosc<br>  -30<br>  9/          | +35<br>9/         | ns              |  |

| Address setup to end of ALE/ADV 7/              | tAVLL             | -;<br>!<br>!                                       |                                                           | 9,10,11                  | A11                | t <sub>OSC</sub>               |                   | ns              |  |

| RD or WR low to<br>address float <u>10</u> /    | t <sub>RLAZ</sub> | -<br> <br> <br>                                    |                                                           | 9,10,11                  | A11                |                                | 25                | ns              |  |

| See footnotes at end o                          | f table.          |                                                    |                                                           | •                        | •                  | <u>. •</u>                     | •                 | *               |  |

| STANDARI                                        |                   | 2                                                  | SIZE<br>A                                                 |                          |                    | 5962-                          | -86809            |                 |  |

|                                                 | S SUPPLY (        | MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER |                                                           |                          | 1<br>5L            | 5962-86809<br>- <b>SHEET</b> 7 |                   |                 |  |

**★ U. S. GOVERNMENT PRINTING OFFICE: 1988—549-90**

| Test I                                           | Symbol                       |                                             | itions <u>1/</u><br>T <sub>C &lt;</sub> +125°C                                            | Group A             | <br> <br> Device   | <br>  Lim                       | its                    | l<br>! Unit<br> |

|--------------------------------------------------|------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------|---------------------|--------------------|---------------------------------|------------------------|-----------------|

|                                                  |                              | $V_{SS} = AN$                               | T <sub>C &lt;</sub> +125°C<br>= 5 V ±10%<br>GND = 0 V<br>.0 to 12 MHz<br>erwise specified | sub-<br> groups<br> | type<br> <br> <br> | Min                             | Max                    | <br> <br> <br>  |

| End of ALE/ADV to<br>RD or WR active             | <sup>t</sup> LLRL            | <br> See figure<br> f <sub>OSC</sub> = 10 M | 5<br>Hz                                                                                   | 9,10,11             | ATT                | t <sub>OSC</sub>                |                        | l ns            |

| Address hold after<br>end of ALE/ADV <u>10</u> / | ቲ <sub>LAX</sub>             | <br> <br> <br> <br>                         |                                                                                           | 9,10,11             | All                | tosc<br>-40                     |                        | ns              |

| WR pulse width                                   | t <sub>WLWH</sub>            | T<br> <br> <br> <br>                        |                                                                                           | 9,10,11             | All                | 3t <sub>0SC</sub>               |                        | ns              |

| Output data valid<br>to end of WR/WRL/<br>WRH    | <sup>t</sup> QVWH            | <br> <br> -<br>                             |                                                                                           | 9,10,11             | A11                | 3t <sub>0SC</sub>               |                        | ns              |

| Output data hold<br>after WR/WRL/WRH             | t <sub>WHQX</sub>            | <u> </u>                                    |                                                                                           | 9,10,11             | All                | tosc<br>-50                     |                        | ns              |

| End of WR/WRL/WRH to<br>ALE/ADV high             | t <sub>WHLH</sub>            | <br> <br> <br>                              |                                                                                           | 9,10,11             | All                | t <sub>OSC</sub>                |                        | ns              |

| RD pulse width                                   | t <sub>rlr</sub> h           |                                             |                                                                                           | 9,10,11             | A11                | 3t <sub>0SC</sub><br>  -30      | <br> <br> <br>         | l ns            |

| End of RD to ALE/ADV<br>high                     | <br> t <sub>RHLH</sub><br>   | T<br> <br>                                  |                                                                                           | 9,10,11             | A11                | 3t <sub>0SC</sub><br> <br>  -45 |                        | ns              |

| CLOCKOUT low to ALE/                             | t <sub>CLLL</sub>            | †<br> <br> <br>                             |                                                                                           | 9,10,11             | All                | tosc<br>-40                     | t <sub>0SC</sub> +35   | ns              |

| RD high to INST, BHE,<br>AD8-15 inactive         | I<br>  t <sub>RHBX</sub><br> | T<br> <br> <br>                             |                                                                                           | 9,10,11             | A11                | t <sub>OSC</sub>                | t <sub>0SC</sub>   +30 | ns              |

| WR high to INST, BHE,<br>AD8-15 inactive         | t <sub>WHBX</sub>            | T<br> <br>                                  |                                                                                           | 9,10,11             | All                | tosc                            | t <sub>0SC</sub> +100  | i ns            |

| See footnotes at end                             | of table                     | •                                           |                                                                                           | ·                   |                    |                                 |                        |                 |

| STANDARDIZED                                     | SIZE<br>A                    | · · · · · · · · · · · · · · · · · · ·       |                                                                                           | 5962                | 2-86809            |                                 |                        |                 |

| MILITARY D                                       |                              |                                             |                                                                                           | REVISION LE         | L                  |                                 | EET                    |                 |

± U. S. GOVERNMENT PRINTING OFFICE: 1968—549-904

| Test                                                                  | Symbol            | Cond<br>-55°C <                        | itions 1/<br>T <sub>C &lt; +125</sub> C<br>= 5 V ±10%       |                             | Device | Limits                      |                          | Unit |

|-----------------------------------------------------------------------|-------------------|----------------------------------------|-------------------------------------------------------------|-----------------------------|--------|-----------------------------|--------------------------|------|

|                                                                       |                   | VSS = AN                               | = 5 V ±10%<br>GND = 0 V<br>.0 to 12 MHz<br>erwise specified | sub-<br> g <b>roups</b><br> | type   | Min                         | Max                      |      |

| WRE, WRH low to WRE<br>WRH high                                       | t <sub>HLHH</sub> | See figure<br> f <sub>OSC</sub> = 10 M | 5<br>IHz                                                    | 9,10,11                     | A11    | 2t <sub>OSC</sub>           | 2t <sub>0SC</sub> +40    | ns   |

| ALE/ADV low to WRE, WRH low                                           | tlihl<br>         |                                        |                                                             | 9,10,11                     | All    | 2t <sub>OSC</sub>           | 2t <sub>OSC</sub><br>+55 | ns   |

| Output data valid to WRE, WRH low                                     | t <sub>QVHL</sub> |                                        |                                                             | 9,10,11                     | All    | t <sub>0SC</sub><br>  -60   |                          | ns   |

| Serial port clock<br>period                                           | txLxL             | Serial port                            | shift register<br>igure 5                                   | 9,10,11                     | A11    | 8t <sub>OSC</sub>           |                          | ns   |

| Serial port clock<br>falling edge to<br>rising edge                   | t <sub>XLXH</sub> | T<br> <br> <br> <br>                   |                                                             | 9,10,11                     | A11    | 4t <sub>0SC</sub><br>  -50  | 4t <sub>0SC</sub> +50    | ns   |

| Output data setup<br>to clock rising<br>edge                          | ₹QVXН             |                                        |                                                             | 9,10,11                     | I FA   | 3t <sub>OSC</sub>           |                          | ns   |

| Output data hold<br>after clock rising<br>edge                        | t <sub>XHQX</sub> |                                        |                                                             | 9,10,11                     | A11    | 2t <sub>0SC</sub>           |                          | ns   |

| Next output data<br>valid after clock<br>rising edge                  | ¢хноу             |                                        |                                                             | 9,10,11                     | A11    |                             | 2t <sub>0SC</sub> +50    | ns   |

| Input data setup<br>to clock rising<br>edge                           | ¢D∀XH             | -T<br> <br> <br> <br>                  |                                                             | 9,10,11                     | A11    | 2t <sub>0SC</sub><br>  +200 |                          | l ns |

| Input data hold<br>after clock rising<br>edge                         | †XHDX             | Ţ                                      |                                                             | 9,10,11                     | A11    | 0                           |                          | n s  |

| See footnotes at end                                                  | of table          |                                        |                                                             |                             |        |                             |                          |      |

| STANDAF                                                               |                   |                                        | SIZE<br>A                                                   |                             |        | 5962                        | 2-86809                  |      |

| MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                   |                                        | REVISION LE                                                 | VEL.                        |        |                             |                          |      |

# U. S. GOVERNMENT PRINTING OFFICE: 1900-549-904

| Test                              | <br> Symbol                  | Conditions 1/<br>  -55°C < T <sub>C</sub> < +125°C     | <br> Group A        | <br> Device | L1      | Uni               |              |

|-----------------------------------|------------------------------|--------------------------------------------------------|---------------------|-------------|---------|-------------------|--------------|

|                                   |                              | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | sub-<br> groups<br> | type        | Min<br> | Max               | -;<br>!<br>! |

| Last clock rising to output float | txHQZ                        | <br> Serial port shift register<br> mode, see figure 5 | 9,10,11             | All         |         | 5t <sub>OSC</sub> | ns           |

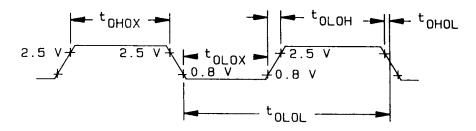

| Oscillator frequency              | <br> 1/t <sub>OLOL</sub><br> | <br> External clock drive,<br> see figure 5            | 9,10,11             | A11         | 6       | 12                | MH;          |

| High time                         | toHOX                        |                                                        | 9,10,11             | All         | 1 25    | 1                 | ns           |

| Low time                          | t <sub>OLOX</sub>            |                                                        | 9,10,11             | All         | 25      |                   | ns           |

| Rise time                         | <sup>‡</sup> OLOH            |                                                        | 9,10,11             | A11         |         | 15                | ns           |

| Fall time                         | toHOL                        |                                                        | 9,10,11             | A11         |         | 15                | ns           |

| Resolution                        | 1                            | <br> See figure 5<br> V <sub>REF</sub> = 5 V ±10%      | 9,10,11             | A11         | 1024    | 1024              | leve<br>bits |

| Absolute error                    | <br> <br>                    |                                                        | 9,10,11             | All         | 0       | ±4                | LSBS         |

| Non-lineraity                     |                              | -<br> <br>                                             | 9,10,11             | A11         | 0       | ±4                | LSBS         |

| Differential non-<br>linearity    |                              | -]<br> <br>                                            | 9,10,11             | A11         | 0       | ±2                | LSBS         |

| Channel to channel matching       |                              |                                                        | 9,10,11             | All         | 0       | ±1                | LSBS         |

| Off isolation<br>11/ 12/ 13/      |                              | <br> See figure 5                                      | 9,10,11             | A11         | -60     |                   | dB           |

See footnotes on next page.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |       |            | 5962-86809 |   |

|------------------------------------------------------|-----------|-------|------------|------------|---|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVIS | BION LEVEL | SHEET 10   | ) |

DESC FORM 193A SEP 87

# U. S. GOVERNMENT PRINTING OFFICE: 1988-549-90

- Case temperatures are instant on.

- $2/V_{REF} = V_{PP} = V_{EA} = 5 V \pm 10\%$ .

- Quasi-bidirectional pins include those on P1, for P2.6 and P2.7. Standard output pins include TXD, RXD (mode 0 only), PWM and HSO pins. Bus/Control pins include CLKOUT, ALE, BHE, RD WR. INST, and ADO-15.

- Maximum current per pin must be externally limited to the following value if Vol is held above 0.45 V.

$I_{OL}$  on quasi-bidirectional pins and Ports 3 and 4 when used as ports: 4.0 mA.

IOL on standard output pins and RESET: 8.0 mA.

IoL on Bus/Control pins: 2.0 mA.

$\frac{5}{}$  During normal (non-transient) operation the following limits apply:

Total I $_{0L}$  on port 1 must not exceed 8.0 mA. Total I $_{0L}$  on P2.0, P2.6, RESET and all HSO pins must not exceed 15 mA. Total I $_{0L}$  on port 3 must not exceed 10 mA. Total I $_{0L}$  on P2.5, P2.7, and port 4 must not exceed 20 mA.

- $\frac{6}{100}$  on HSO.X (X = 0, 4, 5) = 1.6 mA @ 0.5 V.

- 7/ The term "Address Valid" applies to ADO-15, BHE and INST.

- CLKOUT is directly generated as a divide by 3 of the oscillator. The period will be 3tosc  $\pm 10$  ns if  $t_{OSC}$  is constant and the rise and fall times on XTAL1 are less than 10 ns.

- 9/ Max spec applies only to ALE. Min spec applies to both ALE and ADV.

- 10/ The term "Address" in this definition applies to ADO-7 for 8-bit cycles, and ADO-15 for 16-bit cycles.

- 11/ These values are not tested in production and are based on theoretical estimates and laboratory tests.

- 12/ DC to 100 kHz.

- 13/ Multiplexer Break Before Make Guaranteed.

- 3.5 Certificate of compliance. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in 6.4. The certificate of compliance submitted to DESC-ECS prior to listing as an approved source of supply shall state that the manufacturer's product meets the requirements of MIL-STD-883 (see 3.1 herein) and the requirements herein.

- 3.6 Certificate of conformance. A certificate of conformance as required in MIL-STD-883 (see 3.1 herein) shall be provided with each lot of microcircuits delivered to this drawing.

- 3.7 Notification of change. Notification of change to DESC-ECS shall be required in accordance with MIL-STD-883 (see 3,1 herein).

- 3.8 Verification and review. DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

STANDARDIZED SIZE A 5962-86809 MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER REVISION LEVEL SHEET DAYTON, OHIO 45444 11

DESC FORM 193A **SEP 87**

**☆ U. S. GOVERNMENT PRINTING OFFICE: 1988--549-904**

± U. S. GOVERNMENT PRINTING OFFICE: 1988—680-547

| <br>                      | Dim        | ens ions |        |        |  |

|---------------------------|------------|----------|--------|--------|--|

|                           | Inc        | hes      | Millim | eters  |  |

| Symbol                    | Min        | Max      | Min    | Max    |  |

| A                         | .090 l     | .195     | 2.25   | 3.68   |  |

| В                         | .016       | .020     | 0.41   | 0.51   |  |

| B <sub>1</sub> <u>1</u> / | .040       | .060     | 1.02   | 1.52   |  |

| B <sub>2</sub> <u>1</u> / | .030       | .040     | 0.76   | 1.02   |  |

| B <sub>3</sub> <u>1</u> / | .005       | .020     | 0.13   | 0.51   |  |

| С                         | .008       | .012     | 0.20   | 0.31   |  |

| D D                       | 1.640      | 1.870    | 41.66  | 47.50  |  |

| D <sub>1</sub>            | .935       | .970     | 23.75  | 24.64  |  |

| 02                        | . 800<br>! | BSC      | 20.3   | 32 BSC |  |

| e <sub>1</sub>            | .050       | D BSC    | 1.3    | 27 BSC |  |

| L                         | .375       | .450     | 9.53   | 11.43  |  |

| L <sub>1</sub>            | .040       | .060     | 1.02   | 1.52   |  |

| N                         | 6          | 8        | i 68   |        |  |

| S                         | .066       | .087     | 1.68   | 2.21   |  |

| s <sub>1</sub>            | .050       |          | 1.27   | [<br>  |  |

$\underline{1}$ / These are typical values.

FIGURE 1. Case outline Y - Continued.

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

FREVISION LEVEL

SHEET

13

DESC FORM 193A SEP 87

U. S. GOVERNMENT PRINTING OFFICE: 1968—550-547

**SEP 87**

± U. S. GOVERNMENT PRINTING OFFICE: 1988-560-547

| Case Z | Case Y | Description      | Case Z | Case Y | Description               | Case Z | Case Y | Description     |

|--------|--------|------------------|--------|--------|---------------------------|--------|--------|-----------------|

| T      | 9      | ACH7/P0.7        | 24     | 54     | AD6/P3.6                  | 47     | 31     | P1.6            |

| 1 2    | 8      | ACH6/PO.6        | 25     | 53     | AD7/P3.7                  | 48     | 30     | P1.5            |

| 2      | 7      | ACH2/PO.2        | 26     | 52     | AD8/P4.0                  | 49     | 29     | HSO.1           |

|        | 6      | ACHO/PO.O        | 27     | 51     | AD9/P4.1                  | 50     | 28     | HSO.0           |

| 4 5    | 5      | ACH1/PO.1        | 28     | 50     | AD10/P4.2                 | 51     | 27     | HS0.5/HSI.3     |

| 6      |        | ACH3/PO.3        | 29     | 49     | AD11/P4.3                 | 52     | 26     | HSO.4/HSI.2     |

| 6      | 4<br>3 | NMI              | 30     | 48     | AD12/P4.4                 | 53     | 25     | HSI.1           |

|        | 2      | EA               | 31     | 47     | AD13/P4.5                 | 54     | 24     | HSI.O           |

| 8      | ī      | Уcc              | 32     | 46     | AD14/P4.6                 | 55     | 23     | P1.4            |

| 10     | 68     | VCC              | 33     | 45     | AD15/P4.7                 | 56     | 22     | P1.3            |

| ii     | 67     | VSS<br>XTAL1     | 34     | 44     | T2CLK/P2.3                | 57     | 21     | P1.2            |

| 12     | 66     | XTAL2            | 35     | 43     | READY                     | 58     | 20     | P1.1            |

| 13     | 65     | CLKOUT           | 36     | 42     | T2RST/P2.4                | 59     | 19     | P1.0            |

| 14     | 64     | BUSWIDTH         | 37     | 41     | BHE/WRH                   | 60     | 18     | TXD/P2.0        |

| 15     | 63     | INST             | 38     | 40     |                           | 61     | 17     | RXD/P2.1        |

|        |        | INOI<br>ALE /ĀDV | 39     |        | WR/WRL                    | 62     | 16     | RESET           |

| 16     | 62     | ALE/ADV          |        | 39     | PWM/P2.5                  |        |        |                 |

| 17     | 61     | RD               | 40     | 38     | P2.7                      | 63     | 15     | EXTINT/P2.2     |

| 18     | . 60   | ADO/P3.0         | 41     | 37     | Vpp                       | 64     | 14     | V <sub>PD</sub> |

| 19     | 59     | AD1/P3.1         | 42     | 36     | V <sub>S</sub> S<br>HSO.3 | 65     | 13     | VREF<br>ANGND   |

| 20     | 58     | AD2/P3.2         | 43     | 35     |                           | 66     | 12     |                 |

| 21     | 57     | AD3/P3.3         | 44     | 34     | HS0.2                     | 67     | 11     | ACH4/PO.4       |

| 1 22   | 56     | AD4/P3.4         | 45     | 33     | P2.6                      | 68     | 10     | ACH5/PO.5       |

| 23     | 55     | AD5/P3.5         | 46     | 32     | P1.7                      | l_     |        | 1               |

FIGURE 2. <u>Terminal connections</u> - Continued.

| STANDARDIZED MILITARY DRAWING                           | SIZE<br>A |                | 5962-86809 |

|---------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET 15   |

# U. S. GOVERNMENT PRINTING OFFICE: 1988-550-54

★ U. S. GOVERNMENT PRINTING OFFICE: 1988-560-547

± U. S. GOVERNMENT PRINTING OFFICE: 1968--550-547

à U.S. GOVERNMENT PRINTING OFFICE 1988-550-547

| Mnemonic    | Oper-       | Operation (Note 1)                                    | <br>        | ,           | Fla         | 198        |          |             | Notes      |

|-------------|-------------|-------------------------------------------------------|-------------|-------------|-------------|------------|----------|-------------|------------|

|             | ands        |                                                       | Z           | l<br>I N    | l C         | ٧          | VT       | ST I        |            |

| ADD/ADDB    | 2           | <br> D <b>∢</b> D + A                                 | √           | 1           | \<br> \     | <b>√</b>   | <b>↑</b> |             |            |

| ADD/ADDB    | 3           | <br> D <b>←</b> B + A                                 | 1           | <b>!</b> √  | <b>V</b>    | <b>/</b>   | <b></b>  | _           |            |

| ADDC/ADDCB  | 2           | <br> D <b>◄</b> D + A + C                             | ₩           | 1           | 1           | \ <u> </u> | <b></b>  | _           |            |

| SUB/SUBB    | 2           | D ← D - A                                             | <b>\</b>    | <b>V</b>    | <b>V</b>    | <b>V</b>   | <b></b>  |             |            |

| SUB/SUBB    | 3           | D <b>←</b> B - A                                      | 1           | <b>V</b>    | <b>V</b>    | <b>V</b>   | <b>↑</b> | _           |            |

| SUBC/SUBCB  | 2           | <br> D <b>←</b> −D - A + C - 1                        | ₩           | 1           | 1           | 1          | 1        | <br>  -     |            |

| CMP/CMPB    | 2           | ID - A                                                | <b>V</b>    | \ <u>/</u>  | 1           | 1          | 1        | <br>  -     |            |

| MUL/MULU    | 2           | <br> D, D + 2 <b>←</b> D*A                            | -           | -           | <br> -      | <br>  -    | <br>     | ?           | 2          |

| MUL/MULU    | 3           | D, D + 2 ← B*A                                        | -           | -           | <br>  -     | <br>  -    | !<br>! - | 7           | l<br>  2   |

| MULB/MULUB  | 2           | D, D + 1 <b>←</b> D*A                                 | <br> -      | <br>  -     | <br>  -     | <br>  -    | !<br>  - | 7           | <br>  3    |

| MULB/MULUB  | 3           | D, D + 1 <b>←</b> B*A                                 | <br>  -     | -           | -           | -          | -        | ?           | 3          |

| DIVU        | 2           | D 			 (D, D + 2)/A, D + 2                             | <br>  -<br> | -           | <br> -<br>  | <u> </u> / | <b> </b> | -           | 2          |

| DIVUB       | 2           | D <b>←</b> (D, D + 1)/A, D + 1 <del>←</del> remainder | <br>  -<br> | <br>  -<br> | <br>  -<br> | <b> </b>   | <b></b>  | <br>  -<br> | 3          |

| DIV         | <br>  2<br> | D ← (D, D + 2)/A, D + 2 ← remainder                   | <br>  -<br> | <br>  -<br> | -           | <br>       | <b>†</b> | <br>  -<br> |            |

| DIVB        | 2           | D ← (D, D + 1)/A, D + 1 ← remainder                   | -<br>  -    | <br>  -<br> | -           | 1          | 1        | <br>  -<br> | ]<br> <br> |

| AND/ANDB    | 2           | ID 			 □ D and A                                      | 1           | 1           | 10          | 10         | -        | -           |            |

| AND/ANDB    | 3           | ID ← B and A                                          | 1           | 1           | 10          | 10         | T -      | -           |            |

| OR/ORB      | 2           | <br> D <b>←</b> D or A                                | 1           | 1           | 0           | 10         | -        | -           |            |

| XOR/XORB    | 2           | <br> D <b>←</b> D (excl. or) A                        | V           | <b>V</b>    | 10          | 10         | -        | -           |            |

| <br> LD/LDB | 2           | ID <b>←</b> A                                         | -           | -           | <u> </u>    | T -        | <u> </u> | <br>  -     |            |

| <br> ST/STB | 2           | A <b>←</b> D                                          | -           | -           | -           | -          | -        | -           |            |

| <br> LDBSE  | 2           | D ← A; D + 1 ← SIGN(A)                                | -           | -           | -           | -          | <br> -   |             | 3,4        |

| <br> LDBZE  | 2           | <br> D <b>←</b> A; D + 1 <b>←</b> 0                   | -           | -           | -           | -          | -        | -           | 3,4        |

FIGURE 4. Instruction summary.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                | 5962-86809      |

|------------------------------------------------------|-----------|----------------|-----------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | <b>SHEET</b> 19 |

± U. S. GOVERNMENT PRINTING OFFICE 1988—550-547

| Mnemonic         | <br> Oper- | Operation (Note 1)                 |          | <del></del> -, | Fla      | ıgs          |                     | <br>         | Notes        |

|------------------|------------|------------------------------------|----------|----------------|----------|--------------|---------------------|--------------|--------------|

| <del></del>      | ands       |                                    | Z        | N.             | С        | V            | VT                  | ST           |              |

| JNV              | 1          | Jump if V = O                      | -        | _              | -        |              | -                   | _            | 5            |

| JVT              | 1          | Jump if VT = 1; Clear VT           | -        | -              | -        | -            | 0                   | -            | 5            |

| JNVT             | 1          | <br> Jump if VT = O; Clear VT      | _        | -              | -        | -            | 0                   | _            | 5            |

| JST              | 1          | Jump if ST = 1                     | l<br>  - | <br>  -        | _        | _            |                     | _            | 5            |

| JNST             | 1          | <br> Jump if ST = 0                | <br>  -  | <br>  -        |          | -            | -                   | -            | 5            |

| JBS              | 3          | <br> Jump if Specified Bit = 1     | <br>  -  | <br>  -        | <br>  -  | !<br>  -     | -                   | -            | 5,6          |

| JBC              | 3          | <br> Jump if Specified Bit = 0     | <br>  -  | <br>  -        | !<br>  - | <br>         | _                   | -            | 5,6          |

| DJNZ             | 1 1        | <br> D                             | -        |                | -        | <br> <br>  - | <br> <br>  <u>-</u> |              | <br> <br>  5 |

| DEC/DECB         | 1          | D ← D - 1                          | V        | <b>V</b>       | \<br> \  | <b>V</b>     | <b></b>             | -            |              |

| NEG/NEGB         | 1          | D <b> </b>                         | <b>V</b> | \<br> \        | <b>V</b> | <b>V</b>     | <b></b>             | <br>  -      |              |

| INC/INCB         | 1          | D <b>←</b> − D + 1                 | V        | V              | <b>V</b> | V            | <b>↑</b>            | ]<br>  _     |              |

| EXT              | 1 1        | <br> D                             | <b>V</b> | <b>V</b>       | 0        | 0            | !<br>  -            | <br> -       | 2            |

| ЕХТВ             | 1          | D ← D; D + 1 ← Sign (D)            | V        | <b> </b> √     | l<br>l 0 | <br>  0      | <br>  _             | <br>  -      | 3            |

| NOT/NOTB         | 1 1        | <br> D <b>∢</b> — Logical Not (D)  | <b>V</b> | V              | 0        | l<br>  0     | -                   | -            |              |

| CLR/CLRB         | 1          | <br> D <b>←</b> 0                  | 1        | 0              | 0        | 0            | -                   | -            | ]            |

| SHL/SHLB/SHLL    | 2          | <br> C ← msb Isb ← O               | \        | ?              | 1        | 1            | 1                   | <br>  -      | 7            |

| SHR/SHRB/SHRL    | 2          | <br> 0 → msb Isb → C               | 1        | ?              | 1        | 0            | -                   | 1            | 7            |

| SHRA/SHRAB/SHRAL | 2          | <br> msb→ msb                      | <b>V</b> | <b>V</b>       | 1        | 10           | -                   | V            | 7            |

| SETC             | 0          | C <b>←</b> 1                       | -        | -              | 1        | -            | -                   | <br>  -      |              |

| CLRC             | 0          | c <b>←</b> 0                       | -        | -              | 0        | -            | -                   | -            |              |

| CLRVT            | 1 0        | <br> VT <b>←</b> 0                 | -        | -              | <br>  -  | -            | 0                   | -            |              |

| RST              | 0          | <br> PC <b>←</b> 2080H             | 10       | 1 0            | 0        | 10           | 1 0                 | 10           | 8            |

| DI               | 0          | <br> Disable all interrupts (I← O) | -        | -              | T -      | -            | -                   | <del> </del> |              |

| EI               | 0          | <br> Enable all interrupts (I ← 1) |          | T _            | _        | T _          |                     |              |              |

FIGURE 4. <u>Instruction summary</u> - Continued.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br><b>A</b> |               |      | 5962-86809 |    |

|------------------------------------------------------|------------------|---------------|------|------------|----|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVI | EL . | SHEET      | 20 |

± U. S. GOVERNMENT PRINTING OFFICE: 1988—550-547

| Mnemonic        | Oper- | Operation (Note 1)                                          |             |                | Fla         | igs            | ,               |             | Notes       |

|-----------------|-------|-------------------------------------------------------------|-------------|----------------|-------------|----------------|-----------------|-------------|-------------|

|                 | ands  |                                                             | Z           | N              | C           | V              | VT              | ST          |             |

| PUSH            | 1 1   | SP← SP - 2; (SP)← A                                         | -           | _              | -           | -              | -               | -           |             |

| POP             | 1     | <br> A <b>←</b> (SP); SP <b>←</b> SP + 2                    | -           | -              | <br>  -     | <br>  -        | <br> -          | -           |             |

| PUSHF           |       | <br> SP ← SP - 2; (SP) ← PSW;<br> PSW ← 0000H I ← 0         | <br>  0<br> | <br>  0<br>    | <br>  0<br> | <br>  0<br>    | <br>  0<br>     | <br>  0<br> |             |

| POPF            | 0     | <br> PSW <b>←-</b> (SP); SP <b>←-</b> SP + 2; I <b>←-</b> √ | <br> √      | <br>  <b> </b> | <b>V</b>    | <b>V</b>       | <b>V</b>        | <b>V</b>    |             |

| SJMP            | 1     | l<br> PC <b>←</b> PC + 11-bit offset                        | <br>  _     | <br>  -        | (<br>  _    | <br>  <u>-</u> | <br>  -         | <br>  -     | <br> 5      |

| LJMP            | 1     | <br> PC ← PC + 16-bit offset                                | <br>  -     | -              | <br>  -     | <br>  -        | <u> </u><br>  - | <br>  -     | 5           |

| BR (indirect)   | 1 1   | PC <b>←</b> (A)                                             | <br>  -     | <br>  -        | <br>  -     | <br>  -        | <br>  -         | <br>  -     |             |

| SCALL           | 1     | <br> SP                                                     | <br>  -<br> | -              | -           | <br>           | !<br> <br>      | <br> -<br>  | <br>  5<br> |

| LCALL           | 1     | <br> SP ← SP - 2; (SP) ← PC;<br> PC ← PC + 16-bit offset    | <br>  -<br> | <br>  -<br>    | <br>  -<br> | <br> <br>      |                 | <br>  -<br> | <br>  5<br> |

| RET             | 0     | <br> PC <b>←</b> (SP); SP <b>←</b> SP + 2                   | <br> -      | <br>  -        | <br> -      | -              | -               | <br>  _     | 1           |

| J (conditional) | 1     | <br> PC                                                     | <br>  -<br> | <br>  -<br>    | <br>  -<br> | <br> -<br>     | -               | <br>  -<br> | <br>  5<br> |

| JC              | 1     | <br> Jump if C = 1                                          | -           | -              | _           | <u> </u>       |                 | !<br>! -    | 5           |

| JNC             | 1 1   | <br> Jump if C = O                                          | -           | -              | <br> -      | <br>  -        | -               | l<br>  -    | 5           |

| JE              | 1     | <br> Jump if Z = 1                                          | -           | -              | -           | -              | -               | -           | 5           |

| JNE             | 1 1   | <br> Jump if Z ≈ O                                          | -           | <br>  -        | -           | -              | -               | <br>  -     | 5           |

| JGE             | 1 1   | <br> Jump if N = O                                          | _           | -              | -           | -              | <br>  -         | -           | 5           |

| JLT             | 1     | <br> Jump if N = 1                                          | T -         | -              | -           | -              | -               | -           | 5           |

| JGT             | 1     | Jump if $N = 0$ and $Z = 0$                                 | <u> </u>    |                |             | <u> </u>       | -               | -           | T<br>  5    |

| JLE             | 1     | <br> Jump if N = 1 or Z = 1                                 | -           | -              | <br> -      | -              | -               | -           | 5           |

| JH              | 1     | Jump if $C = 1$ and $Z = 0$                                 | -           | -              | -           | -              | -               | -           | 5           |

| JNH             | 1     | Jump if C = O or Z = 1                                      | -           | -              | -           | -              | -               | -           | 5           |

| J <b>V</b>      | 1     | <br> Jump if V = 1                                          | -           | -              | -           | -              | -               | -           | 5           |

FIGURE 4. <u>Instruction summary</u> - Continued.

| STANDARDIZED MILITARY DRAWING                           | SIZE<br><b>A</b> |       |            | 5962-86809 |  |  |

|---------------------------------------------------------|------------------|-------|------------|------------|--|--|

| DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 |                  | REVIS | SION LEVEL | SHEET 21   |  |  |

± U S. GOVERNMENT PRINTING OFFICE: 1988-550-547

| Mnemonic | l<br> Oper-<br> ands | Operation (Note 1)                                        | 1   | Notes    |             |             |         |    |       |

|----------|----------------------|-----------------------------------------------------------|-----|----------|-------------|-------------|---------|----|-------|

|          | lands                | <br>                                                      | l Z | N        | C           | V           | VT      | ST | Notes |

| NOP      | 0                    | PC ← PC + 1                                               | -   | <br>  -  | -           | <u> </u>    | -       | _  |       |

| SKIP     | 0                    | <br> PC                                                   |     | -        | <u> </u>    | <br>  -     | <br>  - | -  |       |

| NORML    | 2                    | <br> Left shift till msb = 1;<br> D <b>∢—</b> shift count | /   | <b> </b> | <br>  0<br> | <br>  -<br> | -       | •  | 7     |

| TRAP     | 0                    | <br> SP                                                   | -   | -        | -           | <br>  -     | -       | -  | 9     |

If the mnemonic ends in "B", a byte operation is performed, otherwise a word operation is done. Operands D, B, and A must conform to the alignment rules for the required operand type. D and B are locations in the Register File; A can be located anywhere in memory. D, D + 2 are consecutive WORDS in memory; D is DOUBLE-WORD aligned. D, D + 1 are consecutive BYTES in memory; D is WORD aligned.

Changes a byte to a word.

Offset is a 2's complement number.

Specified bit is one of the 2048 bits in the register file.

The "L" (Long) suffix indicates double-word operation.

Initiates a Reset by pulling RESET low. Software should re-initialize all the necessary registers with code starting at 2080H.

9. The assembler will not accept this mnemonic.

FIGURE 4. Instruction summary - Continued.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                    | 5962-86809 |  |

|------------------------------------------------------|-----------|--------------------|------------|--|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | <br>REVISION LEVEL | SHEET 22   |  |

DESC FORM 193A SEP 87

**☆** U. S. GOVERNMENT PRINTING OFFICE: 1988--550-547

± U. S. GOVERNMENT PRINTING OFFICE: 1988—550-547

Powered by ICminer.com Electronic-Library Service CopyRight 2003

± U. S. GOVERNMENT PRINTING OFFICE: 1988-550-547

External clock drive waveforms

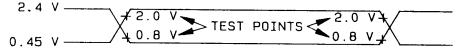

A.C. testing input, output waveform

A. C. TESTING INPUTS ARE DRIVEN AT 2.4 V FOR A LOGIC "1" AND 0.45 V FOR A LOGIC "0". TIMING MEASUREMENTS ARE MADE AT 2.0 V FOR A LOGIC "1" AND 0.8 V FOR A LOGIC"0".

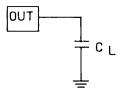

Float waveform

FOR TIMING PURPOSES A PORT PIN IS NO LONGER FLOATING WHEN A 100 mV CHANGE FROM LOAD VOLTAGE OCCURS, AND BEGINS TO FLOAT WHEN A 100 mV CHANGE FROM THE LOADED  $\rm V_{OH}/\rm V_{OL}$  LEVEL OCCURS  $\rm I_{OH}/\rm I_{OL} \geq \pm 15$  mA.

Output load circuit

C | = 80pf UNLESS OTHERWISE SPECIFIED.

FIGURE 5. Switching test circuit and waveforms - Continued.

DESC FORM 193A SEP 87

± U. S. GOVERNMENT PRINTING OFFICE: 1988—550-547

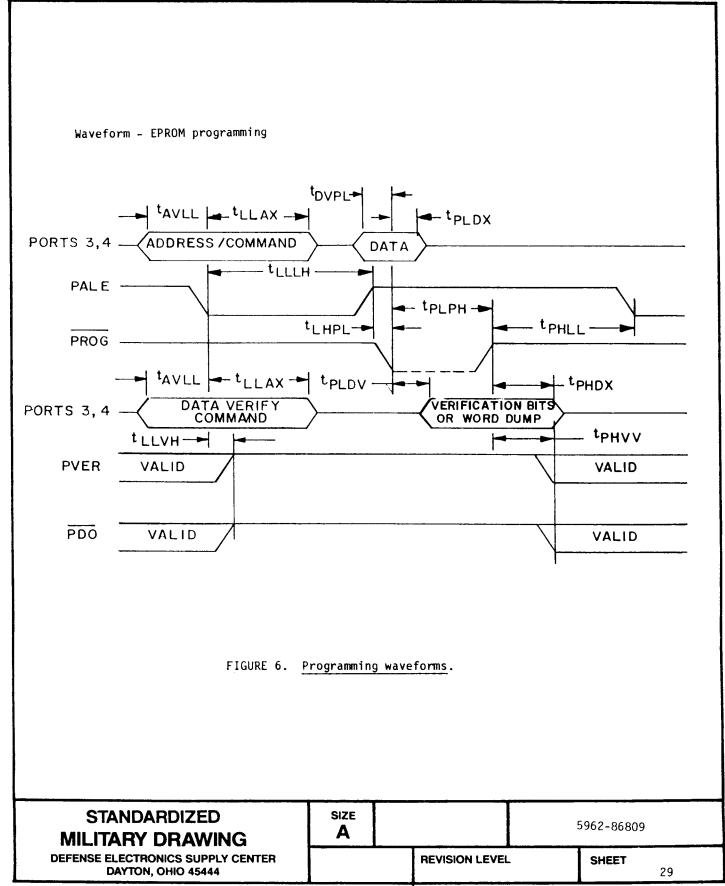

- 3.9 <u>Processing EPROMS</u>. All testing requirements and quality assurance provisions herein shall be satisfied by the manufacturer prior to delivery.

- 3.9.1 Erasure of EPROMS. When specified, devices shall be erased in accordance with the procedures and characteristics specified in 4.4.

- 3.9.2 Programmability of EPROMS. When specified, devices shall be programmed to the specified pattern using the procedures and characteristics specified in 4.5 and table III.

- 3.9.3 Verification of erasure of programmability of EPROMS. When specified, devices shall be verified as either programmed to the specified pattern or erased. As a minimum, verification shall consist of performing a functional test (subgroup 7) to verify that all bits are in the proper state. Any bit that does not verify to be in the proper state shall constitute a device failure, and shall be removed from the lot.

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 <u>Sampling and inspection</u>. Sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein).

- 4.2 <u>Screening.</u> Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.