## 2 MBIT PCM SIGNALLING CIRCUIT MJ 1440 HDB3 ENCODER/DECODER

The 2.048 MBit PCM Signalling Circuits comprise a group of circuits which will perform the common signalling and error detection functions for a 2.048 MBit PCM transmission link operating to the appropriate CCITT recommendations. The circuits are fabricated in N-channel metal gate MOS and operate from a single 5 volt supply, relevant inputs and outputs are TTL compatible.

The MJ1440 is an encoder/decoder for the pseudoternary transmission code, HDB3 (CCITT Orange Book Vol III.2 Annex to Rec. G703). The device encodes and decodes simultaneously and asynchronously. Error monitoring functions are provided to detect violations of HDB3 coding, all ones detection and loss of input (all zeroes detection). In addition a loop back function is provided for terminal testing.

###

Fig. 1 Pin connections

### **FEATURES**

- $\blacksquare$  5v  $\pm$  5% Supply -50 mA Max

- HDB3 Encoding and Decoding to CCITT rec. G703

- Asynchronous Operation.

- Simultaneous Encoding and Decoding.

- Clock Recovery Signal Generated from Incoming HDB3 Data.

- Loop Back Control.

- HDB3 Error Monitor

- All Ones' Error Monitor

- Loss of Input Alarm (All Zeros Detector).

- Decode Data in NRZ Form.

# NRZ DATA IN O CLOCK CLOCK (ENCODER) LOOP TEST ENABLE SWITCH BIN CLOCK (DECODER) AIS CINCUIT AIS CINCUIT AIS CINCUIT AIS CINCUIT AIS CINCUIT AIS CINCUIT

Fig. 2 Block diagram

### **ABSOLUTE MAXIMUM RATINGS**

The absolute maximum ratings are limiting values above which operating life may be shortened or specified parameters may be degraded.

### **Electrical Ratings**

+Vcc Inputs 7V

Vcc + 0.5V Gnd - 0.3V

Outputs

Vcc, Gnd -0.3V

### Thermal Ratings

Max Junction Temperature 175°C Thermal Resistance: Chip to Case 40°C/Watt

Chip to Amb. 120°C/Watt

### **ELECTRICAL CHARACTERISTICS**

### Test conditions (unless otherwise stated):

Supply voltage,  $V_{CC} = 5V \pm 0.25V$ Ambient temperature,  $T_{amb} = 0^{\circ}C$  to +70°C

### Static characteristics

| Characteristic                                                                                                               | Symbol                                                                          | Pins                                                                         |                          | Value |                                           | Units                             | Conditions                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------|-------|-------------------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                              |                                                                                 |                                                                              | Min                      | Тур   | Max                                       |                                   |                                                                                                                                   |

| Low level input voltage                                                                                                      | V <sub>IL</sub>                                                                 | )                                                                            | -0.3                     |       | 8.0                                       | ٧                                 |                                                                                                                                   |

| Low level input current High level input voltage High level input current Low level output voltage High level output voltage | I <sub>IL</sub> V <sub>IH</sub> I <sub>IH</sub> V <sub>OL</sub> V <sub>OH</sub> | 1,2,5,6<br>10,11,12,13<br>)<br>10,14,15<br>3,4,7,9<br>3,4,7,9<br>14,15<br>10 | 2.5<br>2.7<br>2.8<br>2.8 | 20    | 50<br>V <sub>cc</sub><br>50<br>0.5<br>0.4 | µА<br>V<br>µA<br>V<br>V<br>V<br>V | V <sub>IL</sub> = 0V  V <sub>IH</sub> = 5V Isink = 80µA Isink = 1.6mA Isource = 60µA Isource = 2mA Isource = 1mA All inputs to 0V |

### **Dynamic Characteristics**

| Characteristic                                                       |      | Value |      |      | Units |                                       |  |

|----------------------------------------------------------------------|------|-------|------|------|-------|---------------------------------------|--|

|                                                                      |      | Min.  | Тур. | Max. | Units | Conditions                            |  |

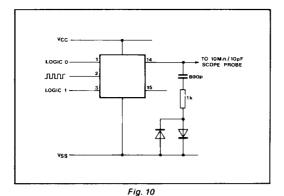

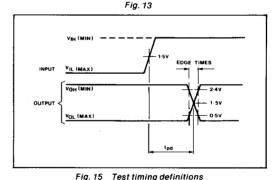

| Max. Clock (Encoder) frequency                                       |      | 4.0   |      |      | MHz   | Figs.10, 15                           |  |

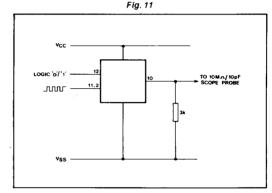

| Max. Clock (Decoder) frequency                                       |      | 2.2   |      |      | MHz   | Figs.11, 15                           |  |

| Propagation delay Clock (Encoder) to O <sub>1</sub> , O <sub>2</sub> |      |       |      | 100  | ns    | Figs.10, 15. See Note 1               |  |

| Rise and Fall times $O_1$ , $O_2$                                    |      |       |      | 20   | ns    | Figs.10, 15                           |  |

| tpd1A-tpd1B                                                          |      |       |      | 20   | ns    | Figs.10, 15                           |  |

| Propagation delay Clock (Encoder) to Clock                           | tpd3 |       |      | 150  | ns    | Loop test enable = Figs.13, 15        |  |

| Setup time of NRZ data in to Clock (Encoder)                         |      | 30    |      |      | ns    | Figs.8, 10, 15                        |  |

| Hold time of NRZ data in                                             | th3  | 55    |      |      | ns    | Figs.10, 15                           |  |

| Propagation delay A <sub>in</sub> , B <sub>in</sub> to Clock         |      |       |      | 150  | ns    | Loop test enable = '0' Figs.9, 13, 15 |  |

| Propagation delay Clock (Decoder) to loss of input                   |      |       |      | 150  | ns    |                                       |  |

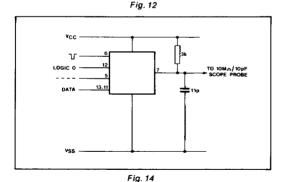

| Propagation delay Clock (Decoder) to error                           | tpd4 |       |      | 200  | ns    | Figs.12, 15                           |  |

| Propagation delay Reset AIS to AIS                                   |      |       |      | 200  | ns    | Loop test enable = '0' Figs.14, 15    |  |

| Propagation delay Clock (Decoder) to NRZ data out                    | tpd6 |       |      | 150  | ns    | Figs.9, 11, 15. See Note 2            |  |

| Setup time of A <sub>in</sub> , B <sub>in</sub> to Clock (Decoder)   | ts1  | 75    |      |      | ns    | Figs.9, 11, 15                        |  |

| Hold time of A <sub>in</sub> , B <sub>in</sub> to Clock (Decoder)    | th1  | 5     |      |      | ns    | Figs.9, 11, 15                        |  |

| Hold time of Reset AIS = '0'                                         |      | 100   |      |      | ns    | Figs.9, 14, 15                        |  |

| Setup time Clock (Decoder) to Reset AIS                              | ts2  | 200   |      |      | ns    | Figs.9, 14, 15                        |  |

| Setup time Reset AIS = 1 to Clock (Decoder)                          | ts2′ | 0     |      |      | ns    | Figs.14, 15                           |  |

### NOTES

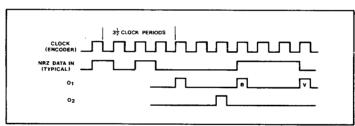

Encoded HDB3 outputs (O<sub>1</sub>, O<sub>2</sub>) are delayed by 3½ clock periods from NRZ data in (Fig.3).

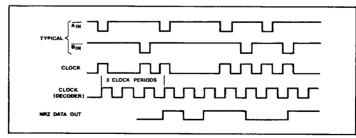

The decoded NRZ output is delayed by 3 clock periods from the HDB3 inputs (AIN, BIN) (Fig.4).

### **FUNCTIONAL DESCRIPTION**

### **Functions Listed by Pin Number**

### 1. NRZ data in

Input data for encoding into ternary HDB3 form. The NRZ data is clocked by the negative edge of the Clock (Encoder).

### 2. Clock (Encoder)

Clock for encoding data on pin 1.

### 3. Loss of input alarm

This output goes to logic '1' if eleven consecutive zeroes are detected in the incoming HDB3 data. The output is set to logic '0' on receipt of a '1'.

### 4. NRZ data out

Decoded data in NRZ form from ternary HDB3 input data (A<sub>in</sub>, B<sub>in</sub>), data is clocked out by positive going edge of clock (Decoder).

### 5. Clock (Decoder)

Clock for decoding ternary data Ain, Bin.

### 6. Reset AIS, AIS

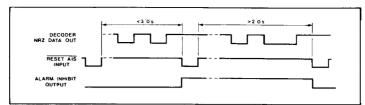

Logic '0' on Reset AIS resets a decoded zero counter and either resets AIS outputs to zero provided 3 or more zeroes have been decoded in the preceding Reset AIS = 1 period or sets AIS to '1' if less than 3 zeroes have been decoded in the preceding two Reset AIS = 1 periods.

Logic '1' on Reset AIS enables the internal decoded zero counter.

### 8. Ground

Zero volts

### 9. Error

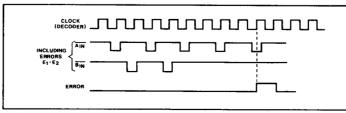

A logic '1' indicates that a violation of the HDB3 coding has been received i.e. 3 '1's of the same polarity.

'OR' function of Air, Bi for clock regeneration when pin 12 = 0, 'OR' function of O, O, when pin 12 = 1.

## 11,13. A<sub>in</sub>, B<sub>in</sub>

Inputs representing the received ternary HDB3 PCM signal.  $\overline{A}_{in} = '0'$  represents a positive going '1',  $\overline{B}_{in} = '0'$ represents a negative going '1'. An and Bn are sampled by the positive going edge of the Clock (Decoder). A and B may be interchanged.

### 12. Loop test enable

Input to select normal or loop back operation. Pin 12 = '0' selects normal operation, encode and decode are independent and asynchronous. When pin 12 = '1' O, is connected internally to  $A_{\rm in}$ ,  $O_2$  is connected to  $B_{\rm in}$ . Clock becomes the OR function  $O_1+O_2$ . The delay from NRZ in to NRZ out is 6% clock periods in the loop back condition.

### 14,15. O, O2

Outputs representing the ternary encoded data for line transmission O<sub>1</sub> = '1' representing a positive going '1', O<sub>a</sub> = '1' represents a negative going '1'. O<sub>a</sub> and O<sub>a</sub> may be interchanged.

16. V<sub>cc</sub> Positive supply, 5V ± 5%.

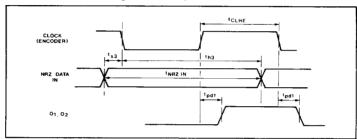

Fig. 3 Encode waveforms

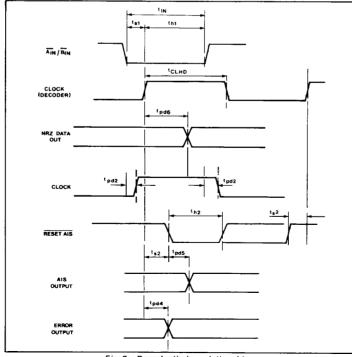

Fig. 4 Decode waveforms

Fig. 5 HDB3 error output waveforms

Fig. 6 AIS error and reset waveforms

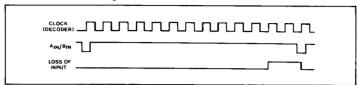

Fig. 7 Loss of input waveforms

Fig. 8 Encoder timing relationship

Fig. 9 Decoder timing relationship

VCC

111

13

13

5

LOGIC 0

12

11p

VSS

**DEFINITION OF THE HDB3 CODE**

Coding of a binary signal into an HDB3 signal is done according to the following rules:

- 1. The HDB3 signal is psuedo-ternary; the three states are denoted  $B_+,\,B_-$  and O.

- 2. Spaces in the binary signal are coded as spaces in the HDB3 signal. For strings of four spaces however, special rules apply (see 4. below).

- 3. Marks in the binary signal are coded alternately as B, and B\_in the HDB3 signal (alternate mark inversion). Violations of the rule of alternate mark inversion are introduced when coding strings of four spaces (see 4. below).

- 4. Strings of four spaces in the binary signal are coded according to the following rules:

- a The first space of a string is coded as a space if the

rig. 10 rest inning deminions

preceding mark of the HDB3 signal has a polarity opposite to the polarity of the preceding violation and is not a violation by itself; it is coded as a mark, i.e. not a violation (i.e.  $B_+$ ,  $B_-$ ), if the preceding mark of the HDB3 signal has the same polarity as that of the preceding violation or is by itself a violation.

This rule ensures that successive violations are of alternative polarity so that no DC component is introduced.

- **b** The second and third spaces of a string are always coded as spaces.

- c The last space of a string of four is always coded as a mark, the polarity of which is such that it it violates the rule of alternate mark inversion. Such violations are denoted V<sub>2</sub> or V<sub>2</sub> according to their polarity.