# microelectronics group

# **ATT1700A Series Serial ROMs**

#### **Features**

- 32K, 64K, and 128K x 1 Serial ROMs for configuration of ATT3000 and ORCA Series FPGAs

- Pinout and functional replacement of Xilinx XC1700 series

- Simple 4-wire interface

- Cascadable to support large FPGAs, multiple configurations, and multiple FPGAs

- 8-pin, plastic DIP; 8-pin SOIC; and 20-pin PLCC packages

- Programming support from leading programmer manufacturers

- Programmable polarity on RESET/OE pin

- Full static operation

- Standby current—100 µA typical

- Operating current—10 mA maximum

- 10 MHz maximum clock rate

- Electrostatic discharge protection: >4000 V

- Temperature ranges: Commercial: 0 °C to 70 °C Industrial: -40 °C to +85 °C

## Description

The ATT1700A Series Serial ROM family provides easy-to-use, cost-effective, nonvolatile memory for configuring ATT3000 and *ORCA* Series FPGAs. The ATT1700A Series consists of one-time programmable (OTP) devices. The ATT1700A devices are available in 8-pin, plastic DIP, 8-pin SOIC, and 20-pin PLCC packages.

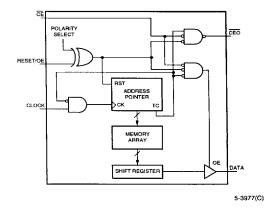

The ATT1700A Series is a pinout and functional replacement for the ATT1700 and Xilinx XC1700 families (see Figure 1) and can be programmed by most commercially available programmers. FPGA development tools, such as ORCA Foundry, generate configuration files in Intel, Motorola, and Tektronix formats for use in programmers.

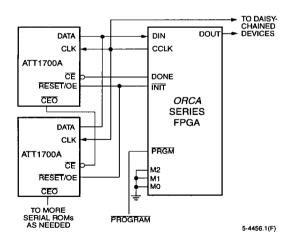

The ATT1700A Series is most often used when the ATT3000 Series and *ORCA* Series FPGAs are configured in the master serial mode. The primary advantage of this configuration mode is that it provides a simple, four-wire interface between the FPGA and serial ROM (see Figure 2).

Figure 1. Block Diagram

Lucent Technologies Inc.

2-371

I 0050026 0021760 41T 🎟

## **Pin Information**

**Table 1. Pin Descriptions**

| Symbol Pin |       | umbers | 1/0 | F                                                                                                                                                                                                                                                                                                                                                                                               |  |

|------------|-------|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Symbol     | 8-Pin | 20-Pin | 1/0 | Function                                                                                                                                                                                                                                                                                                                                                                                        |  |

| DATA       | 1     | 2      | 0   | DATA output from the serial ROM to FPGA synchronous with the CLOCK input. DATA is 3-stated when either CE or OE is inactive.                                                                                                                                                                                                                                                                    |  |

| CLOCK      | 2     | 4      | i   | CLOCK is an input used to increment the address pointer which strobes data out of the DATA pin.                                                                                                                                                                                                                                                                                                 |  |

| RESET/OE   | 3     | 6      | I   | RESET/OUTPUT ENABLE is a dual-function pin used to reset and enable the ATT1700A Series device. An active level on both CE and OE inputs enables data out of the DATA pin. An active level on RESET resets the address pointer. When the serial ROM is programmed, the polarity of RESET/OE is set either with RESET active-high and OE active-low or with RESET active-low and OE active-high. |  |

| CE         | 4     | 8      | ı   | CHIP ENABLE is an input used to select the device. An active level on both CE and OE enables data out of the device. A high on CE disables the address pointer and forces the serial ROM into a low-power mode.                                                                                                                                                                                 |  |

| Vss        | 5     | 10     | 1   | Ground.                                                                                                                                                                                                                                                                                                                                                                                         |  |

| CEO        | 6     | 14     | 0   | CHIP ENABLE OUT is asserted low on the clock cycle following the last bit read from the device. CEO remains low as long as CE and OE are both active.                                                                                                                                                                                                                                           |  |

| VPP        | 7     | 17     | I   | VPP is an input used by programmers when programming the serial ROM. The programming operations, voltages, and timing are defined later in this data sheet. For read operations, VPP must be tied directly to VDD.                                                                                                                                                                              |  |

| VDD        | 8     | 20     | ı   | Power supply.                                                                                                                                                                                                                                                                                                                                                                                   |  |

2-372

Lucent Technologies Inc.

#### **FPGA Configuration**

The functionality of Lucent Technologies Microelectronics Groups' FPGAs is determined by the contents of the FPGA's configuration memory. The configuration memory is loaded either automatically at powerup or with a configuration command by pulsing the PRGM pin low. The FPGAs can be programmed in a variety of modes, and the mode used is determined by the inputs into the FPGA's M[2:0] pins. The configuration modes allow the FPGA to act as a master or a slave and also allow configuration data to be transmitted either serially or in parallel. The ATT1700A Series ROMS are targeted for use when the FPGA is configured serially, primarily in the master serial mode. Table 2 provides the configuration memory requirements for Lucent's FPGAs.

## **FPGA Master Serial Configuration Mode**

The master serial mode provides a simple interface between the FPGA and the serial ROM. Four interface lines, DATA, CLOCK, CE, and RESET/OE, are required to configure the FPGA. Upon powerup or a configure command (PRGM in ORCA, PROG in ATT3000), when the FPGA's M[2:0] pins are low, the FPGA configures using the master serial mode. The configuration data is transmitted serially into the FPGA's DIN pin from the serial ROM's DATA pin. To synchronize the data, the FPGA's CCLK output is routed into the serial ROM's CLOCK input.

Because the FPGA DIN signal may be unused after FPGA configuration, it is necessary to avoid an unresolved state once the serial ROM has finished sending configuration data. If this pin is used only for the configuration process, it should be configured so that it does not float. This can be accomplished by programming it as an output during normal operation or by programming it as an input with an internal pull-up resistor enabled. CCLK must also be pulled up following configuration.

Signal contention on the DIN pin must be avoided if it is to be used for a user I/O signal after configuration. To avoid contention, the FPGA DONE signal may be programmed (selected in ORCA Foundry) to go high prior to the FPGA I/O signals being enabled. An alternative is to use the FPGA's LDC to drive the serial ROM's CE pin, rather than DONE, and configure LDC to output a constant logic 1 high-voltage level after configuration. Control of the serial ROM's CE and RESET/OE pins varies, depending upon the FPGA series being used, and is described in subsequent sections.

**Table 2. Configuration Requirements**

| Lucent FPGA             | Memory<br>Requirements |

|-------------------------|------------------------|

| ATT3020                 | 14,819                 |

| ATT3030                 | 22,216                 |

| ATT3042                 | 30,824                 |

| ATT3064                 | 46,104                 |

| ATT3090                 | 64,200                 |

| ATT1C03                 | 57,144                 |

| ATT1C05                 | 76,376                 |

| ATT1C07                 | 98,296                 |

| ATT1C09                 | 122,904                |

| ATT2C04/OR2C04A/OR2T04A | 65,424                 |

| ATT2C06/OR2C06A/OR2T06A | 91,024                 |

| ATT2C08/OR2C08A/OR2T08A | 115,600                |

| ATT2C10/OR2C10A/OR2T10A | 148,944                |

| ATT2C12/OR2C12A/OR2T12A | 179,856                |

| ATT2C15/OR2C15A/OR2T15A | 220,944                |

| ATT2C26/OR2C26A/OR2T26A | 307,024                |

| ATT2C40/OR2C40A/OR2T40A | 474,176                |

The FPGA serial ROM interface used also depends upon the system and configuration requirements. The following are some typical system requirements:

- Configuring an FPGA at powerup

- Configuring an FPGA in response to a configure command

- One serial ROM configures an FPGA with multiple configuration programs

- Cascaded serial ROMs configure daisy-chained FPGAs

In addition to the clock and data lines, the FPGA pins used in configuration/startup are RESET, DONE, PRGM, LDC, HDC, and INIT. Normally, only a small subset of these pins is used to control the serial ROM's CE and RESET/OE pins. In some applications, the RESET/OE signal is generated by the system host, not the FPGA. For example, the host may generate a system reset, allowing the FPGA and the serial ROM to be reset synchronously.

Lucent Technologies Inc.

2-373

### FPGA Configuration (continued)

#### ATT3000 Series/ORCA Series Differences

While both the ATT3000 and ORCA Series have RESET, LDC, HDC, INIT, DIN, CCLK, and DOUT pins, there are some configuration differences in the FPGAs. The ATT3000 Series DONE/PROG pin is a shared open-drain I/O, while the ORCA Series has discrete DONE and PRGM pins. When the system generates a configure command to the ATT3000, the DONE/PROG pin is held low throughout the configuration cycle. For the ORCA Series, the PRGM pin is pulsed low and returned high to initiate configuration. A second difference is the internal pull-ups on the mode select pins. For the ATT3000 Series, only M2 has an internal pull-up during configuration, but for the ORCA Series, M[3:0] have pull-ups.

#### Configuring the FPGA at Powerup

The ATT1700A series can configure FPGAs at powerup. There is level-sensitive, power-on-reset circuitry included in the device that resets the address pointer during powerup. The ATT3000 and ORCA FPGAs enable the serial ROM using either the DONE (or LDC) and INIT pins. If these signals are low at powerup and they are connected to the CE and RESET/OE pins on the serial ROM, the FPGA is programmed from the serial ROM (see Figures 2 and 3). When these FPGA signals go high at the end of configuration, the serial ROM is disabled.

Figure 2. ORCA Master Serial Configuration

# Configuring the ORCA Series FPGA with a Configure Command

The FPGA needs to enable the serial ROM's RESET/OE and  $\overline{\text{CE}}$  inputs. The polarity of the RESET/OE input is programmable in the ATT1700A series. In the method shown in Figure 2, the system generates an active-low configure pulse to the FPGA's PRGM pin. This configuration pulse causes the FPGA to drive its  $\overline{\text{INIT}}$  pin low, which forces a RESET on the serial ROM RESET/OE pin (with the RESET/OE pin programmed for active-low RESET and active-high OE). The FPGA's DONE pin is routed to the serial ROM's  $\overline{\text{CE}}$  pin. At the end of configuration, DONE returns high, disabling the serial ROM. Alternatively, the  $\overline{\text{LDC}}$  pin can be used instead of the DONE pin to enable the serial ROM.

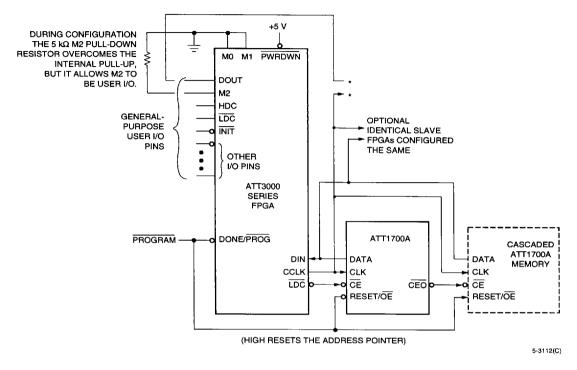

# Configuring the ATT3000 Series FPGA with a Configure Command

In the method illustrated in Figure 3, the system generates an active-low configure pulse on the FPGA's DONE/PROG pin. The system then releases the opendrain DONE/PROG pin, allowing the FPGA to control it and drive it low during configuration. DONE/PROG is generally connected to both the CE and RESET/OE pins of the serial ROM, which has been programmed so that RESET is active-high and OE is active-low. At the end of configuration, the DONE/PROG pin returns high, disabling and resetting the serial ROM. The LDC pin may be used instead of the DONE/PROG pin to enable the serial ROM, as shown.

Lucent Technologies Inc.

2-374

■ 0050026 0021763 129 ■

## FPGA Configuration (continued)

Figure 3. ATT3000 Master Serial Configuration

# Programming the FPGA with the Address Pointer Unchanged Upon Completion

In the two interfaces previously discussed, the serial ROM is reset at the completion of configuration. This is typically the case when one or more serial ROMs are used to configure one or more FPGAs with one configuration program. In applications in which a serial ROM is used to configure an FPGA with multiple configuration programs, the address pointer should not be reset. This allows the next configuration program to be loaded at the next internal ROM address.

When multiple FPGA configurations are stored in a serial ROM, the OE pin of the serial ROM should be tied low. Upon powerup, the internal address pointer is reset and configuration begins with the first set of configuration data stored in memory. Since the OE pin is held low, the address pointer is left unchanged after configuration is complete. To reprogram the FPGA with another program, the DONE/PROG or PRGM pin is pulled low, and configuration begins at the last value of the address pointer.

Lucent Technologies Inc.

2-375

I 0050026 0021764 065 📟

#### FPGA Configuration (continued)

#### Cascading Serial ROMs

Figure 2 and Figure 3 also illustrate the cascading of serial ROMs. This is done to provide additional memory for large FPGAs and/or for configuring multiple FPGAs in a daisy chain. The serial ROMs are cascaded with the next ROM's CE input connected to the CEO output of the previous serial ROM. All of the cascaded serial ROM's DATA lines are routed to the FPGA's DIN input, and the FPGA's CCLK output is routed in parallel to all of the serial ROMs' CLOCK inputs.

After the last bit from the first serial ROM is read, the first serial ROM asserts CEO low and disables its DATA output. The next serial ROM recognizes the low on its CE input and enables its DATA output. The inactive CE into all serial ROMs causes the inactive DATA pins to be 3-stated after configuration is finished.

The ATT3000 DONE/PROG signal and the ORCA DONE signal are open-drain outputs with optional internal pull-ups and can be used to control the output enable of multiple serial ROMs. Extremely large, cascaded serial memories may require additional logic if the DONE/PROG or DONE signals are too slow to activate many serial ROMs.

#### Standby Mode

The ATT1700A Series enters a low-power standby mode when  $\overline{CE}$  is high. In standby mode, the serial ROM consumes less than 100  $\mu$ A of current. The DATA pin remains in the high-impedance state regardless of the state of the RESET/OE input.

#### **RESET/OE Polarity**

The ATT1700A Series allows the user to select the polarity of the dual-function RESET/OE pin. The PROM programmer software is used to program the desired polarity. The method used to select a polarity depends on the prom programmer user interface.

2-376

Lucent Technologies Inc.

0050026 0021765 TT1 **=**

# **Absolute Maximum Ratings**

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

| Parameter                           | Symbol | Min  | Max       | Unit      |

|-------------------------------------|--------|------|-----------|-----------|

| Supply Voltage Relative to GND      | VDD    | -0.6 | 6.6       |           |

| Programming Voltage Relative to GND | VPP    | -0.6 | 14.0      | V         |

| Input Voltage with Respect to GND   | VIN    | -0.6 | VDD + 0.6 | V         |

| Voltage Applied to 3-state Output   | VTS    | -0.6 | VDD + 0.6 | V         |

| Ambient Storage Temperature         | Tstg   | -65  | 150       | °C        |

| Maximum Soldering Temperature       | Tsol   | _    | 300       | °C        |

| Maximum Junction Temperature        | TJ     | _    | 125       | <u>°C</u> |

#### **Electrical Characteristics**

#### **Table 3. dc Electrical Characteristics**

Commercial: 0 °C  $\leq$  TA  $\leq$  70 °C, VDD = 5.0 V  $\pm$  5%; Industrial: -40 °C  $\leq$  TA  $\leq$  +85 °C, VDD = 5.0 V  $\pm$  10%.

| Parameter                                     | Symbol | Conditions                                                  | Min  | Max       | Unit                     |

|-----------------------------------------------|--------|-------------------------------------------------------------|------|-----------|--------------------------|

| High-level Input Voltage                      | ViH    | _                                                           | 2.0  | VDD       | V                        |

| Low-level Input Voltage                       | VIL    | _                                                           | -0.3 | 0.8       | V                        |

| High-level Output Voltage                     | Voн    | VDD = 3.0 V, IOH = -4.0 mA                                  | 2.40 |           | V                        |

|                                               | Voн    | VDD = 4.5  V, IOH = -4.0  mA                                | 3.86 | 1 —       | V                        |

| Low-level Output Voltage                      | Vol    | VDD = 5.5 V, IOL = 4.0 mA                                   | _    | 0.32      | V                        |

| Supply Voltage Relative to Vss:<br>Commercial | _      | _                                                           | 4.75 | 5.25      | V                        |

| Industrial                                    | _      |                                                             | 4.50 | 5.50      | V                        |

| Standby Supply Current                        | IDDSB  | VIN = VDD = 5.5 V<br>VIN = VDD = 3.6 V                      | _    | 100<br>50 | μ <b>Α</b><br>μ <b>Α</b> |

| Operating Supply Current                      | IDD    | VDD = 5.5 V, Clock = 10 MHz<br>VDD = 3.6 V, Clock = 2.5 MHz |      | 10<br>2   | mA<br>mA                 |

| Input Leakage Current                         | liL    | VDD = 5.5 V,<br>VIN = VDD and 0 V                           | -10  | 10        | μА                       |

| Output Leakage Current                        | liL    | VDD = 5.5 V,<br>VIN = VDD and 0 V                           | -10  | 10        | μА                       |

| Pin Capacitance                               | CIN    | VCC = 5 V, Ta = 25 °C,<br>FCLK = 1 MHz                      | _    | 10        | pF                       |

Lucent Technologies Inc.

2-377

**=** 0050026 0021766 938 **=**

2-378

# **Electrical Characteristics** (continued)

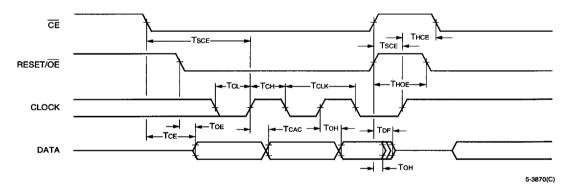

#### **Table 4. ac Characteristics During Read**

Commercial:  $0 \, ^{\circ}\text{C} \le \text{TA} \le 70 \, ^{\circ}\text{C}$ ,  $\text{VDD} = 5.0 \, \text{V} \pm 5\%$ ; Industrial:  $-40 \, ^{\circ}\text{C} \le \text{TA} \le +85 \, ^{\circ}\text{C}$ ,  $\text{VDD} = 5.0 \, \text{V} \pm 10\%$ .

| Parameter                        | Symbol | Test<br>Conditions | $\begin{array}{c} \text{Limits} \\ \text{3.0 V} \leq \text{VDD} \leq \text{6.0 V} \end{array}$ |     | Limits<br>4.5 V ≤ VDD ≤ 6.0 V |     | Unit |

|----------------------------------|--------|--------------------|------------------------------------------------------------------------------------------------|-----|-------------------------------|-----|------|

|                                  |        | Conditions         | Min                                                                                            | Max | Min                           | Max |      |

| OE to Data Delay                 | TOE    | _                  | _                                                                                              | 45  |                               | 45  | ns   |

| CE to Data Delay                 | TCE    | _                  | _                                                                                              | 60  | _                             | 50  | ns   |

| CLOCK to DATA Delay              | TCAC   |                    | _                                                                                              | 200 | _                             | 60  | ns   |

| DATA Hold from CE, OE, or CLOCK  | Тон    | -                  | 0                                                                                              |     | 0                             |     | ns   |

| CE or OE to DATA Float Delay     | TDF    | <del></del>        |                                                                                                | 50  | <del></del>                   | 50  | ns   |

| CLOCK Frequency                  | TCLK   | _                  | _                                                                                              | 2.5 | -                             | 10  | MHz  |

| CLOCK Low Time                   | TCL    |                    | 100                                                                                            |     | 25                            |     | ns   |

| CLOCK High Time                  | Тсн    | _                  | 100                                                                                            | _   | 25                            |     | ns   |

| CE Setup Time to CLOCK           | TSCE   | _                  | 40                                                                                             | _   | 25                            | _   | ns   |

| (Guarantees correct counting.)   |        |                    |                                                                                                |     |                               |     |      |

| CE Hold Time from CLOCK          | THCE   | _                  | 0                                                                                              | _   | 0                             | _   | ns   |

| (Guarantees correct counting.)   |        |                    |                                                                                                |     |                               |     |      |

| OE High Time                     | THOE   | CE high            | 100                                                                                            | _   | 20                            |     | ns   |

| (Guarantees counters are reset.) |        | or low             |                                                                                                |     |                               |     |      |

Figure 4. Read Characteristics

Lucent Technologies Inc.

■ 0050026 0021767 874 ■

#### Table 5. ac Characteristics at End of Read

Commercial: 0 °C  $\leq$  Ta  $\leq$  70 °C, VDD = 5.0 V  $\pm$  5%; Industrial: -40 °C  $\leq$  Ta  $\leq$  +85 °C, VDD = 5.0 V  $\pm$  10%.

| Parameter                   | Symbol |     | Limits<br>/ ≤ VDD ≤ 6.0 V 4.5 |     | Limits<br>4.5 V ≤ VDD ≤ 6.0 V |    |

|-----------------------------|--------|-----|-------------------------------|-----|-------------------------------|----|

|                             |        | Min | Max                           | Min | Max                           |    |

| CLOCK to DATA Disable Delay | TCDF   | _   | 50                            | _   | 50                            | ns |

| CLOCK to CEO Delay          | Тоск   |     | 65                            | _   | 40                            | ns |

| CE to CEO Delay             | TOCE   | _   | 45                            |     | 40                            | ns |

| OE to CEO Delay             | TOOE   |     | 40                            |     | 40                            | ns |

Figure 5. Read Characteristics at End of Array

Lucent Technologies Inc.

**--** 0050026 0021768 700 **--**

2-379

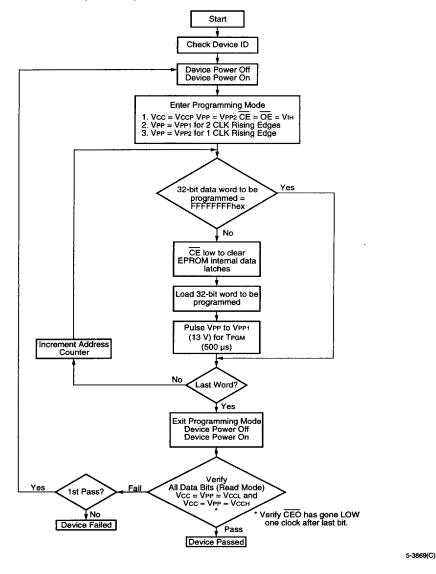

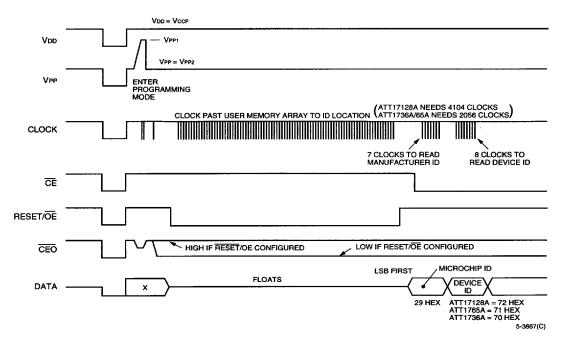

Figure 6. ATT1700A Programming

Lucent Technologies Inc.

2-380

■ 0050026 0021769 647

## **Table 6. dc Programming Specifications**

Commercial: 0 °C  $\leq$  TA  $\leq$  70 °C, VDD = 5.0 V  $\pm$  5%; Industrial: -40 °C  $\leq$  TA  $\leq$  +85 °C, VDD = 5.0 V  $\pm$  10%.

| Parameter                                                     | Symbol | Min  | Max      | Unit  |

|---------------------------------------------------------------|--------|------|----------|-------|

| Supply Voltage During Programming                             | VCCP   | 5.0  | 6.0      | V     |

| Low-level Input Voltage                                       | VIL    | 0.0  | 0.5      | V     |

| High-level Input Voltage                                      | VIH    | 2.4  | Vcc      | V     |

| Low-level Output Voltage                                      | VOL    |      | 0.4      | V     |

| High-level Output Voltage                                     | Voн    | 3.7  |          | V     |

| Programming Voltage*                                          | VPP1   | 12.5 | 13.5     | V     |

| Programming Mode Access Voltage                               | VPP2   | VCCP | VCCP + 1 | V     |

| Supply Current in Programming Mode                            | IPPP   |      | 100      | mA    |

| Input or Output Leakage Current                               | IL     | -10  | 10       | μА    |

| First-pass, Low-level Supply Voltage for Final Verification   | VDDL   | 2.8  | 3.0      | ····v |

| Second-pass, High-level Supply Voltage for Final Verification | VDDH   | 6.0  | 8.2      | V     |

<sup>\*</sup> No overshoot is permitted on this signal. VPP must not be allowed to exceed 14 V.

Lucent Technologies Inc.

2-381

**=** 0050026 002177**0** 369 **=**

#### **Table 7. ac Programming Specifications**

Commercial:  $0 \text{ °C} \le \text{TA} \le 70 \text{ °C}$ , VDD =  $5.0 \text{ V} \pm 5\%$ ; Industrial:  $-40 \text{ °C} \le \text{TA} \le +85 \text{ °C}$ , VDD =  $5.0 \text{ V} \pm 10\%$ .

| Parameter                                              | Test Conditions | Symbol | Min | Max  | Unit |

|--------------------------------------------------------|-----------------|--------|-----|------|------|

| 10% to 90% Rise Time of VPP                            | *               | TRPP   | 1   | _    | μs   |

| 90% to 10% Fall Time of VPP                            | *               | TFPP   | 1   |      | μs   |

| VPP Programming Pulse Width                            | <del></del>     | TPGM   | 0.5 | 1.05 | ms   |

| VPP Setup to Clock for Entering Programming Mode       | *               | Tsvc   | 100 |      | ns   |

| CE Setup to Clock for Entering Programming Mode        | *               | TSVCE  | 100 | _    | ns   |

| OE Setup to Clock for Entering Programming<br>Mode     | *               | TSVOE  | 100 | _    | ns   |

| VPP Hold from Clock for Entering Programming Mode      | *               | THVC   | 300 | _    | ns   |

| Data Setup to Clock for Programming                    | _               | TSDP   | 50  | _    | ns   |

| Data Hold from Clock for Programming                   | _               | THDP   | 0   | _    | ns   |

| CE Low Time to Clear Data Latches                      | _               | TLCE   | 100 | _    | ns   |

| CE Setup to Clock for Programming/Verifying            | _               | Tscc   | 100 | _    | ns   |

| OE Setup to Clock for Incrementing Address<br>Counter  | _               | Tsic   | 100 | _    | ns   |

| OE Hold from Clock for Incrementing Address<br>Counter | <del>-</del>    | THIC   | 0   | _    | ns   |

| OE Hold from VPP                                       | *               | THOV   | 200 | _    | ns   |

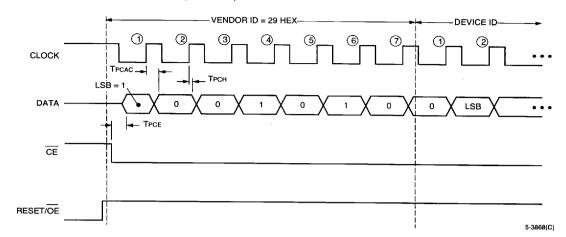

| Clock to Data Valid                                    |                 | TPCAC  | _   | 400  | ns   |

| Data Hold from Clock                                   | _               | Трон   | 0   |      | ns   |

| CE Low to Data Valid                                   | _               | TPCE   | _   | 250  | ns   |

<sup>\*</sup> This parameter is periodically sampled and is not 100% tested.

Note: While in programming mode,  $\overline{CE}$  should only be changed while  $\overline{OE}$  is HIGH and has been HIGH for 200 ns, and  $\overline{OE}$  should only be changed while  $\overline{CE}$  is HIGH and has been HIGH for 200 ns.

Lucent Technologies Inc.

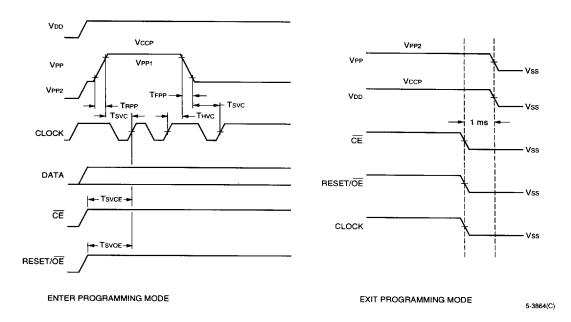

Figure 7. Entering and Exiting Programming Mode

<sup>\*</sup> The CEO pin is high impedance when VPP = VPP1.

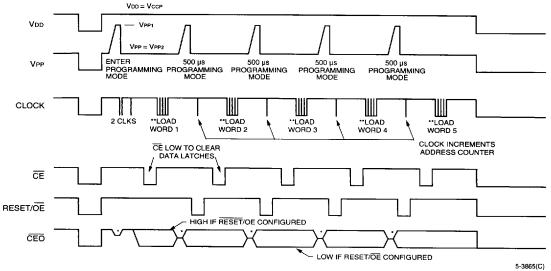

Figure 8. Programming Cycle Overview

Lucent Technologies Inc.

2-383

**■** 0050026 0021772 131 **■**

<sup>\*\* 32</sup> clocks.

2-384

## **Electrical Characteristics** (continued)

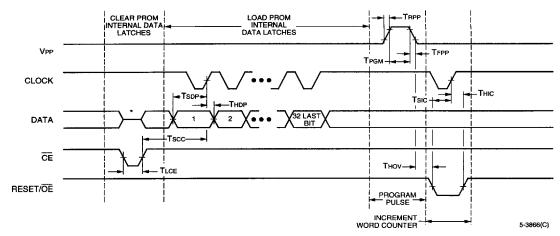

<sup>\*</sup> The programmer must float the data pin while CE is low to avoid bus contention.

Figure 9. Details of Programming Cycle

Figure 10. Read Manufacturer and Device ID Overview

Lucent Technologies Inc.

■ 0050026 0021773 078 ■

Figure 11. Details of Read Manufacturer and Device ID

Lucent Technologies Inc.

**■** 0050026 0021774 TO4 **■**

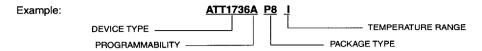

# **Ordering Information**

ATT1736A; One-Time Programmable; 8-pin, Plastic DIP; Industrial Temperature

Table 8. Device Type

| Device    | Size    |

|-----------|---------|

| ATT1736A  | 36,288  |

| ATT1765A  | 65,536  |

| ATT17128A | 131,072 |

**Table 9. Programmability**

| Designation | Programmability       |

|-------------|-----------------------|

| Blank or A  | One-Time Programmable |

### Table 10. Package Type

| Designation | Package            |

|-------------|--------------------|

| P8          | 8-pin, plastic DIP |

| SO8         | 8-pin SOIC         |

| M20         | 20-pin PLCC        |

**Table 11. Temperature Range**

| Designation | Туре       | Operating Range  |

|-------------|------------|------------------|

| Blank       | Commercial | 0 °C to 70 °C    |

| 1           | Industrial | -40 °C to +85 °C |

Lucent Technologies Inc.