T-51-09-90

### *DAC D20400* Dual 20 Bit Audio DAC 8X - Oversampling

#### **Features**

- 20 Bit Resolution

- 2 Independent Channels

- 400 kHz Max. Update Rate Per Channel

- Fully Characterized For **Audio Applications**

- Includes Distortion Suppressors

- **Guaranteed Maximum** Specifications

- Unsurpassed T.H.D. + Noise Performance

### **Applications**

- Upgrade 16 Bit Digital **Audio Systems**

- Digital Multi-channel Recorders

- Digital Audio Workstations

- Disk Based Recording

- Digital Audio Tape (DAT)

- Oversampled Audio Reconstruction

- Synthesizers

#### Description

The DAC D20400 includes two complete 20 Bit D/A Converters, a stable bipolar reference, a serial CMOS/TTL compatible digital interface and two distortionsuppressing output dealitcher amplifiers. The DAC D20400 converts at rates up to 400 kHz, thereby accommodating 8X oversampling applications. The product utilizes the finest available components including: a custom CMOS IC, custom thin-film resistor networks, low-noise operational amplifiers and a variety of discrete components.

The DAC D20400 achieves better initial linearity, superior long term stability and less sensitivity to resistor mismatch than other designs. Perhaps the most significant benefit of the proprietary UltraAnalog architecture is that no transitions of the more significant bits (MSBs) occur for near-zero signals. The proprietary architecture combines digital data enhancement techniques with an over-ranging discrete DAC for the 8 MSBs and a monolithic 12 bit DAC for the 12 less significant bits (LSBs). The additional resolution of the over-ranging DAC allows conversions to occur away from the major carry of the ladder network, while preventing an output over-range condition. This improves the integrity of conversions for small signals, thereby ensuring faithful audio signal reconstruction. The result is a typical small-signal performance (THD + N) of 112 dB over the 20 to 20 kHz band, that is guaranteed by design and will not deteriorate with time or temperature changes.

Another feature of the design architecture is that both D/A Converters share the same precision resistor ladder network that determines the weight of the 6 MSBs and also share the bipolar reference. By sharing these circuits, both D/A Converters will track each other over time and temperature and will behave nearly identically.

The large-signal performance of the product is limited by initial calibration and long term stability of the MSB ladder network. Consequently, the DAC D20400 uses premium quality thin-film resistor networks. Once installed in the product, the networks are fine-trimmed with stable metal film resistors. To perform the fine trimming, each DAC D20400 is exercised with a computerized calibration system that makes approximately 100,000 measurements and calculations to determine the optimum trim resistor values. Next, a test operator installs discrete metal film resistors into the DAC to complete the calibration. Although this procedure is more time consuming than laser trimming, the algorithm corrects for every conceivable error that affects largesignal linearity. Once factory calibration is complete, the user need not make any external adjustments.

Digital interface connections to the product are through the universal serial interface. The interface accepts Offset Binary, 2's Complement, Complementary Offset Binary and Complementary 2's Complement coding schemes. Input data words from 16 to 32 bits may be applied, which allows easy interfacing to existing systems. Further, data words for left and right channels may be applied simultaneously or multiplexed. An application note guides the user in selecting the appropriate interface configuration for the application. The interface is compatible with other serial input DACs, digital filter ICs and DSP processor ICs.

Finally, each DAC D20400 is 100% tested for critical parameters and guaranteed to meet its specifications. The overall result of these design innovations and specialized manufacturing techniques is the world's first Dual 20 Bit 8X Oversampling Audio DAC Subsystem.

## DAC D20400 Block Diagram

Left channel indicated by shadowed blocks. 20 Bit 20 Bit 20.1 Bit 20:20.1 Shift Latch Digital Ultra-linear Register D/A Converter Data Output L Modify Output 20 Deglitcher Out Rtn L and Code (NRZ) Output R Convert Out Rtn R Offs Adj R Offs Adj L Hold R DATA R Hold L DATA I Digital Timing and Control Low Noise Clocks Bipolar Ref Adj Reference Control

NOTE: Analog and Digital grounds

37E D

| ANALOG OUTDUT                                                                         |                                                                  |

|---------------------------------------------------------------------------------------|------------------------------------------------------------------|

| ANALOG OUTPUT                                                                         |                                                                  |

| Number of Channels:                                                                   | Two (independent)                                                |

| Full Scale Range:                                                                     | ±5V                                                              |

| Output Current:                                                                       | ±1 mA                                                            |

| Output Impedance:                                                                     | 0.1Ω, typ.                                                       |

| DIGITAL INPUT                                                                         |                                                                  |

| Resolution1:                                                                          | 20 Bits                                                          |

| Compatibility:<br>Vih:<br>Vil:                                                        | CMOS/TTL<br>2.4V, min.<br>0.8V, max.                             |

| Input Capacitance of<br>Digital Inputs (CI):                                          | 15 pF, typ.                                                      |

| Input Coding:                                                                         | 2's Complement, Offset Binary (OB),<br>Comp. Offset Binary (COB) |

| Hold Inputs:                                                                          | 1.5 μS width, 5 ns max. risetime                                 |

| Serial Input:                                                                         | MSB first, LSB last                                              |

| Clocks (3):                                                                           | Refer to Timing Diagram                                          |

| Control Lines (7):                                                                    | Refer to Timing Diagram                                          |

| Data L, Data R:                                                                       | Refer to Timing Diagram                                          |

| ACCURACY (+25°C                                                                       | C.)                                                              |

| Absolute Gain Error:<br>(Ext Ref Adj allows<br>adjustment to zero<br>for one channel) | ±0.1%, max.                                                      |

| Chan-to-Chan<br>Gain Mismatch:                                                        | ±0.05%, max.                                                     |

| Offset Error <sup>2</sup> :                                                           | ±5 mV, max.                                                      |

| Differential<br>Non-linearity (D.N.L.):                                               | ±0.0001% of FSR, typ.,<br>±0.0003% of FSR, max.                  |

| Monotonicity<br>(@ 0V Output):                                                        | 20 Bits, typ., 19 Bits, min.                                     |

| DYNAMIC PERFORMANCE                                       |                                     |

|-----------------------------------------------------------|-------------------------------------|

| Total Harmonic<br>Distortion + Noise<br>@ 20 Hz - 20 kHz³ |                                     |

| $V_{out} = -0.1 dB$ :                                     | -102 dB, typ., -100 dB, max.        |

| $V_{out} = -6 dB$ :                                       | -100 dB, typ., -96 dB, max.         |

| V <sub>out</sub> = -20 dB;                                | -88 dB, typ., -86 dB, max.          |

| V <sub>out</sub> = -60 dB:                                | -52 dB, typ., -50 dB, max.          |

| Sampling Rate:                                            | 400 kHz, max., per channel          |

| Channel-To-Channel<br>Crosstalk4:                         | -110 dB, typ., -100 dB, max.        |

| STABILITY                                                 |                                     |

| Warm-up Time:                                             | 5 minutes                           |

| Offset Drift:                                             | ±20μV/°C, typ., ±50μV/°C., max.     |

| Gain Drift:                                               | ±15 ppm/°C, typ., ±25 ppm/°C., max. |

| D.N.L. Drift @<br>0V Output:                              | ±0.15 ppm/°C., max.                 |

| POWER SUPPLY                                              |                                     |

| +15V ±3%,<br>Linear Regulated:                            | 65 mA, typ.                         |

| −15V ±3%,<br>Linear Regulated:                            | 45 mA, typ.                         |

| +5V ±5%:                                                  | 5 mA, typ.                          |

| MECHANICAL/ENVIRONMENTAL                                  |                                     |

| Package:                                                  | 2" × 3" × 0.4"                      |

| Operating<br>Temperature:                                 | +10°C. to +50°C.                    |

| Relative Humidity:                                        | 0 to 85%                            |

|                                                           |                                     |

#### NOTES:

- 1. The user may apply 16-32 bit data. The DAC D20400 will fill in the 2 or 4 LSBs automatically for 16 or 18 bit data.

- 2. Offset for each channel may be adjusted by connecting external trimpots.

- 3. T.H.D. + Noise specification applies for a single frequency measured in the 20 to 20 kHz band, with a

- sampling rate of 384 kHz. At 0 dB, the T.H.D. + N is -96 dB, maximum for signals >5 kHz. 4. One channel has an output signal of  $\pm$ FS at 5 kHz while the channel being measured has a 1 kHz output signal at -40 dB.

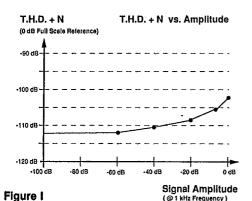

In **Figure I**, the characteristic of the DAC D20400 improving in performance as the signal amplitude is decreased is clearly displayed. For large signals, some T.H.D. exists that diminishes as the signal amplitude decreases. For signals below approximately  $-50 \, \text{dB}$ , the T.H.D. + N performance is limited only by the noise floor . . . typically 112 dB below full scale!

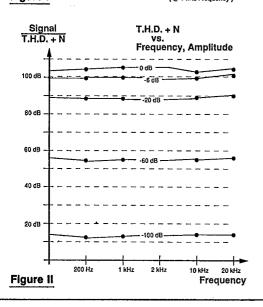

In **Figure II**, Signal/(Noise + Distortion) vs. Frequency is plotted at five amplitudes, 0, -6, -20, -60, and -100 dB. Many authorities of digital audio signal reconstruction believe that the small signal behavior of digital audio systems determines the limit on listening quality. UltraAnalog characterizes the performance of the DAC D20400 Dual D/A Converter with sinusoidal signals at -100 dB.

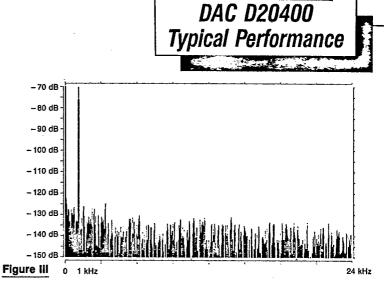

In **Figure III**, the FFT performance of the DAC D20400 with a 1 kHz, -70 dB signal is shown. This plot is the result of a 8k point FFT displayed with a Hanning window. The small signal performance achieved with this product is insensitive to miscalibration or aging effects and is guaranteed by design!

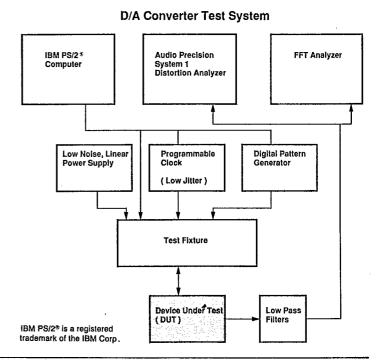

# Test System

The Block Diagram of the test system used by UltraAnalog to calibrate and verify final test data of D/A Converters during manufacturing is shown here. The IBM PS/2 satisfies all of the computational and data storage requirements, and acts as the system controller of the test system. A Programmable Clock, Digital Pattern Generator and Calibration Test Fixture were custom-designed as part of the overall system.

The Programmable Clock generates pulses with selectable frequency and width, while achieving approximately 3 pS RMS jitter. The Digital Pattern Generator is a special purpose memory box that stores 16 pages of different digital waveforms that are downloaded from the IBM PS/2. Each memory page contains 2 channels of 24 bit wide data that allows different amplitude and frequency signals to be simultaneously applied to both D/A Converter channels. Other test capabilities, including output filters, calibration hardware and FFT analysis software are engineered to eliminate test system errors FFT analysis software are engineered to eliminate test system errors from measured data. Extensive software allows each DAC D20400 to be automatically calibrated and final tested during manufacturing. The user is assured of receiving products that comfortably meet the published specifications.

D20400-DS (N7-89)

ULTRAANALOG,INC.

| Advancing the Analog Art.

47747 Warm Springs Blvd. P.O. Box 14164 Fremont, California 94539

TEL: (415) 657-2227 FAX: (415) 657-4225