# PN CODER STEL-1032

STANFORD TELECOM®

# **FEATURES**

- 3 independent PN code generators

- III Independent clocks, controls and outputs

- **■** Microprocessor control interface

- Composite code generation capabilities

- Punctual, early and late outputs for code tracking

- 30 MHz operation

- Low power CMOS

- Military and commercial temperature ranges available

# **APPLICATIONS**

- Pseudorandom (PN) code generation

- Gold Code generation

- JPL Ranging Code generation

- Syncopated Code generation

# **FUNCTIONAL DESCRIPTION**

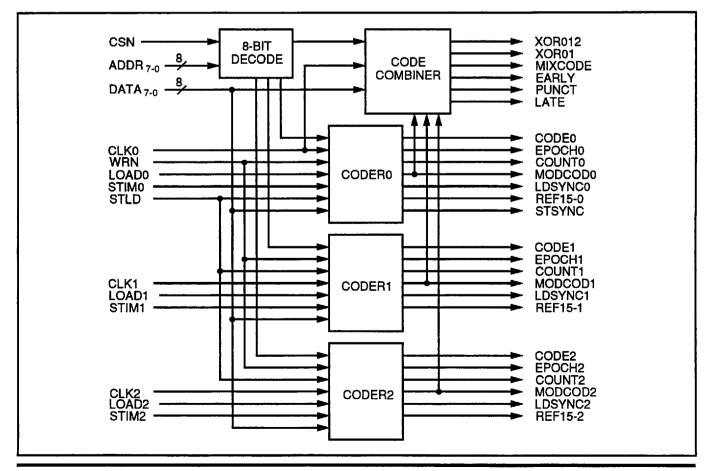

The STEL-1032 PN (Pseudo-Random Number) Coder provides the communications industry with a cost-effective and compact solution to code generation. The device's unique architectural design provides a power-efficient, high-speed code generator able to produce any 3 maximal or non-maximal length codes with up to 32 feedback taps per generator, and code lengths up to 2<sup>32</sup>-1 (4,394,967,295) bits. Capabilities for modulo-2 addition (EXOR), code modulation, and nonlinear composite code generation are also provided in the device. The device can be programmed very easily via the microprocessor interface.

# **BLOCK DIAGRAM**

# **CIRCUIT DESCRIPTION**

The STEL-1032 PN (Pseudo-Random Number) Coder generates the codes using three 32-bit registers. The feedback tap combinations are controlled by the MASK Registers, and any number of taps may be selected. In this way each of the three coders can independently generate all possible codes with lengths up to 2<sup>32</sup>-1 (4,294,967,295). The codes can be started at any random point by loading the start code in the INIT Registers, and a specific position in any of the codes can be detected, according to the values stored in the EPOCH

Registers. The codes can be made to restart at this point if desired. In addition to the three independent codes that can be generated, the outputs of code generators 0 and 1 can be EXORed together, and similarly the outputs of all three generators can be EXORed together, greatly expanding the lengths and versatilities of the codes. The output of code the combiner is also available both late and early by one half of a clock cycle relative to the punctual code, and nonlinear codes can be generated by means of an internal programmable lookup table.

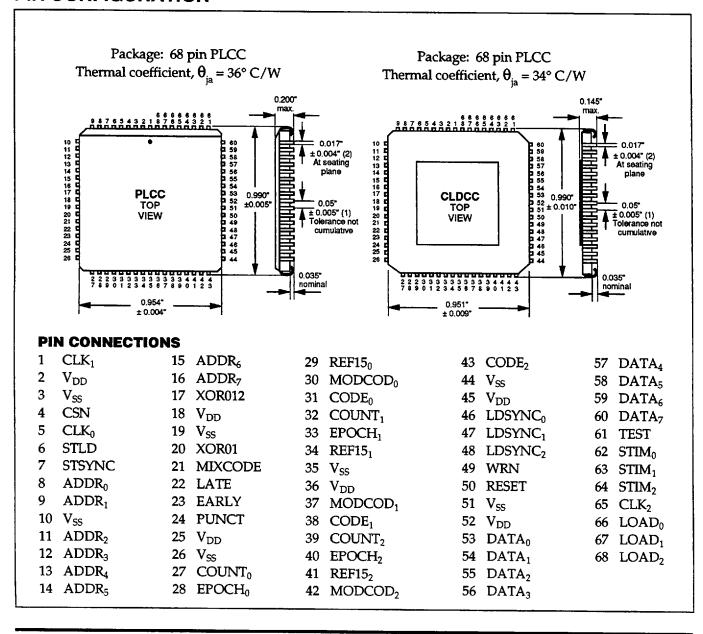

# PIN CONFIGURATION

# INPUT SIGNALS

### RESET

When the reset input is low, all the registers inside the coder are reset to zero. Normal operation will not commence until an initialization value has been loaded into the PN Generators from the corresponding INIT registers.

### CLK<sub>0</sub>-CLK<sub>2</sub>

Clock inputs to Coders 0-2, respectively. All operations occur on the rising edges of the clocks, with the exception of the EARLY and LATE outputs, which change on the falling edges of CLK<sub>0</sub>. The clocks should nominally be square waves, with a maximum frequency of 30 MHz.

### **WRN**

Register write control. When this line is low data is written into the register(s) selected by the address lines and latched on the rising edge of WRN.

### **CSN**

A low level on the Chip Select input enables the loading of data via the data bus.

# ADDR<sub>0</sub>-ADDR<sub>4</sub>

Register select address inputs. The addressing of the registers is shown in the table below:

| A4 | А3 | <b>A2</b> | <b>A</b> 1 | <b>A</b> 0 | Register Selected         |

|----|----|-----------|------------|------------|---------------------------|

| 0  | 0  | 0         | 0          | 0          | MASK Register bits 0-7    |

| 0  | 0  | 0         | 0          | 1          | MASK Register bits 8–15   |

| 0  | 0  | 0         | 1          | 0          | MASK Register bits 16–23  |

| 0  | 0  | 0         | 1          | 1          | MASK Register bits 24-31  |

| 0  | 0  | 1         | 0          | 0          | INIT Register bits 0-7    |

| 0  | 0  | 1         | 0          | 1          | INIT Register bits 8–15   |

| 0  | 0  | 1         | 1          | 0          | INIT Register bits 16–23  |

| 0  | 0  | 1         | 1          | 1          | INIT Register bits 24–31  |

| 0  | 1  | 0         | 0          | 0          | EPOCH Register bits 0-7   |

| 0  | 1  | 0         | 0          | 1          | EPOCH Register bits 8-15  |

| 0  | 1  | 0         | 1          | 0          | EPOCH Register bits 16–23 |

| 0  | 1  | 0         | 1          | 1          | EPOCH Register bits 24-31 |

| 0  | 1  | 1         | 0          | 0          | COUNT Register bits 0-7   |

| 0  | 1  | 1         | 0          | 1          | COUNT Register bits 8-15  |

| 0  | 1  | 1         | 1          | 0          | COUNT Register bits 16-23 |

| 0  | 1  | 1         | 1          | 1          | COUNT Register bits 24-31 |

| 1  | 0  | 0         | 0          | 0          | MUX Register bits 0-4     |

| 1  | 0  | 0         | 0          | 1          | CTL Register bits 0-7     |

### ADDR<sub>5</sub>-ADDR<sub>7</sub>

Coder and code combiner select address inputs. The addressing of the registers is shown in the table below:

|   | A7 A6 A5 |   |   | Coder Selected                |

|---|----------|---|---|-------------------------------|

| Γ | 0        | 0 | 0 | Coder 0                       |

|   | 0        | 0 | 1 | Coder 1                       |

|   | 0        | 1 | 0 | Coder 2                       |

|   | 0        | 1 | 1 | All coders                    |

|   | 1        | 0 | 0 | Code Combiner Lookup register |

### DATA<sub>0</sub>-DATA<sub>7</sub>

Data bus inputs, used to write data to the registers. DATA<sub>7</sub> is the MSB and DATA<sub>0</sub> is the LSB.

# LOAD<sub>0</sub>-LOAD<sub>2</sub>

On the rising edge of the clock following the falling edge of a load input a load command is issued. This will cause the corresponding PN Generator register and Counter register are loaded with the contents of the corresponding INIT register and COUNT register, respectively.

### STIM<sub>0</sub>-STIM<sub>2</sub>

Data applied to the STIM<sub>0-2</sub> inputs is modulo-2 added (EXORed) with the outputs of the corresponding PN Generator (CODE<sub>0-2</sub>). The data is latched in on the falling edges of the STLD input.

### STLD

The STLD signal is used to latch the data appearing on the  $STIM_{0-2}$  inputs. The data is latched in on the falling edge of this signal, the stim load command.

# **OUTPUT SIGNALS**

### **TEST**

The **TEST** output is used for test purposes only. It should be left unconnected in normal use.

### CODE<sub>0</sub>-CODE<sub>2</sub>

The CODE<sub>0-2</sub> outputs are the outputs of the PN Generators 0-2. The register bit in the PN Generator from which the output is derived is set by the Phase Multiplexer.

### MODCOD<sub>0</sub>-MODCOD<sub>2</sub>

The MODCOD<sub>0-2</sub> outputs are the CODE<sub>0-2</sub> signals after modulation by the STIM<sub>0-2</sub> inputs. The register bit in the PN Generator from which the output is derived is set by the Phase Mux.

### **PUNCT**

The PUNCT output is an exact replica of the MIXCODE output delayed by one clock cycle.

### **EARLY**

The EARLY output is an exact replica of the PUNCT output advanced by half a clock cycle. This is achieved by clocking the signal into the output register on the falling edge of CLK<sub>0</sub>. In order to make the advance exactly half a clock cycle, the duty cycle of CLK<sub>0</sub> must be exactly 50%. This also applies to the timing of the LATE signal.

### LATE

The LATE output is an exact replica of the PUNCT output delayed by half a clock cycle. This is achieved by clocking the signal into the output register on the falling edge of CLK<sub>0</sub>

# LDSYNC<sub>0</sub>-LDSYNC<sub>2</sub>

A Loadsync output goes low for one clock cycle after the contents of the corresponding INIT register have been loaded into the corresponding PN Generator. This pulse indicates the clock cycle in which the PN Generator value is identical to that of the INIT register.

### REF150-REF152

The REF15<sub>0-2</sub> outputs are reference codes derived from the fifteenth taps of the corresponding PN Generator. These outputs will be identical to the corresponding CODE<sub>0-2</sub> outputs when the data stored in the corresponding Phase Mux is 01110.

### **STSYNC**

The STSYNC output is normally high and goes low for one clock cycle following a falling edge on the STLD signal. The result of the new modulation bits will appear on the output codes MODCOD<sub>0-2</sub> during this clock cycle.

### EPOCH<sub>0</sub>-EPOCH<sub>2</sub>

The EPOCH<sub>0-2</sub> outputs are normally high and go low whenever the corresponding PN Generator code is equal to the code stored in the corresponding Epoch register. Note that this condition will not be detected, and the EPOCH<sub>n</sub> output will not go low, if this condition occurs within 2 clock cycles of a rising edge on the corresponding input.

### COUNT<sub>0</sub>-COUNT<sub>2</sub>

The COUNT<sub>0-2</sub> outputs are delayed replicas of the LDSYNC<sub>0-2</sub> outputs. The length of the delay is equal (in clock cycles) to the value stored in the corresponding Count register.

### XOR01

The XOR01 output is the result of the modulo-2 addition (XOR) of the  $CODE_0$  and  $CODE_1$  signals. The result is delayed by one clock cycle before appearing at the XOR01 output.

### **XOR012**

The XOR012 output is the result of the modulo-2 addition (XOR) of the CODE<sub>0</sub>, CODE<sub>1</sub> and CODE<sub>2</sub> signals. The result is delayed by one clock cycle before appearing at the XOR012 output.

### MIXCODE

The MODCOD<sub>0-2</sub> signals are used to address the Code Combiner Lookup Register. The data bit stored in the location addressed by the three bits of MODCOD<sub>0-2</sub> is the MIXCODE output, as shown in the table:

| M2 | M2 M1 M0 |   | MIXCODE               |

|----|----------|---|-----------------------|

| 0  | 0        | 0 | Lookup Register Bit 0 |

| 0  | 0        | 1 | Lookup Register Bit 1 |

| 0  | 1        | 0 | Lookup Register Bit 2 |

| 0  | 1        | 1 | Lookup Register Bit 3 |

| 1  | 0        | 0 | Lookup Register Bit 4 |

| 1  | 0        | 1 | Lookup Register Bit 5 |

| 1  | 1        | 0 | Lookup Register Bit 6 |

| 1  | 1        | 1 | Lookup Register Bit 7 |

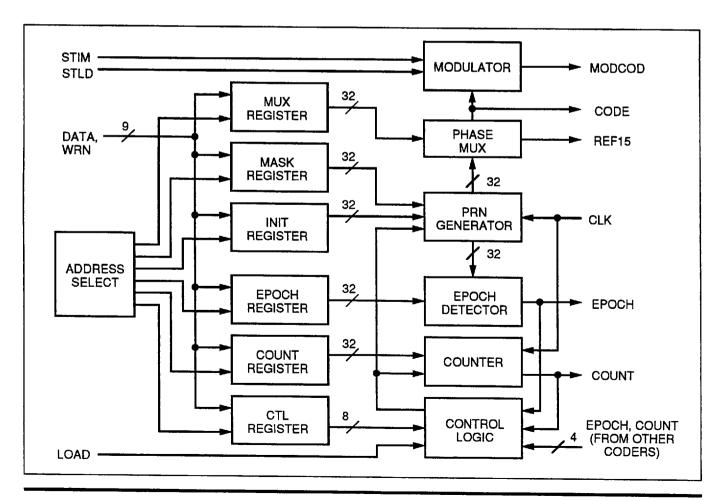

# **FUNCTION BLOCKS**

Each of the three separate coders contains a number of function blocks. The three coders are completely independent, except for the COUNT and EPOCH functions which go from every coder to every other coder's control logic block. This allows each coder to be controlled by either of the other two coders for the generation of syncopated functions.

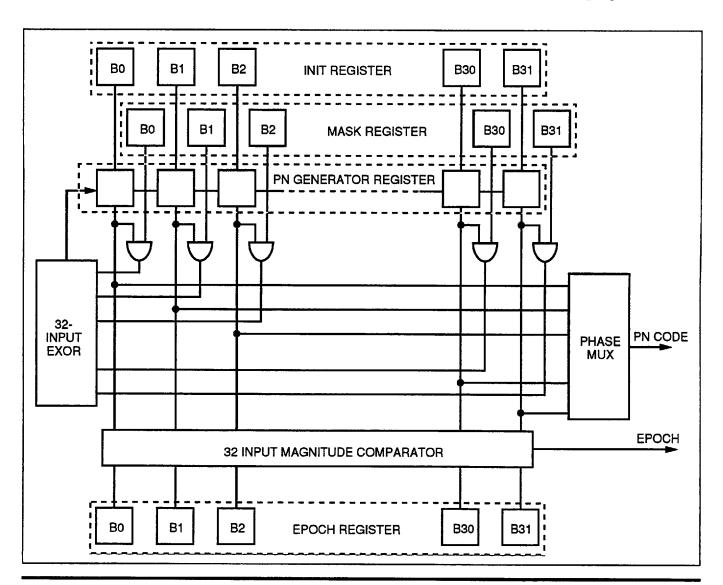

### PN CODE GENERATOR BLOCK

The 32-bit PN Code generator generates codes with programmable lengths and polynomials. The polynomials are set by programming the desired taps in the Mask register. Each bit in the Mask register which is set to a logic '1' enables the corresponding tap in the PN generator polynomial:

G=1+D1(x)+D2(

$$x^2$$

)+D3( $X^3$ )-----+D31( $X^{31}$ )+D32( $X^{32}$ ) where D1 = Bit 0, D2 = Bit 1, D3 = Bit 2, etc.

A logic '0' disables the tap. Note that the most significant (i.e. last) tap set determines the effective length of the PN generator register. These are the active bits of the PN Generator. e.g., if the most significant tap set is D17 (i.e., D18 through D32 are all zero), then the maximum code length possible with that configuration will be  $2^{17}$ -1 bits.

The start code of the PN sequence is set by loading the code into the INIT register. The code is loaded into the PN generator register under the control of the Control Logic block. This will happen a load command is issued, and also on an EPOCH or COUNT pulse, if one or both of the functions are programmed. The PN generators should not be re-initialized within 8 clock cycles of being initialized.

# **EPOCH DETECTOR BLOCKS**

Every clock cycle the active bits of the output of the PN Generator are compared with the word stored in the EPOCH register. The EPOCH output pulses low each

time a match is found between the active bits in the PN generator and the corresponding bits of the word in the EPOCH register.

### **COUNTER BLOCK**

The 32-bit Counter is programmed by means of the COUNT register. The counter can be started by any of the COUNT and EPOCH pulses, and once started will count up to the value stored in the COUNT register and then stop. The counter should not be restarted within 8 clock cycles of being started.

### **CONTROL LOGIC BLOCK**

The control logic block performs the functions programmed in the CTL register. The EPOCH and COUNT outputs of all three coders, as well as the LOAD input, are the inputs of the control logic block. Depending on the contents of the CTL register, the PN Generator register may be reloaded from the INIT register, and/or the counter may be reloaded from the COUNT register each time any of these signals are activated.

# PHASE MULTIPLEXER BLOCK

The Phase Mux block performs a one-out-of-thirty two selection function. The outputs of all thirty two bits of

the PN generator register are fed into the phase mux, and the code stored in the MUX register is used to select one of these. This allows the phasing of the coder output to be varied.

### **MODULATOR BLOCK**

The modulator permits the CODE output to be modulated with the STIM signal. The modulation function is a logical exclusive-OR (EXOR). New STIM bits are loaded into the modulators on each STLD command.

### **REGISTER BLOCKS**

The STEL-1032 is programmed by means of the data stored in the registers. Each of the three independent code generators has a complete set of these registers. The 8-bit data bus is mapped into the 32-bit registers by means of address inputs ADDR<sub>0</sub> and ADDR<sub>1</sub>, as shown on page 4.

### **MASK Registers**

The 32-bit Mask register is used to define the active feedback taps in the PN generators. Each bit set to a one enables the corresponding tap. The MASK register is not buffered, and any changes made will affect the PN generator polynomial immediately. Care should

be taken in modifying the contents of the MASK register while the generator is operating, since the bits can only be changed eight (one byte) at a time.

### INIT<sub>0-2</sub> Register

The 32-bit Init register is used to define the start value of the code generated in the PN Generator. The contents of the INIT register are loaded into the PN generator by means of the Control logic. This occurs when a load command is issued, and whenever an EPOCH or COUNT pulse occurs, when these functions are enabled.

### EPOCH<sub>0-2</sub> Register

The 32-bit Epoch register is used to define the distinct code value to be detected in the PN Generator. The EPOCH register is not buffered, and any changes made will affect the EPOCH detected immediately. Note that all bits of the EPOCH register beyond the most significant feedback tap in the PN generator (i.e. the most significant one in the corresponding MASK register), must always be set to zero, otherwise undesirable effects will occur. e.g. polynomial set by MASK register = 00000101 makes effective length of PN generator eight bits. In this case, bits 8 through 31 of the EPOCH register must be set to zero.

# COUNT<sub>0-2</sub> Register

The 32-bit Count register is used to set the counter stop point. Once triggered, the counter will run for a number of clock cycles equal to the number stored in the COUNT register and then generate a COUNT pulse. The contents of the COUNT register are loaded into the counter by means of the Control logic. This occurs when a load command is issued, and whenever an EPOCH or COUNT pulse occurs, when these functions are enabled.

# **Phase MUX Register**

The 5-bit Phase Mux register is used to select the PN generator register output bits used for the code outputs. The value stored in the Mux register is decoded and determines the tap number used. e.g.

Mux register value = 00000, tap number used =1 Mux register value = 11111, tap number used =32

### **CTL Register**

The 8-bit CTL register is used to define the reloading of the coder and counter. The functions performed by the bits in the CTL register are shown in the tables:

| B <sub>7</sub> B <sub>6</sub>          | Function                                        |  |  |  |  |  |

|----------------------------------------|-------------------------------------------------|--|--|--|--|--|

| 0 0                                    | Counter is not reloaded on any EPOCH pulse      |  |  |  |  |  |

| 0 1                                    | Counter is reloaded on EPOCH <sub>0</sub> pulse |  |  |  |  |  |

| 1 0                                    | Counter is reloaded on EPOCH <sub>1</sub> pulse |  |  |  |  |  |

| 1 1                                    | Counter is reloaded on EPOCH <sub>2</sub> pulse |  |  |  |  |  |

| B <sub>5</sub> B <sub>4</sub> Function |                                                 |  |  |  |  |  |

| D <sub>5</sub> D <sub>4</sub>          | runction                                        |  |  |  |  |  |

| 0 0                                    | Counter is not reloaded on any COUNT pulse      |  |  |  |  |  |

|                                        | Counter is reloaded on COUNT <sub>0</sub> pulse |  |  |  |  |  |

| 1 |                               | <u> </u>                                        |

|---|-------------------------------|-------------------------------------------------|

|   | B <sub>3</sub> B <sub>2</sub> | Function                                        |

| i | 0 0                           | PN gen. is not reloaded on any EPOCH pulse      |

|   | 0 1                           | PN gen. is reloaded on EPOCH <sub>0</sub> pulse |

|   |                               | PN gen. is reloaded on EPOCH <sub>1</sub> pulse |

|   | 1 1                           | PN gen. is reloaded on EPOCH <sub>2</sub> pulse |

1 0 Counter is reloaded on COUNT<sub>1</sub> pulse

1 1 Counter is reloaded on COUNT<sub>2</sub> pulse

| $B_1B$ | 0 | Function                                        |

|--------|---|-------------------------------------------------|

| 0 0    | ) | PN gen. is not reloaded on any COUNT pulse      |

|        |   | PN gen. is reloaded on COUNT <sub>0</sub> pulse |

| 1 (    | ) | PN gen. is reloaded on COUNT <sub>1</sub> pulse |

| 1 1    | L | PN gen. is reloaded on COUNT <sub>2</sub> pulse |

The CTL register is not buffered, and all changes take place immediately.

### **CODE COMBINER**

The STEL-1032 contains a single Code Combiner block in which the MODCOD outputs of the three modulators are used to address a lookup table to produce the MIXCODE output. This allows nonlinear codes to be generated.

# **PROGRAMMING EXAMPLES**

Using the INIT, MASK, EPOCH and CTL registers to generate a truncated sequence with the polynomial:

$$G = 1 + X^3 + X^4$$

in generator 0. This polynomial generates the following sequence:

| _ | _ | _ | _ |           |

|---|---|---|---|-----------|

| 1 | 0 | 0 | 0 |           |

| 0 | 1 | 0 | 0 |           |

| 0 | 0 | 1 | 0 |           |

| 1 | 0 | 0 | 1 |           |

| 1 | 1 | 0 | 0 |           |

| 0 | 1 | 1 | 0 |           |

| 1 | 0 | 1 | 1 |           |

| 0 | 1 | 0 | 1 |           |

| 1 | 0 | 1 | 0 |           |

| 1 | 1 | 0 | 1 |           |

| 1 | 1 | 1 | 0 |           |

| 1 | 1 | 1 | 1 |           |

| 0 | 1 | 1 | 1 |           |

| 0 | 0 | 1 | 1 |           |

| 0 | 0 | 0 | 1 | (repeats) |

Note that this is a maximal-length sequence, i.e., it contains every possible combination of four bits, except 0000. The all-zeroes combination never exists in any PN sequence, it is a lockup condition since the all-zeroes combination will always generate a zero in an exclusive-OR function. In addition, any PN generator with an odd number of taps will also have the all-ones state as a lockup condition.

Since this is a 4-bit code only the first four bits of the registers will be considered in this example. It is assumed that all the other bits are set to zero in all the registers. By setting the MASK register to 0011 feedback taps three and four are selected, generating the desired polynomial. By setting the INIT register to 1001 the generator can be made to start at code 1001. By setting the EPOCH register to 0101 and the CTL register to XXXX01XX the generator can be made to detect the code 0101 and then reload the contents of the INIT register. It will then cycle through the following states:

| 1 | 0 | 0 | 1 |           |

|---|---|---|---|-----------|

| 1 | 1 | 0 | 0 |           |

| 0 | 1 | 1 | 0 |           |

| 1 | 0 | 1 | 1 |           |

| 0 | 1 | 0 | 1 | (repeats) |

Note that it is possible to start any of the PN generators when any specific code is detected in either in itself or in either of the other two generators. In this way it is possible to concatenate codes, as shown in the second example.

2. Syncopated codes. Assuming that generator 0 is set up to generate the same code as in the first example, set up generator 1 to generate the polynomial:

$$G = 1 + X^2 + X^3 + X^5$$

by setting the MASK register to 01101 (first five bits only, all others zero). This generates non-maximal length sequences, one of which is ten states long, and includes the sequence:

| 1 | 1 | 0 | 1 | 0 |

|---|---|---|---|---|

| 1 | 1 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

By setting the INIT register to 11010 and the EPOCH register to 01011 this sequence can be generated. If CTL register 0 is set to XXXX10X and CTL register 1 is set to XXXX01X the two generators will operate in a syncopated manner, each one restarting the other. Note that each one continues generating its own code until restarted.

- 3. Direct-sequence spread-spectrum modulation. By using the STIM input for the data, a spreading code can be added to the modulation pattern. The result is available at the corresponding MODCOD output.

- 4. Generating a nonlinear code using the Code Combiner block. By writing a data byte into the Code Combiner Lookup Register special codes can be generated. For example, by writing  $E8_H$  into this register a code can be generated which produces a one whenever two or more of the MODCOD outputs are ones, and a zero at all other times, i.e., a majority function.

# **ELECTRICAL CHARACTERISTICS**

# **ABSOLUTE MAXIMUM RATINGS**

Warning: Stresses greater than those shown below may cause permanent damage to the device. Exposure of the device to these conditions for extended periods may also affect device reliability. All voltages are referenced to  $V_{\rm SS}$ .

| Symbol              | Parameter                         | Range                    | Units                |

|---------------------|-----------------------------------|--------------------------|----------------------|

| $T_{stg}$           | Storage Temperature               | ∫-40 to +125             | °C (Plastic package) |

|                     |                                   | \_65 to +150             | °C (Ceramic package) |

| V <sub>DDmax</sub>  | Supply voltage on V <sub>DD</sub> | -0.3 to + 7              | volts                |

| V <sub>I(max)</sub> | Input voltage                     | $-0.3$ to $V_{DD} + 0.3$ | volts                |

| $I_i$               | DC input current                  | ± 10                     | mA                   |

# RECOMMENDED OPERATING CONDITIONS

| Symbol         | Parameter                       | Range Units             |                                           |

|----------------|---------------------------------|-------------------------|-------------------------------------------|

| $V_{DD}$       | Supply Voltage                  | +5 ± 5%                 | Volts                                     |

| T <sub>a</sub> | Operating Temperature (Ambient) | 0 to +70<br>-55 to +125 | °C (Plastic package) °C (Ceramic package) |

# **D.C. CHARACTERISTICS** (Operating Conditions: $V_{DD} = 5.0 \text{ V} \pm 5\%$ , $V_{SS} = 0 \text{ V}$ , $T_a = 0^{\circ}$ to $70^{\circ}$ C)

| Symbol               | Parameter                     | Min. | Тур.        | Max. | Units  | Conditions                          |

|----------------------|-------------------------------|------|-------------|------|--------|-------------------------------------|

| $I_{DD(Q)}$          | Supply Current, Quiescent     |      |             | 1.0  | mA     | Static, no clock                    |

| $I_{DD}$             | Supply Current, Operational   |      |             | 3.0  | mA/MHz |                                     |

| V <sub>IH(min)</sub> | High Level Input Voltage      |      |             |      |        |                                     |

|                      | Standard Operating Conditions | 2.0  |             |      | volts  | Logic '1'                           |

| :                    | Extended Operating Conditions | 2.25 |             |      | volts  | Logic '1'                           |

| V <sub>IL(max)</sub> | Low Level Input Voltage       |      |             | 0.8  | volts  | Logic '0'                           |

| I <sub>IH(min)</sub> | High Level Input Current      |      |             | 10   | μΑ     | $V_{IN} = V_{DD}$                   |

| I <sub>IL(max)</sub> | Low Level Input Current       |      |             | -10  | μА     | $V_{IN} = V_{SS}$                   |

| V <sub>OH(min)</sub> | High Level Output Voltage     | 2.4  | 4.5         |      | volts  | $I_O = -4.0 \text{ mA}$             |

| V <sub>OL(max)</sub> | Low Level Output Voltage      |      | 0.2         | 0.4  | volts  | $I_{O} = +4.0 \text{ mA}$           |

| Ios                  | Output Short Circuit Current  | 20   | 65          | 130  | mA     | $V_{OUT} = V_{DD}$ , $V_{DD} = max$ |

|                      |                               | -10  | <b>-4</b> 5 | -130 | mA     | $V_{OUT} = V_{SS}$ , $V_{DD} = max$ |

| C <sub>IN</sub>      | Input Capacitance             |      | 2           | :    | рF     | All inputs                          |

| C <sub>OUT</sub>     | Output Capacitance            |      | 4           |      | pF     | All outputs                         |

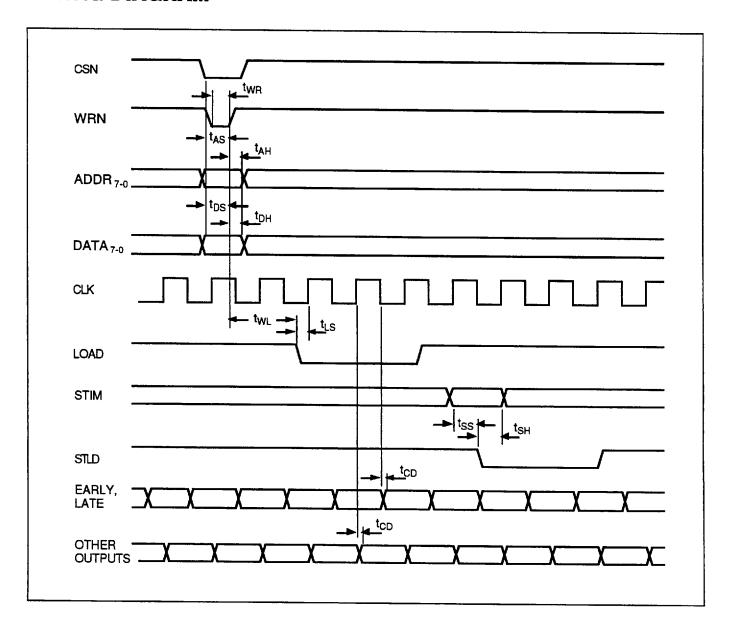

# **TIMING DIAGRAM**

**A.C. CHARACTERISTICS** (Operating Conditions:  $V_{DD} = 5.0 \text{ V} \pm 5\%$ ,  $V_{SS} = 0 \text{ V}$ ,  $T_a = 0^{\circ}$  to  $70^{\circ}$  C)

| Symbol          | Parameter                      | Min. | Max. | Units | Conditions   |

|-----------------|--------------------------------|------|------|-------|--------------|

| t <sub>DS</sub> | Data Setup time                | 10   |      | nsec. |              |

| t <sub>AS</sub> | Address Setup time             | 10   |      | nsec. |              |

| t <sub>DH</sub> | Data Hold time                 | 10   |      | nsec. |              |

| t <sub>AH</sub> | Address Hold time              | 10   |      | nsec. |              |

| t <sub>is</sub> | Load Setup time                | 10   | i    | nsec. |              |

| t <sub>wL</sub> | Write to Load delay time       | 160  |      | nsec. |              |

| t <sub>DH</sub> | STIM to STLD Setup time        | 10   | ļ    | nsec. |              |

| t <sub>ah</sub> | STIM to STLD Hold time         | 10   |      | nsec. |              |

| t <sub>CP</sub> | Max. CLK frequency             |      | 30   | MHz   |              |

| t <sub>LS</sub> | CLK pulse width                | 10   |      | nsec. |              |

| t <sub>wr</sub> | WRN pulse width                | 20   |      | nsec. |              |

| t <sub>CD</sub> | Clock delay, CLK to any output | 5    | 18   | nsec. | Load = 20 pF |

Note: The duty cycle of the CLK<sub>□</sub> signal must be 50% in order to achieve correct timing of the EARLY and LATE signals, since these outputs are latched on the falling edge of the clock and the PUNCT signal is latched on the rising edge.

# FOR FURTHER INFORMATION CALL OR WRITE STANFORD TELECOMMUNICATIONS

ASIC & Custom Products Division

Tel: (408) 541-9031 Fax: (408) 541-9030

480 Java Drive • Sunnyvale, CA 94089-1125

© 1989 - 1994 Stanford Telecommunications, Inc. 9/94