Date Jan. 20. 2003

## PRELIMINARY DATASHEET

# DATASHEET

**PRODUCT**: 64M (x16) Flash Memory

MODEL NO: LH28F640BFB-PTTL60

O This device datasheet is subject to change without notice.

O Copyright Sharp Co., Ltd. All rights reserved. No reproduction or republication without written permission.

O Contact your local Sharp sales office to obtain the latest datasheet.

- Handle this document carefully for it contains material protected by international copyright law. Any reproduction, full or in part, of this material is prohibited without the express written permission of the company.

- When using the products covered herein, please observe the conditions written herein and the precautions outlined in the following paragraphs. In no event shall the company be liable for any damages resulting from failure to strictly adhere to these conditions and precautions.

- (1) The products covered herein are designed and manufactured for the following application areas. When using the products covered herein for the equipment listed in Paragraph (2), even for the following application areas, be sure to observe the precautions given in Paragraph (2). Never use the products for the equipment listed in Paragraph (3).

- Office electronics

- Instrumentation and measuring equipment

- Machine tools

- Audiovisual equipment

- Home appliance

- Communication equipment other than for trunk lines

- (2) Those contemplating using the products covered herein for the following equipment which demands high reliability, should first contact a sales representative of the company and then accept responsibility for incorporating into the design fail-safe operation, redundancy, and other appropriate measures for ensuring reliability and safety of the equipment and the overall system.

- Control and safety devices for airplanes, trains, automobiles, and other transportation equipment

- Mainframe computers

- Traffic control systems

- Gas leak detectors and automatic cutoff devices

- Rescue and security equipment

- Other safety devices and safety equipment, etc.

- (3) Do not use the products covered herein for the following equipment which demands extremely high performance in terms of functionality, reliability, or accuracy.

- Aerospace equipment

- Communications equipment for trunk lines

- Control equipment for the nuclear power industry

- Medical equipment related to life support, etc.

- (4) Please direct all queries and comments regarding the interpretation of the above three Paragraphs to a sales representative of the company.

- Please direct all queries regarding the products covered herein to a sales representative of the company.

## CONTENTS

| PAGE                                                | PAGE                                                             |

|-----------------------------------------------------|------------------------------------------------------------------|

| 0.8mm pitch 60-Ball CSP Pinout                      | Extended Status Register Definition                              |

| Pin Descriptions                                    | Partition Configuration Register Definition 16                   |

| Simultaneous Operation Modes                        | Partition Configuration                                          |

| Allowed with Four Planes 5                          | 1 Electrical Specifications                                      |

| Memory Map 6                                        | 1.1 Absolute Maximum Ratings 17                                  |

| Identifier Codes and OTP Address for Read Operation | 1.2 Operating Conditions                                         |

| Identifier Codes and OTP Address for                | 1.2.1 Capacitance                                                |

| Read Operation on Partition Configuration 7         | 1.2.2 AC Input/Output Test Conditions                            |

| OTP Block Address Map for OTP Program 8             | 1.2.3 DC Characteristics                                         |

| Bus Operation                                       | 1.2.4 AC Characteristics                                         |

| Command Definitions 10                              | - Read-Only Operations                                           |

| Functions of Block Lock and Block Lock-Down 12      | 1.2.5 AC Characteristics - Write Operations                      |

| Block Locking State Transitions upon                | •                                                                |

| Command Write                                       | 1.2.6 Reset Operations                                           |

| Block Locking State Transitions upon WP# Transition | 1.2.7 Block Erase, Full Chip Erase,<br>(Page Buffer) Program and |

| Status Register Definition                          | OTP Program Performance                                          |

| Status register Definition                          | 2 Related Document Information                                   |

## LH28F640BFB-PTTL60 64Mbit (4Mbit×16) Page Mode Dual Work Flash MEMORY

- 64M density with 16Bit I/O Interface

- High Performance Reads

- 60/25ns 8-Word Page Mode

- Configurative 4-Plane Dual Work

- Flexible Partitioning

- Read operations during Block Erase or (Page Buffer)

Program

- Status Register for Each Partition

- Low Power Operation

- 2.7V Read and Write Operations

- V<sub>CCO</sub> for Input/Output Power Supply Isolation

- • Automatic Power Savings Mode Reduces  $I_{CCR}$  in Static Mode

- Enhanced Code + Data Storage

- 5µs Typical Erase/Program Suspends

- OTP (One Time Program) Block

- 4-Word Factory-Programmed Area

- 4-Word User-Programmable Area

- High Performance Program with Page Buffer

- 16-Word Page Buffer

- $5\mu s$ /Word (Typ.) at  $12V V_{pp}$

- Operating Temperature 0°C to +70°C

- CMOS Process (P-type silicon substrate)

- Flexible Blocking Architecture

- Eight 4K-word Parameter Blocks

- One-hundred and twenty-seven 32K-word Main Blocks

- Top Parameter Location

- Enhanced Data Protection Features

- Individual Block Lock and Block Lock-Down with Zero-Latency

- All blocks are locked at power-up or device reset.

- Absolute Protection with V<sub>PP</sub>≤V<sub>PPLK</sub>

- Block Erase, Full Chip Erase, (Page Buffer) Word Program Lockout during Power Transitions

- Automated Erase/Program Algorithms

- 3.0V Low-Power 11µs/Word (Typ.) Programming

- 12V No Glue Logic 9µs/Word (Typ.) Production Programming and 0.5s Erase (Typ.)

- Cross-Compatible Command Support

- · Basic Command Set

- Common Flash Interface (CFI)

- Extended Cycling Capability

- Minimum 100,000 Block Erase Cycles

- 0.8mm pitch 60-Ball CSP

- ETOX<sup>TM\*</sup> Flash Technology

- Not designed or rated as radiation hardened

The product, which is 4-Plane Page Mode Dual Work (Simultaneous Read while Erase/Program) Flash memory, is a low power, high density, low cost, nonvolatile read/write storage solution for a wide range of applications. The product can operate at  $V_{CC}$ =2.7V-3.6V and  $V_{PP}$ =1.65V-3.6V or 11.7V-12.3V. Its low voltage operation capability greatly extends battery life for portable applications.

The product provides high performance asynchronous page mode. It allows code execution directly from Flash, thus eliminating time consuming wait states. Furthermore, its newly configurative partitioning architecture allows flexible dual work operation.

The memory array block architecture utilizes Enhanced Data Protection features, and provides separate Parameter and Main Blocks that provide maximum flexibility for safe nonvolatile code and data storage.

Fast program capability is provided through the use of high speed Page Buffer Program.

Special OTP (One Time Program) block provides an area to store permanent code such as a unique number.

\* ETOX is a trademark of Intel Corporation.

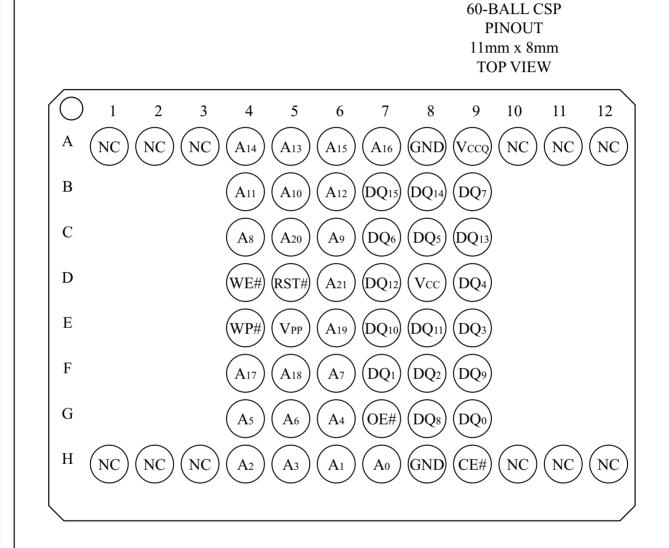

Figure 1. 0.8mm pitch 60-Ball CSP Pinout

Table 1. Pin Descriptions

| Symbol                            | Type             | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> -A <sub>21</sub>   | INPUT            | ADDRESS INPUTS: Inputs for addresses. 64M: A <sub>0</sub> -A <sub>21</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DQ <sub>0</sub> -DQ <sub>15</sub> | INPUT/<br>OUTPUT | DATA INPUTS/OUTPUTS: Inputs data and commands during CUI (Command User Interface) write cycles, outputs data during memory array, status register, query code, identifier code and partition configuration register code reads. Data pins float to high-impedance (High Z) when the chip or outputs are deselected. Data is internally latched during an erase or program cycle.                                                                                                                                                                                                                                                                                    |

| CE#                               | INPUT            | CHIP ENABLE: Activates the device's control logic, input buffers, decoders and sense amplifiers. CE#-high (V <sub>IH</sub> ) deselects the device and reduces power consumption to standby levels.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

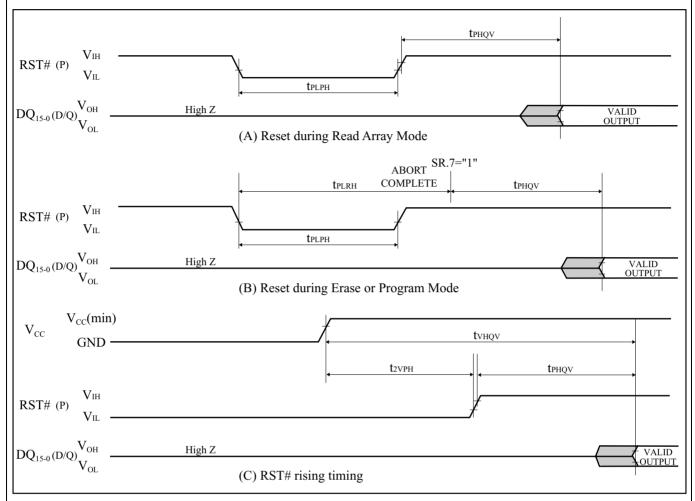

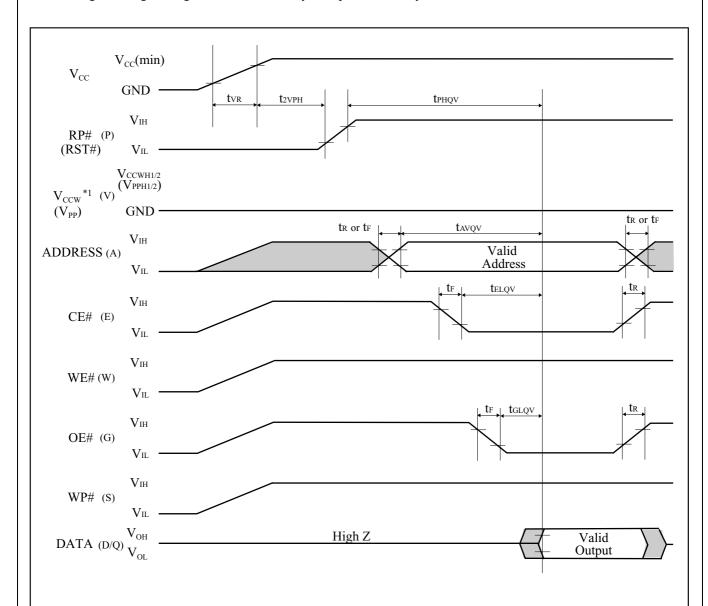

| RST#                              | INPUT            | RESET: When low $(V_{IL})$ , RST# resets internal automation and inhibits write operations which provides data protection. RST#-high $(V_{IH})$ enables normal operation. After power-up or reset mode, the device is automatically set to read array mode. RST# must be low during power-up/down.                                                                                                                                                                                                                                                                                                                                                                  |

| OE#                               | INPUT            | OUTPUT ENABLE: Gates the device's outputs during a read cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| WE#                               | INPUT            | WRITE ENABLE: Controls writes to the CUI and array blocks. Addresses and data are latched on the rising edge of CE# or WE# (whichever goes high first).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| WP#                               | INPUT            | WRITE PROTECT: When WP# is $V_{IL}$ , locked-down blocks cannot be unlocked. Erase or program operation can be executed to the blocks which are not locked and not locked-down. When WP# is $V_{IH}$ , lock-down is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| $ m V_{PP}$                       | INPUT            | MONITORING POWER SUPPLY VOLTAGE: $V_{PP}$ is not used for power supply pin. With $V_{PP} \le V_{PPLK}$ , block erase, full chip erase, (page buffer) program or OTP program cannot be executed and should not be attempted. Applying $12V\pm0.3V$ to $V_{PP}$ provides fast erasing or fast programming mode. In this mode, $V_{PP}$ is power supply pin. Applying $12V\pm0.3V$ to $V_{PP}$ during erase/program can only be done for a maximum of 1,000 cycles on each block. $V_{PP}$ may be connected to $12V\pm0.3V$ for a total of 80 hours maximum. Use of this pin at 12V beyond these limits may reduce block cycling capability or cause permanent damage. |

| V <sub>CC</sub>                   | SUPPLY           | DEVICE POWER SUPPLY (2.7V-3.6V): With $V_{CC} \le V_{LKO}$ , all write attempts to the flash memory are inhibited. Device operations at invalid $V_{CC}$ voltage (see DC Characteristics) produce spurious results and should not be attempted.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>CCQ</sub>                  | SUPPLY           | INPUT/OUTPUT POWER SUPPLY (2.7V-3.6V): Power supply for all input/output pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| GND                               | SUPPLY           | GROUND: Do not float any ground pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| NC                                |                  | NO CONNECT: Lead is not internally connected; it may be driven or floated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Table 2. Simultaneous Operation Modes Allowed with Four Planes<sup>(1, 2)</sup>

|                        |               |                | THEN T         | ТНЕ МО        | DES ALL         | OWED IN                   | THE OTI        | HER PAI        | RTITION I          | S:                 |                           |

|------------------------|---------------|----------------|----------------|---------------|-----------------|---------------------------|----------------|----------------|--------------------|--------------------|---------------------------|

| IF ONE PARTITION IS:   | Read<br>Array | Read<br>ID/OTP | Read<br>Status | Read<br>Query | Word<br>Program | Page<br>Buffer<br>Program | OTP<br>Program | Block<br>Erase | Full Chip<br>Erase | Program<br>Suspend | Block<br>Erase<br>Suspend |

| Read Array             | X             | X              | X              | X             | X               | X                         |                | X              |                    | X                  | X                         |

| Read ID/OTP            | X             | X              | X              | X             | X               | X                         |                | X              |                    | X                  | X                         |

| Read Status            | X             | X              | X              | X             | X               | X                         | X              | X              | X                  | X                  | X                         |

| Read Query             | X             | X              | X              | X             | X               | X                         |                | X              |                    | X                  | X                         |

| Word Program           | X             | X              | X              | X             |                 |                           |                |                |                    |                    | X                         |

| Page Buffer<br>Program | X             | X              | X              | X             |                 |                           |                |                |                    |                    | X                         |

| OTP Program            |               |                | X              |               |                 |                           |                |                |                    |                    |                           |

| Block Erase            | X             | X              | X              | X             |                 |                           |                |                |                    |                    |                           |

| Full Chip Erase        |               |                | X              |               |                 |                           |                |                |                    |                    |                           |

| Program<br>Suspend     | X             | X              | X              | X             |                 |                           |                |                |                    |                    | X                         |

| Block Erase<br>Suspend | X             | X              | X              | X             | X               | X                         |                |                |                    | X                  |                           |

### NOTES:

- "X" denotes the operation available.

Configurative Partition Dual Work Restrictions:

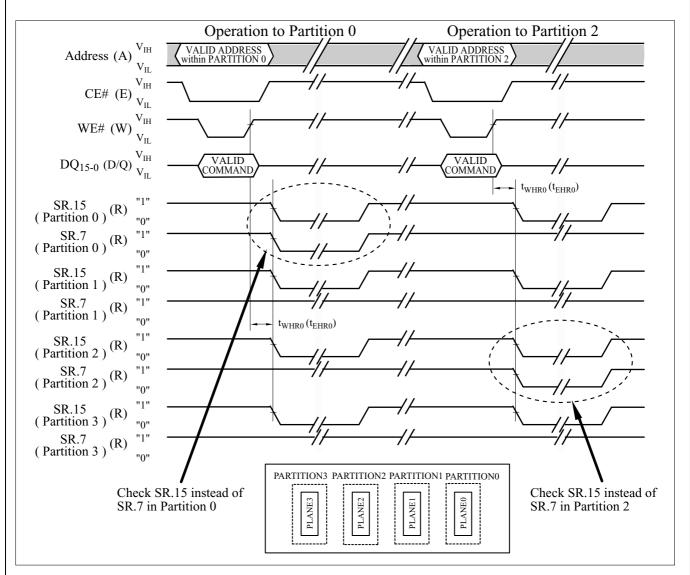

Status register reflects partition state, not WSM (Write State Machine) state - this allows a status register for each partition. Only one partition can be erased or programmed at a time - no command queuing. Commands must be written to an address within the block targeted by that command.

#### BLOCK NUMBER ADDRESS RANGE 3FF000H - 3FFFFFH 4K-WORD 134 3FE000H - 3FEFFFH 4K-WORD 133 3FD000H - 3FDFFFH 4K-WORD 132 3FC000H - 3FCFFFH 4K-WORD 131 3FB000H - 3FBFFFH 130 4K-WORD 3FA000H - 3FAFFFH 129 4K-WORD BLOCK NUMBER ADDRESS RANGE 4K-WORD 3F9000H - 3F9FFFH 128 1F8000H - 1FFFFFH 3F8000H - 3F8FFFH 4K-WORD 32K-WORD 1F0000H - 1F7FFFH 32K-WORD 3F0000H - 3F7FFFH 32K-WORD 1E8000H - 1EEEEH 125 32K-WORD 3E8000H - 3EFFFFH 61 32K-WORD 1E0000H - 1E7FFFH 3E0000H - 3E7FFFH 124 32K-WORD 60 32K-WORD PLANE 1D8000H - 1DFFFFH 123 32K-WORD 3D8000H - 3DFFFFH 59 32K-WORD 3D0000H - 3D7FFFH 1D0000H - 1D7FFFH 58 122 32K-WORD 32K-WORD 1C8000H - 1CFFFFH 3C8000H - 3CFFFFH 32K-WORD 121 32K-WORD 3C0000H - 3C7FFFH 56 1C0000H - 1C7FFFH 120 32K-WORD 32K-WORD 55 54 1B8000H - 1BFFFFH (PARAMETER 3B8000H - 3BFFFFH 119 32K-WORD 32K-WORD 3B0000H - 3B7FFFH PL ANE 32K-WORD 1B0000H - 1B7FFFH 118 32K-WORD 3A8000H - 3AFFFFH 53 32K-WORD 1A8000H - 1AFFFFH 32K-WORD 117 3A0000H - 3A7FFFH 52 1A0000H - 1A7FFFH 32K-WORD 32K-WORD 116 32K-WORD 398000H - 39FFFFH 51 198000H - 19FFFFH 32K-WORD 115 114 32K-WORD 390000H - 397FFFH 50 32K-WORD 190000H - 197FFFH (UNIFORM 113 32K-WORD 388000H - 38FFFFH 49 32K-WORD 188000H - 18FFFFH 32K-WORD 380000H - 387FFFH 48 32K-WORD 180000H - 187FFFH 112 PLANE3 32K-WORD 378000H - 37FFFFH 47 32K-WORD 178000H - 17FFFFH 111 32K-WORD 32K-WORD 370000H - 377FFFH 46 170000H - 177FFFH 110 168000H - 16FFFFH 109 32K-WORD 368000H - 36FFFFH 45 32K-WORD 160000H - 167FFFH 108 32K-WORD 360000H - 367FFFH 44 32K-WORD **PLANE1** 158000H - 15FFFFH 358000H - 35FFFFH 107 32K-WORD 43 32K-WORD 350000H - 357FFFH 42 150000H - 157FFFH 106 32K-WORD 32K-WORD 348000H - 34FFFFH 41 148000H - 14FFFFH 105 32K-WORD 32K-WORD 340000H - 347FFFH 40 140000H - 147FFFH 32K-WORD 104 32K-WORD 338000H - 33FFFFH 39 138000H - 13FFFFH 103 32K-WORD 32K-WORD 130000H - 137FFFH 32K-WORD 330000H - 337FFFH 38 32K-WORD 102 128000H - 12FFFFH 101 32K-WORD 328000H - 32FFFFH 37 32K-WORD 320000H - 327FFFH 120000H - 127FFFH 100 32K-WORD 36 32K-WORD 32K-WORD 318000H - 31FFFFH 32K-WORD 118000H - 11FFFFH 99 32K-WORD 310000H - 317FFFH 32K-WORD 110000H - 117FFFH 98 97 32K-WORD 308000H - 30FFFFH 33 32K-WORD 108000H - 10FFFFH 96 32K-WORD 300000H - 307FFFH 32K-WORD 100000H - 107FFFH 2F8000H - 2FFFFFH OF8000H - OFFFFFH 32K-WORD 32K-WORD 95 2F0000H - 2F7FFFH 30 0F0000H - 0F7FFFH 94 32K-WORD 32K-WORD 93 2E8000H - 2EFFFFH 0E8000H - 0EFFFFH 32K-WORD 32K-WORD 0E0000H - 0E7FFFH 2E0000H - 2E7FFFH 92 32K-WORD 28 32K-WORD 2D8000H - 2DFFFFH 91 27 0D8000H - 0DFFFFH 32K-WORD 32K-WORD 2D0000H - 2D7FFFH 32K-WORD 0D0000H - 0D7FFFH 90 32K-WORD 26 89 32K-WORD 2C8000H - 2CFFFFH 32K-WORD 0C8000H - 0CFFFFH 2C0000H - 2C7FFFH 0C0000H - 0C7FFFH 88 32K-WORD 24 32K-WORD 23 22 21 20 2B8000H - 2BFFFFH 0B8000H - 0BFFFFH 87 32K-WORD 32K-WORD ANE) 2B0000H - 2B7FFFH 32K-WORD 0B0000H - 0B7FFFH 86 32K-WORD 85 32K-WORD 2A8000H - 2AFFFFH 32K-WORD 0A8000H - 0AFFFFH 84 32K-WORD 2A0000H - 2A7FFFH 32K-WORD 0A0000H - 0A7FFFH PL 298000H - 29FFFFH P 098000H - 09FFFFH 83 32K-WORD 19 32K-WORD 290000H - 297FFFH 090000H - 097FFFH 32K-WORD 82 18 32K-WORD (UNIFORM PLANEO (UNIFORM 288000H - 28FFFFH 088000H - 08FFFFH 32K-WORD 81 32K-WORD 17 280000H - 287FFFH 080000H - 087FFFH 80 32K-WORD 16 32K-WORD 278000H - 27FFFFH 078000H - 07FFFFH 79 32K-WORD 15 32K-WORD 270000H - 277FFFH 070000H - 077FFFH 32K-WORD 78 14 32K-WORD 268000H - 26FFFFH 068000H - 06FFFFH 13 32K-WORD 77 32K-WORD 260000H - 267FFFH 12 060000H - 067FFFH 32K-WORD 76 32K-WORD PLANE2 258000H - 25FFFFH 058000H - 05FFFFH 75 32K-WORD 11 32K-WORD 74 32K-WORD 250000H - 257FFFH 10 32K-WORD 050000H - 057FFFH 248000H - 24FFFFH 32K-WORD 048000H - 04FFFFH 73 32K-WORD 9 040000H - 047FFFH 240000H - 247FFFH 8 32K-WORD 72 32K-WORD 038000H - 03FFFFH 238000H - 23FFFFH 32K-WORD 71 32K-WORD 030000H - 037FFFH 70 32K-WORD 230000H - 237FFFH 6 32K-WORD 028000H - 02FFFFH 32K-WORD 228000H - 22FFFFH 32K-WORD 69 020000H - 027FFFH 220000H - 227FFFH 32K-WORD 4 32K-WORD 68 018000H - 01FFFFH 218000H - 21FFFFH 67 32K-WORD 3 32K-WORD 010000H - 017FFFH 210000H - 217FFFH 66 32K-WORD 32K-WORD 008000H - 00FFFFH 208000H - 20FFFFH 32K-WORD 65 32K-WORD 000000H - 007FFFH 200000H - 207FFFH 64 32K-WORD

Figure 2. Memory Map (Top Parameter)

Table 3. Identifier Codes and OTP Address for Read Operation

|                           | Code                             | Address<br>[A <sub>15</sub> -A <sub>0</sub> ] | Data<br>[DQ <sub>15</sub> -DQ <sub>0</sub> ] | Notes |

|---------------------------|----------------------------------|-----------------------------------------------|----------------------------------------------|-------|

| Manufacturer Code         | Manufacturer Code                | 0000Н                                         | 00B0H                                        | 1     |

| Device Code               | Top Parameter Device Code        | 0001H                                         | 00B0H                                        | 1, 2  |

| Block Lock Configuration  | Block is Unlocked                |                                               | $DQ_0 = 0$                                   | 3     |

| Code                      | Block is Locked                  | Block<br>Address                              | $DQ_0 = 1$                                   | 3     |

|                           | Block is not Locked-Down         | + 2                                           | $DQ_1 = 0$                                   | 3     |

|                           | Block is Locked-Down             |                                               | $DQ_1 = 1$                                   | 3     |

| Device Configuration Code | Partition Configuration Register | 0006Н                                         | PCRC                                         | 1, 4  |

| OTP                       | OTP Lock                         | 0080Н                                         | OTP-LK                                       | 1, 5  |

|                           | OTP                              | 0081-0088H                                    | OTP                                          | 1, 6  |

### NOTES:

- 1. The address A<sub>21</sub>-A<sub>16</sub> are shown in below table for reading the manufacturer code, device code, device configuration code and OTP data.

- 2. Top parameter device has its parameter blocks in the plane3 (The highest address).

- 3. Block Address = The beginning location of a block address within the partition to which the Read Identifier Codes/OTP command (90H) has been written. DQ<sub>15</sub>-DQ<sub>2</sub> are reserved for future implementation.

- 4. PCRC=Partition Configuration Register Code.

- 5. OTP-LK=OTP Block Lock configuration.

- 6. OTP=OTP Block data.

Table 4. Identifier Codes and OTP Address for Read Operation on Partition Configuration<sup>(1)</sup> (64M-bit device)

| Partition C | Configuration I | Register (2) | Address (64M-bit device)            |

|-------------|-----------------|--------------|-------------------------------------|

| PCR.10      | PCR.9           | PCR.8        | [A <sub>21</sub> -A <sub>16</sub> ] |

| 0           | 0               | 0            | 00H                                 |

| 0           | 0               | 1            | 00H or 10H                          |

| 0           | 1               | 0            | 00H or 20H                          |

| 1           | 0               | 0            | 00H or 30H                          |

| 0           | 1               | 1            | 00H or 10H or 20H                   |

| 1           | 1               | 0            | 00H or 20H or 30H                   |

| 1           | 0               | 1            | 00H or 10H or 30H                   |

| 1           | 1               | 1            | 00H or 10H or 20H or 30H            |

- 1. The address to read the identifier codes or OTP data is dependent on the partition which is selected when writing the Read Identifier Codes/OTP command (90H).

- 2. Refer to Table 12 for the partition configuration register.

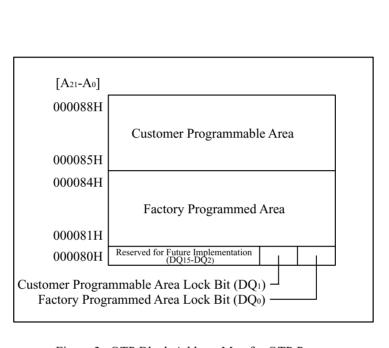

Figure 3. OTP Block Address Map for OTP Program (The area outside 80H~88H cannot be used.)

Table 5. Bus Operation<sup>(1, 2)</sup>

| Mode                         | Notes | RST#            | CE#             | OE#             | WE#             | Address                       | $V_{PP}$ | DQ <sub>0-15</sub>            |

|------------------------------|-------|-----------------|-----------------|-----------------|-----------------|-------------------------------|----------|-------------------------------|

| Read Array                   | 6     | $V_{IH}$        | $V_{IL}$        | $V_{IL}$        | $V_{IH}$        | X                             | X        | D <sub>OUT</sub>              |

| Output Disable               |       | $V_{IH}$        | V <sub>IL</sub> | $V_{IH}$        | V <sub>IH</sub> | X                             | X        | High Z                        |

| Standby                      |       | $V_{IH}$        | V <sub>IH</sub> | X               | X               | X                             | X        | High Z                        |

| Reset                        | 3     | $V_{IL}$        | X               | X               | X               | X                             | X        | High Z                        |

| Read Identifier<br>Codes/OTP | 6     | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | See<br>Table 3 and<br>Table 4 | X        | See<br>Table 3 and<br>Table 4 |

| Read Query                   | 6,7   | $V_{IH}$        | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | See<br>Appendix               | X        | See<br>Appendix               |

| Write                        | 4,5,6 | $V_{IH}$        | V <sub>IL</sub> | $V_{IH}$        | $V_{IL}$        | X                             | X        | D <sub>IN</sub>               |

- Refer to DC Characteristics. When V<sub>PP</sub>≤V<sub>PPLK</sub>, memory contents can be read, but cannot be altered.

X can be V<sub>IL</sub> or V<sub>IH</sub> for control pins and addresses, and V<sub>PPLK</sub> or V<sub>PPH1/2</sub> for V<sub>PP</sub> See DC Characteristics for V<sub>PPLK</sub> and V<sub>PPH1/2</sub> voltages.

RST# at GND±0.2V ensures the lowest power consumption.

- 4. Command writes involving block erase, full chip erase, (page buffer) program or OTP program are reliably executed when V<sub>PP</sub>=V<sub>PPH1/2</sub> and V<sub>CC</sub>=2.7V-3.6V.

5. Refer to Table 6 for valid D<sub>IN</sub> during a write operation.

6. Never hold OE# low and WE# low at the same timing.

- 7. Refer to Appendix of LH28F640BF series for more information about query code.

Table 6. Command Definitions<sup>(11)</sup>

|                                                  | Bus             |       | 1                   | First Bus Cyc       | ele           | Se                  | econd Bus Cy        | ycle                |

|--------------------------------------------------|-----------------|-------|---------------------|---------------------|---------------|---------------------|---------------------|---------------------|

| Command                                          | Cycles<br>Req'd | Notes | Oper <sup>(1)</sup> | Addr <sup>(2)</sup> | Data          | Oper <sup>(1)</sup> | Addr <sup>(2)</sup> | Data <sup>(3)</sup> |

| Read Array                                       | 1               |       | Write               | PA                  | FFH           |                     |                     |                     |

| Read Identifier Codes/OTP                        | ≥ 2             | 4     | Write               | PA                  | 90H           | Read                | IA or OA            | ID or OD            |

| Read Query                                       | ≥ 2             | 4     | Write               | PA                  | 98H           | Read                | QA                  | QD                  |

| Read Status Register                             | 2               |       | Write               | PA                  | 70H           | Read                | PA                  | SRD                 |

| Clear Status Register                            | 1               |       | Write               | PA                  | 50H           |                     |                     |                     |

| Block Erase                                      | 2               | 5     | Write               | BA                  | 20H           | Write               | BA                  | D0H                 |

| Full Chip Erase                                  | 2               | 5,9   | Write               | X                   | 30H           | Write               | X                   | D0H                 |

| Program                                          | 2               | 5,6   | Write               | WA                  | 40H or<br>10H | Write               | WA                  | WD                  |

| Page Buffer Program                              | ≥ 4             | 5,7   | Write               | WA                  | E8H           | Write               | WA                  | N-1                 |

| Block Erase and (Page Buffer)<br>Program Suspend | 1               | 8,9   | Write               | PA                  | ВОН           |                     |                     |                     |

| Block Erase and (Page Buffer)<br>Program Resume  | 1               | 8,9   | Write               | PA                  | D0H           |                     |                     |                     |

| Set Block Lock Bit                               | 2               |       | Write               | BA                  | 60H           | Write               | BA                  | 01H                 |

| Clear Block Lock Bit                             | 2               | 10    | Write               | BA                  | 60H           | Write               | BA                  | D0H                 |

| Set Block Lock-down Bit                          | 2               |       | Write               | BA                  | 60H           | Write               | BA                  | 2FH                 |

| OTP Program                                      | 2               | 9     | Write               | OA                  | СОН           | Write               | OA                  | OD                  |

| Set Partition Configuration Register             | 2               |       | Write               | PCRC                | 60H           | Write               | PCRC                | 04H                 |

- 1. Bus operations are defined in Table 5.

- 2. All addresses which are written at the first bus cycle should be the same as the addresses which are written at the second bus cycle.

- X=Any valid address within the device.

- PA=Address within the selected partition.

- IA=Identifier codes address (See Table 3 and Table 4).

- QA=Query codes address. Refer to Appendix of LH28F640BF series for details.

- BA=Address within the block being erased, set/cleared block lock bit or set block lock-down bit.

- WA=Address of memory location for the Program command or the first address for the Page Buffer Program command.

- OA=Address of OTP block to be read or programmed (See Figure 3).

- PCRC=Partition configuration register code presented on the address A<sub>0</sub>-A<sub>15</sub>.

- 3. ID=Data read from identifier codes. (See Table 3 and Table 4).

- QD=Data read from query database. Refer to Appendix of LH28F640BF series for details.

- SRD=Data read from status register. See Table 10 and Table 11 for a description of the status register bits.

- WD=Data to be programmed at location WA. Data is latched on the rising edge of WE# or CE# (whichever goes high first) during command write cycles.

- OD=Data within OTP block. Data is latched on the rising edge of WE# or CE# (whichever goes high first) during command write cycles.

- N-1=N is the number of the words to be loaded into a page buffer.

- 4. Following the Read Identifier Codes/OTP command, read operations access manufacturer code, device code, block lock configuration code, partition configuration register code and the data within OTP block (See Table 3 and Table 4).

- The Read Query command is available for reading CFI (Common Flash Interface) information.

- 5. Block erase, full chip erase or (page buffer) program cannot be executed when the selected block is locked. Unlocked block can be erased or programmed when RST# is  $V_{IH}$ .

- 6. Either 40H or 10H are recognized by the CUI (Command User Interface) as the program setup.

- 7. Following the third bus cycle, input the program sequential address and write data of "N" times. Finally, input the any valid address within the target block to be programmed and the confirm command (D0H). Refer to Appendix of

LH28F640BF series for details.

- 8. If the program operation in one partition is suspended and the erase operation in other partition is also suspended, the suspended program operation should be resumed first, and then the suspended erase operation should be resumed next.

- 9. Full chip erase and OTP program operations can not be suspended. The OTP Program command can not be accepted while the block erase operation is being suspended.

- 10. Following the Clear Block Lock Bit command, block which is not locked-down is unlocked when WP# is V<sub>IL</sub>. When WP# is V<sub>IH</sub>, lock-down bit is disabled and the selected block is unlocked regardless of lock-down configuration.

11. Commands other than those shown above are reserved by SHARP for future device implementations and should not be

- used.

Table 7. Functions of Block Lock<sup>(5)</sup> and Block Lock-Down

|                      |     | Cu                             | rrent State  |                   | (2)                       |

|----------------------|-----|--------------------------------|--------------|-------------------|---------------------------|

| State                | WP# | DQ <sub>1</sub> <sup>(1)</sup> | $DQ_0^{(1)}$ | State Name        | Erase/Program Allowed (2) |

| [000]                | 0   | 0                              | 0            | Unlocked          | Yes                       |

| $[001]^{(3)}$        | 0   | 0                              | 1            | Locked            | No                        |

| [011]                | 0   | 1                              | 1            | Locked-down       | No                        |

| [100]                | 1   | 0                              | 0            | Unlocked          | Yes                       |

| [101] <sup>(3)</sup> | 1   | 0                              | 1            | Locked            | No                        |

| [110] <sup>(4)</sup> | 1   | 1                              | 0            | Lock-down Disable | Yes                       |

| [111]                | 1   | 1                              | 1            | Lock-down Disable | No                        |

#### NOTES:

- 1.  $DQ_0=1$ : a block is locked;  $DQ_0=0$ : a block is unlocked. DQ<sub>1</sub>=1: a block is locked-down; DQ<sub>1</sub>=0: a block is not locked-down.

- 2. Erase and program are general terms, respectively, to express: block erase, full chip erase and (page buffer) program operations.

- 3. At power-up or device reset, all blocks default to locked state and are not locked-down, that is,

- [001] (WP#=0) or [101] (WP#=1), regardless of the states before power-off or reset operation. 4. When WP# is driven to  $V_{\rm IL}$  in [110] state, the state changes to [011] and the blocks are automatically locked.

- 5. OTP (One Time Program) block has the lock function which is different from those described above.

Table 8. Block Locking State Transitions upon Command Write<sup>(4)</sup>

|       | Curren | t State         |        | Result after Lock Command Written (Next State) |                           |                              |  |  |

|-------|--------|-----------------|--------|------------------------------------------------|---------------------------|------------------------------|--|--|

| State | WP#    | DQ <sub>1</sub> | $DQ_0$ | Set Lock <sup>(1)</sup>                        | Clear Lock <sup>(1)</sup> | Set Lock-down <sup>(1)</sup> |  |  |

| [000] | 0      | 0               | 0      | [001]                                          | No Change                 | [011] <sup>(2)</sup>         |  |  |

| [001] | 0      | 0               | 1      | No Change <sup>(3)</sup>                       | [000]                     | [011]                        |  |  |

| [011] | 0      | 1               | 1      | No Change                                      | No Change                 | No Change                    |  |  |

| [100] | 1      | 0               | 0      | [101]                                          | No Change                 | [111] <sup>(2)</sup>         |  |  |

| [101] | 1      | 0               | 1      | No Change                                      | [100]                     | [111]                        |  |  |

| [110] | 1      | 1               | 0      | [111]                                          | No Change                 | [111] <sup>(2)</sup>         |  |  |

| [111] | 1      | 1               | 1      | No Change                                      | [110]                     | No Change                    |  |  |

- 1. "Set Lock" means Set Block Lock Bit command, "Clear Lock" means Clear Block Lock Bit command and "Set Lock-down" means Set Block Lock-Down Bit command.

- 2. When the Set Block Lock-Down Bit command is written to the unlocked block (DQ $_0$ =0), the corresponding block is locked-down and automatically locked at the same time.

- 3. "No Change" means that the state remains unchanged after the command written.

- 4. In this state transitions table, assumes that WP# is not changed and fixed  $V_{IL}$  or  $V_{IH}$ .

Table 9. Block Locking State Transitions upon WP# Transition<sup>(4)</sup>

| D : C++                         |       | Current S | State           |        | Result after WP# Transition (Next State) |                        |  |

|---------------------------------|-------|-----------|-----------------|--------|------------------------------------------|------------------------|--|

| Previous State                  | State | WP#       | DQ <sub>1</sub> | $DQ_0$ | WP#=0→1 <sup>(1)</sup>                   | WP#=1→0 <sup>(1)</sup> |  |

| -                               | [000] | 0         | 0               | 0      | [100]                                    | -                      |  |

| -                               | [001] | 0         | 0               | 1      | [101]                                    | -                      |  |

| [110] <sup>(2)</sup>            | [011] | 0         | 1               | 1      | [110]                                    | -                      |  |

| Other than [110] <sup>(2)</sup> | [011] | 0         | 1               |        | [111]                                    | -                      |  |

| -                               | [100] | 1         | 0               | 0      | -                                        | [000]                  |  |

| -                               | [101] | 1         | 0               | 1      | -                                        | [001]                  |  |

| -                               | [110] | 1         | 1               | 0      | -                                        | [011] <sup>(3)</sup>   |  |

| -                               | [111] | 1         | 1               | 1      | -                                        | [011]                  |  |

- 1. "WP#=0 $\rightarrow$ 1" means that WP# is driven to  $V_{IH}$  and "WP#=1 $\rightarrow$ 0" means that WP# is driven to  $V_{IL}$ .

- 2. State transition from the current state [011] to the next state depends on the previous state.

- 3. When WP# is driven to  $V_{\rm IL}$  in [110] state, the state changes to [011] and the blocks are automatically locked.

- 4. In this state transitions table, assumes that lock configuration commands are not written in previous, current and next state.

| Table 10. Status Register Definition | Table 10. | Status F | Register | Definition |

|--------------------------------------|-----------|----------|----------|------------|

|--------------------------------------|-----------|----------|----------|------------|

| R    | R    | R      | R      | R    | R     | R   | R |

|------|------|--------|--------|------|-------|-----|---|

| 15   | 14   | 13     | 12     | 11   | 10    | 9   | 8 |

| WSMS | BESS | BEFCES | PBPOPS | VPPS | PBPSS | DPS | R |

| 7    | 6    | 5      | 4      | 3    | 2     | 1   | 0 |

SR.15 - SR.8 = RESERVED FOR FUTURE ENHANCEMENTS (R)

NOTES:

SR.7 = WRITE STATE MACHINE STATUS (WSMS)

- 1 = Ready

- 0 = Busy

SR.6 = BLOCK ERASE SUSPEND STATUS (BESS)

- 1 = Block Erase Suspended

- 0 = Block Erase in Progress/Completed

SR.5 = BLOCK ERASE AND FULL CHIP ERASE STATUS (BEFCES)

- 1 = Error in Block Erase or Full Chip Erase

- 0 = Successful Block Erase or Full Chip Erase

SR.4 = (PAGE BUFFER) PROGRAM AND OTP PROGRAM STATUS (PBPOPS)

- 1 = Error in (Page Buffer) Program or OTP Program

- 0 = Successful (Page Buffer) Program or OTP Program

$SR.3 = V_{PP} STATUS (VPPS)$

- $1 = V_{pp}$  LOW Detect, Operation Abort

- $0 = V_{PP} OK$

SR.2 = (PAGE BUFFER) PROGRAM SUSPEND STATUS (PBPSS)

- 1 = (Page Buffer) Program Suspended

- 0 = (Page Buffer) Program in Progress/Completed

SR.1 = DEVICE PROTECT STATUS (DPS)

- 1 = Erase or Program Attempted on a Locked Block, Operation Abort

- 0 = Unlocked

Status Register indicates the status of the partition, not WSM (Write State Machine). Even if the SR.7 is "1", the WSM may be occupied by the other partition when the device is set to 2, 3 or 4 partitions configuration.

Check SR.7 to determine block erase, full chip erase, (page buffer) program or OTP program completion. SR.6 - SR.1 are invalid while SR.7="0".

If both SR.5 and SR.4 are "1"s after a block erase, full chip erase, (page buffer) program, set/clear block lock bit, set block lock-down bit, set partition configuration register attempt, an improper command sequence was entered.

SR.3 does not provide a continuous indication of  $V_{PP}$  level. The WSM interrogates and indicates the  $V_{PP}$  level only after Block Erase, Full Chip Erase, (Page Buffer) Program or OTP Program command sequences. SR.3 is not guaranteed to report accurate feedback when  $V_{PP} \neq V_{PPH1}$ ,  $V_{PPH2}$  or  $V_{PPLK}$ .

SR.1 does not provide a continuous indication of block lock bit. The WSM interrogates the block lock bit only after Block Erase, Full Chip Erase, (Page Buffer) Program or OTP Program command sequences. It informs the system, depending on the attempted operation, if the block lock bit is set. Reading the block lock configuration codes after writing the Read Identifier Codes/OTP command indicates block lock bit status.

SR.15 - SR.8 and SR.0 are reserved for future use and should be masked out when polling the status register.

SR.0 = RESERVED FOR FUTURE ENHANCEMENTS (R)

| Table 11. | Extended | Status | Register | Definition |

|-----------|----------|--------|----------|------------|

|-----------|----------|--------|----------|------------|

| R   | R  | R  | R  | R  | R  | R | R |

|-----|----|----|----|----|----|---|---|

| 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| SMS | R  | R  | R  | R  | R  | R | R |

| 7   | 6  | 5  | 4  | 3  | 2. | 1 | 0 |

### XSR.15-8 = RESERVED FOR FUTURE ENHANCEMENTS (R)

XSR.7 = STATE MACHINE STATUS (SMS)

- 1 = Page Buffer Program available

- 0 = Page Buffer Program not available

XSR.6-0 = RESERVED FOR FUTURE ENHANCEMENTS (R)

### NOTES:

After issue a Page Buffer Program command (E8H), XSR.7="1" indicates that the entered command is accepted. If XSR.7 is "0", the command is not accepted and a next Page Buffer Program command (E8H) should be issued again to check if page buffer is available or not.

XSR.15-8 and XSR.6-0 are reserved for future use and should be masked out when polling the extended status register.

|    |    |    | Č  | Č  |     |     |     |

|----|----|----|----|----|-----|-----|-----|

| R  | R  | R  | R  | R  | PC2 | PC1 | PC0 |

| 15 | 14 | 13 | 12 | 11 | 10  | 9   | 8   |

| R  | R  | R  | R  | R  | R   | R   | R   |

| 7  | 6  | 5  | 1  | 2  | 2   | 1   | 0   |

Table 12. Partition Configuration Register Definition

### PCR.15-11 = RESERVED FOR FUTURE ENHANCEMENTS (R)

PCR.10-8 = PARTITION CONFIGURATION (PC2-0)

000 = No partitioning. Dual Work is not allowed.

001 = Plane1-3 are merged into one partition. (default in a bottom parameter device)

010 = Plane 0-1 and Plane2-3 are merged into one partition respectively.

100 = Plane 0-2 are merged into one partition. (default in a top parameter device)

011 = Plane 2-3 are merged into one partition. There are three partitions in this configuration. Dual work operation is available between any two partitions.

110 = Plane 0-1 are merged into one partition. There are three partitions in this configuration. Dual work operation is available between any two partitions.

101 = Plane 1-2 are merged into one partition. There are three partitions in this configuration. Dual work operation is available between any two partitions.

111 = There are four partitions in this configuration.

Each plane corresponds to each partition respectively. Dual work operation is available between any two partitions.

### PCR.7-0 = RESERVED FOR FUTURE ENHANCEMENTS (R)

### NOTES:

After power-up or device reset, PCR10-8 (PC2-0) is set to "001" in a bottom parameter device and "100" in a top parameter device.

See Figure 4 for the detail on partition configuration.

PCR.15-11 and PCR.7-0 are reserved for future use and should be masked out when checking the partition configuration register.

| PC2 PC1 PC0 | PARTITIONING FOR DUAL WORK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PC2 PC1 PC0 PARTITIONING FOR DUAL WORK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 0 0       | PLANE3  PLANE1  PLANE0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PARTITION2 PARTITION1 PARTITION0  0 1 1  BLANE  BLANE  DELA  DEL  DEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0 0 1       | PLANE3 PLANE3 PLANE3 PLANE1 PLANE9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PARTITION2 PARTITION1 PARTITION0  1 1 0  LANE  PARTITION2 PARTITION1 PARTITION0  1 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0 1 0       | DRANE3  PLANE3  PLANE3  PLANE3  BLANE3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PARTITION2 PARTITION1 PARTITION0  1 0 1 EBUNET BLANE  PARTITION2 PARTITION1 PARTITION0  1 0 1 EBUNET BLANE  1 0 1 EBUNET BLANE |

| 1 0 0       | ONOITITAAP INOITITAAP INOITITAAPI | PARTITION3 PARTITION2 PARTITION1 PARTITION0  1 1 1 1 EBUN BIT STATE OF THE PARTITION P |

Figure 4. Partition Configuration

### 1 Electrical Specifications

### 1.1 Absolute Maximum Ratings\*

Operating Temperature

During Read, Erase and Program ..... 0°C to +70°C (1)

Storage Temperature

During under Bias.....-10°C to +80°C During non Bias....-65°C to +125°C

Voltage On Any Pin

(except  $V_{CC}$  and  $V_{PP}$ )......-0.5V to  $V_{CC}+0.5V^{(2)}$

$V_{CC}$  and  $V_{CCO}$  Supply Voltage ...... -0.2V to +3.9V <sup>(2)</sup>

$V_{pp}$  Supply Voltage .....-0.2V to +12.6V (2, 3, 4)

Output Short Circuit Current......100mA (5)

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

### NOTES:

- 1. Operating temperature is for commercial temperature product defined by this specification.

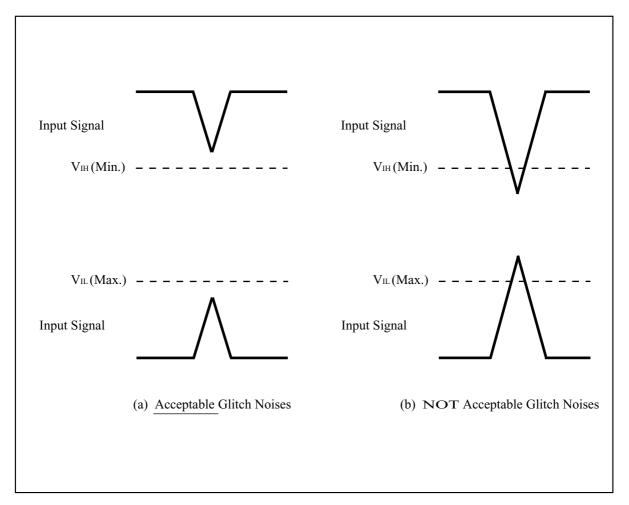

- 2. All specified voltages are with respect to GND. Minimum DC voltage is -0.5V on input/output pins and -0.2V on  $V_{CC}$  and  $V_{PP}$  pins. During transitions, this level may undershoot to -2.0V for periods <20ns. Maximum DC voltage on input/output pins is  $V_{CC}$ +0.5V which, during transitions, may overshoot to  $V_{CC}$ +2.0V for periods <20ns.

- 3. Maximum DC voltage on V<sub>PP</sub> may overshoot to +13.0V for periods <20ns.

- 4.  $V_{PP}$  erase/program voltage is normally 2.7V-3.6V. Applying 11.7V-12.3V to  $V_{PP}$  during erase/program can be done for a maximum of 1,000 cycles on the main blocks and 1,000 cycles on the parameter blocks.  $V_{PP}$  may be connected to 11.7V-12.3V for a total of 80 hours maximum.

- 5. Output shorted for no more than one second. No more than one output shorted at a time.

### 1.2 Operating Conditions

| Parameter                                                                   | Symbol          | Min.    | Тур. | Max.  | Unit   | Notes |

|-----------------------------------------------------------------------------|-----------------|---------|------|-------|--------|-------|

| Operating Temperature                                                       | $T_A$           | 0       | +25  | +70   | °C     |       |

| V <sub>CC</sub> Supply Voltage                                              | V <sub>CC</sub> | 2.7     | 3.0  | 3.6   | V      | 1     |

| I/O Supply Voltage                                                          | $V_{CCQ}$       | 2.7     | 3.0  | 3.6   | V      | 1     |

| V <sub>PP</sub> Voltage when Used as a Logic Control                        | $V_{PPH1}$      | 1.65    | 3.0  | 3.6   | V      | 1     |

| V <sub>PP</sub> Supply Voltage                                              | $V_{PPH2}$      | 11.7    | 12   | 12.3  | V      | 1, 2  |

| Main Block Erase Cycling: V <sub>PP</sub> =V <sub>PPH1</sub>                |                 | 100,000 |      |       | Cycles |       |

| Parameter Block Erase Cycling: V <sub>PP</sub> =V <sub>PPH1</sub>           |                 | 100,000 |      |       | Cycles |       |

| Main Block Erase Cycling: V <sub>PP</sub> =V <sub>PPH2</sub> , 80 hrs.      |                 |         |      | 1,000 | Cycles |       |

| Parameter Block Erase Cycling: V <sub>PP</sub> =V <sub>PPH2</sub> , 80 hrs. |                 |         |      | 1,000 | Cycles |       |

| Maximum V <sub>PP</sub> hours at V <sub>PPH2</sub>                          |                 |         |      | 80    | Hours  |       |

- 1. See DC Characteristics tables for voltage range-specific specification.

- 2. Applying  $V_{pp}$ =11.7V-12.3V during a erase or program can be done for a maximum of 1,000 cycles on the main blocks and 1,000 cycles on the parameter blocks. A permanent connection to  $V_{pp}$ =11.7V-12.3V is not allowed and can cause damage to the device.

## 1.2.1 Capacitance<sup>(1)</sup> (T<sub>A</sub>=+25°C, f=1MHz)

| Parameter          | Symbol           | Condition              | Min. | Тур. | Max. | Unit |

|--------------------|------------------|------------------------|------|------|------|------|

| Input Capacitance  | $C_{IN}$         | V <sub>IN</sub> =0.0V  |      | 4    | 7    | pF   |

| Output Capacitance | C <sub>OUT</sub> | V <sub>OUT</sub> =0.0V |      | 6    | 10   | pF   |

### NOTE:

1. Sampled, not 100% tested.

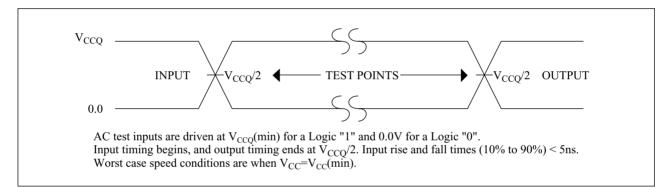

### 1.2.2 AC Input/Output Test Conditions

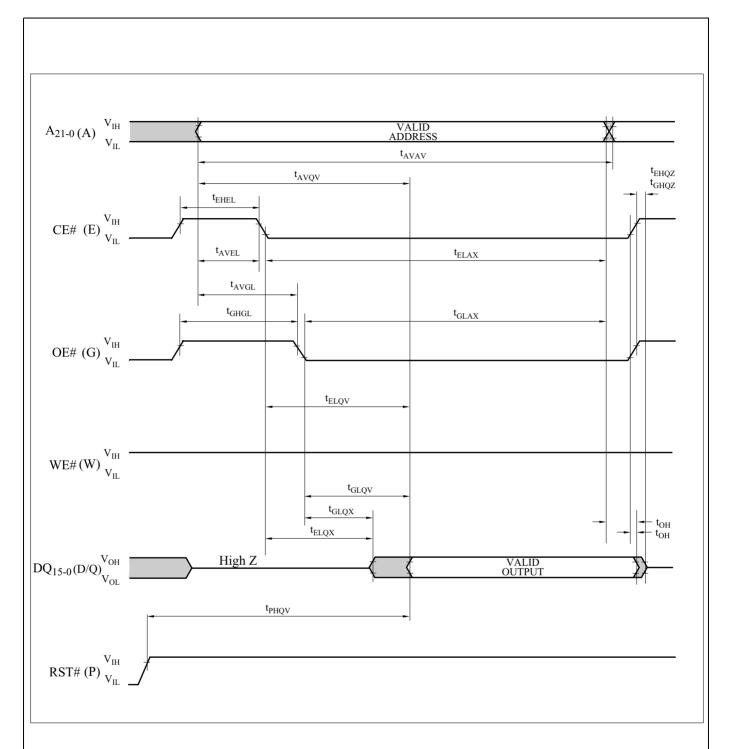

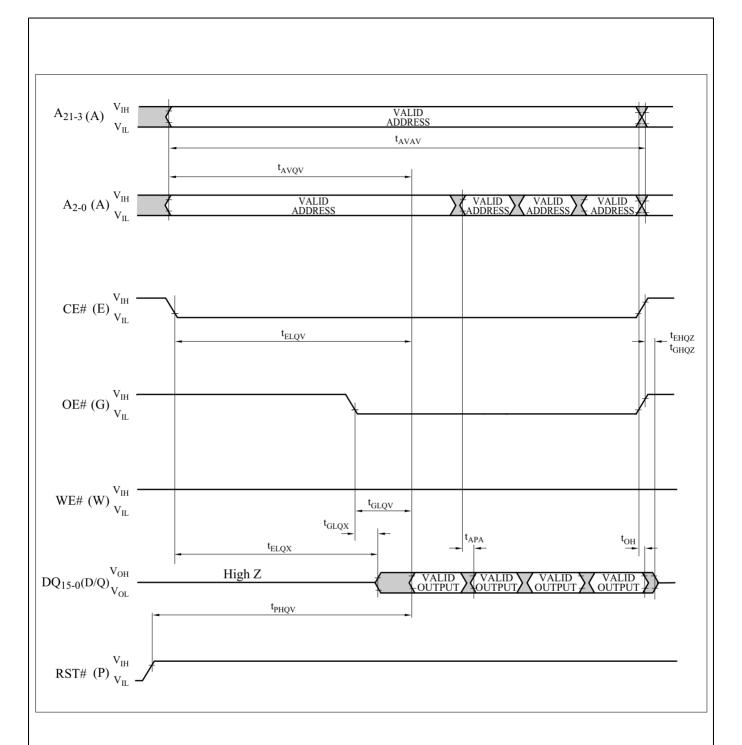

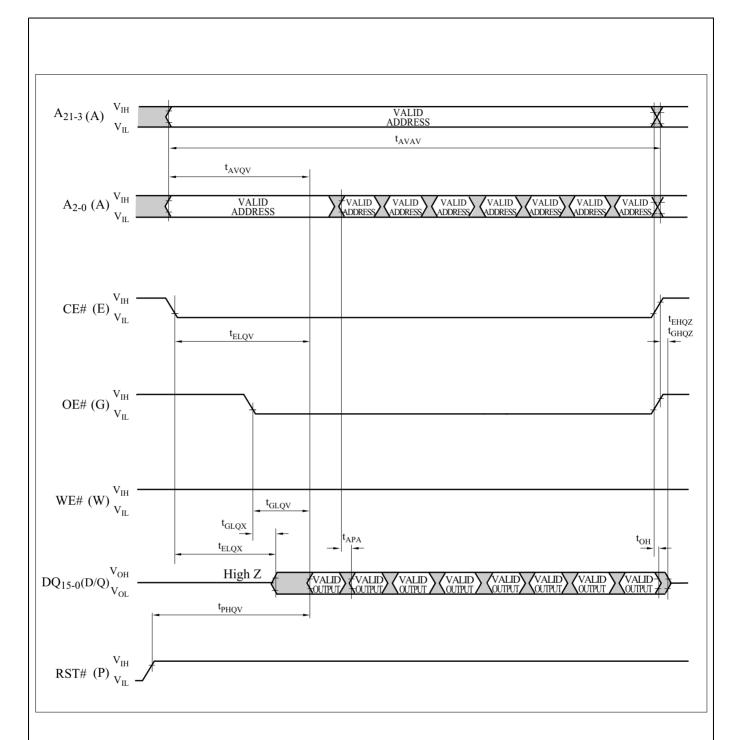

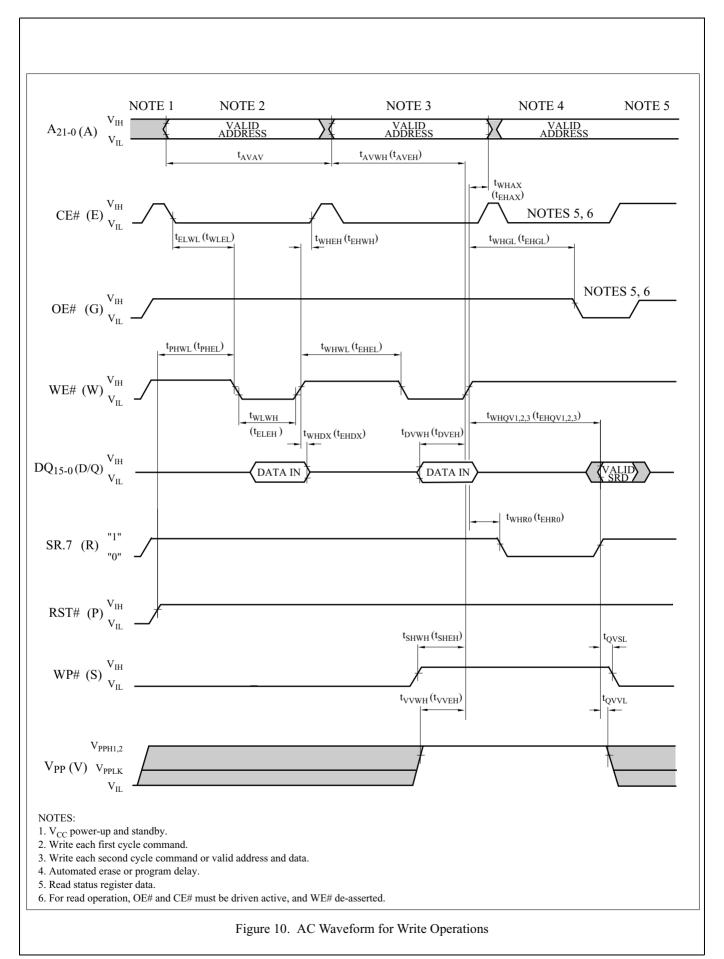

Figure 5. Transient Input/Output Reference Waveform for  $V_{CC}$ =2.7V-3.6V

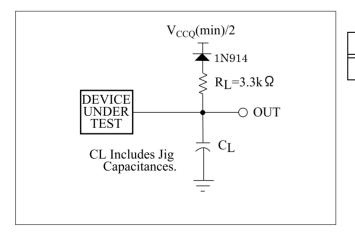

Figure 6. Transient Equivalent Testing Load Circuit

Table 13. Configuration Capacitance Loading Value

| Test Configuration       | $C_L(pF)$        |

|--------------------------|------------------|

| $V_{CC} = 2.7 V - 3.6 V$ | 30pF, 50pF, 70pF |

### 1.2.3 DC Characteristics

$V_{CC} = 2.7 \text{V} - 3.6 \text{V}$

| Symbol                                 | Paran                                                  | neter                           | Notes   | Min. | Тур. | Max. | Unit | Test Conditions                                                                                           |

|----------------------------------------|--------------------------------------------------------|---------------------------------|---------|------|------|------|------|-----------------------------------------------------------------------------------------------------------|

| $I_{LI}$                               | Input Load Current                                     |                                 | 1       | -1.0 |      | +1.0 | μΑ   | V <sub>CC</sub> =V <sub>CC</sub> Max.,                                                                    |

| $I_{LO}$                               | Output Leakage Cur                                     | Output Leakage Current          |         | -1.0 |      | +1.0 | μА   | V <sub>CCQ</sub> =V <sub>CCQ</sub> Max.,<br>V <sub>IN</sub> /V <sub>OUT</sub> =V <sub>CCQ</sub> or<br>GND |

| I <sub>CCS</sub>                       | V <sub>CC</sub> Standby Curren                         | V <sub>CC</sub> Standby Current |         |      | 4    | 20   | μΑ   | $V_{CC} = V_{CC} Max.,$ $CE = RST = V_{CCQ} \pm 0.2V,$ $WP = V_{CCQ} \text{ or GND}$                      |

| I <sub>CCAS</sub>                      | V <sub>CC</sub> Automatic Pow                          | er Savings Current              | 1,4     |      | 4    | 20   | μА   | V <sub>CC</sub> =V <sub>CC</sub> Max.,<br>CE#=GND±0.2V,<br>WP#=V <sub>CCQ</sub> or GND                    |

| $I_{CCD}$                              | V <sub>CC</sub> Reset Power-Do                         | own Current                     | 1       |      | 4    | 20   | μΑ   | RST#=GND±0.2V                                                                                             |

| ī                                      | Average V <sub>CC</sub> Read<br>Current<br>Normal Mode |                                 | 1,7     |      | 15   | 25   | mA   | V <sub>CC</sub> =V <sub>CC</sub> Max.,<br>CE#=V <sub>IL</sub> ,                                           |

| I <sub>CCR</sub>                       | Average V <sub>CC</sub> Read<br>Current<br>Page Mode   | 8 Word Read                     | 1,7     |      | 5    | 10   | mA   | OE#=V <sub>IH</sub> ,<br>f=5MHz                                                                           |

| $I_{CCW}$                              | V <sub>CC</sub> (Page Buffer) P                        | rogram Current                  | 1,5,7   |      | 20   | 60   | mA   | $V_{PP}=V_{PPH1}$                                                                                         |

| 1CCW                                   | VCC (Tage Bullet) T                                    | rogram Current                  | 1,5,7   |      | 10   | 20   | mA   | V <sub>PP</sub> =V <sub>PPH2</sub>                                                                        |

| Lagn                                   | V <sub>CC</sub> Block Erase, Fu                        | ıll Chip                        | 1,5,7   |      | 10   | 30   | mA   | V <sub>PP</sub> =V <sub>PPH1</sub>                                                                        |

| $I_{CCE}$                              | Erase Current                                          |                                 | 1,5,7   |      | 4    | 10   | mA   | V <sub>PP</sub> =V <sub>PPH2</sub>                                                                        |