# 8-BITS SINGLE MICROCONTROLLER with 16/32/64-Kbytes of FLASH, 256 byte +512 byte RAM

#### **FEATURES**

- 80C52 based architecture

- 256 Byte RAM internal RAM and 512 Bytes auxiliary RAM available

- Three 16-bit Timer/Counters

- · Full duplex serial channel

- Boolean processor

- · Power Save Mode:

- 1) Idle Mode

- 2) Power Down Mode waken up from interrupt level trigger mode

- Program memory lock

- Lock bits (3)

- Four 8-bit I/O ports, 32 I/O lines

- · Memory addressing capability

- 64K Program Memory and 64K Data Memory

- CMOS and TTL compatible

- Maximum speed ranges at Vcc = 5V is 40 MHz and most instructions execute in 0.3 µs

- · Packages available:

- 40-pin DIP

- 44-pin PLCC

- 44-pin PQFP

- 16K/32K/64K Byte Flash Memory with fast-pulse programming algorithm

- 36 I/O pins(above 44-pin package only)

- 8 interrupts vectors (above 44-pin package only)

- Low EMI mode

# **GENERAL DESCRIPTION**

IC89E54, IC89E58, IC89E64 are members of ICSI embedded microcontroller family. The IC89E54/58/64 uses the same powerful instruction set, has the same architecture, and is pin-to-pin compatible with standard 80C51 controller devices. They have IC89E54/58/64 all functions and some enhanced function is included. These enhanced functions include 512 bytes auxiliary memory, 36 I/O pins (44 pin package only), 8 interrupts (44 pin package only) with two-level priority, Power off flag, Low EMI mode, power down mode is waken up from interrupt level trigger mode.

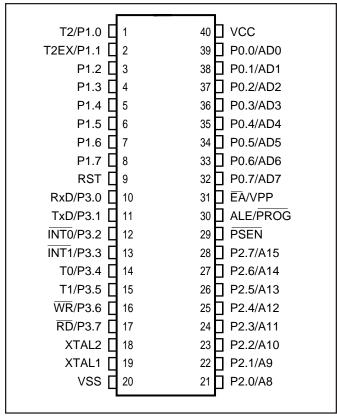

Figure 1. IC89E54/58/64 Pin Configuration: 40-pin DIP

ICSI reserves the right to make changes to its products at any time without notice in order to improve design and supply the best possible product. We assume no responsibility for any errors which may appear in this publication. © Copyright 2000, Integrated Circuit Solution Inc.

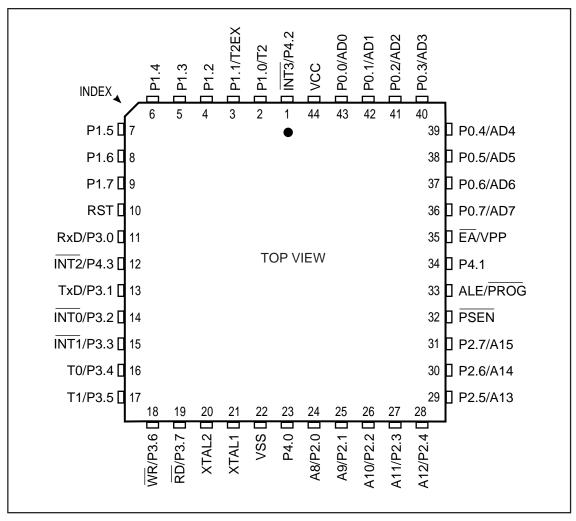

Figure 2. IC89E54/58/64 Pin Configuration: 44-pin PLCC

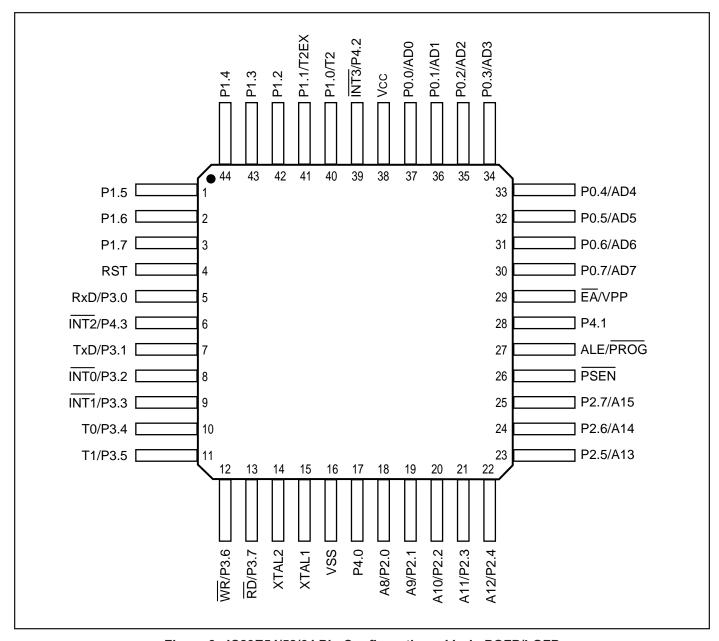

Figure 3. IC89E54/58/64 Pin Configuration: 44-pin PQFP/LQFP

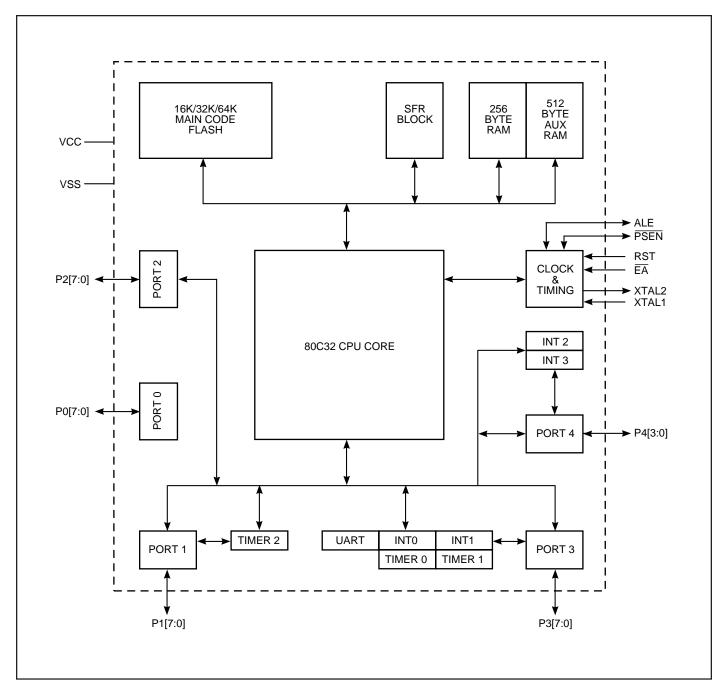

Figure 4. IC89E54/58/64 Block Diagram

**Table 1. Detailed Pin Description**

| Symbol    | PDIP   | PLCC  | PQFP     | I/O    | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------|--------|-------|----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0.0-P0.7 | 39-32  | 43-36 | 37-30    | I/O    | Port 0: Port 0 is an open-drain, bi-directional I/O port. Port 0 pins that have 1s written to them float and can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external program and data memory. In this application, it uses strong internal pullups when emitting 1s.                                                                                                                                                                                                                                                                                                                           |

|           |        |       |          |        | Port 0 also receives the command and code bytes during memory program and verification, and outputs the code bytes during program verification. External pullups are required during program verification.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P1.0-P1.7 | 1-8    | 2-9   | 40-44    | I/O    | Port 1: Port 1 is an 8-bit bi-directional I/O port with internal pullups. Port 1 pins that have 1s written to them are pulled high by the internal pullups and can be used as inputs. As inputs, port 1 pins that are externally pulled low will source current because of the internal pullups.  Port 1 also receives the low-order address byte during memory program and verification.                                                                                                                                                                                                                                                                              |

|           | 1<br>2 | 2 3   | 40<br>41 | I<br>I | T2(P1.0): Timer/counter 2 external count input. T2EX(P1.1): Timer/counter 2 trigger input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P2.0-P2.7 | 21-28  | 24-31 | 18-25    | I/O    | Port 2: Port 2 is an 8-bit bi-directional I/O port with internal pullups. Port 2 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 2 pins that are externally pulled low will source current because of the internal pullups. Port 2 emits the high order address byte during fetches from external program memory and during accesses to external data memory that used 16-bit addresses. In this application, it uses strong internal pullups when emitting 1s. During accesses to external data memory that use 8-bit addresses, port 2 emits the contents of the P2 special function register. |

|           |        |       |          |        | Port 2 also receives the high-order address bits from A13 to A8 and some control signals during Flash programming and verification. P2.6, P2.7 are the control signals while the chip programs and erases. P2.6 is a program command strobe signal. P2.7 is a data output enable signal.                                                                                                                                                                                                                                                                                                                                                                               |

Table 1. Detailed Pin Description (continued)

| Symbol    | PDIP  | PLCC      | PQFP    | I/O | Name and Function                                                                                                                                                                                                                                                                                |

|-----------|-------|-----------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3.0-P3.7 | 10-17 | 11, 13-19 | 5, 7-13 | I/O | Port 3: Port 3 is an 8-bit bi-directional I/O port with internal pullups. Port 3 pins that have 1s written to them are pulled high by the internal pullups and can be used as inputs. As inputs, port 3 pins that are externally pulled low will source current because of the internal pullups. |

|           |       |           |         |     | Port 3 also serves the special features of the IC89E54/58/64, as listed below:                                                                                                                                                                                                                   |

|           | 10    | 11        | 5       | I   | RxD (P3.0): Serial input port.                                                                                                                                                                                                                                                                   |

|           | 11    | 13        | 7       | Ο   | TxD (P3.1): Serial output port.                                                                                                                                                                                                                                                                  |

|           | 12    | 14        | 8       | I   | <b>INTO (P3.2):</b> External interrupt. Serve as A14 during memory program and verification.                                                                                                                                                                                                     |

|           | 13    | 15        | 9       | I   | <b>INT1 (P3.3):</b> External interrupt. Serve as A15 during memory program and verification.                                                                                                                                                                                                     |

|           | 14    | 16        | 10      | ı   | T0 (P3.4): Timer 0 external input.                                                                                                                                                                                                                                                               |

|           | 15    | 17        | 11      | I   | T1 (P3.5): Timer 1 external input.                                                                                                                                                                                                                                                               |

|           | 16    | 18        | 12      | 0   | <b>WR</b> (P3.6):External data memory write strobe. Control signal during memory program, verification and erase.                                                                                                                                                                                |

|           | 17    | 19        | 13      | 0   | RD (P3.7): External data memory read strobe. Control signal during memory program, verification and erase.                                                                                                                                                                                       |

| P4.0-P4.3 |       | 23        | 17      | I/O | Port 4: In mode 0, Port 4 is an 8-bit bi-directional I/O port                                                                                                                                                                                                                                    |

|           |       | 34        | 29      |     | with internal pullups. Port 4 pins that have 1s written to them are                                                                                                                                                                                                                              |

|           |       | 1         | 39      |     | pulled high by the internal pullups and can be used as inputs.                                                                                                                                                                                                                                   |

|           |       | 12        | 6       |     | As inputs, port 4 pins that are externally pulled low will source current because of the internal pullups.                                                                                                                                                                                       |

|           |       |           |         |     | In mode 1, 2, 3, Port 4 is an address strobe signal which appears with $\overline{RD}$ or $\overline{WR}$ signals.                                                                                                                                                                               |

|           |       | 12        | 6       |     | Port 4 also serves the special features, as listed below:                                                                                                                                                                                                                                        |

|           |       | 1         | 39      |     | INT2 (P4.3): External interrupt                                                                                                                                                                                                                                                                  |

|           |       |           |         |     | INT3 (P4.2): External interrupt                                                                                                                                                                                                                                                                  |

| RST       | 9     | 10        | 4       | I   | Reset: A high on this pin for two machine cycles while the oscillator is running resets the device. An internal resistor to VSS permits a power-on reset using only an external capacitor. A small internal resistor permits power-on reset using only a capacitor connected to VCC.             |

|           |       |           |         |     | RST is an input control signal during memory program and verification.                                                                                                                                                                                                                           |

| XTAL 2    | 18    | 20        | 14      | 0   | Crystal 2: Output from the inverting oscillator amplifier.                                                                                                                                                                                                                                       |

| XTAL 1    | 19    | 21        | 15      | I   | <b>Crystal 1:</b> Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                |

Table 1. Detailed Pin Description (continued)

| Symbol   | PDIP | PLCC | PQFP | I/O | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|------|------|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PSEN     | 29   | 32   | 26   | 0   | Program Store Enable: The read strobe to external program memory. When the device is executing code from the external program memory, PSEN is activated twice each machine cycle except that two PSEN activations are skipped during each access to external data memory. PSEN is not activated during fetches from internal program memory.  PSEN is an input control signal while memory program and verification. |

| ALE/PROG | 30   | 33   | 27   | I/O | Address Latch Enable: Output pulse for latching the low byte of the address during an address to the external memory. In normal operation, ALE is emitted at a constant rate of 1/6 the oscillator frequency, and can be used for external timing or clocking. Note that one ALE pulse is skipped during each access to external data memory.                                                                        |

|          |      |      |      |     | This pin is also the program pulse input (PROG) during programmable memory programming and erase.                                                                                                                                                                                                                                                                                                                    |

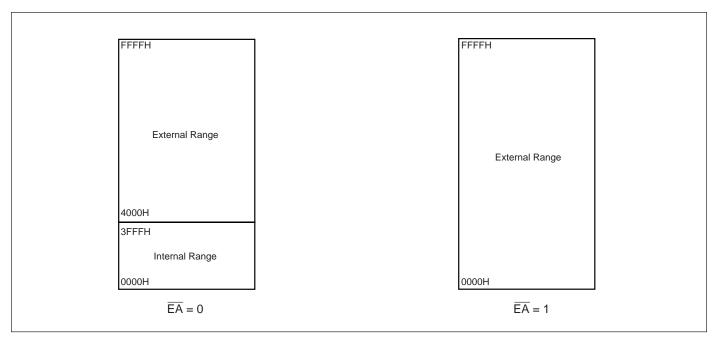

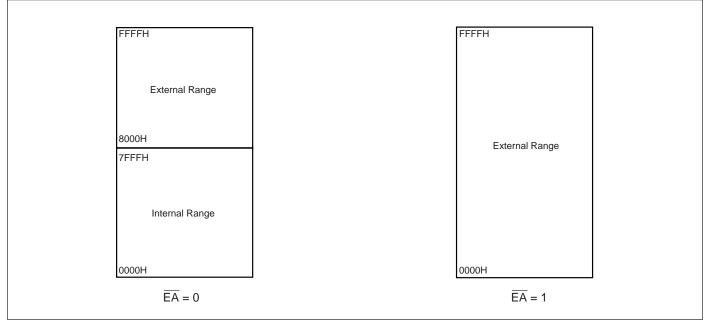

| EA/Vpp   | 31   | 35   | 29   | I   | External access enable: EA must be externally held low to enable the device to fetch code from external program memory locations 0000H to FFFFH. If EA is held high, the device executes from internal program memory unless the program counter contains an address grater than 3FFFH/7FFFH respecting to IC89C54/58 and the device always executes internal program memory in IC89C64.                             |

|          |      |      |      |     | This is also receives the 12 V programming enable voltage (Vpp) during Flash programming, when 12 V programming is selected.                                                                                                                                                                                                                                                                                         |

| Vss      | 20   | 22   | 16   |     | Ground: 0V reference.                                                                                                                                                                                                                                                                                                                                                                                                |

| Vcc      | 40   | 44   | 38   | I   | Power Supply: This is the power supply voltage for operation.                                                                                                                                                                                                                                                                                                                                                        |

### **OPERATING DESCRIPTION**

The detail description of the IC89E54/58/64 included in this description are:

- Memory Map and Registers

- Timer/Counters

- Serial Interface

- Interrupt System

- Other Information

- Flash Memory

# **MEMORY MAP AND REGISTERS**

# **Program Memory and data memory**

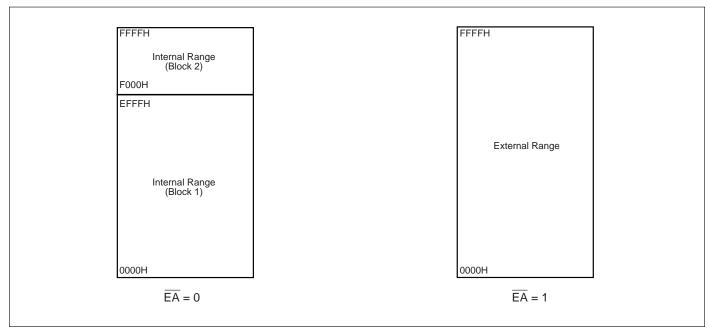

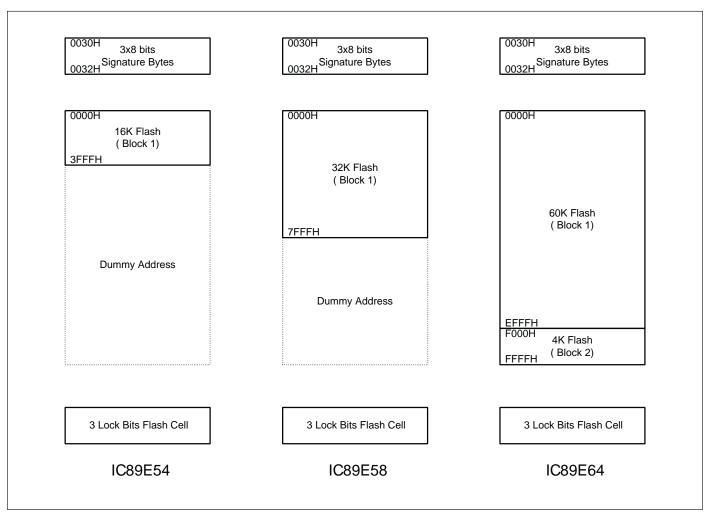

Table 2 shows program memory and data memory size versus three products. The IC89E54/58/64 series includes a standard IC80C32 and a 16K/32K/64K Flash Memory. The IC89E54/58/64 includes IC80C32, a 16K/32K/64K Flash and some enhanced functions. The figures 3~5 show IC89E54/58/64 program memory architecture and program memory access status versus EA pin. These enhanced functions are described in later descriptions. The program memory and data memory access ranges are listed table 1. The AUX RAM status is disable after reset, so MOVX instructions will access external RAM. If set ENARAM bit, the AUX RAM will be enabled and MOVX instructions will access AUX RAM in 0000H~01FFH, access external RAM in 0200H~FFFFH. Figure 6 shows the external data memory and AUX RAM accesses relation.

Table 2. Program memory and Data memory sizes

|         | Main Flash             | RAM Size             | AUX RAM Size          |

|---------|------------------------|----------------------|-----------------------|

| IC89E54 | 16K Bytes : [0H~3FFFH] | 256 Bytes : [ 0-FFH] | 512 Bytes : [ 0-1FFH] |

| IC89E58 | 32K Bytes : [0H~7FFFH] | 256 Bytes : [ 0-FFH] | 512 Bytes : [ 0-1FFH] |

| IC89E64 | 64K Bytes : [0H~FFFFH] | 256 Bytes : [ 0-FFH] | 512 Bytes : [ 0-1FFH] |

Figure 5. IC89E54 Flash Architecture

Figure 6. IC89E58 Flash Architecture

Figure 7. IC89E64 Flash Architecture

Figure 8. IC89E54/58/64 Data Memory Architecture

| F8H |                     |                  |                    |                     |                   |                    |                    |                   | FFH |

|-----|---------------------|------------------|--------------------|---------------------|-------------------|--------------------|--------------------|-------------------|-----|

| F0H | B<br>00000000       |                  |                    |                     |                   |                    |                    |                   | F7H |

| E8H |                     |                  |                    |                     |                   |                    |                    |                   | EFH |

| ЕОН | ACC<br>00000000     |                  |                    |                     |                   |                    |                    |                   | E7H |

| D8H | P4[3:0]<br>XXXX1111 |                  |                    |                     |                   |                    |                    |                   | DF  |

| D0H | PSW<br>00000000     |                  |                    |                     |                   |                    |                    |                   | D7H |

| С8Н | T2CON<br>00000000   |                  | RCAP2L<br>00000000 | RCAP2H<br>00000000  | TL2<br>00000000   | TH2<br>00000000    |                    |                   | CFI |

| СОН | XICON<br>00000000   |                  | P4CONA<br>00000000 | P4CCONB<br>00000000 |                   |                    |                    |                   | C7H |

| В8Н | IP<br>XX000000      |                  |                    |                     |                   |                    |                    |                   | BFH |

| вон | P3<br>11111111      |                  |                    |                     | P43AL<br>00000000 | PH43AH<br>00000000 |                    |                   | B7H |

| A8H | IE<br>0X000000      |                  |                    |                     | P42AL<br>00000000 | P42AH<br>00000000  | P2ECON<br>0000XX00 |                   | AF  |

| A0H | P2<br>11111111      |                  |                    |                     |                   |                    |                    |                   | A7H |

| 98H | SCON<br>00000000    | SBUF<br>XXXXXXXX |                    |                     |                   |                    | P2EAL<br>00000000  | P2EAH<br>00000000 | 9FH |

| 90H | P1<br>11111111      |                  |                    |                     | P41AL<br>00000000 | P41AH<br>00000000  |                    |                   | 971 |

| 88H | TCON<br>00000000    | TMOD<br>00000000 | TL0<br>00000000    | TL1<br>00000000     | TH0<br>00000000   | TH1<br>00000000    | AUXR<br>XXX00000   |                   | 8FI |

| 80H | P0<br>11111111      | SP<br>00000000   | DPL<br>00000000    | DPH<br>00000000     | P40AL<br>00000000 | P40AH<br>00000000  |                    | PCON<br>0XX00000  | 87H |

Figure 9. IC89E54/58/64 SFRs Map and Reset value (The gray blocks are non-standard.)

These descriptions are added from standard IC80C32. So, more information for SFRs and memory refer to IC80C32.

#### The timers/counters

Refer to IC80C32 data sheet.

#### The serial interface

Refer to IC80C32 data sheet.

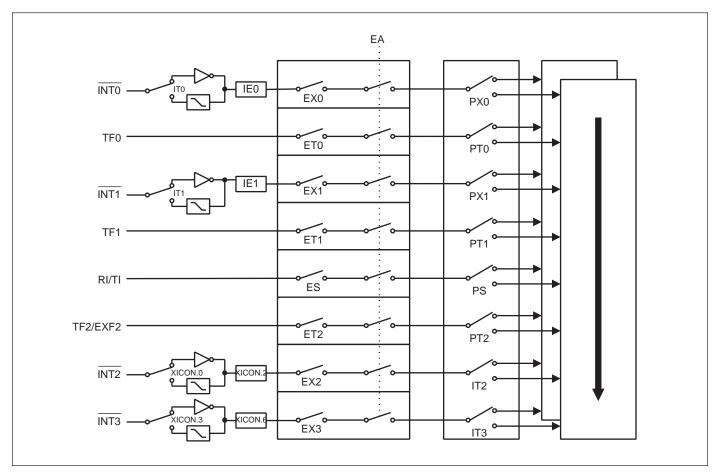

# The interrupt system

There are 8 interrupt vectors in 44 pins package and 6 interrupt vectors in 40 pins package. Eight interrupt vectors only exist in IC89E54/58/64 series. INT2 and INT3 are new interrupts that add on standard IC80C32. The interrupt information shows in Table 3. The interrupt architecture shows in figure 10. External interrupt 2 and 3 control register is XICON shown in following.

Two additional external interrupts,  $\overline{\text{INT2}}$  and  $\overline{\text{INT3}}$ , whose function are similar to those of external interrupt 0 and 1 in the standard 80C32. The functions/status of these interrupts are determined/shown by the bits in the XICON(External Interrupt Control) register. The XICON register is bit-addressable but is not a standard register in the 80C32. Its address is at 0C0H. To set/clear bits in the XICON register, one can use the "SETB (/CLR) bit" instruction.

Table 3. Eight interrupt information

| Interrupt Source         | Vector Address | Polling Sequence     | Enable Required | Interrupt Type |

|--------------------------|----------------|----------------------|-----------------|----------------|

|                          |                | within priority leve | Settings        | Edge/Level     |

| External Interrupt 0     | 03H            | 0 (Highest)          | IE.0            | TCON.0         |

| Timer/Counter 0 0BH      |                | 1                    | IE.1            | -              |

| External Interrupt 1     | 13H            | 2                    | IE.2            | TCON.2         |

| Timer/Counter 1          | 1BH            | 3                    | IE.3            | -              |

| Serial Port              | 23H            | 4                    | IE.4            | -              |

| Timer/Counter 2          | 2BH            | 5                    | IE.5            | -              |

| External Interrupt 2 (1) | 33H            | 6                    | XICON.2         | XICON.0        |

| External Interrupt 3 (1) | 3ВН            | 7 (Lowest)           | XICON.6         | XICON.3        |

#### Note:

<sup>1.</sup> Interrupt 2 and interrupt 3 exist in IC89E54/58/64 44 pins package.

# XICON(C0H)

|           | B7  | B6  | B5  | B4  | B3  | B2  | B1  | B0  |

|-----------|-----|-----|-----|-----|-----|-----|-----|-----|

| Flag Name | PX3 | EX3 | IE3 | IT3 | PX2 | EX2 | IE2 | IT2 |

| Bit | Name | Description                                                                                        |

|-----|------|----------------------------------------------------------------------------------------------------|

| 7   | PX3  | External interrupt 3 priority high if set.                                                         |

| 6   | EX3  | External interrupt 3 enable if set.                                                                |

| 5   | IE3  | If IT3=1, IE3 is set/cleared automatically by hardware when interrupt is detected/serviced.        |

| 4   | IT3  | External interrupt 3 is falling-edge/low-level triggered when this bit is set/cleared by software. |

| 3   | PX2  | External interrupt 2 priority high if set.                                                         |

| 2   | EX2  | External interrupt 2 enable if set.                                                                |

| 1   | IE2  | If IT2=1, IE2 is set/cleared automatically by hardware when interrupt is detected/serviced.        |

| 0   | IT2  | External interrupt 2 is falling-edge/low-level triggered when this bit is set/cleared by software. |

Figure 10. IC89E54/58/64 Interrupt Architecture

These descriptions are added from standard 80C32. So, more detailed information for interrupts refer to IC80C52.

# **Operation of Power-Save Mode**

Refer to IC80C32 data sheet.

#### **Instruction Definitions**

Refer to IC80C32 data sheet.

#### **Enhanced Function**

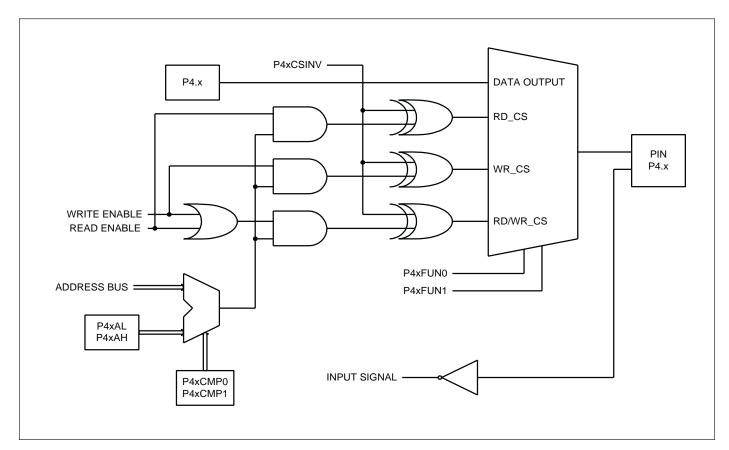

#### Port 4

Port 4, SFR P4 at address D8H, is a 4-bit multipurpose programmable I/O port. Each bit can be configured individually by software. The Port 4 has four different operation modes.

In mode 0, P4.0~P4.3 is a bi-directional I/O port which is same as port 1. P4.2 and P4.3 also serve as external interrupt INT3 and INT2 if enabled.

In mode 1, P4.0~P4.3 are read data strobe signals which are synchronized with beginning of read address signal at specified address. These signals can be used as chip-select signals for external peripherals.

In mode 2, P4.0~P4.3 are write data strobe signals which are synchronized with beginning of written address signal at specified address. These signals can be used as chip-select signals for external peripherals.

In mode 3, P4.0~P4.3 are write data strobe signals which are synchronized with beginning of read or written address signal at specified address. These signals can be used as chip-select signals for external peripherals.

When Port 4 is configured with the feature of chip-select signals, the chip-select signal address range depends on the contents of the SFRs P4xAH, P4xAL, P4CONA an P4CONB. The registers P4xAH and P4xAL contain the 16-bit base address of P4.x. The registers P4CONA and P4CONB contain the control bits to configure the Port 4 operating mode.

Here is an example to program the P4.0 as a write strobe signal at the I/O port address 1234H~1237H and positive polarity, and P4.1~P4.3 are used as general I/O ports.

MOV P40AH,#12H ;Define the base I/O address 1234H for P4.0 as an special function pin.

MOV P40AL,#34H

MOV P4CONA,#00001010B ;Define the P4.0 as a write strobe signal pin and the compartor, length is 14.

MOV P4CONB,#00H ;P4.1~P4.3 as general I/O port which are the same as Port 1.

MOV P2ECON,#10H ;Write the P40SINV=1 to inverse the P4.0 write strobe polarity, default is

;negative.

Then any instruction MOVX @DPTR,A (with DPTR=1234H~1237H) will generate the positive polarity write strobe signal at pin P4.0. And the instruction MOV P4,#XX will output the bit 3 to bit 1 of data #XX to pin P4.3~P4.1.

The SFRs of Port 4 are described in following. Figure 11 shows architecture of Port 4.

Port 4 base Address Registers: Reset values are 00000000B.

**P40AH, P40AL(85H, 84H)**: The Base address register for comparator of P4.0. P40AH contains the high-order byte of address, P40AL contains the low-order byte of address.

**P41AH**, **P41AL**(**95H**, **94H**): The Base address register for comparator of P4.1. P41AH contains the high-order byte of address, P41AL contains the low-order byte of address.

**P42AH**, **P42AL**(**ADH**, **ACH**): The Base address register for comparator of P4.2. P42AH contains the high-order byte of address, P42AL contains the low-order byte of address.

**P43AH**, **P43AL**(**B5H**, **B4H**): The Base address register for comparator of P4.3. P43AH contains the high-order byte of address, P43AL contains the low-order byte of address.

# P4CONB (C3H)

|        |      | В7      | B6                                                                                          | B5             | B4               | В3                 | B2              | B1            | В0           |  |  |

|--------|------|---------|---------------------------------------------------------------------------------------------|----------------|------------------|--------------------|-----------------|---------------|--------------|--|--|

| Flag I | Name | P43FUN1 | P43FUN0                                                                                     | P43CMP1        | P43CMP0          | P42FUN1            | P42FUN0         | P42CMP1       | P42CMP0      |  |  |

| Bit    | Na   | ame     |                                                                                             |                | D                | escription         |                 |               |              |  |  |

| 7,6    | P43  | FUN1 =  | =00: Mode 0. P4.3 is a general purpose I/O port which is the same as Port 1.                |                |                  |                    |                 |               |              |  |  |

|        | P43  |         | =01: Mode 1. P                                                                              | 4.3 is a Read  | Strobe Signal    | for chip selecting | g purpose. The  |               | ige depends  |  |  |

|        |      |         | on the SFRs                                                                                 | P43AH, P43     | BAL and flags I  | P43CMP1, P430      | CMP0.           |               |              |  |  |

|        |      | =       | =10: Mode 2. P                                                                              | 4.3 is a Write | Strobe Signal    | for chip selecting | g purpose. The  | e address rar | ige depends  |  |  |

|        |      |         | on the SFRs                                                                                 | P43AH, P43     | AL and flags I   | P43CMP1, P430      | CMP0.           |               |              |  |  |

|        |      | =       | =11: Mode 3. F                                                                              | P4.3 is a Rea  | d/Write Strobe   | Signal for chip    | selecting purp  | oose. The ac  | ldress range |  |  |

|        |      |         | depends on                                                                                  | the SFRs P4    | 3AH, P43AL a     | nd flags P43CM     | 1P1, P43CMP     | 0.            |              |  |  |

| 5.4    | P430 | CMP1 (  | Chip-select sig                                                                             | nals for addr  | ess compariso    | on.                |                 |               |              |  |  |

|        | P430 | CMP0 =  | =00: Compare the full address (16 bits length) with the base address register P43AH, P43AL. |                |                  |                    |                 |               |              |  |  |

|        |      | =       | =01: Compare                                                                                | the 15 high b  | oits (A15-A1)    | of address bus v   | vith the base a | address regi  | ster         |  |  |

|        |      |         | P43AH, P43                                                                                  | AL.            |                  |                    |                 |               |              |  |  |

|        |      | =       | =10: Compare                                                                                | the 14 high b  | oits (A15-A2) o  | of address bus v   | vith the base a | address regi  | ster         |  |  |

|        |      |         | P43AH, P43                                                                                  | AL.            |                  |                    |                 |               |              |  |  |

|        |      | =       | =01: Compare                                                                                | the 8 high bi  | ts (A15-A8) of   | address bus wi     | th the base a   | ddress regist | ter          |  |  |

|        |      |         | P43AH, P43                                                                                  | AL.            |                  |                    |                 |               |              |  |  |

| 3,2    | P42  | FUN1    | The P4.2 funct                                                                              | ion control bi | its which are th | ne similar definit | ion as P42FU    | IN1, P42FUN   | ١0.          |  |  |

|        | P42  | FUN0    |                                                                                             |                |                  |                    |                 |               |              |  |  |

| 1,0    | P420 | CMP1    | The P4.2 addr                                                                               | ess compara    | tor length con   | trol bits which ar | e the similar   | definition as | P42CMP1,     |  |  |

|        | P420 | CMP0    | P42CMP0.                                                                                    |                |                  |                    |                 |               |              |  |  |

# P4CONA (C2H)

|        |      | В7      | B6          | B5             | B4              | B3             | B2              | B1              | B0            |

|--------|------|---------|-------------|----------------|-----------------|----------------|-----------------|-----------------|---------------|

| Flag N | lame | P41FUN1 | P41FUN0     | P41CMP1        | P41CMP0         | P40FUN1        | P40FUN0         | P40CMP1         | P40CMP0       |

|        |      |         |             |                |                 |                |                 |                 |               |

| Bit    | Nar  | ne      |             |                | [               | Description    |                 |                 |               |

| 7,6    | P41  | FUN1    | The P4.1 fu | nction control | bits which are  | e the similar  | definition as F | P41FUN1, P4     | 1FUN0.        |

|        | P41  | FUN0    |             |                |                 |                |                 |                 |               |

| 5,4    | P41  | CMP1    | The P4.1 ad | ldress compa   | rator length co | ontrol bits wh | ich are the si  | milar definitio | n as P41CMP1, |

|        | P41  | CMP0    | P41CMP0.    |                |                 |                |                 |                 |               |

| 3,2    | P40  | FUN1    | The P4.0 fu | nction control | bits which are  | e the similar  | definition as F | P40FUN1, P4     | 0FUN0.        |

|        | P40  | FUN0    |             |                |                 |                |                 |                 |               |

| 1,0    | P40  | CMP1    | The P4.0 ad | ldress compa   | rator length co | ontrol bits wh | ich are the si  | milar definitio | n as P40CMP1, |

|        | P40  | CMP0    | P40CMP0.    |                |                 |                |                 |                 |               |

|        | ·    |         |             | <u> </u>       |                 | <u> </u>       | <u> </u>        |                 |               |

# P4(D8H):

|           | B7 | B6 | B5 | B4 | В3   | B2   | B1   | B0   |

|-----------|----|----|----|----|------|------|------|------|

| Flag Name | -  | -  | -  | -  | P4.3 | P4.2 | P4.1 | P4.0 |

| Bit | Name | Description                                        |

|-----|------|----------------------------------------------------|

| 7-4 | -    | These bits are reserved.                           |

| 3   | P4.3 | Port 4 Data bit that output to pin P4.3 at mode 0. |

| 2   | P4.2 | Port 4 Data bit that output to pin P4.2 at mode 0. |

| 1   | P4.1 | Port 4 Data bit that output to pin P4.1 at mode 0. |

| 0   | P4.0 | Port 4 Data bit that output to pin P4.0 at mode 0. |

Figure 11. IC89E54/58/64 Port 4 Architecture

# P2ECON(AEH)

|        |      | B7       | B6                                                                            | B5               | B4                | B3          | B2            | B1          | B0          |  |  |  |

|--------|------|----------|-------------------------------------------------------------------------------|------------------|-------------------|-------------|---------------|-------------|-------------|--|--|--|

| Flag N | lame | P43CSINV | P42CSINV                                                                      | P41CSINV         | P40CSINV          | -           | -             | P2CN1       | P2CN0       |  |  |  |

|        |      |          |                                                                               |                  |                   |             |               |             |             |  |  |  |

| Bit    | Na   | me       |                                                                               |                  | Descripti         | on          |               |             |             |  |  |  |

| 7      | P4   | 3CSINV   | The active polar                                                              | ty of P4.3 wher  | n pin P4.3 is def | ined as rea | ad/write stro | obe signal. |             |  |  |  |

|        |      |          | =1: P4.3 is active high when pin P4.3 is defined as read/write strobe signal. |                  |                   |             |               |             |             |  |  |  |

|        |      |          | =0: P4.3 is active low when pin P4.3 is defined as read/write strobe signal.  |                  |                   |             |               |             |             |  |  |  |

| 6      | P4   | 2CSINV   | The similarity de                                                             | finition as P43S | SINV.             |             |               |             |             |  |  |  |

| 5      | P4   | 1CSINV   | The similarity de                                                             | finition as P43S | SINV.             |             |               |             |             |  |  |  |

| 4      | P4   | 0CSINV   | The similarity de                                                             | finition as P43S | SINV.             |             |               |             |             |  |  |  |

| 3,2    | -    |          | Reserve                                                                       |                  |                   |             |               |             |             |  |  |  |

| 1,0    | P2   | CN1,     | =00 : Pin P2.7-P                                                              | 2.0 is the stand | lard 8052 port 2  |             |               |             |             |  |  |  |

|        | P2   | CN0      | =01 : Pins P2.7-I                                                             | 2.0 is input buf | fer port which th | e port enal | ole address   | depends or  | the content |  |  |  |

=10: Pins P2.7-P2.0 is output-latched port which the port enable address depends on the

of P2EAL and P2EAH.

=11: Undefined.

content of P2EAL and P2EAH.

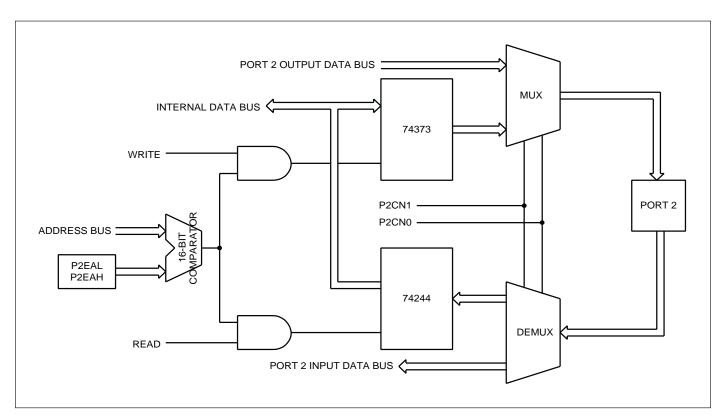

Figure 12. IC89E54/58/64 Port 2 Architecture

**P2EAH**, **P2EAL**: The Port Enable Address Registers for Port 2 is defined as input buffer like 74244, or an output-latched logic like a 74373. The P2EAH contains the high-order byte of address, the P2EAL contains the low-order byte of address. Figure 12 shows architecture of Port 2. The following example shows how to program the Port 2 as a output-latched port at address 5678H.

MOV P2EAL,#78H ;High-order byte of address to enable Port 2 latch function.

MOV P2EAH,#56H ;Low-order byte of address to enable Port 2 latch function.

MOV P2ECON,#02H ;Configure the port 2 as an output-latched port.

MOV DPTR,#5678H ;Move data 5678H to DPTR.

MOV A,#55H

MOVX @DPTR,A ;The pins P2.7~P2.0 will output and latch the value 55H.

When Port 2 is configured as 74244 or 74373 function, the instruction "MOV P2,#XX" will write the data #XX to P2 register only but not output to port pins P2.7~P2.0.

#### **Power Down Mode**

When the PD bit in the PCON register is set, the processor enters the power-down mode. In this mode, all of the clocks are stopped, including the oscillator. To exit from power-down mode is by a hardware reset or external interrupts  $\overline{\text{INT0}}$  to  $\overline{\text{INT3}}$  when enabled and set to level triggered. To ensure that the oscillator is stable before the CPU restarts, the IC89E54/58/64 series provide adjustable internal software delay counter. By the default, the device will experience a delay of 2048 clock cycles while the oscillation is recognized. The period of delay is selected by configuring the AUXR register bits OD0, OD1 and OD2.

#### **Reduce EMI Emission**

Because of on-chip flash, when a program is running in internal program memory space, the ALE will be unused. The transition of ALE will cause larger noise and EMI effect, so it can be turned off to reduce noise and EMI emission if it is useless. Turning off the ALE signal transition only requires setting the bit 0 of the AUXR SFR, which is located at 08EH. When ALE is turned off, it will be reactivated when the program accesses external ROM/RAM data or jumps to execute an external ROM code. The ALE signal will turn off again after it has been completely accessed or program returns to internal ROM code space. The ALED bit in the AUXR register, when set, disables the ALE output.

# **AUXR(8EH)**: Reset value is xxx0x0000B.

|        | B7      | В6                                                                           | B:                       | 5 B4               | В3             | B2            | B1  | В0   |  |

|--------|---------|------------------------------------------------------------------------------|--------------------------|--------------------|----------------|---------------|-----|------|--|

| Flag N | lame -  | -                                                                            | -                        | ENARAI             | M -            | OD1           | OD0 | ALED |  |

| Bit    | Name    |                                                                              |                          |                    | Description    |               |     |      |  |

| 7-5    | -       | These                                                                        | bits are rese            | rved.              |                |               |     |      |  |

| 4      | ENARAM  | 1, Enal                                                                      | , Enable AUX RAM.        |                    |                |               |     |      |  |

| 3      | -       | These                                                                        | These bits are reserved. |                    |                |               |     |      |  |

| 2-1    | OD1-OD0 | Select the delay periods of oscillation when waking up from power-down mode. |                          |                    |                |               |     |      |  |

|        |         | OD1 (                                                                        | DD0 Del                  | ay Period          |                |               |     |      |  |

|        |         | 0 (                                                                          | 2,0                      | 48 clock cycles (I | Default)       |               |     |      |  |

|        |         | 0                                                                            | 1 8,1                    | 92 clock cycles    |                |               |     |      |  |

|        |         | 1 (                                                                          | 32,                      | 768clock cycles    |                |               |     |      |  |

|        |         | 1 1                                                                          | 1 131                    | ,072 clock cycles  | S              |               |     |      |  |

| 0      | ALED    | 1, Turn                                                                      | off ALE out              | out while CPU ac   | cesses interna | al Flash memo | ry. |      |  |

# Power Control Register PCON(87H):

|           | B7   | B6 | B5 | B4 | В3  | B2  | B1 | В0  |

|-----------|------|----|----|----|-----|-----|----|-----|

| Flag Name | SMOD | -  | -  | -  | GF1 | GF0 | PD | IDL |

| Bit | Name | Description                                                                                 |

|-----|------|---------------------------------------------------------------------------------------------|

| 7   | SMOD | Double baud rate bit. If Timer 1 is used to generate baud rate and SMOD=1, the baud rate is |

|     |      | doubled when the serial port is used in modes 1, 2, or 3.                                   |

| 6-4 | -    | These bits are reserved.                                                                    |

| 3   | GF1  | General purpose flag bit.                                                                   |

| 2   | GF0  | General purpose flag bit.                                                                   |

| 1   | PD   | Power down bit. Setting this bit activates power down operation in the IC89E54/58/64.       |

| 0   | IDL  | Idle mode bit. Setting this bit activate idle mode operation in the 89E54/58/64.            |

|     |      | If 1s are written to PD and IDL at the same time, PD takes precedence.                      |

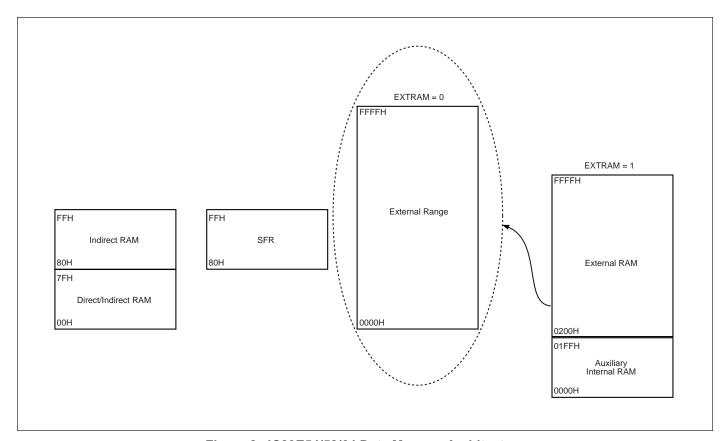

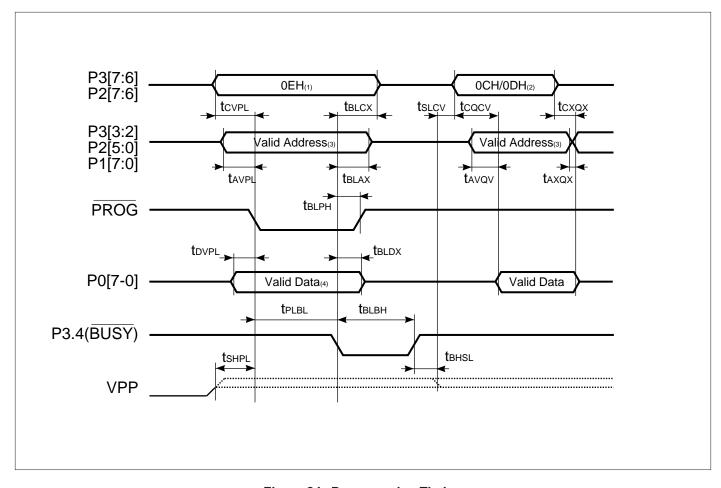

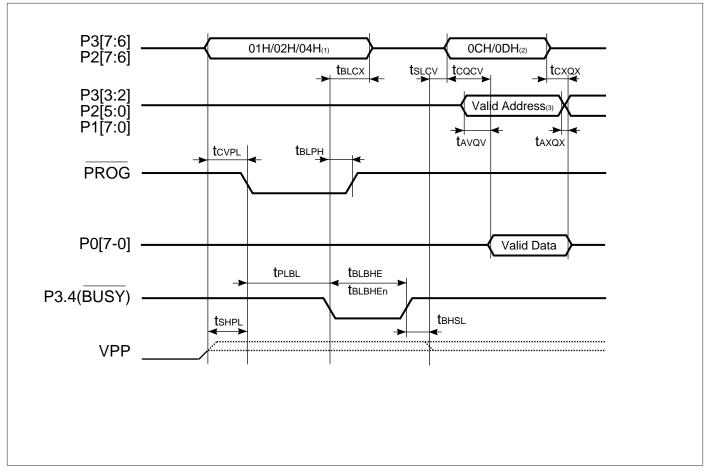

#### FLASH MEMORY PROGRAMMING

The Flash architecture of IC89E54/58/64 is shown in Figure 13. IC89E54/58 include block 1 and lock bits block. The signature bytes are fixed value reside in MCU, they are read only. Block 2 resides in IC89E64 only.

Figure 13. The Flash Architecture of IC89E54/58/64

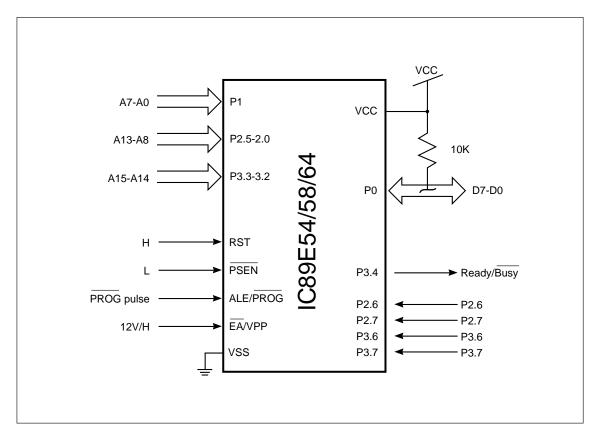

# **EXTERNAL HOST MODE**

The IC89E54/58/64 provide the user with a direct flash memory access that can be used for programming into the flash memory without using the CPU. The direct flash memory access is entered using the External Host Mode. While the reset input (RST) is continually held active (high), if the PSEN pin is forced by an input with low state, the device enters the External Host Mode arming state at this time. The CPU core is stopped from running and all the chip I/O pins are reassigned and become flash memory access and control pins. At this time, the external host should initiate a "Read Signature Bytes" operation. After the completion of the "Read Signature Bytes" operation, the device is armed and enters the External Host Mode. After the device enters into the External Host Mode, the internal flash memory blocks are accessed through the reassigned I/O port pins by an external host, such as a printed circuit board tester, a PC controlled development board or an MCU programmer.

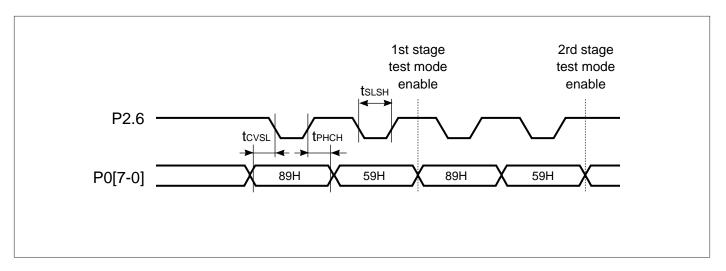

When the chip is in the external host mode, Port 0 pins are assigned to be the parallel data input and output pins. Port 1 pins are assigned to be the low order address bus signals for the internal flash memory (A0-A7). The first six bits of Port 2 pins (P2[0:5]) are assigned to be the upper order address bus signals for the internal flash memory (A8-A13) along with two of the Port 3 pins (P3.2 as A14 and P3.3 as A15). Two upper order Port 2 pins (P2.6 and P2.7) and two upper order Port 3 pins (P3.6 and P3.7) along with RST, PSEN, PROG/ALE, EA pins are assigned as the control signal pins. The P3. 4 is assigned to be the ready/busy status signal, which can be used for handshaking with the external host during a flash memory programming operation. The flash memory programming operation (Erase, Program, Verify, etc.) is internally self-timed and can be controlled by an external host asynchronously or synchronously.

The insertion of an "arming" command prior to entering the External Host Mode by utilizing the "Read Signature Bytes" operation provides additional protection for inadvertent writes to the internal flash memory cause by a noisy or unstable system environment during the power-up or power unstable conditions.

The External Host Mode uses hardware setup mode, which are decoded from the control signal pins, to facilitate the internal flash memory erase, test and programming process. The External Host Mode Commands are enabled on the falling edge of ALE/PROG. The list in Table 4 outlines all the setup conditions of normal mode. Before entering these written modes must have read 3 signature bytes.

# **Programming Interface**

Some conditions must be satisfied before entering the programming mode. The conditions are listed in Table 4. The interface-controlled signals are matched these conditions, then the IC89E54/58/64 will enter received command mode. The flash command is accepted by the flash command decoder in command received mode. The programming interface is listed in figure 14.

Figure 14. IC89E52/54/64 External Host Programming Signals

Table 4. Flash Programming Mode

| Mode <sup>(1)</sup> | RST | PSEN | PROG | ĒĀ    | P2.6 | P2.7 | P3.6 | P3.7 | P0[7:0] | P1[7:0] | P3[3:2] | COM                |

|---------------------|-----|------|------|-------|------|------|------|------|---------|---------|---------|--------------------|

|                     |     |      |      |       |      |      |      |      |         |         | P2[5:0] | HEX <sup>(3)</sup> |

| Read Signature Byte | Н   | L    | Н    | Н     | L    | L    | L    | L    | DO      | AL      | AH      | 0                  |

| Chip Erase          | Н   | L    |      | 12V/H | Н    | L    | L    | L    | Х       | Х       | Х       | 1                  |

| Block 1 (2) Erase   | Н   | L    |      | 12V/H | L    | Н    | L    | L    | Χ       | Χ       | Χ       | 2                  |

| Block 2 (2) Erase   | Н   | L    |      | 12V/H | L    | L    | Н    | L    | Χ       | Χ       | Χ       | 4                  |

| Program Main code   | Н   | L    |      | 12V/H | L    | Н    | Н    | Н    | DI      | AL      | AH      | Е                  |

| Program Lock Bit 1  | Н   | L    |      | 12V/H | Н    | Н    | Н    | Н    | Χ       | Χ       | Χ       | F                  |

| Program Lock Bit 2  | Н   | L    |      | 12V/H | Н    | Н    | L    | L    | Χ       | Χ       | Χ       | 3                  |

| Program Lock Bit 3  | Н   | L    |      | 12V/H | Н    | L    | Н    | L    | Χ       | Χ       | Χ       | 5                  |

| Verify Lock Bits    | Н   | L    | Н    | Н     | Н    | L    | L    | Н    | DO[3:1] | Х       | Х       | 9                  |

| Verify Main Code    | Н   | L    | Н    | Н     | L    | L    | Н    | Н    | DO      | AL      | АН      | С                  |

- 1. To read the signature bytes 30H, 31H, 32H are needed before any written command. To read signature bytes is needed after any new mode changed. This operation provides additional protection for inadvertent writes to the internal flash memory cause by a noisy or unstable system environment during the power-up or unstable power condition. If any unstable power condition has happened while written operation proceeds, to read signature bytes again will re-enable written command. (Power-on reset voltage is about 2.7V.)

- 2. Block 1 includes flash address from 0000H to 3FFFH in IC89E54, from 0000H to 7FFFH in IC89E58, from 0000H to EFFFH in IC89E64. Block 2 includes F000H to FFFFH. Block 2 is resident in IC89E64 only.

- 3. "COM HEX" presents the combination value of [P3.7, P3.6, P2.7, P2.6].

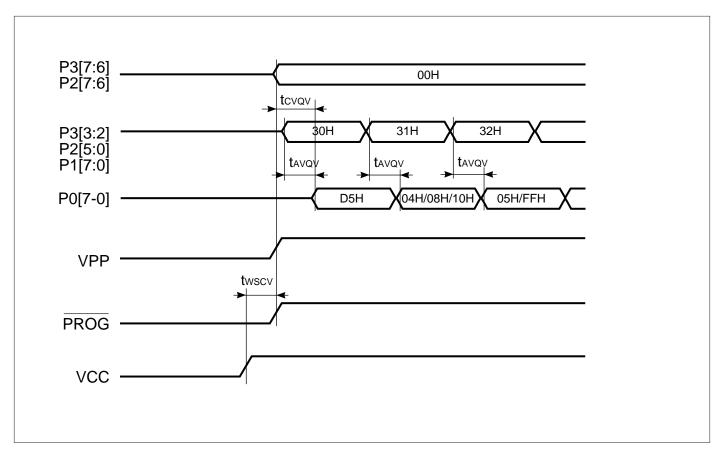

# **Product Identification**

The "Read Signature Bytes" command accesses the Signature Bytes that identify the device as IC89E54/58/64 and the manufacturer code. External programmers primarily use these Signature Bytes, shown in Table 4, in the selection of programming algorithms. The Read Signature Bytes command is selected by the byte code of 00h on P3[7:6] and P2[7:6]. Manufacturer code of ICSI is "D5H" that reside in address 30H of signature. The flash memory sizes of MCU are shown in address 31H, code value 04H respect to 16K main flash memory, code value 08H respect to 32K main flash memory, code value 10H respect to 64K main flash memory. The address 32H value of signature byte respect to written operation VPP value, code value FFH respects to 12V and 55H respects to 5V.

Table 5. Signature Bytes Information

|                   | Addr 30H | Addr 31H | Addr 32H |

|-------------------|----------|----------|----------|

| IC89E54 (VPP=12V) | D5H      | 04H      | FFH      |

| IC89E54 (VPP=5V)  | D5H      | 04H      | 05H      |

| IC89E58 (VPP=12V) | D5H      | 08H      | FFH      |

| IC89E58 (VPP=5V)  | D5H      | 08H      | 05H      |

| IC89E64 (VPP=12V) | D5H      | 10H      | FFH      |

| IC89E64 (VPP=5V)  | D5H      | 10H      | 05H      |

# **Arming Command**

An arming command must take place before a Written Mode will be recognized by the IC89E54/58/64. This is to prevent accidental triggering of written operation due to noise or programmer error. The arming command is as follows:

A Read Signature Bytes command is issued. This is actually a natural step for the programmer, but will also serve as the arming command. After the above sequence, all other Written Mode commands are enabled. Before the Read Signature Bytes command is received, all other Written Mode commands received are ignored. The IC89E54/8/64 will exit Written Mode if power off, so arming command is needed every power on for entering External Host Command Mode.

#### **External Host Mode Commands**

The following is a brief description of the commands. See Table 4 for all signal logic assignments for the External Host Mode Commands. The critical timing for all Erase and Program commands, is self-generated by the flash memory controller on-chip.

The high-to-low transition of the PROG signal initiates the Erase and Program commands, which are synchronized internally. All the data in the memory array will be erased to FFH. Memory addresses that are to be programmed must be in the erased state prior to programming. Selection of the Erase command to use, prior to programming the device, will be dependent upon the contents already in the array and the desired programming field block.

The "Chip Erase" command erases all bytes in both memory blocks of the IC89E54/58/64. This command ignores the "Lock bits" status and will erase the Security Byte. The "Chip Erase" command is selected by the byte code of 01H on P3 [7:6] and P2[7:6].

# Flash Operation Status Detection (Ext. Host Handshake)

The IC89E54/58/64 provide two signals mean for an external host to detect the completion of a flash memory operation, therefore the external host can optimize the system Program or Erase cycle of the embedded flash memory. The end of a flash memory operation cycle (Erase or Program) can be detected by monitoring the Ready/Busy bit at Port 3.4. The following two Program commands are for programming new data into the memory array. Selection of which Program command to use for programming will be dependent upon the desired programming field size. The Program commands will not enable if the Lock bit 2 or Lock Bit 3 is enabled on the selected memory block. The "Program Main Code" command program data into a single byte. Ports P0[0:7] are used for data in. The memory location is selected by P1[0:7], P2[0:5], and P3[2:3] (A0-A15). The "Program Main Code" command is selected by the byte code on P3[6:7] and P2[6:7].

The "Verify Main Code" command allows the user to verify that the IC89E54/58/64 correctly performed an Erase or Program command. Ports P0[0:7] are used for data out. The memory location is selected by P1[0:7], P2[0:5], and P3[2:3] (A0-A15). These commands will not enable if any lock bit is enabled on the selected memory block.

# Ready/Busy

The progress of the flash memory programming can be monitored by the Ready/Busy output signal. The Ready/Busy indicates whether an Embedded Algorithm in Written State Machine (WSM) is in progress or complete. The RY/BY status is valid after the falling edge of the programming or erase controlled signal. If the output is low (Busy), the device is in an erasing/programming state with an internal verification. If the output is high, the device is ready to read data. If Ready/Busy signal doesn't generate a low pulse or doesn't return from low to high in an expected time, the programming/erasing action will be failed.

# Programming a IC89E54/58/64

To program new data into the memory array, supply 5 volts to VDD and RST, and perform the following steps.

- 1. Set RST to high and PSEN to low.

- 2. Read the "Read Signature Bytes" command to ensure the correct programming algorithm.

- 3. Raise EA High (either 12V or 5V).

- 4. Verify that the memory blocks for programming are in the erased state, FFH. If they are not erased, then erase them using the Chip Erase command. (Chip Erase operation will have a Ready/Busy signal output from P3.4, if Ready/Busy signal doesn't return from low to high in 7.2 sec, the Chip Erase operation will be failed.)

- 5. Set P2.6, P2.7, P3.6, P3.7 to a properly programming combination.

- 6. Select the memory location using the address lines (P1[0:7], P2[0:5], P3[2:3]).

- 7. Present the data in on P0[0:7].

- 8. Pulse ALE/PROG.

- 9. Wait for low to high transition on Ready/Busy(P3.4). If Ready/Busy is from low to high, this address is programmed completely. If Ready/Busy pin don't return from low to high in 720us while programming one byte, the Programming operation will be failed.

- 10. Repeat steps 6~9 until programming is finished.

#### **Lock bits Features**

The IC89E54/58/64 provide three lock bits to protect the embedded program against software piracy. These three bytes are user programmable. The relation between lock bits status and protection type are listed in table 6.

**Table 6. Lock Bits Features**

|   | Progr | am Loc | k bits | Protection in Normal Mode                                                  |  |

|---|-------|--------|--------|----------------------------------------------------------------------------|--|

|   | LB1   | LB2    | LB3    |                                                                            |  |

| 1 | U     | U      | U      | No program lock feature enabled.                                           |  |

| 2 | Р     | U      | U      | MOVC instructions executed from external program memory are                |  |

|   |       |        |        | disabled from fetching code bytes from internal memory, $\overline{EA}$ is |  |

|   |       |        |        | sampled and latched on reset, and Data verification is disabled.           |  |

|   |       |        |        | ("Verify Signature Byte" and "Verify Lock Bits are still enabled.)         |  |

| 3 | Р     | Р      | U      | Same as 2, also further written operation of the Flash is disabled         |  |

| 4 | Р     | Р      | Р      | Same as 3, also external execution is disabled.                            |  |

# **Special Issue**

There are two conditions must be sure. One is P2.6 and P2.7 can not be low levels when RST pin falling edge. Another is P4.3 can not be low level while RST falling edge. One of upper case is generate, the program will not be executing correctly.

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                           | Rating       | Unit              |

|-----------------------------------------------------|--------------|-------------------|

| Operating Temperature Under Bias                    | 0 to +70     | °C <sup>(1)</sup> |

| Storage Temperature Range                           | -65 to +125  | °C                |

| Voltage on any other pin to Vss                     | -2.0 to +7.0 | V <sup>(2)</sup>  |

| Power Dissipation (Based on package heat            | 1.5          | W                 |

| transfer limitations, not device power consumption) |              |                   |

#### Note:

- 1. Operating temperature is for commercial products defined by this specification.

- 2. Minimum DC input voltage is -0.5V. During transitions, inputs may undershoot to -2. 0V for periods less than 20 ns. Maximum DC voltage on output pins is Vcc + 0.5V which may overshoot to Vcc + 2.0V for periods less than 20 ns.

# OPERATING RANGE(1)

| Range      | Ambient Temperature | <b>V</b> cc  | Oscillator Frequency |  |

|------------|---------------------|--------------|----------------------|--|

| Commercial | 0°C to +70°C        | +4.5V to +5V | 3.5 to 40 MHz        |  |

#### Note:

1. Operating ranges define those limits between which the functionality of the device is guaranteed.

# DC CHARACTERISTICS

( Ta = 0°C to 70°C; VCC = 5V+10%; VSS = 0V)

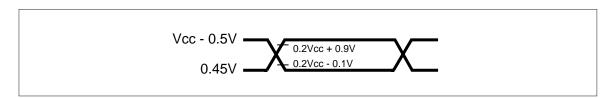

| Symbol              | Parameter                                                        | Test conditions                             | Min          | Max           | Unit |

|---------------------|------------------------------------------------------------------|---------------------------------------------|--------------|---------------|------|

| VIL                 | Input low voltage                                                |                                             | -0.5         | 0.2Vcc - 0.1  | V    |

| Vı∟1                | Input low voltage (XTAL1, EA)                                    |                                             | -0.5         | 0.2 Vcc - 0.3 | V    |

| Vін                 | Input high voltage (except XTAL 1, RST, $\overline{\text{EA}}$ ) |                                             | 0.2Vcc + 0.9 | Vcc + 0.5     | V    |

| Vıн1                | Input high voltage (XTAL 1, EA)                                  |                                             | 0.7Vcc       | Vcc + 0.5     | V    |

| Vsc++               | RST positive schmitt-trigger threshold voltage                   |                                             | 0.7Vcc       | Vcc + 0.5     | V    |

| VscH-               | RST negative schmitt-trigger threshold voltage                   |                                             | 0            | 0.3Vcc        | V    |

| VoL <sup>(1)</sup>  | Output low voltage                                               | lol = 100 μA                                | _            | 0.3           | V    |

|                     | (Ports 1, 2, 3)                                                  | IoL = 1.6 mA                                | _            | 0.45          | V    |

|                     |                                                                  | IoL = 3.5 mA                                | _            | 1.0           | V    |

| Vol1 <sup>(1)</sup> | Output low voltage                                               | Ιοι = 200 μΑ                                | _            | 0.3           | V    |

|                     | (Port 0, ALE, PSEN)                                              | IoL = 3.2 mA                                | _            | 0.45          | V    |

|                     |                                                                  | loL = 7.0 mA                                | _            | 1.0           | V    |

| Vон                 | Output high voltage<br>(Ports 1, 2, 3, ALE, PSEN)                | $IOH = -10 \mu A$<br>$Vcc = 4.5V \sim 5.5V$ | 0.9Vcc       | _             | V    |

|                     |                                                                  | IoL = -25 μA                                | 0.75Vcc      | _             | V    |

|                     |                                                                  | IoL = -60 μA                                | 2.4          | _             | V    |

| Vон1                | Output high voltage<br>(Port 0, ALE, PSEN)                       | IoH = -80 μA<br>Vcc = 4.5V ~ 5.5V           | 0.9Vcc       | _             | V    |

|                     |                                                                  | Іон = -300 µА                               | 0.75Vcc      | _             | V    |

|                     |                                                                  | Іон = -800 µА                               | 2.4          | _             | V    |

| lı∟                 | Logical 0 input current (Ports 1, 2, 3)                          | VIN = 0.45V                                 | _            | -50           | μA   |

| lu                  | Input leakage current (Port 0)                                   | VIN = 0.45V or Vcc                          | -10          | +10           | μΑ   |

| lτι                 | Logical 1-to-0 transition current (Ports 1, 2, 3)                | VIN = 2.0V                                  | _            | <b>–</b> 650  | μA   |

| Rrst                | RST pulldown resister                                            | Vin = 0V                                    | 50           | 300           | KΩ   |

#### Note:

1. Under steady state (non-transient) conditions, lo<sub>L</sub> must be externally limited as follows:

Maximum loL per port pin: 10 mA

Maximum lo∟ per 8-bit port

Port 0: 26 mA

Ports 1, 2, 3: 15 mA

Maximum total loL for all output pins: 71 mA

If lo\_ exceeds the test condition, Vo\_ may exceed the related specification.

Pins are not guaranteed to sink greater than the listed test conditions.

# **POWER SUPPLY CHARACTERISTICS**

| Symbol | Parameter                           | Test conditions | Min | Max | Unit |

|--------|-------------------------------------|-----------------|-----|-----|------|

| Icc    | Power supply current <sup>(1)</sup> | Vcc=5.0V        |     |     |      |

|        | Active mode                         | 12 MHz          | _   | 20  | mA   |

|        |                                     | 16 MHz          | _   | 26  | mA   |

|        |                                     | 20 MHz          | _   | 32  | mA   |

|        |                                     | 24 MHz          | _   | 38  | mA   |

|        |                                     | 32 MHz          | _   | 50  | mA   |

|        |                                     | 40 MHz          | _   | 62  | mA   |

|        | Idle mode                           | de 12 MHz —     |     | 5   | mA   |

|        |                                     | 16 MHz          | _   | 6   | mA   |

|        |                                     | 20 MHz          | _   | 7.6 | mA   |

|        |                                     | 24 MHz          | _   | 9   | mA   |

|        |                                     | 32 MHz          | _   | 12  | mA   |

|        |                                     | 40 MHz          | _   | 15  | mA   |

|        | Power-down mode                     | Vcc=5.0V        | _   | 50  | μA   |

#### Note:

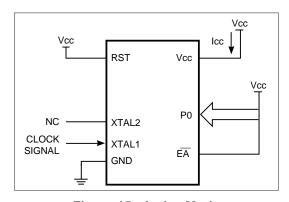

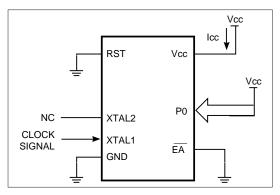

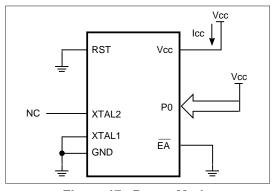

1. The lcc test conditions are shown below. Minimum Vcc for Power Down is 2 V.

Figure 15. Active Mode

Figure 16. Idle Mode

Figure 17. Power Mode (Vcc=2.0V~6.0V)

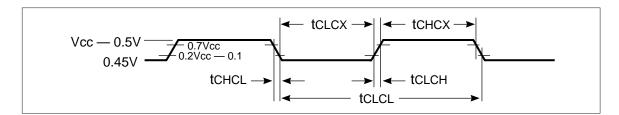

Figure 18. Clock Singal Waveform for Icc Tests in Active and Idle Mode ( $t_{\text{clch}} = t_{\text{chcl}} = 5 \text{ ns}$ )

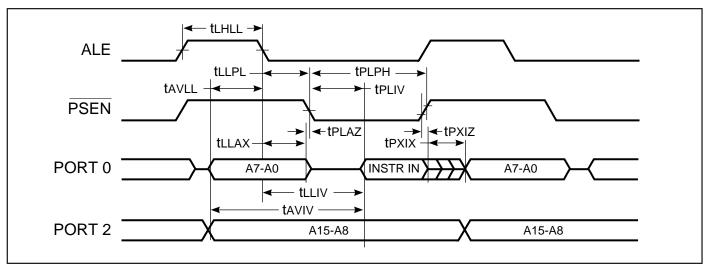

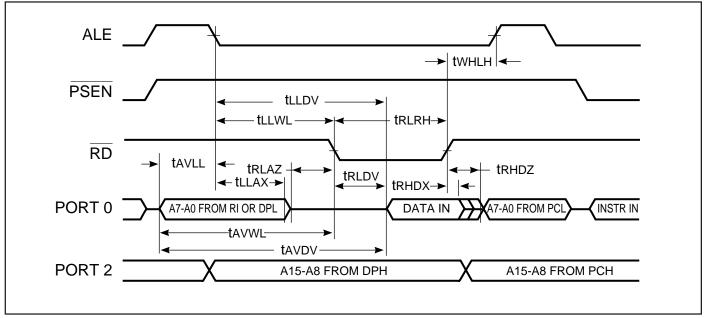

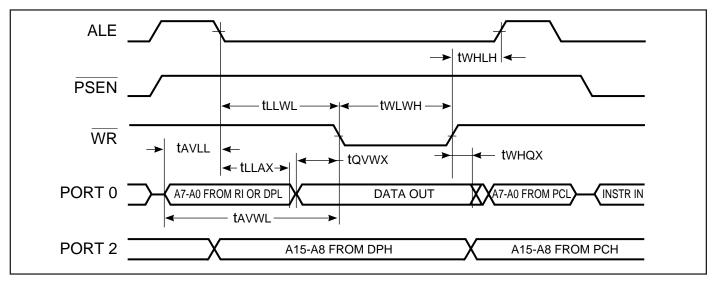

# **AC CHARACTERISTICS**

(Ta=0°Cto 70°C; VCC=5V±10%; Vss=0V; C1 for port 0, ALE and PSEN Outputs=100pF; C1 for other outputs=80pF)

# **EXTERNAL MEMORY CHARACTERISTICS**

|               |                                                   | 24 N       |           |     | MHz        |                 | Oscillator    |      |

|---------------|---------------------------------------------------|------------|-----------|-----|------------|-----------------|---------------|------|

| Symbol        | Parameter                                         | Clo<br>Min | ск<br>Мах |     | ock<br>Max | (3.5 - 4<br>Min | u MHZ)<br>Max | Unit |

| 1/tclcl       | Oscillator frequency                              |            | _         |     | _          | 3.5             | 40            | MHz  |

| tlhll         | ALE pulse width                                   | 68         |           | 35  |            | 2tclcl-15       | <u> </u>      | ns   |

| tavll         | Address valid to ALE low                          | 26         | _         | 10  | _          | tclcl-15        | _             | ns   |

| tllax         | Address hold after ALE low                        | 31         | _         | 15  | _          | tclcl-10        | _             | ns   |

| tlliv         | ALE low to valid instr in                         | _          | 147       | _   | 80         | _               | 4tclcl-20     | ns   |

| tllpl         | ALE low to PSEN low                               | 31         | _         | 15  | _          | tclcl-10        | _             | ns   |

| <b>t</b> PLPH | PSEN pulse width                                  | 110        | _         | 60  | _          | 3tclcl-15       | _             | ns   |

| <b>t</b> PLIV | PSEN low to valid instr in                        | _          | 105       |     | 55         | _               | 3tclcl-20     | ns   |

| tpxix         | Input instr hold after PSEN                       | 0          |           | 0   |            | 0               | _             | ns   |

| <b>t</b> PXIZ | Input instr float after PSEN                      | _          | 37        | _   | 20         | _               | tclcl-5       | ns   |

| taviv         | Address to valid instr in                         | _          | 188       | _   | 105        | _               | 5tclcl-20     | ns   |

| <b>t</b> PLAZ | PSEN low to address float                         | _          | 10        | _   | 10         | _               | 10            | ns   |

| trlrh         | RD pulse width                                    | 230        | _         | 130 | _          | 6tclcl-20       | _             | ns   |

| twlwh         | WR pulse width                                    | 230        | _         | 130 | _          | 6tclcl-20       | _             | ns   |

| trldv         | RD low to valid data in                           | _          | 157       | _   | 90         | _               | 4tclcl-10     | ns   |

| <b>t</b> RHDX | Data hold after RD                                | 0          | _         | 0   | _          | 0               | _             | ns   |

| tRHDZ         | Data float after RD                               | _          | 78        | _   | 45         | _               | 2tclcl-5      | ns   |

| tlldv         | ALE low to valid data in                          | _          | 282       | _   | 165        | _               | 7tclcl-10     | ns   |

| tavdv         | Address to valid data in                          | _          | 323       | _   | 190        | _               | 8tclcl-10     | ns   |

| tllwl         | ALE low to $\overline{RD}$ or $\overline{WR}$ low | 105        | 145       | 55  | 95         | 3tclcl-20       | 3tclcL+20     | ns   |

| <b>t</b> avwl | Address to $\overline{RD}$ or $\overline{WR}$ low | 146        | _         | 80  | _          | 4tclcl-20       | _             | ns   |

| tqvwx         | Data valid to WR transition                       | 26         | _         | 10  | _          | tclcl-15        |               | ns   |

| twhqx         | Data hold after WR                                | 31         | _         | 15  | _          | tclcl-10        |               | ns   |

| trlaz         | RD low to address float                           | _          | 0         | _   | 0          |                 | 0             | ns   |

| twhlh         | RD or WR high to ALE high                         | 26         | 57        | 10  | 40         | tclcl-15        | tclcl+15      | ns   |

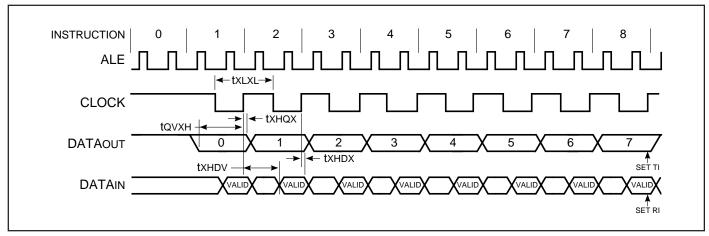

# SERIAL PORT TIMING: SHIFT REGISTER MODE

|        |                                          | 24 MHz<br>Clock |     | 40 MHz<br>Clock |     | Variable Oscillator<br>(3.5-40 MHz) |            |      |

|--------|------------------------------------------|-----------------|-----|-----------------|-----|-------------------------------------|------------|------|

| Symbol | Parameter                                | Min             | Max | Min             | Max | Min                                 | Max        | Unit |

| txLxL  | Serial port clock cycle time             | 490             | 510 | 290             | 310 | 12tclcl-10                          | 12tclcl+10 | ns   |

| tqvxh  | Output data setup to clock rising edge   | 406             | _   | 240             | _   | 10tclcl-10                          | _          | ns   |

| txhqx  | Output data hold after clock rising edge | 73              | _   | 40              | _   | 2tclcl-10                           | _          | ns   |

| txhdx  | Input data hold after clock rising edge  | 0               | _   | 0               | _   | 0                                   | _          | ns   |

| txhdv  | Clock rising edge to input data valid    | _               | 417 | _               | 250 | _                                   | 10tclcl    | ns   |

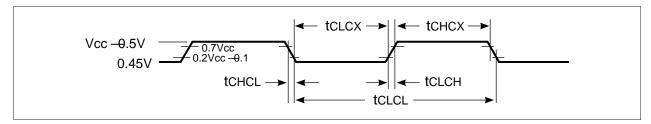

# **EXTERNAL CLOCK DRIVE CHARACTERISTICS**

| Symbol  | Parameter            | Min | Max | Unit |  |

|---------|----------------------|-----|-----|------|--|

| 1/tclcl | Oscillator Frequency | 3.5 | 40  | MHz  |  |

| tchcx   | High time            | 10  | _   | ns   |  |

| tclcx   | Low time             | 10  | _   | ns   |  |

| tclch   | Rise time            | _   | 10  | ns   |  |