# **Buck-Boost Regulator**

#### **DESCRIPTION**

The SiP1759 is a buck-boost regulating charge pump. It is designed to provide a regulated output from 1 cell Li Ion or 2/3 cell NiMH voltages found in handheld portable equipment, 1.6 V to 5.5 V. SiP1759 allows the option of a fixed 3.3 V output voltage, or an adjustable output which can be set from 2.5 V to 5.5 V. The output current is up to 100 mA.

For flexibility in application, SiP1759 has a shutdown pin  $\overline{(SD)}$  and an  $\overline{ERROR}$  output to indicate when the output voltage is in regulation.

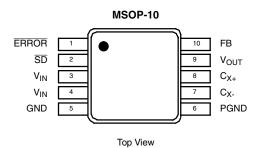

SiP1759 is available in a 10 pin MSOP package and is rated over the industrial temperature range of - 40 °C to 85 °C.

#### **FEATURES**

- Output voltage fixed 3.3 V or adjustable from 2.5 V to 5.5 V

- 1.6 V to 5.5 V input voltage range

- 100 mA output current

- 60 μA quiescent current

- Shutdown current < 1 μA</li>

- · Short circuit crotection

- · Thermal shutdown

- MSOP-10 package

#### **APPLICATIONS**

- 1 cell Li ion battery powered equipment

- · 2 to 3 cell NiMH battery powered equipment

- 2 to 3 cell alkaline battery powered equipment

- Backup battery boost converters

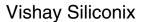

#### TYPICAL APPLICATION CIRCUIT

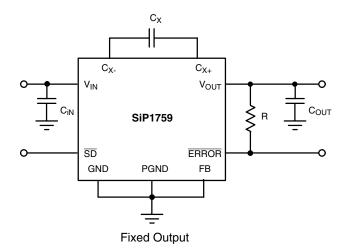

Adjustable Output Voltage

# Vishay Siliconix

| ABSOLUTE MAXIMUM RATINGS (all voltages referenced to GND = 0 V) |                                                                     |    |    |  |  |

|-----------------------------------------------------------------|---------------------------------------------------------------------|----|----|--|--|

| Parameter                                                       | Limit                                                               |    |    |  |  |

| Input Voltage (V <sub>IN</sub> )                                | - 0.3 to 6                                                          |    |    |  |  |

| OUT SD, FB, ERROR to GND                                        | - 0.3 to 6                                                          | V  |    |  |  |

| C <sub>X-</sub> to GND                                          | - 0.3 to (V <sub>IN</sub> + 0.3)                                    |    |    |  |  |

| C <sub>X+</sub> to GND                                          | - 0.3 to (the greater of V <sub>IN</sub> or V <sub>OUT</sub> ) + 1) |    |    |  |  |

| Storage Temperature                                             | - 55 to 150                                                         | °C |    |  |  |

| Maximum Junction Temperature                                    | 150                                                                 | 7  |    |  |  |

| Power Dissipation <sup>a,b</sup>                                | a,b MSOP-10 (T <sub>A</sub> = 70 °C) 444                            |    | mW |  |  |

#### Notes:

- a. Device Mounted with all leads soldered or welded to PC board.

- b. Derate 5.6 mW/°C above 25 °C.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| RECOMMENDED OPERATING RANGE (all voltages referenced to GND = 0 V) |            |      |  |  |

|--------------------------------------------------------------------|------------|------|--|--|

| Parameter                                                          | Limit      | Unit |  |  |

| Input Voltage Range                                                | 1.6 to 5.5 | V    |  |  |

| Output Voltage Adjustment Range                                    | 2.5 to 5.5 | v    |  |  |

| C <sub>IN</sub>                                                    | 10         |      |  |  |

| C <sub>X</sub>                                                     | 0.33       | μF   |  |  |

| C <sub>OUT</sub>                                                   | 10         |      |  |  |

| Operating Temperature Range                                        | - 40 to 85 | °C   |  |  |

| SPECIFICATIONS                     |                       |                                                                                                                       |               |                            |       |                        |       |

|------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------|---------------|----------------------------|-------|------------------------|-------|

|                                    |                       | Test Condition Unless Specified V <sub>IN</sub> = V <sub>SD</sub> = 2 V, FB = PGND = GND                              |               | Limits<br>- 40 °C to 85 °C |       |                        |       |

| Parameter                          | Symbol                | $C_{IN} = 10 \mu F, C_x = 0.33 \mu F, C_{OUT} = 10 \mu F$                                                             | Temp.a        | Min.                       | Typ.b | Max.                   | Unit  |

| Input Voltage Range                | V <sub>IN</sub>       |                                                                                                                       | Full          | 1.6                        |       | 5.5                    |       |

| Input Undervoltage Lockout         | V <sub>UVLO</sub>     |                                                                                                                       | Full          | 0.7                        | 1.0   | 1.5                    |       |

| Output Voltage Adjustment<br>Range |                       | $1.6 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$                                                            | Full          | 2.5                        |       | 5.5                    |       |

|                                    |                       | $2~V \le V_{IN} \le 5.5~V$ , $1~mA \le I_{OUT} \le 50~mA$                                                             | 0 °C to       | 3.17                       | 3.3   | 3.43                   | V     |

| Output Valtage                     | \ \ <u>\</u>          | $2.5 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}, 1 \text{ mA} \le \text{I}_{\text{OUT}} \le 100 \text{ mA}$ | 85 °C         | 3.17                       | 3.3   | 3.43                   |       |

| Output Voltage                     | V <sub>OUT</sub>      | $2 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}, 1 \text{ mA} \le \text{I}_{\text{OUT}} \le 50 \text{ mA}$    | - Full        | 3.15                       |       | 3.45                   |       |

|                                    |                       | $2.5 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}, 1 \text{ mA} \le \text{I}_{\text{OUT}} \le 100 \text{ mA}$ |               | 3.15                       |       | 3.45                   |       |

| Maximum Output Current             | I <sub>OUT(max)</sub> | $2.5 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$                                                            | Full          | 100                        |       |                        | ^     |

| Transient Load Current             |                       | I <sub>OUT</sub> ≤ 100 mA (RMS)                                                                                       | 0 °C to 85 °C |                            | 200   |                        | mA    |

| Outageant Cumply Cumpnt            | IQ                    | V <sub>IN</sub> = V <sub>SD</sub> = 4 V, V <sub>FB</sub> = 0 V, Stepping Down                                         | Full          |                            | 60    | 100                    |       |

| Quiescent Supply Current           |                       | $V_{IN} = V_{SD} = 2 \text{ V}, V_{FB} = 0 \text{ V}, \text{ Stepping Up}$                                            | Full          |                            | 60    | 100                    |       |

| Shutdown Supply Current            | I <sub>QSD</sub>      | $1.6 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}, \text{V}_{\text{SD}} = 0 \text{ V}$                        | Full          |                            | 1     | 5                      | μΑ    |

| Output Leakage Current in SD       |                       | V <sub>IN</sub> = 2 V, V <sub>OUT</sub> = 3.3 V, V <sub>SD</sub> = 0 V                                                | Full          |                            | 1     | 5                      |       |

| SD Logic Input Voltage             | V <sub>IL</sub>       | 1 6 V ≤ V <sub>IN</sub> ≤ 5 5 V                                                                                       | Full          |                            |       | 0.25 * V <sub>IN</sub> | V     |

|                                    | V <sub>IH</sub>       | 10 4 > 4 N > 2 9                                                                                                      | Full          | 0.7 * V <sub>IN</sub>      |       |                        | \ \ \ |

| SD Input Leakage Current           |                       | V <sub>SD</sub> = 5.5 V                                                                                               | Full          | - 1                        |       | 1                      | μΑ    |

| FB Regulation Voltage              | $V_{FB}$              | V <sub>IN</sub> = 1.65 V, V <sub>OUT</sub> = 3.3 V                                                                    | Full          | 1.205                      | 1.235 | 1.265                  | V     |

| FB Input Current                   | I <sub>IFB</sub>      | V <sub>FB</sub> = 1.27 V                                                                                              | Full          |                            | 25    | 200                    | nA    |

| SPECIFICATIONS               |          |                                                                                                 |                    |                            |       |      |       |

|------------------------------|----------|-------------------------------------------------------------------------------------------------|--------------------|----------------------------|-------|------|-------|

|                              |          | Test Condition Unless Specified V <sub>IN</sub> = V <sub>SD</sub> = 2 V, FB = PGND = GND        |                    | Limits<br>- 40 °C to 85 °C |       |      |       |

| Parameter                    | Symbol   | $C_{IN}$ = 10 $\mu$ F, $C_x$ = 0.33 $\mu$ F, $C_{OUT}$ = 10 $\mu$ F                             | Temp. <sup>a</sup> | Min.                       | Typ.b | Max. | Unit  |

| FB Dual Mode Threshold       |          | Internal feedback                                                                               | Full               |                            | 100   | 50   | mV    |

| FB Duai Mode Tillesiloid     |          | External feedback                                                                               | Full               | 200                        | 100   |      | ] ""V |

| ERROR Trip Voltage           |          | Falling edge at FB                                                                              | Full               | 1.0                        | 1.1   | 1.2  | V     |

| ERROR Output Low Voltage     | $V_{OL}$ | $I_{OL} = 0.5 \text{ mA}, V_{IN} = 2 \text{ V}$                                                 | Full               |                            | 5     | 100  | mV    |

| ERROR Leakage Current        |          | V <sub>ERROR</sub> = 5.5 V, V <sub>FB</sub> = 1.27 V                                            | Full               |                            | 0.01  | 0.2  | μΑ    |

| Switching Frequency          | fosc     | $1.6 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}, \text{ V}_{\text{FB}} = 1 \text{ V}$ | Full               | 1.2                        | 1.5   | 1.8  | MHz   |

| Output Short-Circuit Current |          | $V_{OUT} = 0 \text{ V}, 2.5 \text{ V} \le V_{IN} \le 5.5 \text{ V}$ foldback current limit      | Full               |                            | 110   |      | mA    |

| Thermal Shutdown Temperature |          | Temperature rising                                                                              | Full               |                            | 160   |      | °C    |

| Thermal Shutdown Hysteresis  |          |                                                                                                 | Full               |                            | 20    |      | 1     |

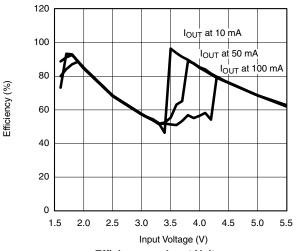

| Efficiency                   |          | V <sub>IN</sub> = 3.6 V, I <sub>OUT</sub> = 10 mA                                               | Full               |                            | 90    |      | %     |

#### Notes:

#### PIN CONFIGURATION AND TRUTH TABLE

| ORDERING INFORMATION |                   |               |  |  |

|----------------------|-------------------|---------------|--|--|

| Part Number          | Temperature Range | Marking       |  |  |

| SiP1759DH-T1         | - 40 °C to 85 °C  | 1759          |  |  |

| Eval Kit             | Temperature Range | Board         |  |  |

| SiP1759DB            | - 40 °C to 85 °C  | Surface Mount |  |  |

| PIN DESCRIPTION |                  |                                                                                                                     |  |  |

|-----------------|------------------|---------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Number      | Name             | Function                                                                                                            |  |  |

| 1               | ERROR            | Open drain error flag - a low output indicates that the output voltage is out of range                              |  |  |

| 2               | SD               | Shutdown input                                                                                                      |  |  |

| 3, 4            | $V_{IN}$         | Input voltage                                                                                                       |  |  |

| 5               | GND              | Ground                                                                                                              |  |  |

| 6               | PGND             | Power ground                                                                                                        |  |  |

| 7               | C <sub>X</sub> - | Negative terminal of the charge pump capacitor                                                                      |  |  |

| 8               | C <sub>X+</sub>  | Positive terminal of the charge pump capacitor                                                                      |  |  |

| 9               | V <sub>OUT</sub> | Regulated output voltage                                                                                            |  |  |

| 10              | FB               | Feedback input - connected to GND for fixed 3.3 V output. Connected to a resistive divider for an adjustable output |  |  |

a. Full = as determined by the operating suffix.

b. Typical values are for Design Aid only, not guaranteed nor subject to production testing.

## Vishay Siliconix

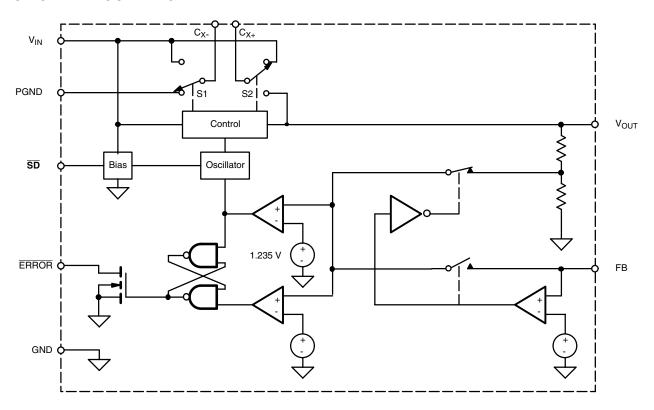

#### **FUNCTIONAL BLOCK DIAGRAM**

#### **DETAILED DESCRIPTION**

The SiP1759 is a buck-boost regulating charge pump. This allows for the  $V_{IN}$  to be a higher or lower voltage than the regulated output. This is done with a charge pump that when  $V_{IN}$  is lower than  $V_{OUT}$  is a regulated voltage doubler. When  $V_{IN}$  is higher than  $V_{OUT}$  the charge pump is a step down gated switch.

In boost mode, the IC controls the transfer capacitor through  $C_{X+}$  and  $C_{X-}$  pins, switching the charge to the output keeping it regulated. In this mode the charge pump only switches to maintain regulation, the output ripple does not increase with light loads. In buck mode, the  $C_{X-}$  pin is internally connected to PGND and the  $C_{X+}$  is switched internally between  $V_{IN}$  and  $V_{OUT}.$  Unless  $V_{IN}$  is significantly larger than  $V_{OUT}$  ( $V_{IN} \geq V_{OUT} + 1$  V), in heavy load the IS will slip from buck mode to boost mode as necessary to charge the transfer capacitor.

#### **Shutdown Mode**

The IC is designed to conserve power by decreasing current consumption during normal operation as well as shutdown mode. Pulling the  $\overline{SD}$  pin logic low, the output is disconnected from the input and is in high impedance; the internal circuitry of the oscillator, control logic, and the charge-pump switches are turned off, decreasing the current consumption to less than 1  $\mu$ A.

#### **Undervoltage Lockout**

When  $V_{\text{IN}}$  falls below 1 V the undervoltage lockout disables the SiP1759.

#### **Power OK Output**

POK is an open-drain output that goes low when the regulator feedback voltage falls below 1.1 V. A 10 k $\Omega$  to 1 M $\Omega$  pull-up resistor from POK to OUT should be used to provide a logic output and keep current consumption to a minimum. Connect POK to GND or leave floating if not used. The POK output is high impedance when the IC is in shutdown mode.

#### **Fixed Output**

The SiP1759 can be configured as a fixed 3.3 V output regulator or as an adjustable output from 2.5 V to 5.5 V. In the fixed 3.3 V output mode the feedback voltage is generated from the internal resistor-divider network. The FB pin must be tied to GND.

#### **Soft-Start and Short Circuit Protection**

The IC features a soft-start mechanism that limits the inrush current during start-up and if the output is short circuited the SiP1759 limits the output current to 110 mA.

#### Thermal Shutdown

The SiP 1759 is designed with a thermal shutdown circuit that will shut down the IC when the die temperature exceeds 160 °C. The thermal shutdown has 20 °C of hysteresis, insuring when the die cools down the IC will turn on again.

#### **DESIGNS CONSIDERATIONS**

#### **Setting the Adjustable Output Voltage**

The SiP1759 regulated output can be adjusted from 2.5 V to 5.5 V via resistor divider network from V\_OUT to GND (see Typical Application Circuits). R1 and R2 should be kept in the 50 k $\Omega$  to 100 k $\Omega$  range for low power consumption, while maintaining adequate noise immunity. The value R1 is calculated using the following formula:

$$R1 = R2 \{(V_{OUT}/V_{FB}) - 1\}$$

V<sub>FR</sub> is nominally 1.235 V.

#### **Capacitor Selection**

Capacitor selection for  $C_{\text{IN}}$ ,  $C_{\text{OUT}}$  and  $C_{\text{X}}$  will have an impact in the voltage output ripple, output current and overall physical size of the circuit.

# minimum. The initial values for the $C_{IN}$ and $C_{OUT}$ capacitors should be 10 $\mu$ F, the $C_X$ capacitor should be 0.33 $\mu$ F.

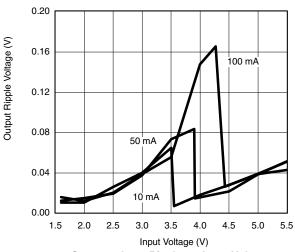

#### **Output Voltage Ripple**

The SiP1759 automatically decides whether to be in step up mode or step down mode depending on the  $V_{IN},\,V_{OUT}$  and current load conditions, therefore the voltage output ripple will vary. In step-up mode the voltage output ripple is higher than step-down mode. But unless  $V_{IN}$  is significant larger than  $V_{OUT}\,(V_{IN} \geq V_{OUT} + 1\,\,V)$ , in heavy load the IC will slip from buck mode to boost mode as necessary to charge the transfer capacitor and the ripple will increase. Reducing the  $C_X$  capacitor value will cause an increase in the switching frequency and a reduction of the output ripple.

Ceramic capacitors are recommenced for their low ESR ( $\leq 20 \text{ m}\Omega$ ) which will help keep the output voltage ripple at a

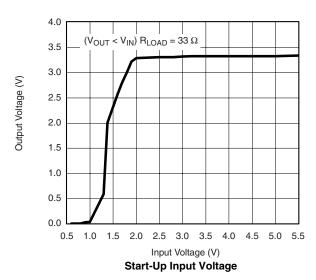

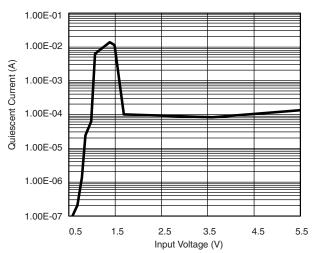

#### **TYPICAL CHARACTERISTICS**

Efficiency vs. Input Voltage

Quiescent Current vs. Input Voltage (No Load)

Output voltage Ripple vs. Input Voltage

# Vishay Siliconix

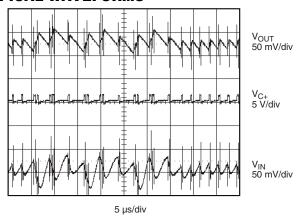

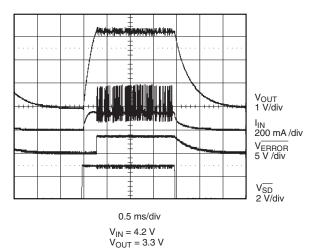

#### TYPICAL WAVEFORMS

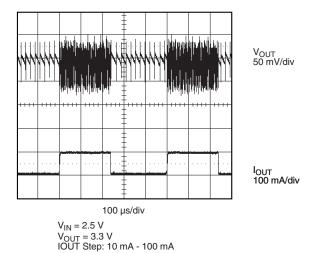

$V_{OUT} = 3.3 \text{ V}$   $R_{LOAD} = 33 \Omega$ Figure 1. Typical Switching Waveform ( $V_{OUT} > V_{IN}$ )

$V_{1N} = 2.5 \text{ V}$

Figure 3. Load Transient Response (V<sub>OUT</sub> > V<sub>IN</sub>)

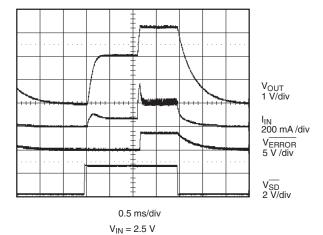

$V_{OUT} = 3.3 \text{ V}$ Figure 5. Turn On/Off Response (V<sub>IN</sub> = 2.5 V)

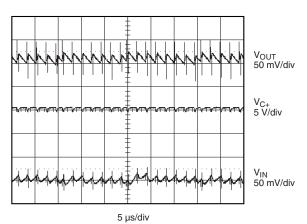

$V_{IN} = 4.2 \text{ V}$  $V_{OUT} = 3.3 \text{ V}$  $R_{LOAD} = 33 \Omega$

Figure 2. Typical Switching Waveforms ( $V_{OUT} > V_{IN}$ )

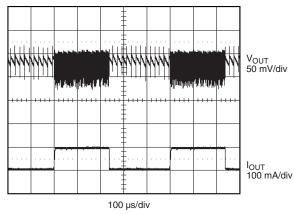

$V_{1N} = 4.2 V$ V<sub>IN</sub> - 4-2 V V<sub>OUT</sub> = 3.3 V IOUT Step: 10 mA - 100 mA Figure 4. Load Transient Response (V<sub>OUT</sub> < V<sub>IN</sub>)

Figure 6. Turn On/Off Response (V<sub>IN</sub> = 4.2 V)

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see <a href="https://www.vishay.com/ppg?72949">www.vishay.com/ppg?72949</a>.

# VISHAY

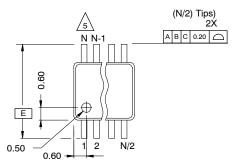

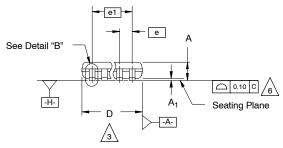

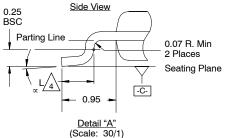

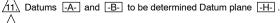

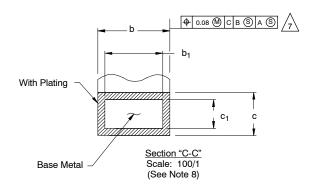

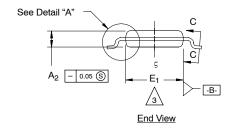

#### MSOP: 10-LEADS (POWER IC ONLY)

JEDEC Part Number: MO-187, (Variation AA and BA)

Top View

1. Die thickness allowable is 0.203 ± 0.0127.

2. Dimensioning and tolerances per ANSI.Y14.5M-1994.

3.

Dimensions "D" and "E $_1$ " do not include mold flash or protrusions, and are measured at Datum plane  $\boxed{-H_2}$ , mold flash or protrusions shall not exceed 0.15 mm per side.

Dimension is the length of terminal for soldering to a substrate.

Terminal positions are shown for reference only.

Formed leads shall be planar with respect to one another within 0.10 mm at seating plane.

The lead width dimension does not include Dambar protrusion. Allowable Dambar protrusion shall be 0.08 mm total in excess of the lead width dimension at maximum material condition. Dambar cannot be located on the lower radius or the lead foot. Minimum space between protrusions and an adjacent lead to be 0.14 mm. See detail "B" and Section "C-C".

Section "C-C" to be determined at 0.10 mm to 0.25 mm from the lead tip.

9. Controlling dimension: millimeters.

10. This part is compliant with JEDEC registration MO-187, variation AA and BA.

$\frac{\lambda}{2\lambda}$  Exposed pad area in bottom side is the same as teh leadframe pad size.

N = 10L

|                                             | MI   |      |      |      |  |  |

|---------------------------------------------|------|------|------|------|--|--|

| Dim                                         | Min  | Nom  | Max  | Note |  |  |

| Α                                           | -    | -    | 1.10 |      |  |  |

| A <sub>1</sub>                              | 0.05 | 0.10 | 0.15 |      |  |  |

| A <sub>2</sub>                              | 0.75 | 0.85 | 0.95 |      |  |  |

| b                                           | 0.17 | -    | 0.27 | 8    |  |  |

| b <sub>1</sub>                              | 0.17 | 0.20 | 0.23 | 8    |  |  |

| С                                           | 0.13 | -    | 0.23 |      |  |  |

| C <sub>1</sub>                              | 0.13 | 0.15 | 0.18 |      |  |  |

| D                                           |      |      | 3    |      |  |  |

| E                                           |      |      |      |      |  |  |

| E <sub>1</sub>                              | 2.90 | 3.00 | 3.10 | 3    |  |  |

| е                                           |      |      |      |      |  |  |

| e <sub>1</sub>                              |      |      |      |      |  |  |

| L                                           | 0.40 | 0.55 | 0.70 | 4    |  |  |

| N                                           |      | 5    |      |      |  |  |

| œ                                           | 0°   | 4°   | 6°   |      |  |  |

| ECN: S-40082—Rev. A, 02-Feb-04<br>DWG: 5922 |      |      |      |      |  |  |

Document Number: 72817

Vishay

### **Disclaimer**

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk and agree to fully indemnify and hold Vishay and its distributors harmless from and against any and all claims, liabilities, expenses and damages arising or resulting in connection with such use or sale, including attorneys fees, even if such claim alleges that Vishay or its distributor was negligent regarding the design or manufacture of the part. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

Revision: 11-Mar-11