# 82573 Family of GbE Controllers

Datasheet

#### **Product Features**

#### ■ PCIe\*

- x1 PCIe\* interface on ICH7 or MCH devices

- Peak bandwidth: 2 Gb/s per direction

- Power management

- High bandwidth density per pin

#### MAC

- Optimized transmit and receive queues

- IEEE 802.3x compliant flow control with software controlled pause times and threshold values

- Caches up to 64 packet descriptors per queue

- Programmable host memory receive buffers (256 bytes to 16 KB) and cache line size (16 bytes to 256 bytes)

- 32 KB configurable transmit and receive FIFO buffer

- Mechanism available for reducing interrupts generated by transmit and receive operation

- Descriptor ring management hardware for transmit and receive

- Optimized descriptor fetching and write-back mechanisms

- Wide, pipelined internal data path architecture

#### - DUV

- Integrated PHY for 10/100/1000 Mb/s full and half duplex operation

- IEEE 802.3ab auto negotiation support

- IEEE 802.3ab PHY compliance and compatibility

- DSP architecture implements digital adaptive equalization, echo cancellation, and cross-talk cancellation

#### Host Offloading

- Transmit and receive IP, TCP and UDP checksum off-loading capabilities

- Transmit TCP segmentation, IPv6 offloading, and advanced packet filtering

- IEEE 802.1q VLAN support with VLAN tag insertion, stripping and packet filtering for up to 4096 VLAN tags

- Descriptor ring management hardware for transmit and receive

#### Manageability

- Intel® Active Management Technology (Intel® AMT) support (82573E only)

- Alerting Standards Format 2.0 and advanced pass through support (82573E/V only)

- Boot ROM Preboot eXecution Environment (PXE) Flash interface support

- Compliance with PCI Power Management 1.1 and Advanced Configuration and Power Interface (ACPI) 2.0 register set compliant

- Wake on LAN support

#### Additional

- Three activity and link indication outputs that directly drive LEDs

- Programmable LEDs

- Internal PLL for clock generation that can use a 25 MHz crystal

- Power saving feature for the 82573L. During the L1 and L2 link states, the 82573L asserts the Clock Request signal (CLKREQ#) to indicate that its PCIe\* reference clock can be gated

- On-chip power control circuitry

- Loopback capabilities

- JTAG (IEEE 1149.1) Test Access Port (TAP) built in silicon

#### Technology

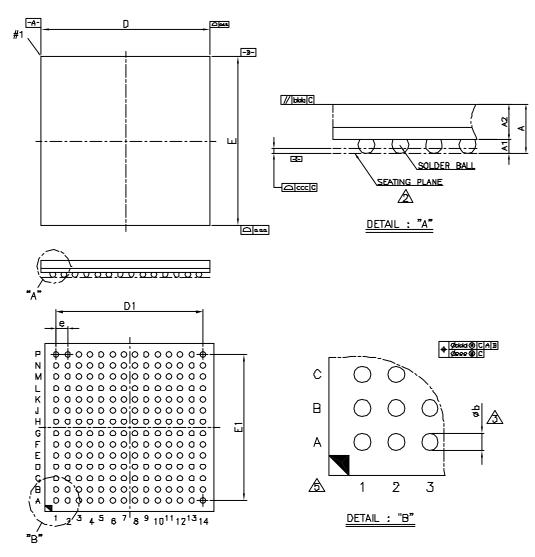

- Lead-free 196-pin Thin and Fine Pitch Ball Grid Array (TF-BGA) package

- Operating temperature: 0° C to 70° C (with external regulators)

- Operating temperature: 0° to 55° C (with ondie 2.5V regulator)

- Storage temperature -40° C to 125° C

Order Number: 315514-002 Revision 2.5

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

IMPORTANT - PLEASE READ BEFORE INSTALLING OR USING INTEL® PRE-RELEASE PRODUCTS

Please review the terms at http://www.intel.com/netcomms/prerelease\_terms.htm carefully before using any Intel® pre-release product, including any evaluation, development or reference hardware and/or software product (collectively, "Pre-Release Product"). By using the Pre-Release Product, you indicate your acceptance of these terms, which constitute the agreement (the "Agreement") between you and Intel Corporation ("Intel"). In the event that you do not agree with any of these terms and conditions, do not use or install the Pre-Release Product and promptly return it unused to Intel.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See http://www.intel.com/products/processor\_number for details.

This document contains information on products in the design phase of development. The information here is subject to change without notice. Do not finalize a design with this information.

The 82573 GbE Controllers may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Hyper-Threading Technology requires a computer system with an Intel<sup>®</sup> Pentium<sup>®</sup> 4 processor supporting HT Technology and a HT Technology enabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. See http://www.intel.com/products/ht/Hyperthreading\_more.htm for additional information.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Intel and Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2007, Intel Corporation. All Rights Reserved.

# Contents

| 1.0 | Intro                      | duction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7                                                                                                        |

|-----|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|     | 1.1                        | Document Scope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8                                                                                                        |

|     | 1.2                        | Reference Documents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8                                                                                                        |

|     | 1.3                        | 82573 Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                          |

|     | 1.4                        | Product Codes for the 82573                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10                                                                                                       |

| 2.0 | Signa                      | al Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10                                                                                                       |

|     | 2.1                        | Signal Type Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                          |

|     | 2.2                        | PCIe* Data Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                          |

|     | 2.3                        | PCIe* Miscellaneous Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                          |

|     | 2.4                        | Non-Volatile Memory Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                          |

|     | 2.5                        | Miscellaneous Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                          |

|     | 2.0                        | 2.5.1 Reset and Power-down Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                          |

|     |                            | 2.5.2 System Management Bus (SMBus) Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13                                                                                                       |

|     |                            | 2.5.3 LED Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                          |

|     |                            | 2.5.4 Other Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                          |

|     | 2.6                        | PHY Analog and Crystal Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                          |

|     | 2.7                        | Test Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                          |

|     |                            | 2.7.1 MAC Test Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                          |

|     |                            | 2.7.2 PHY Test Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                          |

|     |                            | 2.7.3 Other Test Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                          |

|     | 2.8                        | Power Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |

|     |                            | 2.8.1 Power Support Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16                                                                                                       |

|     |                            | 2.8.2 Digital and Analog Power Supply Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 16                                                                                                       |

|     | 2.9                        | Grounds and No Connects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16                                                                                                       |

|     | ,                          | Crounds and the connects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . ~                                                                                                      |

| 3.0 |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                          |

| 3.0 | Volta                      | ge, Temperature, and Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17                                                                                                       |

| 3.0 | Volta<br>3.1               | ge, Temperature, and Timing Specifications  Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17<br>17                                                                                                 |

| 3.0 | <b>Volta</b> 3.1 3.2       | ge, Temperature, and Timing Specifications  Absolute Maximum Ratings  Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17<br>17<br>17                                                                                           |

| 3.0 | Volta<br>3.1               | ge, Temperature, and Timing Specifications  Absolute Maximum Ratings  Recommended Operating Conditions  Power Supply Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17<br>17<br>17<br>17                                                                                     |

| 3.0 | <b>Volta</b> 3.1 3.2       | ge, Temperature, and Timing Specifications  Absolute Maximum Ratings  Recommended Operating Conditions  Power Supply Connections  3.3.1 External LVR Power Delivery                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17<br>17<br>17<br>17<br>18                                                                               |

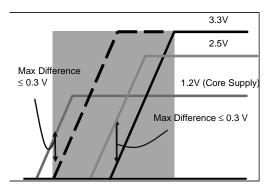

| 3.0 | <b>Volta</b> 3.1 3.2       | ge, Temperature, and Timing Specifications  Absolute Maximum Ratings  Recommended Operating Conditions  Power Supply Connections  3.3.1 External LVR Power Delivery  3.3.2 Power Sequencing with External Regulators                                                                                                                                                                                                                                                                                                                                                                                                 | 17<br>17<br>17<br>17<br>18                                                                               |

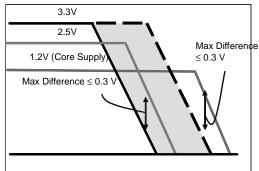

| 3.0 | <b>Volta</b> 3.1 3.2       | Absolute Maximum Ratings Recommended Operating Conditions Power Supply Connections 3.3.1 External LVR Power Delivery 3.3.2 Power Sequencing with External Regulators 3.3.3 Internally Generated Power Delivery                                                                                                                                                                                                                                                                                                                                                                                                       | 17<br>17<br>17<br>18<br>19<br>20                                                                         |

| 3.0 | <b>Volta</b> 3.1 3.2       | Absolute Maximum Ratings Recommended Operating Conditions Power Supply Connections 3.3.1 External LVR Power Delivery 3.3.2 Power Sequencing with External Regulators 3.3.3 Internally Generated Power Delivery                                                                                                                                                                                                                                                                                                                                                                                                       | 17<br>17<br>17<br>17<br>18<br>19<br>20<br>21                                                             |

| 3.0 | Volta<br>3.1<br>3.2<br>3.3 | Absolute Maximum Ratings Recommended Operating Conditions Power Supply Connections 3.3.1 External LVR Power Delivery 3.3.2 Power Sequencing with External Regulators 3.3.3 Internally Generated Power Delivery 3.3.4 Internal LVR Power Sequencing                                                                                                                                                                                                                                                                                                                                                                   | 17<br>17<br>17<br>18<br>19<br>20<br>21<br>25                                                             |

| 3.0 | Volta 3.1 3.2 3.3          | Absolute Maximum Ratings Recommended Operating Conditions Power Supply Connections 3.3.1 External LVR Power Delivery 3.3.2 Power Sequencing with External Regulators 3.3.3 Internally Generated Power Delivery 3.3.4 Internal LVR Power Sequencing DC and AC Specifications                                                                                                                                                                                                                                                                                                                                          | 17<br>17<br>17<br>17<br>18<br>19<br>20<br>21<br>25<br>28                                                 |

| 3.0 | Volta 3.1 3.2 3.3          | Absolute Maximum Ratings Recommended Operating Conditions Power Supply Connections 3.3.1 External LVR Power Delivery 3.3.2 Power Sequencing with External Regulators 3.3.3 Internally Generated Power Delivery 3.3.4 Internal LVR Power Sequencing DC and AC Specifications External Interfaces 3.5.1 Crystal 3.5.2 External Clock Oscillator                                                                                                                                                                                                                                                                        | 17<br>17<br>17<br>18<br>19<br>20<br>21<br>25<br>28<br>28<br>28                                           |

| 3.0 | Volta 3.1 3.2 3.3          | Absolute Maximum Ratings Recommended Operating Conditions Power Supply Connections 3.3.1 External LVR Power Delivery 3.3.2 Power Sequencing with External Regulators 3.3.3 Internally Generated Power Delivery 3.3.4 Internal LVR Power Sequencing DC and AC Specifications External Interfaces 3.5.1 Crystal                                                                                                                                                                                                                                                                                                        | 17<br>17<br>17<br>18<br>19<br>20<br>21<br>25<br>28<br>28<br>28                                           |

|     | Volta 3.1 3.2 3.3          | Absolute Maximum Ratings Recommended Operating Conditions Power Supply Connections 3.3.1 External LVR Power Delivery 3.3.2 Power Sequencing with External Regulators 3.3.3 Internally Generated Power Delivery 3.3.4 Internal LVR Power Sequencing DC and AC Specifications External Interfaces 3.5.1 Crystal 3.5.2 External Clock Oscillator 3.5.3 Non-Volatile Memory (NVM) Interface: EEPROM                                                                                                                                                                                                                      | 17<br>17<br>17<br>18<br>19<br>20<br>21<br>25<br>28<br>28<br>28                                           |

| 4.0 | Volta 3.1 3.2 3.3 3.4 3.5  | Absolute Maximum Ratings Recommended Operating Conditions Power Supply Connections 3.3.1 External LVR Power Delivery 3.3.2 Power Sequencing with External Regulators 3.3.3 Internally Generated Power Delivery 3.3.4 Internal LVR Power Sequencing DC and AC Specifications External Interfaces 3.5.1 Crystal 3.5.2 External Clock Oscillator 3.5.3 Non-Volatile Memory (NVM) Interface: EEPROM                                                                                                                                                                                                                      | 17<br>17<br>17<br>17<br>18<br>19<br>20<br>21<br>25<br>28<br>28<br>28<br>29                               |

|     | Volta 3.1 3.2 3.3 3.4 3.5  | Absolute Maximum Ratings Recommended Operating Conditions Power Supply Connections 3.3.1 External LVR Power Delivery 3.3.2 Power Sequencing with External Regulators 3.3.3 Internally Generated Power Delivery 3.3.4 Internal LVR Power Sequencing DC and AC Specifications External Interfaces 3.5.1 Crystal 3.5.2 External Clock Oscillator 3.5.3 Non-Volatile Memory (NVM) Interface: EEPROM  age and Pinout Information Package Information                                                                                                                                                                      | 17<br>17<br>17<br>17<br>18<br>19<br>20<br>21<br>25<br>28<br>28<br>29<br>30<br>30                         |

|     | Volta 3.1 3.2 3.3  3.4 3.5 | Absolute Maximum Ratings Recommended Operating Conditions Power Supply Connections 3.3.1 External LVR Power Delivery 3.3.2 Power Sequencing with External Regulators 3.3.3 Internally Generated Power Delivery 3.3.4 Internal LVR Power Sequencing DC and AC Specifications External Interfaces 3.5.1 Crystal 3.5.2 External Clock Oscillator 3.5.3 Non-Volatile Memory (NVM) Interface: EEPROM Package Information Thermal Specifications                                                                                                                                                                           | 17<br>17<br>17<br>17<br>18<br>19<br>20<br>21<br>25<br>28<br>28<br>29<br>30<br>30<br>32                   |

|     | Volta 3.1 3.2 3.3 3.4 3.5  | Absolute Maximum Ratings Recommended Operating Conditions Power Supply Connections 3.3.1 External LVR Power Delivery 3.3.2 Power Sequencing with External Regulators 3.3.3 Internally Generated Power Delivery 3.3.4 Internal LVR Power Sequencing DC and AC Specifications External Interfaces 3.5.1 Crystal 3.5.2 External Clock Oscillator 3.5.3 Non-Volatile Memory (NVM) Interface: EEPROM  Package Information Thermal Specifications Pinout Information Pinout Information                                                                                                                                    | 17<br>17<br>17<br>17<br>18<br>19<br>20<br>21<br>25<br>28<br>29<br>30<br>30<br>32<br>33                   |

|     | Volta 3.1 3.2 3.3  3.4 3.5 | Absolute Maximum Ratings Recommended Operating Conditions Power Supply Connections 3.3.1 External LVR Power Delivery 3.3.2 Power Sequencing with External Regulators 3.3.3 Internally Generated Power Delivery 3.3.4 Internal LVR Power Sequencing DC and AC Specifications External Interfaces 3.5.1 Crystal 3.5.2 External Clock Oscillator 3.5.3 Non-Volatile Memory (NVM) Interface: EEPROM  age and Pinout Information Package Information Thermal Specifications Pinout Information Pinout Information Pole Bus Interface Signals                                                                              | 17<br>17<br>17<br>18<br>19<br>20<br>21<br>25<br>28<br>28<br>29<br>30<br>30<br>32<br>33<br>33             |

|     | Volta 3.1 3.2 3.3  3.4 3.5 | Absolute Maximum Ratings Recommended Operating Conditions Power Supply Connections 3.3.1 External LVR Power Delivery 3.3.2 Power Sequencing with External Regulators 3.3.3 Internally Generated Power Delivery 3.3.4 Internal LVR Power Sequencing DC and AC Specifications External Interfaces 3.5.1 Crystal 3.5.2 External Clock Oscillator 3.5.3 Non-Volatile Memory (NVM) Interface: EEPROM  age and Pinout Information Package Information Thermal Specifications Pinout Information 4.3.1 PCIe Bus Interface Signals 4.3.2 Non-Volatile Memory Interface Signals                                               | 17<br>17<br>17<br>17<br>18<br>19<br>20<br>21<br>25<br>28<br>28<br>29<br>30<br>32<br>33<br>33<br>34       |

|     | Volta 3.1 3.2 3.3  3.4 3.5 | Absolute Maximum Ratings Recommended Operating Conditions Power Supply Connections 3.3.1 External LVR Power Delivery 3.3.2 Power Sequencing with External Regulators 3.3.3 Internally Generated Power Delivery 3.3.4 Internal LVR Power Sequencing DC and AC Specifications. External Interfaces 3.5.1 Crystal 3.5.2 External Clock Oscillator 3.5.3 Non-Volatile Memory (NVM) Interface: EEPROM age and Pinout Information Package Information Thermal Specifications Pinout Information 4.3.1 PCIe Bus Interface Signals 4.3.2 Non-Volatile Memory Interface Signals 4.3.3 Miscellaneous Signals                   | 17<br>17<br>17<br>17<br>18<br>19<br>20<br>21<br>25<br>28<br>29<br>30<br>32<br>33<br>33<br>34<br>34       |

|     | Volta 3.1 3.2 3.3  3.4 3.5 | Absolute Maximum Ratings Recommended Operating Conditions Power Supply Connections 3.3.1 External LVR Power Delivery 3.3.2 Power Sequencing with External Regulators 3.3.3 Internally Generated Power Delivery 3.3.4 Internal LVR Power Sequencing DC and AC Specifications External Interfaces 3.5.1 Crystal 3.5.2 External Clock Oscillator 3.5.3 Non-Volatile Memory (NVM) Interface: EEPROM  age and Pinout Information Package Information Thermal Specifications Pinout Information 4.3.1 PCIe Bus Interface Signals 4.3.2 Non-Volatile Memory Interface Signals 4.3.3 Miscellaneous Signals 4.3.4 PHY Signals | 17<br>17<br>17<br>17<br>18<br>19<br>20<br>21<br>25<br>28<br>28<br>29<br>30<br>32<br>33<br>34<br>34<br>35 |

|     | Volta 3.1 3.2 3.3  3.4 3.5 | Absolute Maximum Ratings Recommended Operating Conditions Power Supply Connections 3.3.1 External LVR Power Delivery 3.3.2 Power Sequencing with External Regulators 3.3.3 Internally Generated Power Delivery 3.3.4 Internal LVR Power Sequencing DC and AC Specifications. External Interfaces 3.5.1 Crystal 3.5.2 External Clock Oscillator 3.5.3 Non-Volatile Memory (NVM) Interface: EEPROM age and Pinout Information Package Information Thermal Specifications Pinout Information 4.3.1 PCIe Bus Interface Signals 4.3.2 Non-Volatile Memory Interface Signals 4.3.3 Miscellaneous Signals                   | 17<br>17<br>17<br>17<br>18<br>19<br>20<br>21<br>25<br>28<br>29<br>30<br>32<br>33<br>34<br>35<br>35       |

# **Figures**

| 1 | 82573 Block Diagram                                  | 9  |

|---|------------------------------------------------------|----|

|   | Minimum Requirements for Power Supply Sequencing     |    |

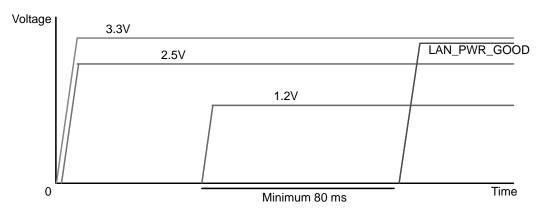

|   | Power Supply Sequencing                              |    |

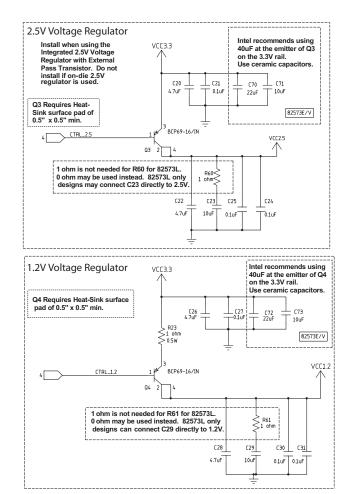

|   | 82573 2.5V and 1.2V LVR Schematic                    |    |

|   | External Clock Oscillator Connectivity to the 82573  |    |

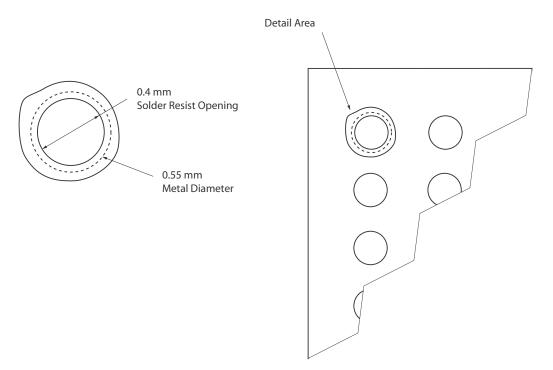

|   | 82573 Controller TF-BGA Package Ball Pad Dimensions  |    |

|   |                                                      |    |

| 8 | 82573E and 82573V Gigabit Ethernet Controller Pinout | 38 |

|   | 82573L Gigabit Ethernet Controller Pinout            |    |

## Tables

| 1  | Absolute Maximum Ratings                                           | . 17 |

|----|--------------------------------------------------------------------|------|

| 2  | Recommended Operating Conditions                                   | . 17 |

| 3  | 3.3V External Supply Voltage Ramp and Sequencing Recommendations   | . 18 |

| 4  | 2.5V External Supply Voltage Ramp and Sequencing Recommendations   | . 18 |

| 5  | 1.2V External Supply Voltage Ramp and Sequencing Recommendations   |      |

| 6  | 3.3V Internal Power Supply Parameters                              |      |

| 7  | 82573 Bill of Materials (BOM) of Components for Internal Regulator | . 22 |

| 8  | 2.5V Internal LVR Specification                                    |      |

| 9  | 1.2V Internal LVR Specification                                    | . 23 |

| 10 | PNP Specification                                                  | . 23 |

| 11 | 82573E and 82573V Maximum Measured External Power Characteristics  | . 25 |

| 12 | 82573E and 82573V Typical Measured External Power Characteristics  | . 26 |

| 13 | 82573E and 82573V 2.5V Internal Power Regulator Numbers            | . 26 |

| 14 | 82573L Maximum Measured Power Characteristics                      |      |

| 15 | 82573L Measured Power Characteristics                              | . 27 |

| 16 | DC Specifications                                                  | . 27 |

| 17 | LED DC Specifications                                              | . 28 |

| 18 | Crystal Specifications                                             |      |

| 19 | Specification for External Clock Oscillator                        |      |

| 20 | NVM Interface Timing Specifications for EEPROM                     | . 29 |

| 21 | Thermal Resistance Values                                          | . 33 |

| 22 | PCIe Data Signals                                                  |      |

| 23 | PCI Express Miscellaneous Signals                                  |      |

| 24 | Non-Volatile Memory Interface Signals                              |      |

| 25 | Reset and Power-down Signals                                       | . 34 |

| 26 | SMBus Signals                                                      |      |

| 27 | LED Signals                                                        | . 34 |

| 28 | Other Signals                                                      |      |

| 29 | Analog and Crystal Signals                                         |      |

| 30 | 82573E/V MAC Test Signals                                          |      |

| 31 | 82573L MAC Test Signals                                            |      |

| 32 | PHY Test Interface Signals                                         |      |

| 33 | 82573E/V Other Test Signals                                        |      |

| 34 | Power Support Signals                                              |      |

| 35 | Power Signals                                                      |      |

| 36 | Ground Signals                                                     |      |

| 37 | 82573E/V No Connect Signals                                        |      |

| 38 | 82573L No Connect Signals                                          | . 37 |

|    |                                                                    |      |

# **Revision History**

| Date        | Revision | Description                                                                                                                                                                                                          |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Jan 2007    | 2.5      | Updated the PHY_REF signal description in Section 2.6.                                                                                                                                                               |

| Oct 2006    | 2.4      | Added document order number.  Corrected the AUX_PWR pin (C6) description for the 82573E/V.  Updated Table 18 "Crystal Specifications".  Updated the visual pin assignments for the 82573L.  Major edit all sections. |

| August 2006 | 2.3      | Chapter 1, Introduction, corrected note. 3.5.1, Removed line item 3.5.2, Corrected title Heading                                                                                                                     |

| June 2006   | 2.2      | Revised Section 3.3, 'PCIe Miscellaneous Signals", updated Intel logo.                                                                                                                                               |

| Feb 2006    | 2.1      | Added Section 5.2, 'Thermal Specifications"."                                                                                                                                                                        |

| Sept 2005   | 2.0      | Integrated 82573L information into this document.                                                                                                                                                                    |

| June 2005   | 1.5      | Initial public release.                                                                                                                                                                                              |

### 1.0 Introduction

Note:

Unless specifically noted, 82573 refers to the Intel® 82573E, 82573V and 82573L GbE controllers.

82573 GbE controllers are single, compact components with integrated Gigabit Ethernet Media Access Control (MAC) and Physical Layer (PHY) functions. These devices use PCIe\* architecture (Revision 1.0a). For desktop, workstation, and value server network designs with critical space constraints, the 82573 enables a GbE implementation in a very small area.

The 82573 provides a standard IEEE 802.3 Ethernet interface for 1000BASE-T, 100BASE-TX, and 10BASE-T applications (802.3, 802.3u, and 802.3ab, respectively). In addition to managing MAC and PHY Ethernet layer functions, the 82573 manages PCIe\* packet traffic across its transaction, link, and physical and logical layers.

The 82573E contains a dedicated microcontroller for manageability with an on-board Intel® Active Management Technology (Intel® AMT) enabling network. This enables manageability implementations required by information technology personnel for out-of-band management, remote troubleshooting and recovery, asset management, and non-volatile storage. Intel® AMT is the first step towards a complete Intel® Cross-Platform Manageability Program (Intel® CPMP), which is a business and technology initiative to deliver consistent management capabilities, protocols, and interfaces across all Intel platforms.

The 82573E and 82573V GbE controllers have an integrated System Management Bus (SMBus) port enabling industry standards, such as the Alert Standard Forum (ASF) 2.0. With SMBus, management packets can be routed to or from a management processor. In addition, integrated ASF 2.0 circuitry provides alerting and capabilities with standardized interfaces.

The 82573 with PCIe\* architecture is designed for high performance and low memory latency. The device is optimized to connect to a system I/O Control Hub (ICH7) using one PCIe\* lane. Alternatively, the 82573 is able to connect to a Memory Control Hub (MCH) device with a PCIe\* interface.

Wide internal data paths eliminate performance bottlenecks by efficiently handling large address and data words. The 82573 efficiently handles packets with minimum latency by combining a parallel and pipelined logic architecture optimized for GbE and independent transmit and receive queues. The 82573 also includes advanced interrupt handling features and uses efficient ring buffer descriptor data structures, with up to 64 packet descriptors per queue cached on chip. A 32-KB on-chip packet buffer maintains superior performance. In addition, using hardware acceleration, the 82573 offloads tasks from the host (for example, TCP/UDP/IP checksum calculations and TCP segmentation).

The 82573L features low power management. During the L1 and L2 link states, the 82573L asserts the Clock Request signal (CLKREQ#) to indicate that its PCIe\* reference clock can be gated.

The 82573 is packaged in a 15 mm X 15 mm, 196-Ball Grid Array (BGA).

### 1.1 Document Scope

This document contains targeted datasheet specifications for the 82573 GbE controller, including signal descriptions, DC and AC parameters, packaging data, and pinout information.

#### 1.2 Reference Documents

This application assumes that the designer is acquainted with high-speed design and board layout techniques. The following documents provide additional information:

- IEEE Standard 802.3, 2000 Edition. Institute of Electrical and Electronics Engineers (IEEE).

- PCI Express Base Specification, Revision 1.0a. PCI Special Interest Group.

- PCI Express Card Electromechanical Specification, Revision 1.0a. PCI Special Interest Group.

- PCI Bus Power Management Interface Specification, Revision 1.1. PCI Special Interest Group.

- Intel Ethernet Controller Timing Device Selection Guide. Intel Corporation.

- 82573 NVM Map and Programming Information Guide. Intel Corporation.

- 82573/82562 Dual Footprint Design Guide. Intel Corporation.

- PCIe\* Family of Gigabit Ethernet Controllers Software Developer's Manual. Intel Corporation.

- 82573 Family GbE Controllers Specification Update. Intel Corporation.

### 1.3 82573 Architecture

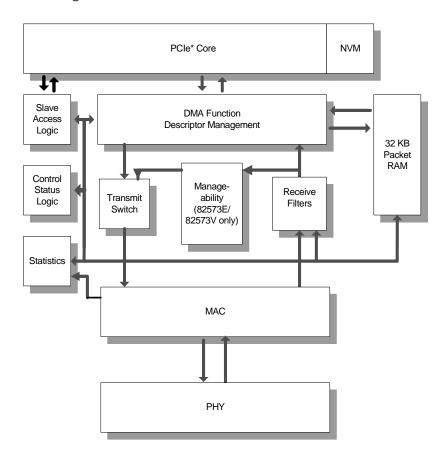

Figure 1. 82573 Block Diagram

Note: The 82573L does not support manageability.

## 1.4 Product Codes for the 82573

| Device | Top Marking | Leaded/<br>Unleaded | Product Features                                                                |

|--------|-------------|---------------------|---------------------------------------------------------------------------------|

| 82573E | RC82573E    | Leaded              | 82573E with Intel® AMT includes: Intel® AMT ASF 2.0 Advanced Pass Through (APT) |

| 82573E | PC82573E    | Lead Free           | 82573E with Intel® AMT includes: Intel® AMT ASF 2.0 APT                         |

| 82573V | RC82573V    | Leaded              | 82573V Baseline includes:  • ASF 2.0  • APT                                     |

| 82573V | PC82573V    | Lead Free           | 82573V Baseline includes: • ASF 2.0 • APT                                       |

| 82573L | RC82573L    | Leaded              | 82573L: • Low-power • No management                                             |

| 82573L | PC82573L    | Lead Free           | 82573L: • Low-power • No management                                             |

# 2.0 Signal Descriptions

# 2.1 Signal Type Definitions

The signals of the 82573 are electrically defined as follows:

| Name | Definition                                                                                                                                                                                                                                                                                 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Input Standard input only digital signal.                                                                                                                                                                                                                                                  |

| 0    | Output<br>Standard output only digital signal.                                                                                                                                                                                                                                             |

| 1/0  | I/O<br>Standard I/O digital signal.                                                                                                                                                                                                                                                        |

| TS   | Tri-state Bi-directional three-state digital input/output signal.                                                                                                                                                                                                                          |

| OD   | Open Drain Wired-OR with other agents. The signaling agent asserts the open drain signal, but the signal is returned to the inactive state by a weak pull-up resistor. The pull-up resistor might require two or three clock periods to fully restore the signal to the de-asserted state. |

| А    | Analog PCIe, SerDes, or PHY analog signal.                                                                                                                                                                                                                                                 |

| Р    | Power Power connection, voltage reference, or other reference connection.                                                                                                                                                                                                                  |

| Name | Definition                                           |

|------|------------------------------------------------------|

| В    | Input Bias                                           |

| PU   | Pull Up This signal requires a pull-up resistor.     |

| PD   | Pull Down This signal requires a pull-down resistor. |

## 2.2 PCIe\* Data Signals

| Signal             | Туре   | Name and Function                                                                                                                                                                                                                                                                               |

|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PE_CLKn<br>PE_CLKp | A(In)  | PCIe Differential Reference Clock The reference clock is furnished by the system and has a 300 ppm frequency tolerance. It is used as reference clock for PCIe transmit and receive circuitry and is used by the PCIe core PLL to generate 125 MHz and 250 MHz clocks for the PCIe* core logic. |

| PE_TOn<br>PE_TOp   | A(Out) | PCIe* Serial Data Output  These signals connect to corresponding PERn and PERp signals on a system motherboard or a PCIe* connector. Series AC coupling capacitors are required at the 82573 device end. The PCIe* differential outputs are clocked at 2.5 Gb/s.                                |

| PE_ROn<br>PE_ROp   | A(In)  | PCIe Serial Data Input These signals connect to corresponding PETn and PETp signals on a system motherboard or a PCIe* connector. The PCIe* differential inputs are clocked at 2.5 Gb/s.                                                                                                        |

# 2.3 PCIe\* Miscellaneous Signals

| Signal                                    | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PE_RST#                                   | I    | Reset This signal indicates whether or not the PCIe* power and clock are available.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PE_WAKE#                                  | OD   | Wake This signal is driven to zero when it receives a wake-up packet and either the PME enable bit of the Power Management Control/Status Register is set to 1b or the Advanced Power Management enabled bit of the Wake Up Control Register equals 1b.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| AUX_<br>PRESENT<br>(AUX_PWR) <sup>1</sup> | I    | Auxiliary Power Present  AUX_PRESENT must be pulled up to 3.3V standby power if the 82573 is powered from standby supplies. This signal must be pulled down if auxiliary power is not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CLKREQ#<br>(82573L only)                  | OD   | Clock Request.  The Clock Request (CLKREQ#) signal is located at ball P9 of the 82573L. When it is sampled high, this open-drain signal alerts the system that the 82573L does not need the PCIe* differential reference clock. During normal operation, the 82573L keeps CLKREQ# asserted (low), and the system supplies this clock to the device on the PE_CLKp and PE_CLKn signals. The 82573L deasserts CLKREQ# (high) when it is in an electrical idle state (L1 and L2), and the system might choose to continue supplying the reference clock or gate it conserving platform power. The CLKREQ# signal should be connected to the clock driver that supplies the 82573L PCIe* clock. If other devices use the same CLKREQ# signal, a pull-up resistor should be used to ensure that no device pulls this signal low when it is powered off. |

This signal is used in all three devices and has the same functionality but is denoted as AUX\_PRESENT in the 82573E/V and AUX\_PWR in the 82573L.

11

# 2.4 Non-Volatile Memory Interface Signals

| Signal      | Туре    | Name and Function                                                                                                                                                                                                                                                        |

|-------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NVM_SI      | 1/0     | NVM Serial Data Output  The data output pin is used for input to the non-volatile memory device. This pin is occasionally used as input during arbitration. This signal has an internal pull-up resistor.                                                                |

| NVM_SO      | I       | NVM Serial Data Input The data input pin is used for output from the non-volatile memory device to the 82573. This signal has an internal pull-up resistor.                                                                                                              |

| NVM_SK      | O<br>TS | NVM Serial Clock The serial clock provides the clock rate for the memory interface.                                                                                                                                                                                      |

| NVM_CS#     | 1/0     | NVM Chip Enable This signal is used to enable the device. This signal has an internal pull-up resistor.                                                                                                                                                                  |

| NVM_REQ     | 0       | NVM Arbitration Request. This signal is used to request use of the NVM interface.                                                                                                                                                                                        |

| NVM_PROT    | I/PU    | NVM Protection Enable.  This pin should be connected to ground to disable NVM protection; otherwise, NVM protection is enabled. This signal has an internal pull-up resistor.                                                                                            |

| NVM_TYPE    | I/PU    | NVM Device Type If the device uses a Flash, this pin should be connected to a pull-down resistor. If the 82573 is connected to an EEPROM, this pin can be connected to an external pull-up resistor. This signal has an internal pull-up resistor of 30 K $\Omega$ ±50%. |

| NVM_SHARED# | I/PU    | NVM Shared Enable This pin should be connected to a pull-down resistor to enable sharing of SPI Flash with ICH. This signal has an internal pull-up resistor.                                                                                                            |

# 2.5 Miscellaneous Signals

## 2.5.1 Reset and Power-down Signals

| Signal           | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LAN_PWR_<br>GOOD | I    | LAN Power Good This signal indicates that stable power is available to the 82573. When the signal is low, LAN_PWR_GOOD acts as a master reset of the entire device. LAN_PWR_GOOD should be connected to a power supervisor driven from auxiliary power. The signal should go active approximately 80 ms after all power rails are within their operating ranges.  A PCIe* reset must only occur after LAN Power Good is active. |

| DEVICE_OFF#      | I    | Device Off This asynchronously disables the 82573, including voltage regulator control outputs if selected in external control.                                                                                                                                                                                                                                                                                                 |

## 2.5.2 System Management Bus (SMBus) Signals<sup>1</sup>

Note:

The signals listed in the following table should not be connected when using an 82573L. Refer to the *82573/82562 Dual Footprint Design Guide* reference schematics for more information.

| Signal                         | Туре | Name and Function                                                                                                                                                        |

|--------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMB_CLK                        | 1/0  | SMBus Clock The SMBus Clock signal is an open drain signal for the serial SMBus interface.                                                                               |

| SMB_DAT                        | 1/0  | SMBus Data The SMB Data signal is an open drain signal for the serial SMBus interface.                                                                                   |

| SMB_ALRT#/<br>ASF_PWR_<br>GOOD | 1/0  | SMBus Alert/PCI Power Good  The SMBus Alert signal is an open drain signal for serial SMBus interface. In ASF mode, this signal acts as the PCI Power Good input signal. |

### 2.5.3 LED Signals

| Signal | Туре | Name and Function                                                |  |

|--------|------|------------------------------------------------------------------|--|

| LED0#  | 0    | LEDO This pin provides a signal for programmable LED indication. |  |

| LED1#  | 0    | LED1 This pin provides a signal for programmable LED indication. |  |

| LED2#  | 0    | LED2 This pin provides a signal for programmable LED indication. |  |

## 2.5.4 Other Signals

| Signal           | Туре | Name and Function                                                                                |  |

|------------------|------|--------------------------------------------------------------------------------------------------|--|

| THERMn<br>THERMp | 0    | Thermal Test Pins These pins are used for thermal testing. They can be connected to test points. |  |

| I FLISEV I P     |      | Fuse Supply This should be connected to 2.5V for normal operation.                               |  |

13

<sup>1.</sup> The 82573L does not support the System Management Bus (SMBus).

# 2.6 PHY Analog and Crystal Signals

| Signal         | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MDIOn<br>MDIOp |      | Media Dependent Interface [0]  1000BASE-T: In MDI configuration, MDIp0/MDIn0 corresponds to BI_DA+/-, and in MDI-X configuration, MDIp0/MDIn0 corresponds to BI_DB+/  100BASE-TX: In MDI configuration, MDIp0/MDIn0 is used for the transmit pair, and in MDI-X configuration, MDIp0/MDIn0 is used for the receive pair.  10BASE-T: In MDI configuration, MDIp0/MDIn0 is used for the transmit pair, and in MDI-X configuration, MDIp0/MDIn0 is used for the transmit pair, and in MDI-X configuration, MDIp0/MDIn0 is used for the receive pair. |

| MDI1n<br>MDI1p | А    | Media Dependent Interface [1]  1000BASE-T: In MDI configuration, MDIp1/MDIn1 corresponds to BI_DB+/-, and in MDI-X configuration, MDIp1/MDIn1 corresponds to BI_DA+/  100BASE-TX: In MDI configuration, MDIp1/MDIn1 is used for the receive pair, and in MDI-X configuration, MDIp1/MDIn1 is used for the transmit pair.  10BASE-T: In MDI configuration, MDIp1/MDIn1 is used for the receive pair, and in MDI-X configuration, MDIp1/MDIn1 is used for the receive pair, and in MDI-X configuration, MDIp1/MDIn1 is used for the transmit pair.  |

| MDI2n<br>MDI2p | А    | Media Dependent Interface [2] 1000BASE-T: In MDI configuration, MDIp2/MDIn2 corresponds to BI_DC+/-, and in MDI-X configuration, MDIp2/MDIn2 corresponds to BI_DD+/ 100BASE-TX: Unused. 10BASE-T: Unused.                                                                                                                                                                                                                                                                                                                                         |

| MDI3n<br>MDI3p | А    | Media Dependent Interface [3] 1000BASE-T: In MDI configuration, MDIp3/MDIn3 corresponds to BI_DD+/-, and in MDI-X configuration, MDIp3/MDIn3 corresponds to BI_DC+/ 100BASE-TX: Unused. 10BASE-T: Unused.                                                                                                                                                                                                                                                                                                                                         |

| PHY_REF        | А    | Reference Input This signal is used as the analog reference input for the PHY. It should be connected to a pull-down, 4.99 K $\Omega$ 1% resistor.                                                                                                                                                                                                                                                                                                                                                                                                |

| XTAL1          | 1    | Crystal One The Crystal One pin is a 25 MHz input signal. It should be connected to a parallel resonant crystal with a frequency tolerance of 30 ppm. The other end of the crystal should be connected to XTAL2.                                                                                                                                                                                                                                                                                                                                  |

| XTAL2          | 0    | Crystal Two Crystal Two is the output of an internal oscillator circuit used to drive a crystal into oscillation.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

## 2.7 Test Signals

### 2.7.1 MAC Test Signals

| Signal                                                         | Туре | Name and Function                                                                                                                                                                                                                                                                                                                       |  |

|----------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TEST_EN                                                        | 1    | factory Test Pin $\Lambda$ 1 K $\Omega$ pull-down resistor should be attached to ground from this pin for normal operation.                                                                                                                                                                                                             |  |