# HFC - S mini

# ISDN HDLC FIFO controller with S/T interface and integrated FIFOs

## **Revision History**

| Date           | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| July 2003      | The data sheet has completely been revised. Section "Processor interface modes" moved into section "Microprocessor interface", "List of registers" moved to the document preamble, information has been added to FIFO initialization, transformer list, processor interface timings, PCM data rate restrictions, electrical characteristics, clock synchronization, cascade-connected HFC-S mini with only one quartz circuitry and the following registers: INC_RES_F, RAM_DATA, FIFO, F_USAGE, F_FILL, FIF_DATA_NOINC, F_THRES, INT_S1, INT_M1, INT_M2, CON_HDLC, STATUS, MST_MODE0, MST_MODE1, MST_MODE2, ST_RD_STA, ST_WR_STA, CLKDEL. |

| September 2001 | Information added to: MST_MODE0 and CON_HDLC register description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| August 2001    | Chapters added: Timing diagrams for Motorala mode (mode2), sample circuitries.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| July 2001      | Information added to: Register description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| January 2001   | Information added to: Microprocessor access, PCM/GCI/IOM2 timing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Cologne Chip AG Eintrachtstrasse 113 D - 50668 Köln Germany

Tel.: +49 (0) 221 / 91 24-0 Fax: +49 (0) 221 / 91 24-100

http://www.CologneChip.com http://www.CologneChip.de support@CologneChip.com

Copyright 1994 - 2003 Cologne Chip AG All Rights Reserved

The information presented can not be considered as assured characteristics. Data can change without notice.

Parts of the information presented may be protected by patent or other rights.

Cologne Chip products are not designed, intended, or authorized for use in any application intended to support or sustain life, or for any other application in which the failure of the Cologne Chip product could create a situation where personal injury or death may occur.

# **Contents**

| 1 | Gen  | neral description                                         | 9  |  |  |  |  |  |  |

|---|------|-----------------------------------------------------------|----|--|--|--|--|--|--|

|   | 1.1  | Features                                                  | 9  |  |  |  |  |  |  |

|   | 1.2  | Block diagram                                             | 10 |  |  |  |  |  |  |

|   | 1.3  | Applications                                              | 10 |  |  |  |  |  |  |

| 2 | Pin  | description                                               | 11 |  |  |  |  |  |  |

| 3 | Fun  | nctional description                                      | 14 |  |  |  |  |  |  |

|   | 3.1  | Microprocessor interface                                  | 14 |  |  |  |  |  |  |

|   |      | 3.1.1 Processor interface modes                           | 14 |  |  |  |  |  |  |

|   |      | 3.1.2 Register access                                     | 14 |  |  |  |  |  |  |

|   | 3.2  | FIFOs                                                     | 15 |  |  |  |  |  |  |

|   |      | 3.2.1 FIFO channel operation                              | 17 |  |  |  |  |  |  |

|   |      | 3.2.1.1 Send channels (B1, B2, D and PCM transmit)        | 17 |  |  |  |  |  |  |

|   |      | 3.2.1.2 Automatically D-channel frame repetition          | 18 |  |  |  |  |  |  |

|   |      | 3.2.1.3 FIFO full condition in send channel               | 18 |  |  |  |  |  |  |

|   |      | 3.2.1.4 Receive Channels (B1, B2, D and PCM or E receive) | 18 |  |  |  |  |  |  |

|   |      | 3.2.1.5 FIFO full condition in receive channels           | 20 |  |  |  |  |  |  |

|   |      | 3.2.2 FIFO initialization                                 | 20 |  |  |  |  |  |  |

|   |      | 3.2.3 FIFO reset                                          | 20 |  |  |  |  |  |  |

|   | 3.3  | Transparent mode of HFC-S mini                            | 20 |  |  |  |  |  |  |

|   | 3.4  | Correspondency between FIFOs, CHANNELs and SLOTs          | 21 |  |  |  |  |  |  |

|   | 3.5  | Subchannel Processing                                     |    |  |  |  |  |  |  |

|   | 3.6  | PCM Interface Function                                    |    |  |  |  |  |  |  |

|   | 3.7  | Configuring test loops                                    | 28 |  |  |  |  |  |  |

| 4 | Reg  | gister description                                        | 29 |  |  |  |  |  |  |

|   | 4.1  | FIFO, interrupt, status and control registers             | 29 |  |  |  |  |  |  |

|   | 4.2  | PCM/GCI/IOM2 bus section registers                        | 44 |  |  |  |  |  |  |

|   |      | 4.2.1 Time slots for transmit direction                   | 44 |  |  |  |  |  |  |

|   |      | 4.2.2 Time slots for receive direction                    | 46 |  |  |  |  |  |  |

|   |      | 4.2.3 PCM data registers                                  | 48 |  |  |  |  |  |  |

|   |      | 4.2.4 Configuration and status registers                  | 50 |  |  |  |  |  |  |

|   | 4.3  | S/T section registers                                     | 54 |  |  |  |  |  |  |

|   |      | 4.3.1 S/T data registers                                  | 59 |  |  |  |  |  |  |

| 5 | Elec | ctrical characteristics                                   | 62 |  |  |  |  |  |  |

# **HFC-S** mini

| 6  | Timi                          | ng Characteristics                                                     | 66 |

|----|-------------------------------|------------------------------------------------------------------------|----|

|    | 6.1                           | Microprocessor access                                                  | 66 |

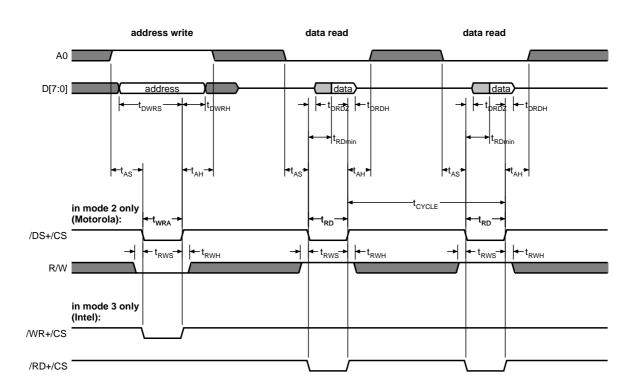

|    |                               | 6.1.1 Register read access in mode 2 (Motorola) and mode 3 (Intel)     | 66 |

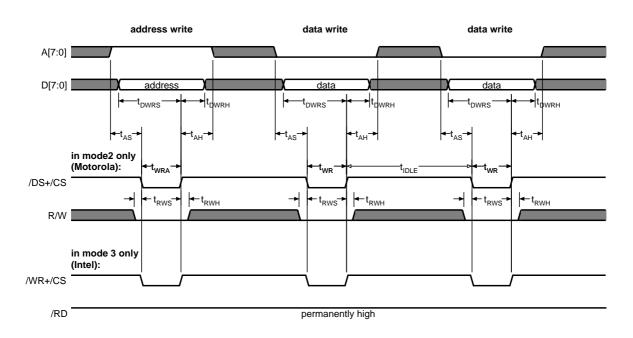

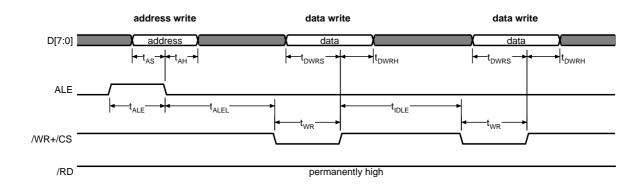

|    |                               | 6.1.2 Register write access in mode 2 (Motorola) and mode 3 (Intel)    | 68 |

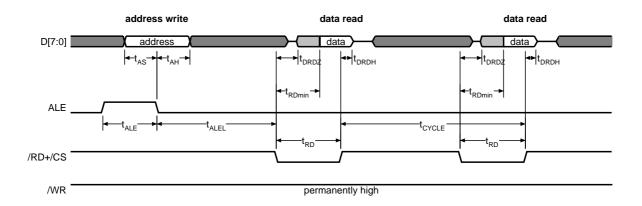

|    |                               | 6.1.3 Register read access in mode 4 (Intel, multiplexed)              | 70 |

|    |                               | 6.1.4 Register write access in mode 4 (Intel, multiplexed)             | 71 |

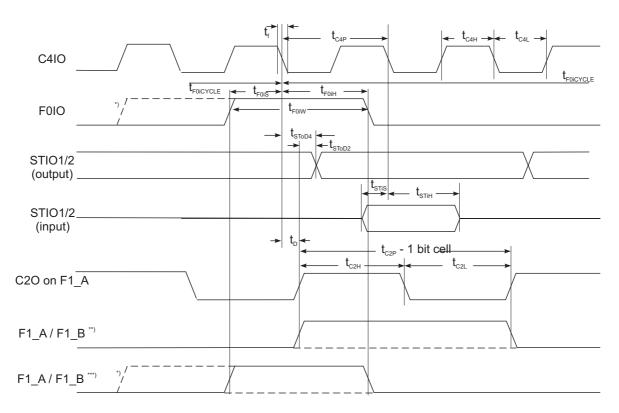

|    | 6.2                           | PCM/GCI/IOM2 timing                                                    | 72 |

|    |                               | 6.2.1 Master mode                                                      | 73 |

|    |                               | 6.2.2 Slave mode                                                       | 74 |

| 7  | Exte                          | rnal circuitries                                                       | 75 |

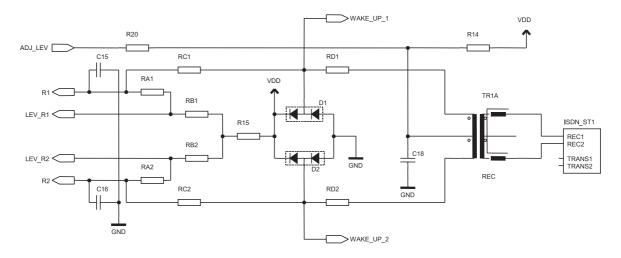

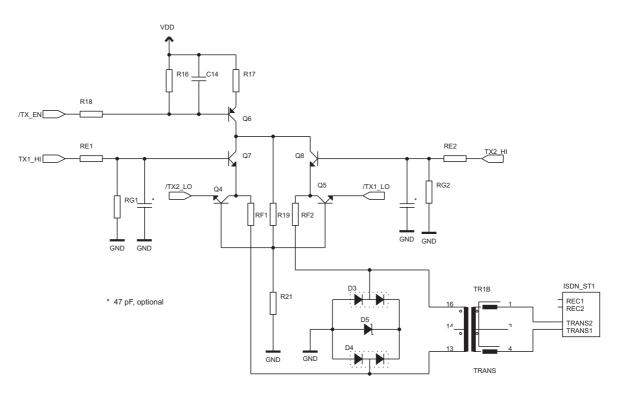

|    | 7.1                           | S/T interface circuitry                                                | 75 |

|    |                               | 7.1.1 External receiver circuitry                                      | 75 |

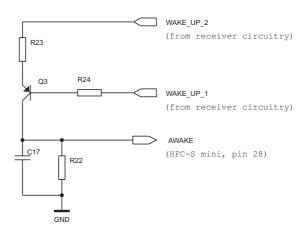

|    |                               | 7.1.2 External wake-up circuitry                                       | 76 |

|    |                               | 7.1.3 External transmitter circuitry                                   | 77 |

|    |                               | 7.1.4 S/T modules and transformers                                     | 78 |

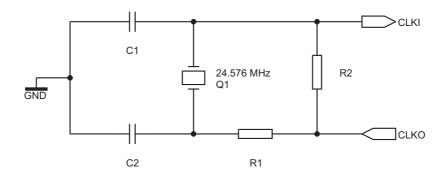

|    | 7.2                           | Oscillator circuitry for system clock                                  | 79 |

| 8  | State                         | e matrices for NT and TE                                               | 80 |

|    | 8.1                           | S/T interface activation / deactivation layer 1 state matrix for NT    | 80 |

|    | 8.2                           | S/T interface activation / deactivation layer 1 state matrix for TE    | 81 |

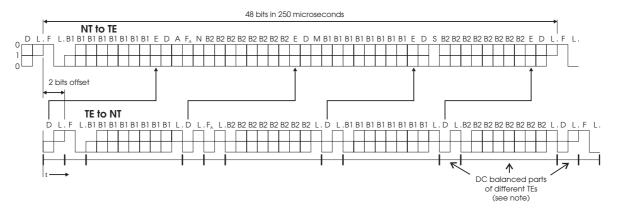

| 9  | ry organization of the frames | 82                                                                     |    |

|    | 9.1                           | S/T frame structure                                                    | 82 |

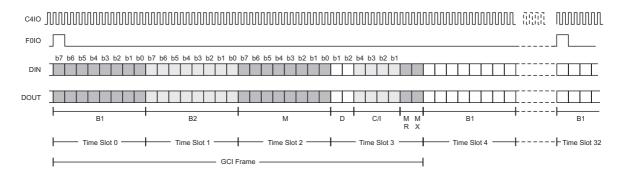

|    | 9.2                           | GCI frame structure                                                    | 83 |

| 10 | Cloc                          | k synchronization                                                      | 84 |

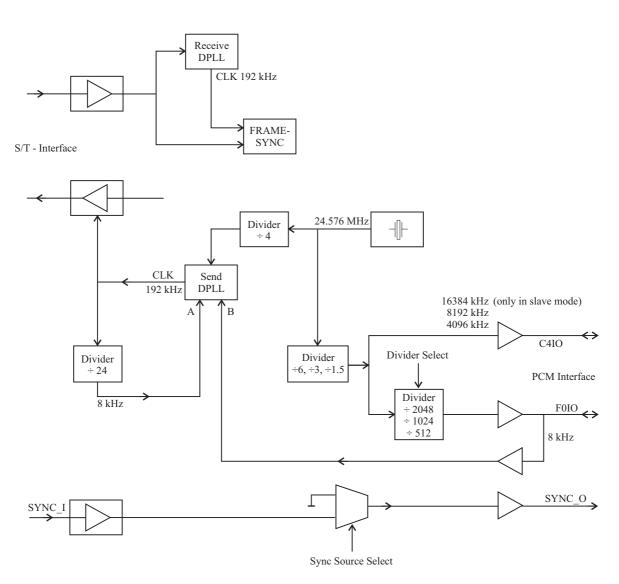

|    | 10.1                          | Clock synchronization in NT-mode                                       | 84 |

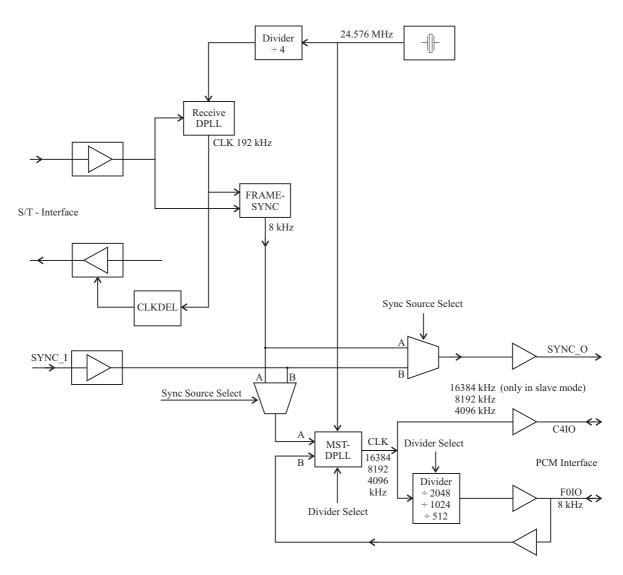

|    | 10.2                          | Clock synchronization in TE-mode                                       | 85 |

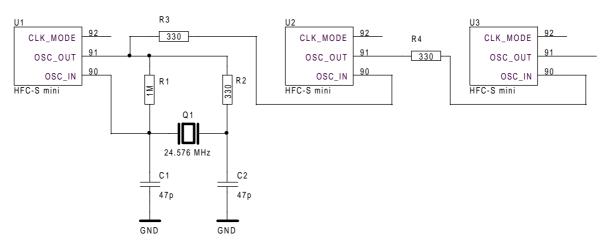

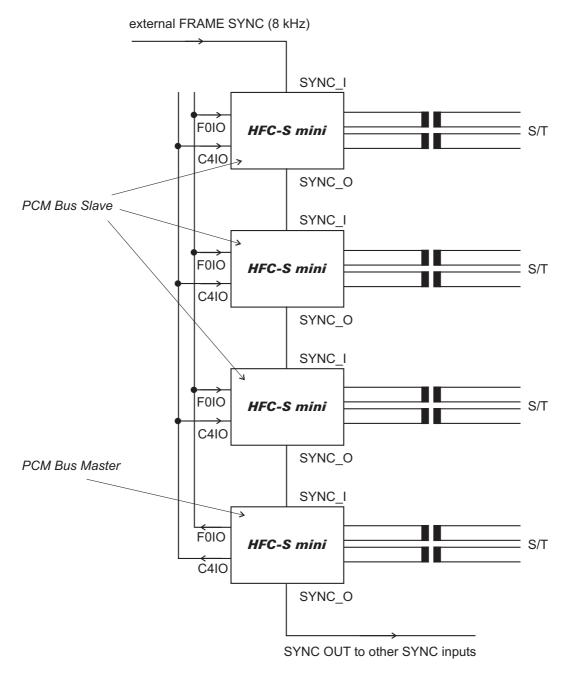

|    | 10.3                          | Multiple HFC-S mini synchronization scheme                             | 86 |

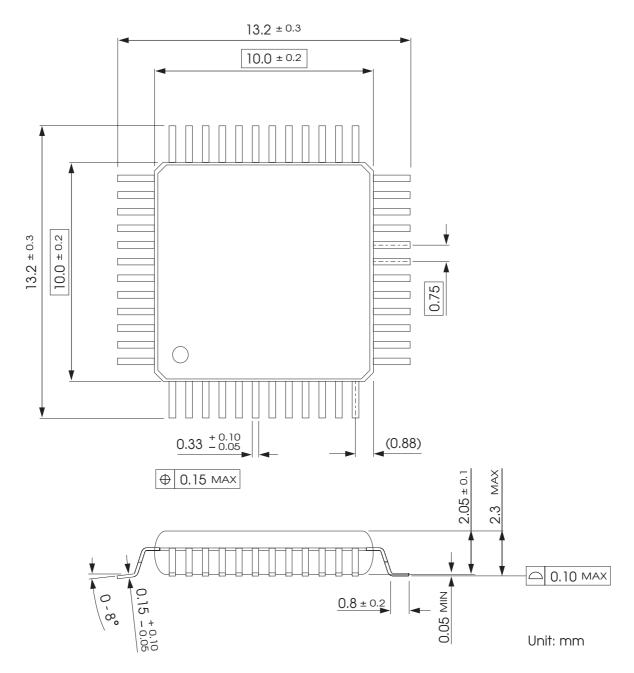

| 11 | HFC                           | C-S mini package dimensions                                            | 87 |

| 12 | Sam                           | ple circuitries                                                        | 88 |

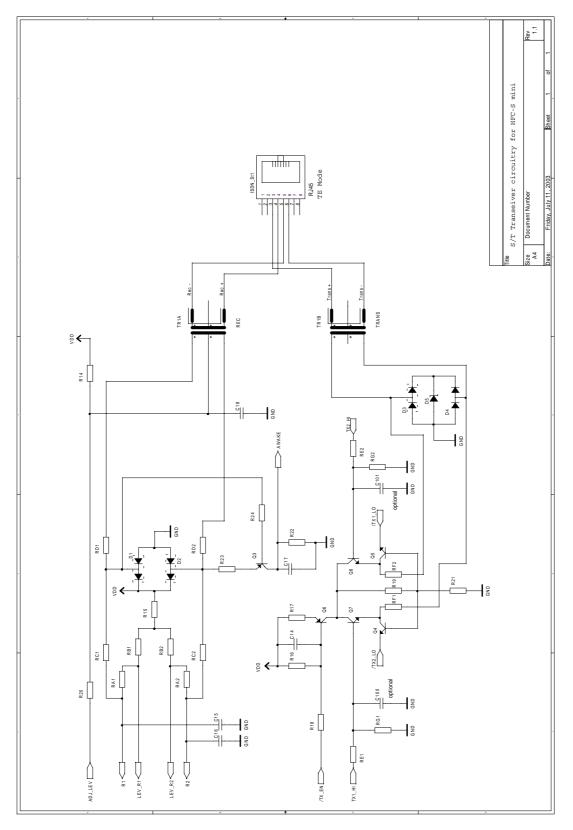

|    | 12.1                          | S/T interface circuitry (valid in all modes)                           | 88 |

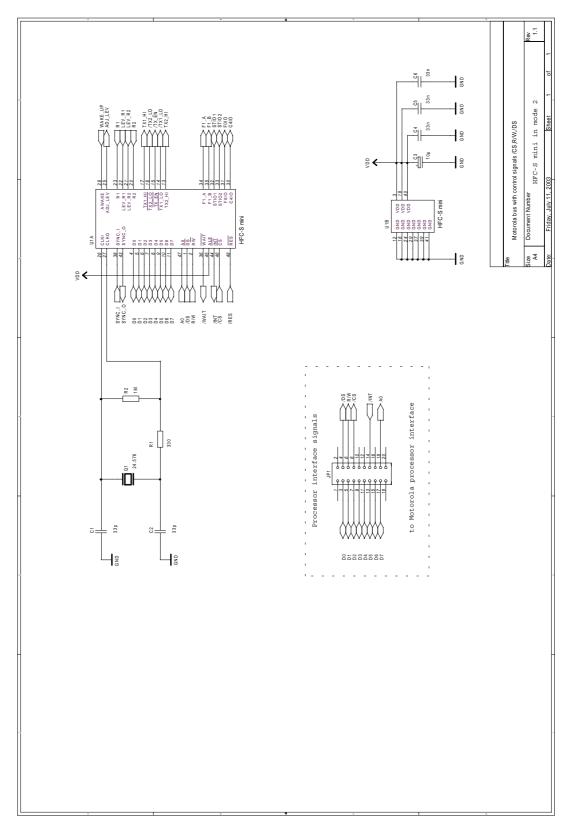

|    | 12.2                          | HFC-S mini in mode 2 (Motorola bus)                                    | 91 |

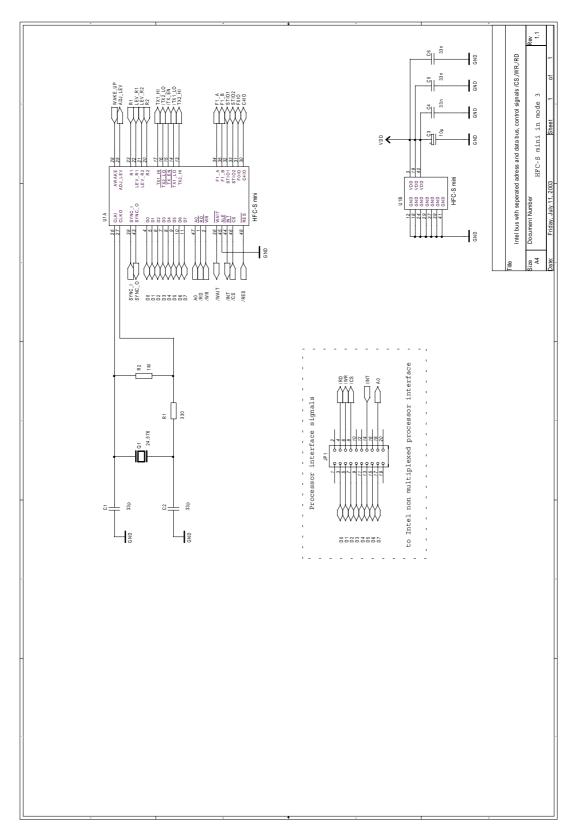

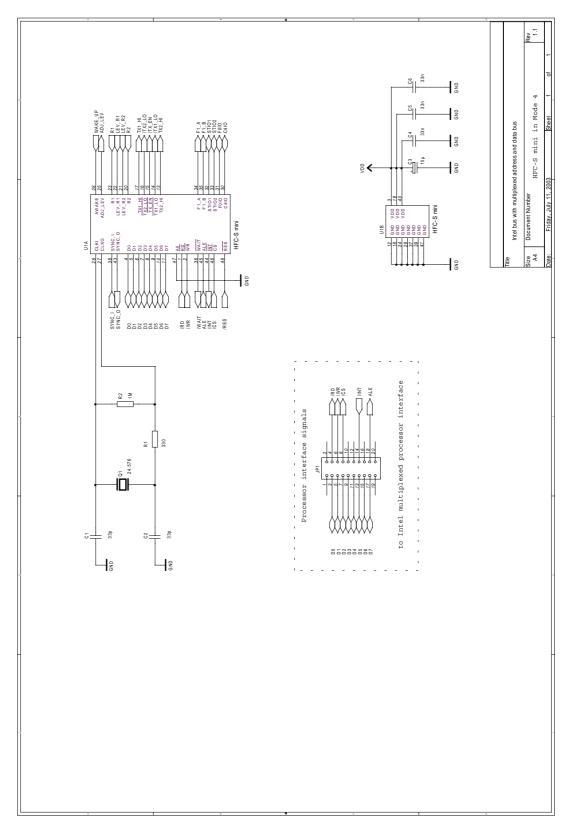

|    | 12.3                          | HFC-S mini in mode 3 (Intel bus with separate address bus/data bus)    | 92 |

|    | 12.4                          | HFC-S mini in mode 4 (Intel bus with multiplexed address bus/data bus) | 93 |

# **HFC-S** mini

# **List of Figures**

| 1  | HFC-S mini block diagram                                                               | 10 |

|----|----------------------------------------------------------------------------------------|----|

| 2  | Pin Connection                                                                         | 11 |

| 3  | FIFO Organization                                                                      | 17 |

| 4  | FIFO Data Organization                                                                 | 19 |

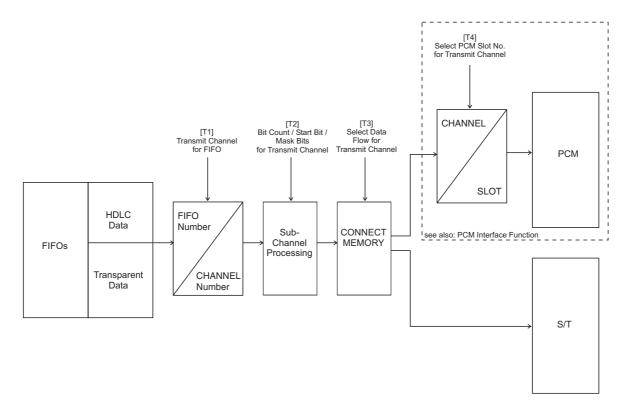

| 5  | FIFOs, CHANNELs and SLOTs in transmit Direction                                        | 24 |

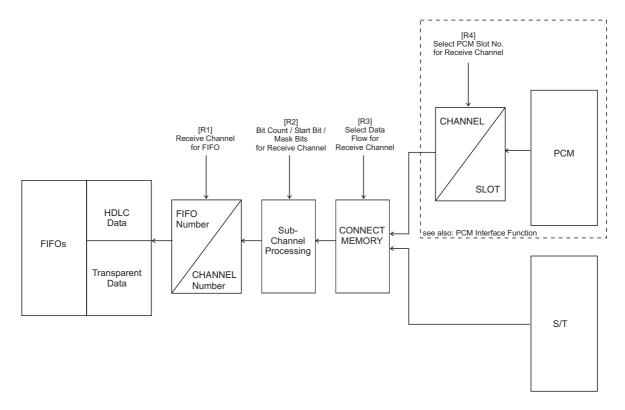

| 6  | FIFOs, CHANNELs and SLOTs in receive direction                                         | 25 |

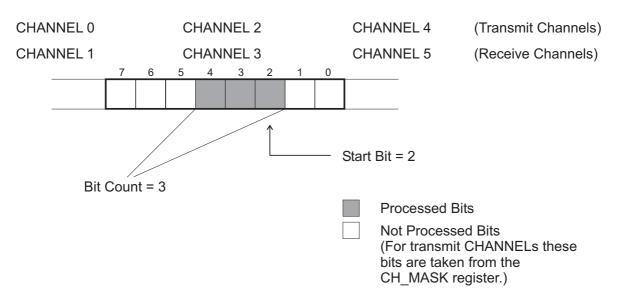

| 7  | Example for Subchannel Processing                                                      | 26 |

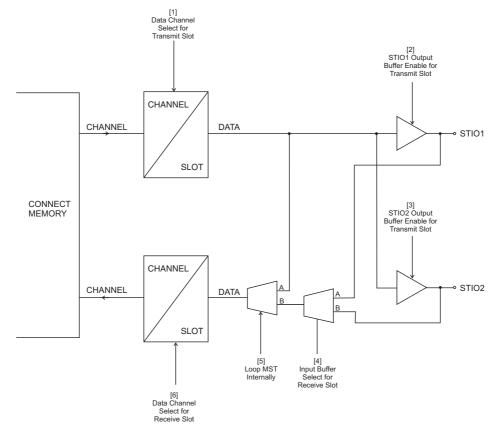

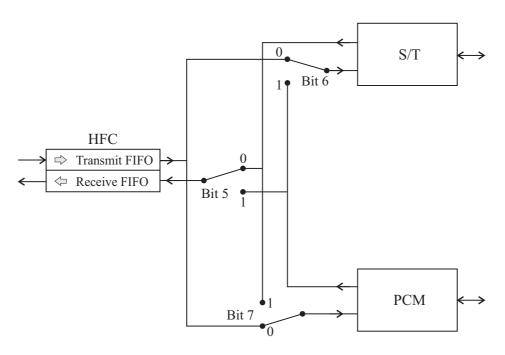

| 8  | PCM Interface Function Block Diagram                                                   | 27 |

| 9  | Function of CON_HDLC register bits 75                                                  | 41 |

| 10 | Read access in mode 2 (Motorola) and mode 3 (Intel)                                    | 66 |

| 11 | Write access in mode 2 (Motorola) and mode 3 (Intel)                                   | 68 |

| 12 | Read access in mode 4 (Intel, multiplexed)                                             | 70 |

| 13 | Write access in mode 4 (Intel, multiplexed)                                            | 71 |

| 14 | PCM/GCI/IOM2 timing                                                                    | 72 |

| 15 | External receiver circuitry                                                            | 75 |

| 16 | External wake-up circuitry                                                             | 76 |

| 17 | External transmitter circuitry                                                         | 77 |

| 18 | Oscillator circuitry for S/T clock                                                     | 79 |

| 19 | Cascade-connected HFC-S mini with only one quartz circuitry                            | 79 |

| 20 | Frame structure at reference point S and T $\dots \dots \dots \dots \dots \dots \dots$ | 82 |

| 21 | Single channel GCI format                                                              | 83 |

| 22 | Clock synchronization in NT-mode                                                       | 84 |

| 23 | Clock synchronization in TE-mode                                                       | 85 |

| 24 | Multiple HFC-S mini synchronization scheme                                             | 86 |

| 25 | HFC-S mini package dimensions                                                          | 87 |

| 26 | HFC-S mini sample circuitry                                                            | 88 |

| 27 | HFC-S mini sample circuitry in processor mode 2 (Motorola)                             | 91 |

| 28 | HFC-S mini sample circuitry in processor mode 3 (Intel), 1st part                      | 92 |

| 29 | HFC-S mini sample circuitry in processor mode 4 (Intel, multiplexed), 1st part         | 93 |

# **HFC-S** mini

# **List of Tables**

| 2  | Function of the microprocessor interface control signals         | 15 |

|----|------------------------------------------------------------------|----|

| 3  | Possible connections of FIFO and CHANNELs in Simple Mode (SM)    | 22 |

| 4  | CHANNEL numbers on the S/T interface and PCM interface           | 22 |

| 5  | FIFO to S/T channel assignment                                   | 26 |

| 6  | PCM interface control options                                    | 27 |

| 7  | I/O characteristics                                              | 65 |

| 8  | Driver Capability                                                | 65 |

| 9  | Symbols of read accesses in Figure 10                            | 67 |

| 10 | Symbols of write accesses in Figure 11                           | 68 |

| 11 | Symbols of read accesses in Figure 12                            | 70 |

| 12 | Symbols of write accesses in Figure 13                           | 71 |

| 13 | PCM timing values in master mode                                 | 73 |

| 14 | PCM timing values in slave mode                                  | 74 |

| 15 | Activation / deactivation layer 1 for finite state matrix for NT | 80 |

| 16 | Activation / deactivation layer 1 for finite state matrix for TE | 81 |

# List of Registers sorted by name

# Please note!

Register addresses are assigned independently for write and read access; i.e. in some cases there are different registers for write and read access with the same address. Only registers with the same meaning and bitmap structure in both write and read directions are declared to be read / write.

## Write only registers:

## Read only registers:

|         |           |      | Address      | Name           | Page |

|---------|-----------|------|--------------|----------------|------|

| Address | Name      | Page | 0x3C         | B1_REC         | 59   |

|         |           |      | 0x3D         | B2_REC         | 60   |

| 0x26    | AUX1_RSL  | 47   | 0x16         | CHIP_ID        | 42   |

| 0x22    | AUX1_SSL  | 45   | 0x3E         | D_REC          | 60   |

| 0x27    | AUX2_RSL  | 47   | 0x3F         | E_REC          | 61   |

| 0x23    | AUX2_SSL  | 45   | 0x1B         | F_FILL         | 35   |

| 0x24    | B1_RSL    | 46   | 0x1A         | F_USAGE        | 32   |

| 0x3C    | B1_SEND   | 60   | 0x19         | F0_CNT_H       | 53   |

| 0x20    | B1_SSL    | 44   | 0x18         | F0_CNT_L       | 52   |

| 0x25    | B2_RSL    | 46   | 0x0C         | FIF_F1         | 32   |

| 0x3D    | B2_SEND   | 60   | 0x0D         | FIF_F2         | 33   |

| 0x21    | B2_SSL    | 44   | 0x04         | FIF_Z1         | 33   |

| 0xF4    | CH_MASK   | 41   | 0x06         | FIF_Z2         | 33   |

| 0xFC    | CHANNEL   | 42   | 0x10         | INT_S1         | 36   |

| 0x00    | CIRM      | 29   | 0x11         | INT_S2         | 37   |

| 0x37    | CLKDEL    | 59   | 0x34         | SQ_REC         | 58   |

| 0xFA    | CON_HDLC  | 40   | 0x30         | ST_RD_STA      | 54   |

| 0x3E    | D_SEND    | 61   | 0x1C         | STATUS         | 43   |

| 0x0B    | F_CROSS   | 29   | 0x29         | TRxR           | 53   |

| 0x0D    | F_MODE    | 30   |              |                |      |

| 0x0C    | F_THRES   | 34   |              |                |      |

| 0x0F    | FIFO      | 31   |              |                |      |

| 0xFB    | HDLC_PAR  | 39   |              |                |      |

| 0x0E    | INC_RES_F | 30   | Read/Write r | egisters:      |      |

| 0x1A    | INT_M1    | 38   |              |                |      |

| 0x1B    | INT_M2    | 38   | Address      | Name           | Page |

| 0x14    | MST_MODE0 | 50   | Address      | Ivaille        | rage |

| 0x15    | MST_MODE1 | 51   | 0x2E         | AUX1_D         | 48   |

| 0x16    | MST_MODE2 | 52   | 0x2F         | AUX2_D         | 49   |

| 0x09    | RAM_ADR_H | 31   | 0x2C         | B1_D           | 48   |

| 80x0    | RAM_ADR_L | 30   | 0x2D         | B2_D           | 48   |

| 0x32    | SCTRL_E   | 57   | 0x28         | C/I            | 53   |

| 0x33    | SCTRL_R   | 57   | 0x84         | FIF_DATA_NOINC | 32   |

| 0x31    | SCTRL     | 56   | 0x80         | FIF_DATA       | 32   |

| 0x34    | SQ_SEND   | 58   | 0x2A         | MON1_D         | 54   |

| 0x30    | ST_WR_STA | 55   | 0x2B         | MON2_D         | 54   |

| 0x1C    | TIME_SEL  | 43   | 0xC0         | RAM_DATA       | 31   |

# List of Registers sorted by address

# Please note!

Register addresses are assigned independently for write and read access; i.e. in some cases there are different registers for write and read access with the same address. Only registers with the same meaning and bitmap structure in both write and read directions are declared to be read / write.

## Write only registers:

## Read only registers:

|         |           |      | Address      | Name           | Page |

|---------|-----------|------|--------------|----------------|------|

| Address | Name      | Page | 0x04         | FIF_Z1         | 33   |

|         | OUD.      |      | 0x06         | FIF_Z2         | 33   |

| 0x00    | CIRM      | 29   | 0x0C         | FIF_F1         | 32   |

| 0x08    | RAM_ADR_L | 30   | 0x0D         | FIF_F2         | 33   |

| 0x09    | RAM_ADR_H | 31   | 0x10         | INT_S1         | 36   |

| 0x0B    | F_CROSS   | 29   | 0x11         | INT_S2         | 37   |

| 0x0C    | F_THRES   | 34   | 0x16         | CHIP_ID        | 42   |

| 0x0D    | F_MODE    | 30   | 0x18         | F0_CNT_L       | 52   |

| 0x0E    | INC_RES_F | 30   | 0x19         | F0_CNT_H       | 53   |

| 0x0F    | FIFO      | 31   | 0x1A         | F_USAGE        | 32   |

| 0x14    | MST_MODE0 | 50   | 0x1B         | F_FILL         | 35   |

| 0x15    | MST_MODE1 | 51   | 0x1C         | STATUS         | 43   |

| 0x16    | MST_MODE2 | 52   | 0x29         | TRxR           | 53   |

| 0x1A    | INT_M1    | 38   | 0x30         | ST_RD_STA      | 54   |

| 0x1B    | INT_M2    | 38   | 0x34         | SQ_REC         | 58   |

| 0x1C    | TIME_SEL  | 43   | 0x3C         | B1_REC         | 59   |

| 0x20    | B1_SSL    | 44   | 0x3D         | B2_REC         | 60   |

| 0x21    | B2_SSL    | 44   | 0x3E         | _<br>D_REC     | 60   |

| 0x22    | AUX1_SSL  | 45   | 0x3F         | E_REC          | 61   |

| 0x23    | AUX2_SSL  | 45   |              | _              |      |

| 0x24    | B1_RSL    | 46   |              |                |      |

| 0x25    | B2_RSL    | 46   |              |                |      |

| 0x26    | AUX1_RSL  | 47   |              |                |      |

| 0x27    | AUX2_RSL  | 47   | Read/Write r | registers:     |      |

| 0x30    | ST_WR_STA | 55   |              |                |      |

| 0x31    | SCTRL     | 56   | Address      | Name           | Dogo |

| 0x32    | SCTRL_E   | 57   | Address      | Name           | Page |

| 0x33    | SCTRL_R   | 57   | 0x28         | C/I            | 53   |

| 0x34    | SQ_SEND   | 58   | 0x2A         | MON1_D         | 54   |

| 0x37    | CLKDEL    | 59   | 0x2B         | MON2_D         | 54   |

| 0x3C    | B1_SEND   | 60   | 0x2C         | B1_D           | 48   |

| 0x3D    | B2_SEND   | 60   | 0x2D         | B2_D           | 48   |

| 0x3E    | D_SEND    | 61   | 0x2E         | AUX1_D         | 48   |

| 0xF4    | CH_MASK   | 41   | 0x2F         | AUX2_D         | 49   |

| 0xFA    | CON_HDLC  | 40   | 0x80         | FIF_DATA       | 32   |

| 0xFB    | HDLC_PAR  | 39   | 0x84         | FIF_DATA_NOINC | 32   |

| 0xFC    | CHANNEL   | 42   | 0xC0         | RAM_DATA       | 31   |

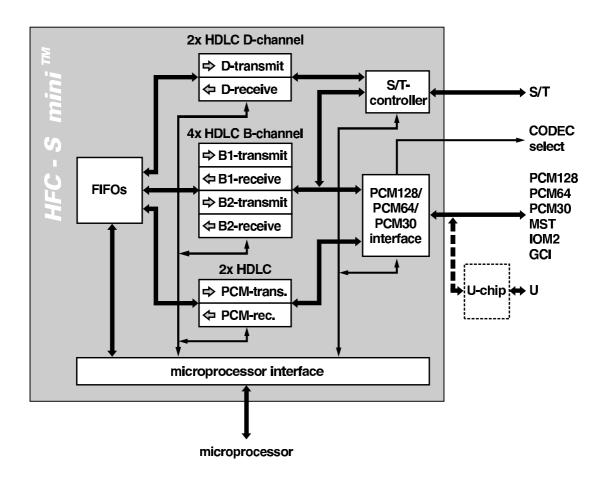

# 1 General description

The HFC-S mini is a single-chip ISDN S/T HDLC basic rate controller for embedded applications. The S/T interface, HDLC controllers, FIFOs and a microprocessor interface are integrated in the HFC-S mini. A PCM128/PCM64/PCM30 interface is also implemented which can be connected to many telecom serial busses. CODECs are usually connected to this interface. All ISDN channels (2 B + 1 D) and the PCM interface are served fully duplex by the 8 integrated FIFOs. HDLC controllers are implemented in hardware so there is no need to implement HDLC on the host processor.

#### 1.1 Features

- single chip ISDN S/T controller with B- and D-channel HDLC support

- integrated S/T interface

- full I.430 ITU S/T ISDN support in TE and NT mode for 3.3 V and 5 V power supply

- independent read and write HDLC channels for two ISDN B-channels, one ISDN D-channel and one additional PCM time slot (or E-channel)

- B1- and B2-channel transparent mode independently selectable

- integrated FIFOs for B1-channel, B2-channel, D-channel and an additional PCM (or E-channel) channel

- FIFO size: 128 bytes per channel and direction; up to 7 HDLC frames per FIFO

- 56 kbit/s restricted mode for U.S. ISDN lines selectable by software

- PCM128/PCM64/PCM30 interface configurable to interface MITEL ST<sup>TM</sup> bus (MVIP<sup>TM</sup>), Siemens IOM2<sup>TM</sup> or GCI<sup>TM</sup> for interface to U-chip or external CODECs

- H.100 data rate supported

- microprocessor interface compatible to Motorola bus and Intel bus

- Timer with interrupt capability

- CMOS technology, 3 V . . 5 V

- PQFP 48 package

## 1.2 Block diagram

Figure 1: HFC-S mini block diagram

## 1.3 Applications

The HFC-S mini can be used for all kinds of ISDN equipment with ISDN basic rate S/T interface.

- ISDN terminal adapters (for internet access)

- ISDN terminal adapters (with POTS interfaces)

- ISDN PABX

- ISDN SoHo PABX (switching done by HFC-S mini)

- ISDN telephones

- ISDN video conferencing equipment

- ISDN dialers and LCR (Least Cost Routers)

- ISDN LAN routers

- ISDN protocol analyzers

- ISDN smart NTs

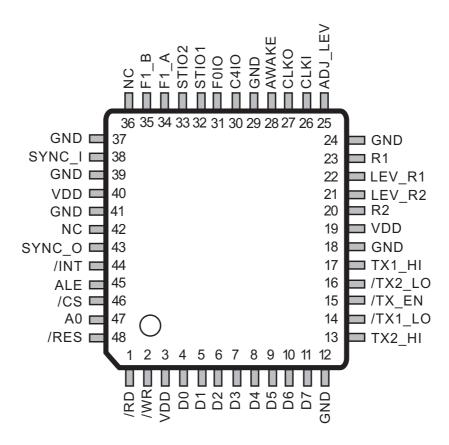

# 2 Pin description

Figure 2: Pin Connection

| Pin | Interface    | Name | I/O | Description                                       |

|-----|--------------|------|-----|---------------------------------------------------|

| 1   | 1st function | /RD  | I   | Read signal from external processor (low active)  |

|     | 2nd function | /DS  | I   | I/O data strobe                                   |

| 2   | 1st function | /WR  | I   | Write signal from external processor (low active) |

|     | 2nd function | R/W  | I   | Read/Write select (WR = '0')                      |

| 3   |              | VDD  |     | VDD (3.3V or 5V)                                  |

| 4   |              | D0   | IOr | Data bus (bit 0)                                  |

| 5   |              | D1   | IOr | Data bus (bit 1)                                  |

| 6   |              | D2   | IOr | Data bus (bit 2)                                  |

| 7   |              | D3   | IOr | Data bus (bit 3)                                  |

| 8   |              | D4   | IOr | Data bus (bit 4)                                  |

| 9   |              | D5   | IOr | Data bus (bit 5)                                  |

| 10  | <u> </u>     | D6   | IOr | Data bus (bit 6)                                  |

| 11  |              | D7   | IOr | Data bus (bit 7)                                  |

|     |              |      |     |                                                   |

(continued on next page)

(continued from previous page)

| Pin | Interface | Name    | I/O  | <b>Description</b>                                                                                                       |

|-----|-----------|---------|------|--------------------------------------------------------------------------------------------------------------------------|

| 12  |           | GND     |      | GND                                                                                                                      |

| 13  |           | TX2_HI  | О    | Transmit output 2                                                                                                        |

| 14  |           | /TX1_LO | О    | GND driver for transmitter 1                                                                                             |

| 15  |           | /TX_EN  | О    | Transmit enable                                                                                                          |

| 16  |           | /TX2_LO | О    | GND driver for transmitter 2                                                                                             |

| 17  |           | TX1_HI  | О    | Transmit output 1                                                                                                        |

| 18  |           | GND     |      | GND                                                                                                                      |

| 19  |           | VDD     |      | VDD (3.3V or 5V)                                                                                                         |

| 20  |           | R2      | I    | Receive data 2                                                                                                           |

| 21  |           | LEV_R2  | Ι    | Level detect for R2                                                                                                      |

| 22  |           | LEV_R1  | I    | Level detect for R1                                                                                                      |

| 23  |           | R1      | I    | Receive data 1                                                                                                           |

| 24  |           | GND     |      | GND                                                                                                                      |

| 25  |           | ADJ_LEV | О    | Level generator                                                                                                          |

| 26  |           | CLKI    | I    | 24.576 MHz clock input or 24.576 MHz crystal                                                                             |

| 27  |           | CLKO    | О    | 24.576 MHz clock output or 24.576 MHz crystal                                                                            |

| 28  |           | AWAKE   | I    | Awake input pin for external awake circuitry                                                                             |

| 29  |           | GND     |      | GND                                                                                                                      |

| 30  |           | C4IO    | IOpu | Double bit clock 4.096 MHz / 8.192 MHz / 16.384 MHz                                                                      |

| 31  |           | F0IO    | IOpu | Frame synchronization, 8 kHz pulse for PCM/GCI/IOM2 bus frame synchronization                                            |

| 32  |           | STIO1   | IOpu | PCM/GCI/IOM2 bus data line 1                                                                                             |

| 33  |           | STIO2   | IOpu | PCM/GCI/IOM2 bus data line 2                                                                                             |

| 34  |           | F1_A    | О    | Enable signal for external CODEC A or C2IO clock (bit clock), programmable as positive (reset default) or negative pulse |

| 35  |           | F1_B    | О    | Enable signal for external CODEC B, programmable as positive (reset default) or negative pulse                           |

| 36  |           | NC      |      | Must not be connected                                                                                                    |

| 38  |           | SYNC_I  | I    | 8 kHz synchronization input                                                                                              |

| 39  |           | GND     |      | GND                                                                                                                      |

| 40  |           | VDD     |      | VDD (3.3V or 5V)                                                                                                         |

| 41  |           | GND     |      | GND                                                                                                                      |

|     |           |         |      | (continued on next page)                                                                                                 |

(continued on next page)

(continued from previous page)

| Pin | Interface | Name   | I/O   | Description                                                           |

|-----|-----------|--------|-------|-----------------------------------------------------------------------|

| 42  |           | NC     |       | Must not be connected                                                 |

| 43  |           | SYNC_O | O     | 8 kHz synchronization output                                          |

| 44  |           | /INT   | Ood   | Interrupt request for external processor (low active)                 |

| 45  |           | ALE    | Ipu   | Address latch enable ALE is also used for mode selection during reset |

| 46  |           | /CS    | Ipu   | Chip select (low active)                                              |

| 47  |           | A0     | I     | Address bit 0 from external processor                                 |

| 48  |           | /RES   | Istpu | Reset (low active)                                                    |

| Legend: | I     | Input pin                                                                                                        |

|---------|-------|------------------------------------------------------------------------------------------------------------------|

|         | O     | Output pin                                                                                                       |

|         | IO    | Bidirectional pin                                                                                                |

|         | Ipu   | Input pin with internal pull-up resistor of app. $100\mathrm{k}\Omega$ to VDD                                    |

|         | IOpu  | Bidirectional pin with internal pull-up resistor of app. $100  k\Omega$ to VDD                                   |

|         | Istpu | Input pin with Schmitt trigger characteristic and internal pull-up resistor of app. $100\mathrm{k}\Omega$ to VDD |

|         | IOr   | Tristated during reset                                                                                           |

|         | Ood   | Output pin with open drain                                                                                       |

|         | NC    | Not connected                                                                                                    |

Unused input pins should be connected to ground.

# 3 Functional description

#### 3.1 Microprocessor interface

The HFC-S mini has an integrated 8 bit microprocessor interface. It is compatible with Motorola bus and Intel bus. The different microprocessor interface modes are selected during reset by ALE.

In mode 2 (Motorola bus mode) and mode 3 (de-multiplexed Intel bus mode) pin A0 is the address input. The data bus is D7..D0.

In mode 4 (multiplexed Intel bus mode) D[7:0] is the multiplexed address/data bus. A0 must be '0' in this mode.

#### 3.1.1 Processor interface modes

**Mode 2:** Motorola bus with control signals /CS, R/W, /DS is selected by setting ALE to VDD.

**Mode 3:** Intel bus with seperated address bus (A0) and data bus (D7..D0) and control signals /CS, /WR, /RD is selected by setting ALE to GND.

**Mode 4:** Intel bus with multiplexed address bus and data bus with control signals /CS, /WR, /RD, ALE. The first rising edge on ALE switches into this mode. A0 must be '0'. ALE latches the address. The multiplexed address / data bus is D7..D0.

In mode 4 all internal registers can be directly accessed. In mode 2 and mode 3 first the address of the desired register must be written to the address with A0 = '1'. Afterwards data can be read/written from/to that register by reading/writing the address with A0 = '0'. In mode 4 A0 must always be '0'.

#### 3.1.2 Register access

In mode 2 and mode 3 the HFC-S mini has 2 addresses. The lower address (A0 = '0') is used for data read/write. The higher address (A0 = '1') is write only and is used for register selection. Registers are selected by first setting A0 to '1' and then writing the address of the desired register to the data bus D7..D0. All following accesses to the HFC-S mini with A0 = '0' are read/write operations concerning this register.

In mode 4 all registers can be directly accessed by their address. The function of the control signals is shown in Table 2. Except in mode 4, ALE is assumed to be stable after reset.

| <b>Table 2:</b> Function of the microprocessor interface control signals $(X = d)$ | : don't care) |

|------------------------------------------------------------------------------------|---------------|

|------------------------------------------------------------------------------------|---------------|

| /RD<br>/DS | /WR<br>R/W | /CS | ALE | Operation      | Mode |

|------------|------------|-----|-----|----------------|------|

| X          | X          | 1   | X   | no data access | all  |

| 1          | 1          | X   | X   | no data access | all  |

| 0          | 1          | 0   | 1   | read data      | 2    |

| 0          | 0          | 0   | 1   | write data     | 2    |

| 0          | 1          | 0   | 0   | read data      | 3    |

| 1          | 0          | 0   | 0   | write data     | 3    |

| 0          | 1          | 0   | 0 * | read data      | 4    |

| 1          | 0          | 0   | 0 * | write data     | 4    |

(\*: 1-pulse latches register address)

#### Please note!

Every asynchronous register read access should be done multiple times until two consecutive read accesses result in the same value. Only this way it is ensured that the read bits are stable.

This information applies to the following registers:

| F_USAGE (0x1A),        | RAM_DATA (0xC0), | FIF_DATA (0x80), |

|------------------------|------------------|------------------|

| FIF_DATA_NOINC (0x84), | FIF_F1 (0x0C),   | FIF_F2 (0x0D),   |

| FIF_Z1 (0x04),         | FIF_Z2 (0x06),   | B1_D (0x2C),     |

| B2_D (0x2D),           | AUX1_D (0x2E),   | AUX2_D (0x2F),   |

| F0_CNT_L (0x18),       | F0_CNT_H (0x19), | C/I (0x28),      |

| MON1_D (0x2A),         | MON2_D (0x2B),   | SQ_REC (0x34).   |

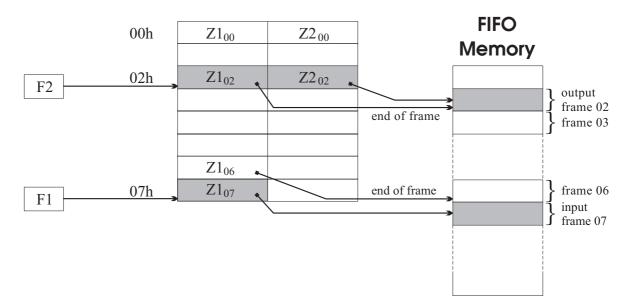

#### 3.2 FIFOs

There is a transmit and a receive FIFO with HDLC controller for each of the two B-channels, for the D-channel and for the PCM interface in the HFC-S mini. As an alternative the PCM receive controller can be used for the E-channel. Every FIFO has a length of 128 bytes in each direction. Up to 7 frames can be stored in every FIFO.

The HDLC circuits are located on the S/T device side of the HFC-S mini. So always plain data is stored in the FIFOs. Zero insertion and CRC checksum processing for receive and transmit data is done by the HFC-S mini automatically.

A FIFO can be selected for access by writing its number in the FIFO select register FIFO.

The FIFOs are ring buffers. To control them there are some counters. Z1 is the FIFO input counter and Z2 is the FIFO output counter.

Each counter points to a byte position in the SRAM. On a FIFO input operation Z1 is incremented. On an output operation Z2 is incremented.

After every pulse of the F0IO signal two HDLC bytes for the B1- and the B2-channel are written into the S/T interface (FIFOs with even numbers) and two HDLC-bytes are read from the S/T interface (FIFOs with odd numbers).

D-channel data is handled in a similar way but only 2 bits are processed.

# **Important!**

Instead of the S/T interface the PCM bus is also selectable for each B-channel (see CON\_HDLC register).

If Z1 = Z2 the FIFO is empty.

Additionally there are two counters F1 and F2 for every FIFO channel (3 bits for each channel). They count the HDLC frames in the FIFOs and form a ring buffer as Z1 and Z2 do, too.

F1 is incremented when a complete frame has been received and stored in the FIFO. F2 is incremented when a complete frame has been read from the FIFO.

If F1 = F2 there is no complete frame in the FIFO.

When the /RES line is active or software reset is active Z1, Z2, F1 and F2 are all initialized to all '1's (so Z-counters are initialized to 0x7F and F-counters are initialized to 0x07).

The access to a FIFO is selected by writing the FIFO number into the FIFO select register FIFO.

#### **Important!**

#### **FIFO** change, **FIFO** reset and F1/F2 incrementation:

Changing the FIFO, reseting the FIFO or incrementing the frame counters causes a short BUSY period of the HFC-S mini. This means an access to FIFO control registers and data registers is *not* allowed until BUSY status is reset (bit 0 of STATUS register). This has a maximum duration of 25 clock cycles ( $2\mu$ s).

Status, interrupt and control registers can be read or written at any time.

#### **Important!**

The counter state 0x00 of the *Z*-counters follows counter state 0x7F in all FIFOs. The counter state 0x00 of the *F*-counters follows counter state 0x07 in all FIFOs.

#### 3.2.1 FIFO channel operation

#### 3.2.1.1 Send channels (B1, B2, D and PCM transmit)

The send channels send data from the host bus interface to the FIFO and the HFC-S mini converts the data into HDLC code and transfers it from the FIFO into the S/T or/and the PCM bus interface write registers.

The HFC-S mini checks Z1 and Z2. If Z1 = Z2 (FIFO empty) the HFC-S mini generates a HDLC flag '0111 1110' or idle pattern '1111 1111' and sends it to the S/T device. In this case Z2 is not incremented. If also F1 = F2 only HDLC flags are sent to the S/T interface and all counters remain unchanged. If the frame counters are unequal F2 is incremented and the HFC-S mini tries to send the next frame to the output device. After the end of a frame (Z2 reaches Z1) it automatically generates the 16 bit CRC checksum and adds the ending flag. If there is another frame in the FIFO ( $F1 \neq F2$ ) the F2 counter is incremented.

With every byte being sent from the host bus side to the FIFO, Z1 is incremented automatically. If a complete frame has been sent, F1 must be incremented to send the next frame. If the frame counter F1 is incremented, also the Z-counters may change because Z1 and Z2 are functions of F1 and F2. So there are Z1(F1), Z2(F1), Z1(F2) and Z2(F2) (see Figure 3).

Figure 3: FIFO Organization

Z1(F1) is used for the frame which is just written from the microprocessor bus side. Z2(F2) is used for the frame which is just beeing transmitted to the S/T device side of the HFC-S mini. Z1(F2) is the end of frame pointer of the current output frame.

In the send channels F1 is only changed from the microprocessor interface side if the software driver wants to say "end of send frame". If bit 0 in INC\_RES\_F register is set, the current value of Z1 is stored, F1 is incremented and Z1 is used as start address of the next frame automatically. Z1(F2) and Z2(F2) can not be accessed.

#### **Important!**

The HFC-S mini begins to transmit the bytes from a FIFO at the moment the FIFO is changed or the F1 counter is incremented. Also changing to the FIFO that is already selected starts the transmission. So by selecting the same FIFO again transmission can be started. This is required if a HDLC frame is longer than 128 bytes.

#### 3.2.1.2 Automatically D-channel frame repetition

The D-channel send FIFO has a special feature. If the S/T interface signals a D-channel contention before the CRC is sent, the Z2 counter is set to the starting address of the current frame and the HFC-S mini tries to repeat the frame automatically.

#### 3.2.1.3 FIFO full condition in send channel

There are two different FIFO full conditions. The first one is met when the FIFO contents comes up to 7 frames. There is no possibility for the HFC-S mini to manage more HDLC frames even if the frames are very small. The driver software must check that there are never more than 7 HDLC frames in a FIFO.

The second limitation is the size of the FIFO (128 bytes each). FIFO full condition can be checked by reading the F\_USAGE register. It shows the actually occupied FIFO space in bytes.

Furthermore a threshold value can be set for all transmit and receive FIFOs in the F\_THRES register. Then the F\_FILL register shows an indication of the filling level for each FIFO. After data processing from or to a FIFO, the F\_FILL register must be updated with a change FIFO or an increment FIFO counter operation. After this it takes up to  $250\,\mu\rm s$  until the bit value in the F\_FILL register of the processed FIFO represents the actual state of the FIFO filling level.

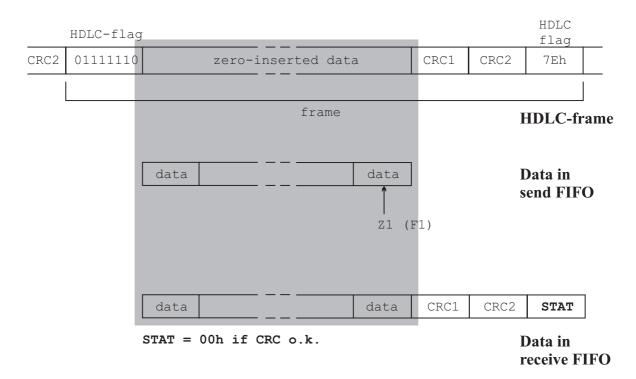

#### 3.2.1.4 Receive Channels (B1, B2, D and PCM or E receive)

The receive channels receive data from the S/T or PCM bus interface read registers. The data is converted from HDLC into plain data and sent to the FIFO. Then the data can be read via the microprocessor bus interface.

The HFC-S mini checks the HDLC data coming in. If it finds a flag or more than 5 consecutive '1's it does not generate any output data. In this case Z1 is not incremented. Proper HDLC data being received is converted by the HFC-S mini into plain data. After the ending flag of a frame the HFC-S mini checks the HDLC CRC checksum. If it is correct one STAT byte (see Figure 4) with all '0's is inserted behind the CRC data in the FIFO. This last byte of a frame in the FIFO is different from all '0's if there is no correct CRC field at the end of the frame.

The ending flag of a HDLC-frame can also be the starting flag of the next frame.

After a frame is received completely, *F*1 is incremented by the HFC-S mini automatically and the next frame can be received.

Figure 4: FIFO Data Organization

After reading a frame via the microprocessor bus interface, F2 must be incremented. If the frame counter F2 is incremented, also the Z-counters may change because Z1 and Z2 are functions of F1 and F2. So there are Z1(F1), Z2(F1), Z1(F2) and Z2(F2) (see Figure 3).

Z1(F1) is used for the frame which is just received from the S/T device side of the HFC-S mini. Z2(F2) is used for the frame which is just beeing transmitted to the microprocessor bus interface. Z1(F2) is the end of frame pointer of the current output frame.

To calculate the length of the current receive frame the software has to evaluate Z1 - Z2 + 1. When Z2 reaches Z1 the complete frame has been read.

In the receive channels F2 must be incremented from the microprocessor bus interface side after the software detects an *end of receive frame* (Z1 = Z2) and  $F1 \neq F2$ . Then the current value of Z2 is stored, F2 is incremented and Z2 is copied as start address of the next frame. If Z1 = Z2 and F1 = F2 the FIFO is totally empty. Z1(F1) can not be accessed.

# **Important!**

Before reading a FIFO, a change FIFO operation (see also: FIFO register) must be done even if the desired FIFO is already selected. The change FIFO operation is required to update the internal buffer of the HFC-S mini. Otherwise the first byte of the FIFO will be taken from the internal buffer and may be invalid.

#### 3.2.1.5 FIFO full condition in receive channels

Because the ISDN B-channels and the ISDN D-channels have no hardware based flow control there is no possibility to stop input data if a receive FIFO is full.

So there is no FIFO full condition implemented in the HFC-S mini. The HFC-S mini assumes that the FIFOs are so deep, that the host processors hardware and software is able to avoid any overflow of the receive FIFOs. Overflow conditions are again more than 7 input frames or a real overflow of the FIFO because of excessive data (more than 128 bytes).

Because HDLC procedures only know a window size of 7 frames no more than 7 frames are sent without software intervention.

The register F\_FILL indicates if the fill level of some FIFOs exceeds the number of bytes defined in the F\_THRES register. A byte overflow can be avoided by polling this register. After data processing from or to a FIFO, the F\_FILL register must be updated with a change FIFO or an increment FIFO counter operation. After this it takes up to  $250\,\mu\rm s$  until the bit value in the F\_FILL register of the processed FIFO represents the actual state of the FIFO filling level.

The register F\_USAGE shows the actually occupied FIFO space in bytes. A byte overflow can be avoided by polling this register.

However to avoid any undetected FIFO overflows the software driver should check the number of frames in the FIFO which is F1-F2. An overflow exists if the number F1-F2 is less than the number in the last reading even if there was no reading of a frame in between.

After a detected FIFO overflow condition this FIFO must be reset by setting the FIFO reset bit in the INC\_RES\_F register.

#### 3.2.2 FIFO initialization

All FIFOs are disabled after reset. To enable a FIFO, at least one of the bits[4:1] of the CON\_HDLC register for the corresponding FIFO must be set to '1'.

For D-channel FIFOs the inter frame fill bit (bit 0 of CON\_HDLC register) must be set to '1'. The HDLC\_PAR register must be set to 0x02 ('0000 0010').

Even for a data transmission between S/T interface and PCM interface where no FIFO data is involved, the data transmission capability is only activated if the corresponding FIFO is enabled.

#### 3.2.3 FIFO reset

All counters Z1, Z2, F1 and F2 of all FIFOs are initialized to all '1's after a reset. Then the result is Z1 = Z2 = 0x7F and F1 = F2 = 0x07.

The same initialisation is done if the bit 3 in the CIRM register is set (soft reset).

Single FIFOs can be reset by setting bit 1 of INC\_RES\_F register.

#### 3.3 Transparent mode of HFC-S mini

You can switch off HDLC operation for each B-channel independently. There is one bit for each B-channel in the CON\_HDLC control register. If this bit is set, data in the FIFO is sent directly to the

S/T or PCM bus interface and data from the S/T or PCM bus interface is sent directly to the FIFO.

The FIFOs should be empty when switching into transparent mode (F1 = F2).

If a send FIFO channel changes to FIFO empty condition no CRC is generated and the last data byte in the FIFO memory is repeated until there is new data. If the last data byte which was written to the selected FIFO should be repeated, the last byte must be written without increment of *Z*-counter (FIF DATA NOINC register, address 84).

In receive channels there is no check on flags or correct CRCs and no status byte is added.

The byte boundaries are not arbitrary like in HDLC mode where byte synchronisation is achieved with HDLC flags. The data is just the same as it comes from the S/T or PCM bus interface or is sent to this.

Send and receive transparent data can be handled in two ways. The usual way is transporting B-channel data with the LSB first as it is usual in HDLC mode. The second way is sending the bytes in reverse bit order as it is usual for PWM data. So the first bit is the MSB. The bit order can be reversed by setting the corresponding bit in the F\_CROSS register.

#### 3.4 Correspondency between FIFOs, CHANNELs and SLOTs

For the data processing of the HFC-S mini you must distinguish between FIFOs, CHANNELs and SLOTs.

The FIFOs are buffers between the microprocessor interface and the data interfaces PCM and/or S/T. The HDLC controllers are located on the non host bus side of the FIFOs.

The CHANNELs are either mapped to the data channels on the S/T interface (then the CHANNEL selects the S/T channel as shown in Table 3) or they can be connected to arbitrary time slots on the PCM interface. SLOTs are 8 bit time slots on the PCM interface. The following values (registers) characterise FIFOs, CHANNELs and SLOTs:

FIFO: FIFO

...

CHANNEL: CHANNEL

SLOT: B1\_RSL, B1\_SSL, B2\_RSL, B2\_SSL, AUX1\_RSL, AUX1\_SSL, AUX2\_RSL and AUX2\_SSL

Even numbers (LSB = '0') always belong to a transmit FIFO, transmit CHANNEL (see Table 4).

Odd numbers (LSB = '1') always belong to a receive FIFO, receive CHANNEL (see Table 4).

In Simple Mode (F\_MODE register bit 7 = '0', SM) the CHANNEL number equals the FIFO number. But it is possible to connect each FIFO to a PCM time slot instead of the S/T interface in this mode (see Table 3).

In Channel Select Mode (F\_MODE register bit 7 = '1', CSM) FIFOs can be associated with arbitrary CHANNELs.

FIFOs are selected by writing their number in the FIFO register. All FIFOs are disabled after initialization (reset). By setting at least one of the CON\_HDLC register bits 3..1 to '1' the selected FIFO is enabled.

The connection between a FIFO and a CHANNEL can be established by the CHANNEL register for each FIFO if Channel Select Mode is enabled (F\_MODE register bit 7 = '1', CSM). Otherwise the CHANNEL number equals the FIFO number.

Table 3: Possible connections of FIFO and CHANNELs in Simple Mode (SM)

| FIFO no. | CHANNEL after reset         | Possible connections in Simple Mode (SM) CON_HDLC[75]                |  |

|----------|-----------------------------|----------------------------------------------------------------------|--|

| '000'    | transmit B1-channel (S/T)   | transmit B1-channel (S/T) transmit PCM time slot selected by B1_SSL  |  |

| '001'    | receive B1-channel (S/T)    | receive B1-channel (S/T) receive PCM time slot selected by B1_RSL    |  |

| '010'    | transmit B2-channel (S/T)   | transmit B2-channel (S/T) transmit PCM time slot selected by B2_SSL  |  |

| '011'    | receive B2-channel (S/T)    | receive B2-channel (S/T) receive PCM time slot selected by B2_RSL    |  |

| '100'    | transmit D-channel (S/T)    | transmit D-channel (S/T) transmit PCM time slot selected by AUX1_SSL |  |

| '101'    | receive D-channel (S/T)     | receive D-channel (S/T) receive PCM time slot selected by AUX1_RSL   |  |

| '110'    | invalid (E is receive only) | - transmit PCM time slot selected by AUX2_SSL                        |  |

| '111'    | receive E-channel (S/T)     | receive E-channel (S/T) receive PCM time slot selected by AUX2_RSL   |  |

The channels on the S/T interface (B1, B2, D and E) and PCM interface (B1, B2, AUX1 and AUX2) are numbered as shown in Table 4.

Table 4: CHANNEL numbers on the S/T interface and PCM interface

| CHANNEL no. CHANNEL[20]            | ISDN channel on the S/T interface     | ISDN channel on the PCM interface |

|------------------------------------|---------------------------------------|-----------------------------------|

| '000'<br>'001'                     | B1 transmit<br>B1 receive             | B1 transmit<br>B1 receive         |

| '010' B2 transmit '011' B2 receive |                                       | B2 transmit B2 receive            |

| '100'<br>'101'                     | D transmit D receive                  | AUX1 transmit AUX1 receive        |

| '110'<br>'111'                     | invalid (E is receive only) E receive | AUX2 transmit<br>AUX2 receive     |

The data flow between the HFC part (FIFOs), S/T interface and PCM interface can be selected by the CON\_HDLC register (bits 7..5) for each FIFO.

The PCM time slot for B1, B2, AUX1 and AUX2 can be set by the time slot assigner (registers B1\_RSL, B1\_SSL, B2\_RSL, B2\_SSL, AUX1\_RSL, AUX1\_SSL, AUX2\_RSL and AUX2\_SSL).

Data of a CHANNEL can furthermore be looped over the PCM interface (and the time slot assigner).

Figure 5: FIFOs, CHANNELs and SLOTs in transmit Direction

- [T1] In Simple Mode (SM) the CHANNEL number is the same as the FIFO number. If Channel Select Mode (CSM) is enabled the transmit CHANNEL for a FIFO can be selected by

- 1. writing the FIFO number (0..7) in the FIFO register

- 2. writing the desired CHANNEL number (0..7) to the CHANNEL register (bits 2..0)

Please note that transmit CHANNELs are even numbered (bit 0 of CHANNEL register = '0').

- [T2] The bit values for the not processed bits of the transmit CHANNEL are read from the CH\_MASK register. The processed bits are taken from the FIFO (see also Section 3.5). Please note that more than one FIFO can transmit data to the same CHANNEL. This is useful to combine subchannels and transmit them in one ISDN channel.

- [T3] Data can either be transmitted to the S/T interface or the PCM interface.

- 1. write the FIFO number (0...7) in the FIFO register

- 2. write the desired connection to the CON\_HDLC register bits 7..5

The CON\_HDLC register bits 7..5 settings must be the same for corresponding receive and transmit FIFOs.

[T4] A PCM SLOT can be connected to a CHANNEL (see Table 5 on Page 26).

The PCM SLOT number for a CHANNEL can be selected by writing the desired SLOT number to its time slot selection register as shown in Table 5. Please note that the ..\_SSL registers are for transmit slots.

Figure 6: FIFOs, CHANNELs and SLOTs in receive direction

- [R1] In Simple Mode (SM) the CHANNEL number is the same as the FIFO number. If Channel Select Mode (CSM) is enabled the transmit CHANNEL for a FIFO can be selected by

- 1. writing the FIFO number (0..7) in the FIFO register

- 2. writing the desired CHANNEL number (0..7) to the CHANNEL register (bits 2..0)

Please note that receive CHANNELs are odd numbered (bit 0 of CHANNEL register = '1').

- [R2] The bit values of the not processed bits of the receive CHANNEL are ignored. The processed bits are taken from the CHANNEL (see also Section 3.5). Please note that more than one FIFO can receive data from the same CHANNEL (e.g. bits 1..0 are processed by FIFO 1 and bits 3..2 by FIFO 3). This is useful to split subchannels that have been combined to be transmitted in one ISDN channel.

- [R3] Data can either be received from the S/T interface or the PCM interface.

- 1. write the FIFO number (0..7) in the FIFO register

- 2. write the desired connection to the CON HDLC register bits 7..5

The CON\_HDLC register bits 7..5 settings must be the same for corresponding receive and transmit FIFOs.

**[R4]** A PCM SLOT can be connected to a CHANNEL (see Table 5).

The PCM SLOT number for a CHANNEL can be selected by writing the desired SLOT number to its time slot selection selection register as shown in Table 5. Please note that only the ..\_RSL registers are for receive slots.

**Table 5:** FIFO to S/T channel assignment (In Simple Mode the FIFO number is used as CHANNEL number; in Channel Select Mode the CHANNEL number can be selected for each FIFO in the register CHANNEL.)

| CHANNEL no.<br>(FIFO[20]<br>or CHANNEL[20] | Register for<br>time slot<br>selection |  |

|--------------------------------------------|----------------------------------------|--|

| '000'                                      | B1_SSL                                 |  |

| '001'                                      | B1_RSL                                 |  |

| '010'                                      | B2_SSL                                 |  |

| '011'                                      | B2_RSL                                 |  |

| '100'                                      | AUX1_SSL                               |  |

| '101'                                      | AUX1_RSL                               |  |

| '110'                                      | AUX2_SSL                               |  |

| '111'                                      | AUX2_RSL                               |  |

#### 3.5 Subchannel Processing

The following example shows how subchannel processing can be configured by the HDLC\_PAR register. Bits are shown on the PCM interface.

Figure 7: Example for Subchannel Processing

The start bit can be selected by bits 5..3 of the HDLC\_PAR register. The number of bits to process can be selected by bits 2..0 of the HDLC\_PAR register. By default (HDLC\_PAR = 0x00) all 8 bits are processed. In the given example the start bit is bit 2 and the number of bits to process is 3. The not processed bits are set to the value given in the CH\_MASK register. Please note that the HDLC\_PAR register settings can be different for each channel.

## 3.6 PCM Interface Function

Figure 8: PCM Interface Function Block Diagram

Table 6: PCM interface control options

| Number Function |                                              | B1_SSL, B2_SSL, AUX1_SSL<br>and AUX2_SSL register bits |  |

|-----------------|----------------------------------------------|--------------------------------------------------------|--|

| [1]             | Data channel select for transmit slot        | Bits[4:0] are for time slot selection                  |  |

| [2]             | STIO1 Output buffer enable for transmit slot | Bits[7:6] = '10' (STIO1 output buffer enable)          |  |

| [3]             | STIO2 output buffer enable for transmit slot | Bits[7:6] = '11' (STIO2 output buffer enable)          |  |

| Number Function |                                              | B1_RSL, B2_RSL, AUX1_RSL                               |  |

|                 |                                              | and AUX2_RSL register bits                             |  |

| [4]             | Input buffer select for receive slot         | Bit 6 = '0' (data in from STIO2 [MUX input B])         |  |

|                 |                                              | Bit 6 = '1' (data in from STIO1 [MUX input A])         |  |

| [5]             | Loop MST internally                          | Bit 6 of MST_MODE1 register                            |  |

|                 |                                              | '0' MUX input B (normal operation)                     |  |

|                 |                                              | '1' MUX input A (internal loop)                        |  |

| [6]             | Data channel select for receive slot         | Bits[4:0] are for time slot selection                  |  |

# 3.7 Configuring test loops

For electrical tests of layer 1 it is useful to create a S/T test loop for the B1/B2 channel. The test loop described here transmits the data that has been received on the B1- or B2-channel of the S/T interface to the same transmit channel back on the S/T interface. To configure the test loop the following settings have to implemented:

| write 0x0F to register CLKDEL (0x37)    | // Adjust the phase offset between receive and                              |

|-----------------------------------------|-----------------------------------------------------------------------------|

|                                         | // transmit direction (the value depends on the external                    |

|                                         | // circuitry).                                                              |

| write 0x43 to register SCTRL (0x31)     | // 0x03 is to enable B1, B2 at the S/T interface for                        |

|                                         | // transmission                                                             |

|                                         | // Bit 6 could be set for /TX1_LO and /TX2_LO setup                         |

|                                         | // (non-capacitive line mode), this depends on the                          |

|                                         | // external S/T circuitry                                                   |

| write 0x00 to register ST_RD_STA (0x30) | // Release S/T state machine for activation over the                        |

|                                         | // S/T interface by incoming INFO 2 or INFO 4.                              |

| write 0x03 to register SCTRL_R (0x33)   | // Configure S/T B1- and B2-channel to normal                               |

|                                         | // receive operation.                                                       |

| write 0x00 to register FIFO (0x0F)      | // Select B1 transmit                                                       |

| write 0xC4 to register CON_HDLC (0xFA)  | // Configure transmit B1-channel for test loop                              |

| write 0x01 to register FIFO (0x0F)      | // Select B1 receive                                                        |

| write 0xC4 to register CON_HDLC (0xFA)  | // Configure receive B1-channel for test loop                               |

| write 0x02 to register FIFO (0x0F)      | // Select B2 transmit                                                       |

| write 0xC4 to register CON_HDLC (0xFA)  | // Configure transmit B2-channel for test loop                              |

| write 0x03 to register FIFO (0x0F)      | // Select B2 receive                                                        |

| write 0xC4 to register CON_HDLC (0xFA)  | // Configure receive B2-channel for test loop                               |

| write 0x80 to register B1_SSL (0x20)    | // Enable transmit channel for PCM/GCI/IOM2 bus,                            |

|                                         | // pin STIO1 is used as output, use time slot #0.                           |

| write 0xC0 to register B1_RSL (0x24)    | // Enable receive channel for PCM / GCI / IOM2 bus,                         |

|                                         | // pin STIO1 is used as input, use time slot #0.                            |

| write 0x81 to register B2_SSL (0x21)    | // Enable transmit channel for PCM/GCI/IOM2 bus,                            |

|                                         | // pin STIO1 is used as output, use transmission slot #1.                   |

| write 0xC1 to register B2_RSL (0x25)    | // Enable receive channel for PCM / GCI / IOM2 bus,                         |

|                                         | // pin STIO1 is used as input, use time slot #1.                            |

| write 0x01 to register MST_MODE0 (0x14) | $\label{lem:configure} \textit{HFC-S mini}\ as\ PCM/GCI/IOM2\ bus\ master.$ |

# 4 Register description

# 4.1 FIFO, interrupt, status and control registers

| CIRM (write only) |                                                                                                       | 0x00 |

|-------------------|-------------------------------------------------------------------------------------------------------|------|

| Soft res          | pet                                                                                                   |      |

| Bits              | Description                                                                                           |      |

| 20                | unused, must be '0'                                                                                   |      |

| 3                 | The reset is active until the bit is cleared. '0' deactivate reset (reset default) '1' activate reset |      |

| 74                | unused, must be '0'                                                                                   |      |

| F_CRO    | SS (write only)                                                                                                  | 0x0B |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------|------|--|--|--|

| '0' norm | Select bit order for FIFO data '0' normal bit order (LSB first, reset default) '1' reverse bit order (MSB first) |      |  |  |  |

| Bits     | Description                                                                                                      |      |  |  |  |

| 0        | B1 transmit                                                                                                      |      |  |  |  |

| 1        | B1 receive                                                                                                       |      |  |  |  |

| 2        | B2 transmit                                                                                                      |      |  |  |  |

| 3        | B2 receive                                                                                                       |      |  |  |  |

| 4        | D transmit                                                                                                       |      |  |  |  |

| 5        | D receive                                                                                                        |      |  |  |  |

| 6        | PCM transmit                                                                                                     |      |  |  |  |

| 7        | PCM receive                                                                                                      |      |  |  |  |

| F_MOD  | DE (write only)      | 0x0D |

|--------|----------------------|------|

| Channe | el Select Mode (CSM) |      |

| Bits   | Description          |      |

| 60     | must be '0'          |      |

| 7      | enable CSM           |      |

| INC_RI | ES_F [FIFO] (write only)                                                                        | 0x0E |

|--------|-------------------------------------------------------------------------------------------------|------|

| F-coun | ter increment and reset                                                                         |      |

| Bits   | Description                                                                                     |      |

| 0      | Increment <i>F</i> -counter of selected FIFO '1' = increment This bit is automatically cleared. |      |

| 1      | Reset selected FIFO '1' = reset FIFO This bit is automatically cleared.                         |      |

| 72     | unused, should be '0'                                                                           |      |

| RAM_A  | DR_L [FIFO]                           | (write only) | 0x08 |

|--------|---------------------------------------|--------------|------|

| Low by | e of RAM address                      |              |      |

| Bits   | Description                           |              |      |

| 70     | Address bits 70 for direct RAM access |              |      |

| RAM_A   | ADR_H (write only)                                                | 0x09 |

|---------|-------------------------------------------------------------------|------|

| High by | te of RAM address                                                 |      |

| Bits    | Description                                                       |      |

| 20      | Address bits 108 for direct RAM access                            |      |

| 53      | must be '0'                                                       |      |

| 6       | '1' reset address This bit is automatically cleared.              |      |

| 7       | '1' increment address after each read or write access to RAM_DATA |      |

| RAM_D  | ATA (read/write)                                            | 0xC0 |

|--------|-------------------------------------------------------------|------|

| Read/w | rite RAM data                                               |      |

| Bits   | Description                                                 |      |

| 70     | FIFOs should be disabled before accessing the RAM directly. |      |

The registers RAM\_ADR\_H, RAM\_ADR\_L and RAM\_DATA can be used or direct accesses to the internal FIFO RAM. They are normally not used.

The FIFOs are located in the address range from 0x000 to 0x3FF. Bits 2..0 of the address select the FIFO number, bits 10..4 are used to address the FIFO data.

Before reading/writing data from/to a memory region all FIFOs using this region must be disabled.

| FIFO    | (write only) 0x                                                                                                                                          | 0F |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| FIFO se | elect                                                                                                                                                    |    |

| Bits    | Description                                                                                                                                              |    |

| 20      | '000' B1 transmit '001' B1 receive '010' B2 transmit '011' B2 receive '100' D transmit '101' D receive '110' PCM transmit '111' PCM receive or E receive |    |

| 73      | unused, should be '0'                                                                                                                                    |    |

| F_USA   | GE [FIFO] (read only)       | 0x1A |

|---------|-----------------------------|------|

| FIFO us | sage                        |      |

| Bits    | Description                 |      |

| 70      | fill level of FIFO in bytes |      |

| FIF_DA  | TA [FIFO] (read/write)                                                                 | 0x80 |

|---------|----------------------------------------------------------------------------------------|------|

| FIFO da | ata register                                                                           |      |

| Bits    | Description                                                                            |      |

| 70      | Read/write data from/to the FIFO selected in the FIFO register and increment Z-counter |      |

| FIF_DA  | TA_NOINC [FIFO] (read/write)                                                               | 0x84 |

|---------|--------------------------------------------------------------------------------------------|------|

| FIFO da | ata register                                                                               |      |

| Bits    | Description                                                                                |      |

| 70      | Read/write data from/to the FIFO selected in the FIFO register without incrementing Z-cour | nter |

| FIF_F1  | [FIFO] (read only)                              | 0x0C |

|---------|-------------------------------------------------|------|

| FIFO in | put HDLC frame counter $F1$                     |      |

| Bits    | Description                                     |      |

| 70      | Up to 7 HDLC frames can be stored in each FIFO. |      |

| FIF_F2  | [FIFO] (read only)                              | 0x0D |

|---------|-------------------------------------------------|------|

| FIFO ou | atput HDLC frame counter $F2$                   |      |

| Bits    | Description                                     |      |

| 70      | Up to 7 HDLC frames can be stored in each FIFO. |      |

| FIF_Z1  | [FIFO] (read only)                                                                        | 0x04 |

|---------|-------------------------------------------------------------------------------------------|------|

| FIFO in | put counter Z1                                                                            |      |

| Bits    | Description                                                                               |      |

| 70      | Up to 128 bytes can be stored in one FIFO so the maximum value of the $Z1$ counter is 0x7 | F.   |

| FIF_Z2  | [FIFO] (read only)                                                                          | 0x06 |

|---------|---------------------------------------------------------------------------------------------|------|

| FIFO or | utput counter Z2                                                                            |      |

| Bits    | Description                                                                                 |      |

| 70      | Up to 128 bytes can be stored in one FIFO so the maximum value of the $Z2$ counter is $0x7$ | 7F.  |

| F_THR   | ES (write only) 0x0C                                                                                                                                                                                                                                                                                                           |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| FIFO tl | FIFO threshold                                                                                                                                                                                                                                                                                                                 |  |  |