# Frequency Timing Generator for PENTIUM II Systems

#### **Features**

- Generates the following system clocks:

- -3 CPU clocks (2.5V, 100/133MHz)

- 10 PCI clocks, including 1 free-running (3.3V, 33.3MHz)

- 1 CPU/2 clocks (2.5V, 50/66.6MHz)

- 1 IOAPIC clocks (2.5V, 16.67MHz)

- -3 Fixed frequency 66MHz clocks(3.3V, 66.6MHz)

- -2 REF clocks(3.3V, 14.318MHz)

- -1 USB clock (3.3V, 48MHz)

- Efficient power management through PD#.

- 0 to -0.5% typical down spread modulation on CPU, PCI, IOAPIC, 3V66 and CPU/2 output clocks.

- Uses external 14.318MHz crystal.

## **Key Specification**

- CPU Output Jitter: <250ps

- CPU/2 Output Jitter. <250ps

- IOAPIC Output Jitter: <500ps

- 48MHz, 3V66, PCI Output Jitter: <500ps

- PCI Output Jitter. <500ps

- Ref Output Jitter. <1000ps

- CPU 0:2 Output Skew: <175ps

- PCI F, PCI 1:7 Output Skew: <500ps

- 3V66 0:2 Output Skew < 250ps

- CPU to 3V66 0:2 Output Offset: 0.0 1.5ns (CPU leads)

- 3V66 to PCI Output Offset: 1.5 4ns (CPU leads)

- CPU to IOAPIC Output Offset 1.5 4.0ns (CPU leads)

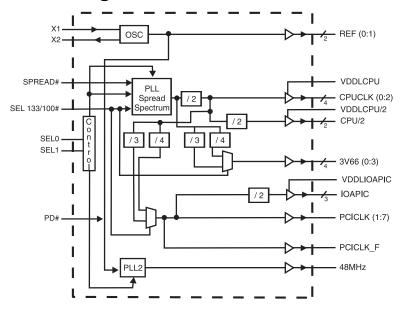

### **Block Diagram**

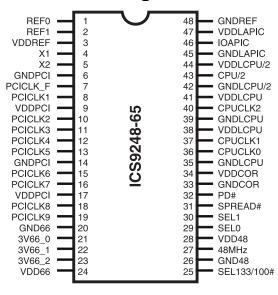

### **Pin Configuration**

### **General Description**

The ICS9248-65 is a main clock synthesizer chip for Pentium II based systems using Rambus Interface DRAMs. This chip provides all the clocks required for such a system when used with a Direct Rambus Clock Generator(DRCG) chip such as the ICS9211-01.

Spread Spectrum may be enabled by driving the SPREAD# pin active. Spread spectrum typically reduces system EMI by 8dB to 10dB. This simplifies EMI qualification without resorting to board design iterations or costly shielding. The ICS9248-65 employs a proprietary closed loop design, which tightly controls the percentage of spreading over process and temperature variations.

The CPU/2 clocks are inputs to the DRCG.

### **Power Groups:**

VDDREF, GNDREF=REF, X1, X2 GNDPCI, VDDPCI=PCICLK VDD66, GND66=3V66 VDD48, GND48=48MHz VDDCOR, GNDCOR=PLL Core VDDLCPU/2, GNDLCPU/2=CPU/2 VDDLIOAPIC, GNDIOAPIC=IOAPIC

### **Pin Descriptions**

| Pin number                    | Pin name        | Туре   | Description                                                                                                                                                                                                                                           |

|-------------------------------|-----------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,2                           | REF             | Output | 3.3V, 14.318 MHz reference clock output.                                                                                                                                                                                                              |

| 3, 9, 17, 24,<br>28, 34       | VDD             | Power  | 3.3 V power for clock outputs.                                                                                                                                                                                                                        |

| 4                             | X1              | Input  | 14.318 MHz crystal input                                                                                                                                                                                                                              |

| 5                             | X2              | Output | 14.318 MHz crystal output                                                                                                                                                                                                                             |

| 6,14, 20, 26,<br>33, 45, 48   | GND             | Power  | Ground for clock outputs                                                                                                                                                                                                                              |

| 7                             | PCICLK_F        | Output | 3.3 V free running PCI clock output, will not be stopped by the PCI_STOP#                                                                                                                                                                             |

| 8,10,11,12,13,<br>15,16,18,19 | PCICLK (1:9)    | Output | 3.3 V PCI clock outputs, generating timing requirements for                                                                                                                                                                                           |

| 21,22,23                      | 3V66            | Output | 3.3 V 66 MHz clock output, fixed frequency clock typically used with AGP                                                                                                                                                                              |

| 25                            | SEL<br>133/100# | Input  | Control for the frequency of clocks at the CPU output pins. If logic "0" is used the 100 MHz frequency is selected. If Logic "1" is used, the 133 MHz frequency is selected. The PCI clock is multiplexed to run at 33.3 MHz for both selected cases. |

| 27                            | 48 MHz          | Output | 3.3 V 48 MHz clock output, fixed frequency clock typically used with USB devices                                                                                                                                                                      |

| 29,30                         | SEL (0:1)       | Input  | Frequency select pin, logic input.                                                                                                                                                                                                                    |

| 31                            | SPREAD#         | Output | Power-on spread spectrum enable option. Active low = spread spectrum clocking enable. Active high = spread spectrum clocking disable.                                                                                                                 |

| 32                            | PD#             | Input  | Asynchronous active low input pin used to power down the device into a low power state. The internal clocks are disabled and the VCO and the crystal are stopped.                                                                                     |

| 35,39                         | GNDLCPU         | Power  | Ground for the CPU and Host clock outputs                                                                                                                                                                                                             |

| 36,37,40                      | CPUCLK<br>(0:2) | Output | 2.5 V CPU and Host clock outputs                                                                                                                                                                                                                      |

| 38,41                         | VDDLCPU         | Power  | 2.5 V power for the CPU and Host clock outputs                                                                                                                                                                                                        |

| 42                            | GNDLCPU/2       | Power  | Ground for the CPU and Host clock outputs                                                                                                                                                                                                             |

| 43                            | CPU/2           | Output | Output running at 1/2 CPU clock frequency. Synchronous to the CPU outputs.                                                                                                                                                                            |

| 44                            | VDDLCPU/2       | Power  | 2.5 V power for the CPU/2 clock outputs                                                                                                                                                                                                               |

| 46                            | IOAPIC(0:1)     | Output | 2.5V fixed 16.6 MHz IOAPIC clock outputs                                                                                                                                                                                                              |

| 47                            | VDDIOAPIC       | Power  | 2.5V power for IOAPIC clock                                                                                                                                                                                                                           |

### **Frequency Select:**

| SEL      | SEL1 | SEL0 | CPU    | CPU/2           | 3V66   | PCI    | 48     | REF       | IOAPIC  | Comments      |

|----------|------|------|--------|-----------------|--------|--------|--------|-----------|---------|---------------|

| 133/100# | SELI | SELU | MHz    | MHz             | MHz    | MHz    | MHz    | MHz       | MHz     | Comments      |

| 0        | 0    | 0    | Hi-Z   | Hi-Z            | Hi-Z   | Hi-Z   | Hi-Z   | Hi-Z      | Hi-Z    | Tri-state     |

| 0        | 0    | 1    | N/A    | N/A             | N/A    | N/A    | N/A    | N/A       | N/A     | Reserved      |

| 0        | 1    | 0    | 100    | 50 66.6 33.3 Hi | Hi-Z   | 14.318 | 16.67  | 48MHz PLL |         |               |

|          | 1    | U    | 100    | 30              | 00.0   | 33.3   | 111-Z  | 14.516    | 10.07   | disabled      |

| 0        | 1    | 1    | 100    | 50              | 66.6   | 33.3   | 48     | 14.318    | 16.67   |               |

| 1        | 0    | 0    | TCLK/2 | TCLK/4          | TCLK/4 | TCLK/8 | TCLK/2 | TCLK      | TCLK/16 | Test mode (1) |

| 1        | 0    | 1    | N/A    | N/A             | N/A    | N/A    | N/A    | N/A       | N/A     | Reserved      |

| 1        | 1    | 0    | 133.3  | 66              | 66     | 33     | Hi-Z   | 14.318    | 16.67   |               |

| 1        | 1    | 1    | 133.3  | 66              | 66     | 33     | 48     | 14.318    | 16.67   |               |

#### Note:

1. TCLK is a test clock driven on the x1 input during test mode.

# ICS9248-65 Power Management Features:

| PD# | CPUCLK | CPU/2 | IOAPIC | 3V66 | PCI | PCI_F | REF.<br>48MHz | Osc | VCOs |

|-----|--------|-------|--------|------|-----|-------|---------------|-----|------|

| 0   | LOW    | LOW   | LOW    | LOW  | LOW | LOW   | LOW           | OFF | OFF  |

| 1   | ON     | ON    | ON     | ON   | ON  | ON    | ON            | ON  | ON   |

#### Note:

- 1. LOW means outputs held static LOW as per latency requirement next page.

- 2. On means active.

- 3. PD# pulled Low, impacts all outputs including REF and 48 MHz outputs.

### **Power Management Requirements:**

| Singal       | Singal State         | Latency No. of rising edges of PCICLK |

|--------------|----------------------|---------------------------------------|

| PD#          | 1 (normal operation) | 3mS                                   |

| Γ <i>D</i> # | 0 (power down)       | 2max.                                 |

#### Note:

- 1. Clock on/off latency is defined in the number of rising edges of free running PCICLKs between the clock disable goes low/high to the first valid clock comes out of the device.

- 2. Power up latency is when PWR\_DWN# goes inactive (high to when the first valid clocks are dirven from the device.

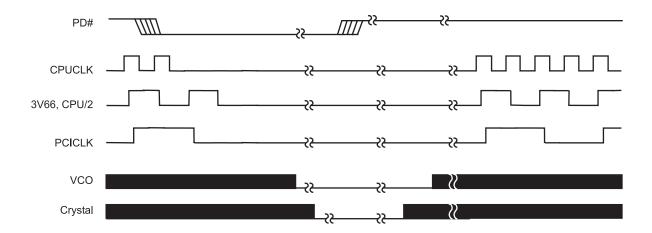

### **PD# Timing Diagram**

The power down selection is used to put the part into a very low power state without turning off the power to the part. PD# is an asynchronous active low input. This signal needs to be synchronized internal to the device prior to powering down the clock synthesizer.

Internal clocks are not running after the device is put in power down. When PD# is active low all clocks need to be driven to a low value and held prior to turning off the VCOs and crystal. The power up latency needs to be less than 3 mS. The power down latency should be as short as possible but conforming to the sequence requirements shown below. PCI\_STOP# and CPU\_STOP# are considered to be don't cares during the power down operations. The REF and 48MHz clocks are expected to be stopped in the LOW state as soon as possible. Due to the state of the internal logic, stopping and holding the REF clock outputs in the LOW state may require more than one clock cycle to complete.

#### Notes:

- 1. All timing is referenced to the Internal CPUCLK (defined as inside the ICS9248 device).

- 2. As shown, the outputs Stop Low on the next falling edge after PD# goes low.

- 3. PD# is an asynchronous input and metastable conditions may exist. This signal is synchronized inside this part.

- 4. The shaded sections on the VCO and the Crystal signals indicate an active clock.

- 5. Diagrams shown with respect to 133MHz. Similar operation when CPU is 100MHz.

### **Absolute Maximum Ratings**

Supply Voltage . . . . . . . . . . . . . . . . . 7.0 V

Ambient Operating Temperature ...... 0°C to +70°C

Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

### **Group Offset**

| Group         | Offset               | Measurement Loads         | Measure Points            |

|---------------|----------------------|---------------------------|---------------------------|

| CPU to 3V66   | 0.0-1.5ns CPU leads  | CPU @ 20pF, 3V66 @ 30pF   | CPU @1.25V, 3V66 @ 1.5V   |

| 3V66 to PCI   | 1.5-4.0ns 3V66 leads | 3V66 @ 30pF, PCI @ 30pF   | 3V66 @ 1.5V, PCI @ 1.5V   |

| CPU to IOAPIC | 1.5-4.0ns CPU leads  | CPU @ 20pF, IOAPIC @ 20pF | CPU @1.25V, IOAPIC @ 1.5V |

Note: 1. All offsets are to be measured at rising edges.

### **Electrical Characteristics - Input/Supply/Common Output Parameters**

$T_A = 0 - 70^{\circ}$  C; Supply Voltage  $V_{DD} = VDDL = 3.3 \text{ V} + /-5\%$ , (unless otherwise stated)

| PARAMETER                      | SYMBOL                                                 | CONDITIONS                                              | MIN           | TYP    | MAX                      | UNITS |

|--------------------------------|--------------------------------------------------------|---------------------------------------------------------|---------------|--------|--------------------------|-------|

| Input High Voltage             | $V_{IH}$                                               |                                                         | 2             |        | V <sub>DD</sub> +0.3     | V     |

| Input Low Voltage              | $V_{ m IL}$                                            |                                                         | $V_{SS}$ -0.3 |        | 0.8                      | V     |

| Input High Current             | $I_{\mathrm{IH}}$                                      | $V_{IN} = V_{DD}$                                       |               | 0.1    | 5                        | μΑ    |

| Input Low Current              | $I_{\rm IL1}$                                          | V <sub>IN</sub> = 0 V; Inputs with no pull-up resistors | -5            | 2.0    |                          | μΑ    |

| Input Low Current              | $I_{IL2}$                                              | $V_{IN} = 0$ V; Inputs with pull-up resistors           | -200          | -100   |                          | μΑ    |

|                                | IDD3.30P100                                            | $C_L = 0 \text{ pF}$ ; Select @ 100 MHz                 |               | 65     |                          |       |

| Omanatina                      | IDD3.30P133                                            | C <sub>L</sub> = 0 pF; Select @ 133.3 MHz               |               | 71     | 160                      | A     |

| Operating                      | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | 75                                                      | 160           | mA     |                          |       |

|                                | IDD3.30P154                                            | $C_L = 0 \text{ pF}$ ; Select @ 154 MHz                 |               | 78     | 200<br>200<br>18 16<br>5 |       |

| Power Down                     | I <sub>DD3.3PD</sub>                                   | $C_L = 0 \text{ pF}; PWRDWN\# = 0$                      |               | 64     | 200                      | μΑ    |

| Supply Current                 |                                                        |                                                         |               |        |                          |       |

| Input frequency                | $F_{i}$                                                | $V_{DD} = 3.3 \text{ V}$                                | 12            | 14.318 | 16                       | MHz   |

| Input Capacitance <sup>1</sup> | $C_{IN}$                                               | Logic Inputs                                            |               |        | 5                        | pF    |

|                                | C <sub>INX</sub>                                       | X1 & X2 pins                                            | 27            | 36     | 45                       | pF    |

| Transition Time <sup>1</sup>   | T <sub>trans</sub>                                     | To 1st crossing of target Freq.                         |               | 1      | 3                        | ms    |

| Settling Time <sup>1</sup>     | $T_{s}$                                                | From 1st crossing to 1% target Freq.                    |               | 0.5    |                          | ms    |

| Clk Stabilization <sup>1</sup> | T <sub>STAB</sub>                                      | From $V_{DD} = 3.3 \text{ V to } 1\%$ target Freq.      |               |        | 3                        | ms    |

| Skew <sup>1</sup>              |                                                        | $V_T = 1.5 \text{ V}; \ V_{TL} = 1.25 \text{ V}$        | 1.5           | 2.4    | 4                        | ns    |

| Skew <sup>1</sup>              | tCPU-3V66                                              | $V_T = 1.5 \text{ V}; V_{TL} = 1.25 \text{ V}$          |               | 1.4    | 1.5                      | ns    |

| Skew <sup>1</sup>              | t3V66-PCI                                              | $V_T = 1.5 \text{ V}$                                   |               | 1.4    | 4                        | ns    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

# **Electrical Characteristics - Input/Supply/Common Output Parameters**

$T_A = 0 - 70^{\circ}$  C; Supply Voltage  $V_{DD} = 3.3 \text{ V} + /-5\%$ ,  $V_{DDL} = 2.5 \text{ V} + /-5\%$  (unless otherwise stated)

| PARAMETER         | SYMBOL      | CONDITIONS                                        | MIN | TYP | MAX | UNITS |

|-------------------|-------------|---------------------------------------------------|-----|-----|-----|-------|

|                   | IDD2.50P100 | $C_L = 0 \text{ pF}$ ; Select @ $100 \text{ MHz}$ |     | 14  | 30  | mA    |

| Operating         | IDD2.50P133 | $C_L = 0 \text{ pF}$ ; Select @ 133.3 MHz         |     | 18  | 30  | IIIA  |

| Supply Current    | IDD2.50P144 | $C_L = 0 \text{ pF}$ ; Select @ 144 MHz           |     | 19  | 30  |       |

|                   | IDD2.50P154 | $C_L = 0 \text{ pF}$ ; Select @ 154 MHz           |     | 20  | 30  |       |

| Power Down        | IDD2.5PD    | $C_L = 0 \text{ pF}; \text{ PWRDWN#} = 0$         |     | 0.3 | 100 | μΑ    |

| Supply Current    |             |                                                   |     |     |     |       |

| Skew <sup>1</sup> | tcpu-pci    | $V_T = 1.5 \text{ V}; V_{TL} = 1.25 \text{ V}$    | 1.5 | 2.4 | 4   | ns    |

| Skew <sup>1</sup> | tcpu-3V66   | $V_T = 1.5 \text{ V}; V_{TL} = 1.25 \text{ V}$    |     | 1.4 | 1.5 | ns    |

| Skew <sup>1</sup> | tcpu-ioapic | $V_{TL} = 1.25 \text{ V}$                         |     | 1.4 | 4   | ns    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

### **Electrical Characteristics - CPUCLK**

$T_A = 0 - 70^{\circ} \text{ C}$ ;  $V_{DD} = 3.3 \text{ V} + /-5\%$ ,  $V_{DDL} = 2.5 \text{ V} + /-5\%$ ;  $C_L = 20 \text{ pF}$  (unless otherwise stated)

| PARAMETER              | SYMBOL                           | CONDITIONS                                             | MIN  | TYP  | MAX  | UNITS |

|------------------------|----------------------------------|--------------------------------------------------------|------|------|------|-------|

| Output High Voltage    | $V_{OH2B}$                       | $I_{OH} = -12.0 \text{ mA}$                            | 2    | 2.3  |      | V     |

| Output Low Voltage     | $V_{OL2B}$                       | $I_{OL} = 12 \text{ mA}$                               |      | 0.31 | 0.4  | V     |

| Output High Current    | $I_{OH2B}$                       | $V_{OH} = 1.7 \text{ V}$                               |      | -39  | -19  | mA    |

| Output Low Current     | $I_{OL2B}$                       | $V_{OL} = 0.7 \text{ V}$                               | 19   | 27   |      | mA    |

| Rise Time              | $t_{r2B}^{1}$                    | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.0 \text{ V}$       |      | 0.95 | 1.6  | ns    |

| Fall Time              | $t_{f2B}^{1}$                    | $V_{OH} = 2.0 \text{ V}, V_{OL} = 0.4 \text{ V}$       |      | 1    | 1.6  | ns    |

| Duty Cycle             | $d_{t2B}^{-1}$                   | $V_T = 1.25 \text{ V}, \text{Freq.} < 124 \text{ MHz}$ | 45   | 50   | 55   | %     |

| Skew                   | $t_{sk2B}^{1}$                   | $V_T = 1.25 \text{ V}$                                 |      | 22   | 175  | ps    |

| Jitter, One Sigma      | $t_{j1\sigma 2B}^{1}$            | $V_T = 1.25 \text{ V}$                                 |      | 21   | 150  | ps    |

| Jitter, Absolute       | t <sub>jabs2B</sub> <sup>1</sup> | $V_T = 1.25 \text{ V}$                                 | -250 | 55   | +250 | ps    |

| Jitter, Cycle-to-cycle | t <sub>jcyc-cyc2B</sub> 1        | $V_T = 1.25 \text{ V}$                                 |      | 110  | 250  | ps    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

### **Electrical Characteristics - CPU/2**

$T_A = 0 - 70^{\circ} \text{ C}; \ V_{DD} = 3.3 \ V + / -5\%, \ V_{DDL} = 2.5 \ V + / -5\%; \ C_L = 20 \ pF (unless otherwise stated)$

| PARAMETER              | SYMBOL                               | CONDITIONS                                             | MIN  | TYP  | MAX  | UNITS |

|------------------------|--------------------------------------|--------------------------------------------------------|------|------|------|-------|

| Output High Voltage    | $V_{OH2B}$                           | $I_{OH} = -12.0 \text{ mA}$                            | 2    | 2.3  |      | V     |

| Output Low Voltage     | $V_{OL2B}$                           | $I_{OL} = 12 \text{ mA}$                               |      | 0.31 | 0.4  | V     |

| Output High Current    | $I_{OH2B}$                           | $V_{OH} = 1.7 \text{ V}$                               |      | -33  | -19  | mA    |

| Output Low Current     | $I_{OL2B}$                           | $V_{OL} = 0.7 \text{ V}$                               | 19   | 27   |      | mA    |

| Rise Time              | $t_{r2B}^{1}$                        | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.0 \text{ V}$       |      | 1.1  | 1.6  | ns    |

| Fall Time              | $t_{f2B}^{1}$                        | $V_{OH} = 2.0 \text{ V}, V_{OL} = 0.4 \text{ V}$       |      | 1    | 1.6  | ns    |

| Duty Cycle             | $d_{t2B}^{-1}$                       | $V_T = 1.25 \text{ V}, \text{Freq.} < 124 \text{ MHz}$ | 45   | 48   | 55   | %     |

| Jitter, One Sigma      | $t_{j1\sigma 2B}^{1}$                | $V_{\rm T} = 1.25 \text{ V}$                           |      | 13   | 150  | ps    |

| Jitter, Absolute       | $t_{\mathrm{jabs2B}}^{-1}$           | $V_{\rm T} = 1.25 \text{ V}$                           | -250 | 42   | +250 | ps    |

| Jitter, Cycle-to-cycle | t <sub>jcyc-cyc2B</sub> <sup>1</sup> | $V_{\rm T} = 1.25 \text{ V}$                           |      | 100  | 250  | ps    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

### **Electrical Characteristics - 3V66**

$T_A = 0 - 70^{\circ} \text{ C}$ ;  $V_{DD} = 3.3 \text{ V} + /-5\%$ ,  $V_{DDL} = 2.5 \text{ V} + /-5\%$ ;  $C_L = 30 \text{ pF}$  (unless otherwise stated)

| PARAMETER                           | SYMBOL                 | CONDITIONS                                       | MIN  | TYP  | MAX | UNITS |

|-------------------------------------|------------------------|--------------------------------------------------|------|------|-----|-------|

| Output High Voltage                 | V <sub>OH1</sub>       | $I_{OH} = -11 \text{ mA}$                        | 2.4  | 3.1  |     | V     |

| Output Low Voltage                  | Vol1                   | IoL = 9.4  mA                                    |      | 0.17 | 0.4 | V     |

| Output High Current                 | I <sub>OH1</sub>       | $V_{OH} = 2.0 \text{ V}$                         |      | -61  | -22 | mA    |

| Output Low Current                  | $I_{OL1}$              | $V_{OL} = 0.8 \text{ V}$                         | 25   | 45   |     | mA    |

| Rise Time <sup>1</sup>              | t <sub>r1</sub>        | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.4 \text{ V}$ | 0.5  | 1.8  | 2   | ns    |

| Fall Time <sup>1</sup>              | tfl                    | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$ | 0.5  | 1.7  | 2   | ns    |

| Duty Cycle <sup>1</sup>             | dt1                    | $V_T = 1.5 \text{ V}$                            | 45   | 51   | 55  | %     |

| Skew <sup>1</sup>                   | $t_{sk1}$              | $V_T = 1.5 \text{ V}$                            |      | 37   | 500 | ps    |

| Jitter, One Sigma <sup>1</sup>      | tj1 <sub>0</sub> 1     | $V_T = 1.5 \text{ V}$                            |      | 16   | 150 | ps    |

| Jitter, Absolute <sup>1</sup>       | tjabs1                 | $V_T = 1.5 \text{ V}$                            | -250 | 50   | 250 | ps    |

| Jitter, Cycle-to-cycle <sup>1</sup> | t <sub>jcyc-cyc1</sub> | $V_T = 1.5 \text{ V}$                            |      | 130  | 500 | ps    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

### **Electrical Characteristics - PCICLK**

$T_A = 0 - 70^{\circ} \text{ C}; V_{DD} = 3.3 \text{ V} + /-5\%, V_{DDL} = 2.5 \text{ V} + /-5\%; C_L = 30 \text{ pF (unless otherwise stated)}$

| PARAMETER                           | SYMBOL                 | CONDITIONS                                       | MIN  | TYP  | MAX | UNITS |

|-------------------------------------|------------------------|--------------------------------------------------|------|------|-----|-------|

| Output High Voltage                 | V <sub>OH1</sub>       | $I_{OH} = -11 \text{ mA}$                        | 2.4  | 3.1  |     | V     |

| Output Low Voltage                  | V <sub>OL1</sub>       | $I_{OL} = 9.4 \text{ mA}$                        |      | 0.17 | 0.4 | V     |

| Output High Current                 | Іон1                   | $V_{OH} = 2.0 \text{ V}$                         |      | -62  | -22 | mA    |

| Output Low Current                  | $I_{OL1}$              | $V_{OL} = 0.8 \text{ V}$                         | 25   | 45   |     | mA    |

| Rise Time <sup>1</sup>              | $t_{r1}$               | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.4 \text{ V}$ |      | 1.5  | 2   | ns    |

| Fall Time <sup>1</sup>              | t <sub>fl</sub>        | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$ |      | 1.6  | 2   | ns    |

| Duty Cycle <sup>1</sup>             | $d_{t1}$               | $V_T = 1.5 \text{ V}$                            | 45   | 50   | 55  | %     |

| Skew <sup>1</sup>                   | $t_{sk1}$              | $V_T = 1.5 \text{ V}$                            |      | 310  | 500 | ps    |

| Jitter, One Sigma <sup>1</sup>      | tj1 <sub>0</sub> 1     | $V_T = 1.5 \text{ V}$                            |      | 11   | 150 | ps    |

| Jitter, Absolute <sup>1</sup>       | tjabs1                 | $V_T = 1.5 \text{ V}$                            | -250 | 45   | 250 | ps    |

| Jitter, Cycle-to-cycle <sup>1</sup> | t <sub>jcyc-cyc1</sub> | $V_T = 1.5 \text{ V}$                            |      | 105  | 500 | ps    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

### **Electrical Characteristics - IOAPIC**

$T_A = 0 - 70^{\circ} \text{ C}; V_{DD} = 3.3 \text{ V} + /-5\%, V_{DDL} = 2.5 \text{ V} + /-5\%; C_L = 20 \text{ pF (unless otherwise stated)}$

| PARAMETER                           | SYMBOL                  | CONDITIONS                                       | MIN  | TYP   | MAX | UNITS |

|-------------------------------------|-------------------------|--------------------------------------------------|------|-------|-----|-------|

| Output High Voltage                 | $V_{\rm OH4B}$          | $I_{OH} = -12 \text{ mA}$                        | 2    | 2.4   |     | V     |

| Output Low Voltage                  | V <sub>OL4B</sub>       | $I_{OL} = 12 \text{ mA}$                         |      | 0.17  | 0.4 | V     |

| Output High Current                 | Іон4в                   | $V_{OH} = 1.7 \text{ V}$                         |      | -61   | -19 | mA    |

| Output Low Current                  | I <sub>OL4B</sub>       | $V_{OL} = 0.7 \text{ V}$                         | 19   | 53    |     | mA    |

| Rise Time <sup>1</sup>              | $T_{r4B}$               | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.0 \text{ V}$ |      | 0.75  | 2.2 | ns    |

| Fall Time <sup>1</sup>              | $T_{\rm f4B}$           | $V_{OH} = 2.0 \text{ V}, V_{OL} = 0.4 \text{ V}$ |      | 0.675 | 2   | ns    |

| Duty Cycle <sup>1</sup>             | D <sub>t4B</sub>        | $V_T = 1.25 \text{ V}$                           | 45   | 49.5  | 55  | %     |

| Jitter, One Sigma <sup>1</sup>      | $T_{j1}$ 04B            | $V_T = 1.25 \text{ V}$                           |      | 26    | 150 | ps    |

| Jitter, Absolute <sup>1</sup>       | Tjabs4B                 | $V_T = 1.25 \text{ V}$                           | -500 | 137   | 500 | ps    |

| Jitter, Cycle-to-cycle <sup>1</sup> | t <sub>jcyc-cyc4B</sub> | $V_T = 1.25 \text{ V}$                           |      | 200   | 500 | ps    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

Electrical Characteristics - REF, 48MHz  $T_A = 0 - 70^{\circ} \text{ C}; \ V_{DD} = 3.3 \ \text{V} + /-5\%, \ V_{DDL} = 2.5 \ \text{V} + /-5\%; \ C_L = 20 \ \text{pF} \ \text{(unless otherwise stated)}$

| PARAMETER                      | SYMBOL             | CONDITIONS                                       | MIN  | TYP  | MAX | UNITS |

|--------------------------------|--------------------|--------------------------------------------------|------|------|-----|-------|

| Output High Voltage            | V <sub>OH5</sub>   | $I_{OH} = -12 \text{ mA}$                        | 2.4  | 2.9  |     | V     |

| Output Low Voltage             | V <sub>OL5</sub>   | $I_{OL} = 10 \text{ mA}$                         |      | 0.33 | 0.4 | V     |

| Output High Current            | I <sub>OH5</sub>   | $V_{OH} = 2.0 \text{ V}$                         |      | -31  | -22 | mA    |

| Output Low Current             | $I_{OL5}$          | $V_{OL} = 0.8 \text{ V}$                         | 16   | 23   |     | mA    |

| Rise Time <sup>1</sup>         | $t_{r5}$           | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.4 \text{ V}$ |      | 1.8  | 4   | ns    |

| Fall Time <sup>1</sup>         | ts                 | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$ |      | 2.1  | 4   | ns    |

| Duty Cycle <sup>1</sup>        | d <sub>t5</sub>    | $V_T = 1.5 \text{ V}$                            | 45   | 52   | 55  | %     |

| Jitter, One Sigma <sup>1</sup> | tj1 <sub>0</sub> 5 | $V_T = 1.5 \text{ V, REF}$                       |      | 85   | 150 | ps    |

| Jitter, Absolute <sup>1</sup>  | tjabs5             | $V_T = 1.5 \text{ V}, \text{REF}$                | -500 | 285  | 500 | ps    |

| Jitter, One Sigma <sup>1</sup> | t <sub>j1o</sub> 5 | $V_T = 1.5 \text{ V}, 48 \text{ MHz}$            |      | 32   | 150 | ps    |

| Jitter, Absolute <sup>1</sup>  | tjabs5             | $V_T = 1.5 \text{ V}, 48 \text{ MHz}$            | -250 | 110  | 250 | ps    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

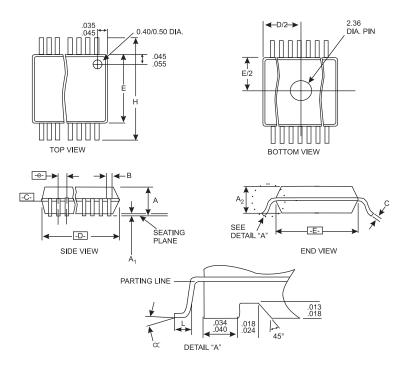

| SYMBOL | COMMON DIMENSIONS |      |       | VARIATIONS | D    |      |      | N  |

|--------|-------------------|------|-------|------------|------|------|------|----|

|        | MIN.              | NOM. | MAX.  |            | MIN. | NOM. | MAX. |    |

| A      | .095              | .101 | .110  | AC         | .620 | .625 | .630 | 48 |

| A1     | .008              | .012 | .016  |            |      |      |      |    |

| A2     | .088              | .090 | .092  |            |      |      |      |    |

| В      | .008              | .010 | .0135 |            |      |      |      |    |

| С      | .005              | -    | .010  |            |      |      |      |    |

| D      | See Variations    |      |       |            |      |      |      |    |

| Е      | .292              | .296 | .299  |            |      |      |      |    |

| e      | 0.025 BSC         |      |       |            |      |      |      |    |

| Н      | .400              | .406 | .410  |            |      |      |      |    |

| h      | .010              | .013 | .016  | 48 Pin     | SSO  | P P  | acka | ae |

| L      | .024              | .032 | .040  | 1 40 1 111 |      |      | uonu | 9~ |

| N      | See Variations    |      |       |            |      |      |      |    |

| ∞      | 0°                | 5°   | 8°    |            |      |      |      |    |

| X      | .085              | .093 | .100  |            |      |      |      |    |

# **Ordering Information**

# ICS9248<u>y</u>F-65