## 4

# **Advanced DMA Controller** for 16-/32-Bit Microcomputer Systems

# **SAB 82258A**

#### **SAB 82258A**

#### 8 MHz

- Fully upward-compatible with SAB 82258 (hardware and software)

- Supports 32-bit fly-by transfers

- 4 independent high-speed DMA channels

- Multiplexer channel operation supporting up to 32 subchannels

- Adaptive on-chip bus interface for direct connection to 16/8-bit processors

- Standalone operation for modular systems

- Programmable bus loading

- Transfer rates up to 20 Mbytes/s (10 MHz system)

#### SAB 82258A-1

#### 10 MHz

- 16 Mbytes addressing range

- 16 Mbytes maximum block size

- Command chaining for automatic processing

- Automatic data chaining (scattering gathering) for flexible data structures

- "On-the-fly" compare, translate and verify operations

- Single and double cycle transfers

- Automatic assembly/disassembly of data

- Memory-based communication scheme with CPU

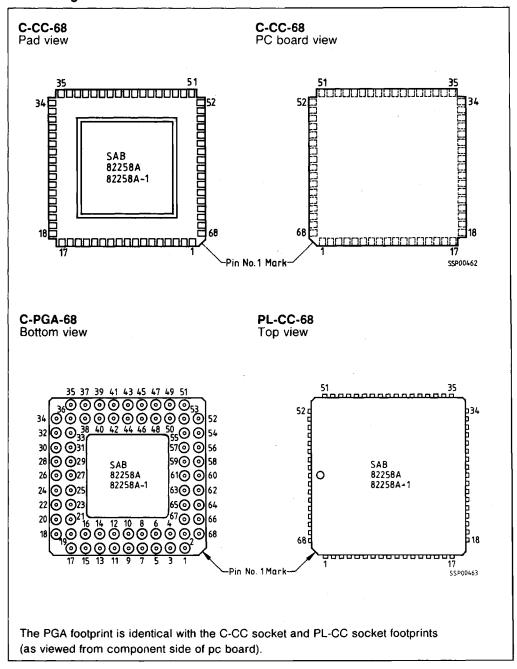

- 3 package types: C-CC-68, C-PGA-68, and PL-CC-68

The SAB 82258A is an advanced DMA (direct memory access) controller especially designed for the 16-bit microprocessors SAB 80286 and SAB 8086/186/88/188. In addition the operation with other processors is supported by the remote mode. The 32-bit fly-by transfer mode supports operation with 32-bit microprocessors (like 80386). The SAB 82258A has 4 independent DMA channels which can transfer data at rates up to 10 Mbytes/second at 10 MHz clock frequency in an SAB 80286 system or up to 5 Mbytes/second at 10 MHz in an SAB 8086/80186 system. Using 32-bit fly-by transfers it can transfer 20 Mbytes/second at 10 MHz. This great bandwidth allows the user to handle very fast data transfers or a large number of concurrent peripherals.

The device is fabricated in advanced +5 V N-channel Siemens MYMOS technology and comes in a 68-pin ceramic leadless chip carrier (C-CC-68), in a 68-pin ceramic pin grid array (C-PGA-68), or in a 68-pin plastic leaded chip carrier (PL-CC-68).

# Modes of Operation, Adaptive Bus Interface

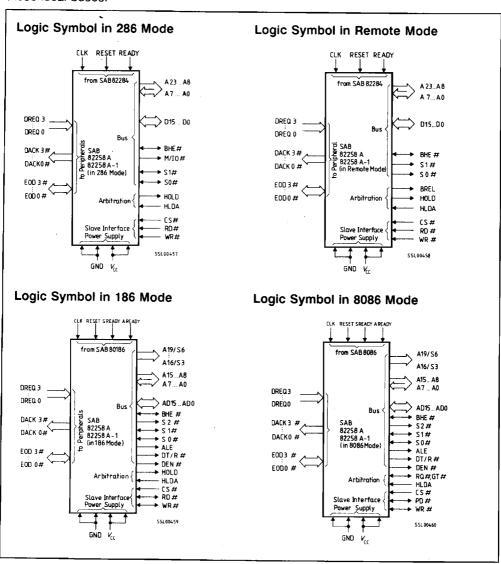

The SAB 82258A has been defined to work with all 16-bit processors linke SAB 80286, SAB 80186/188 and SAB 8086/88 without additional support and interface logic. Hence the local buses of the above processors are different in signals, functions and timings, the SAB 82258A has an adaptive bus interface to meet the different requirements of these local buses.

As a result of this, a bus compatibility with identical timing is attained with the processors SAB 80286, SAB 80186 and SAB 8086. A compatibility with the 8-bit bus versions of these processors, SAB 8088 and SAB 80188, is also guaranteed by defining the physical bus width of the SAB 82258A (per software) as 8 bits. The only difference in operation with SAB 8086 or SAB 80186 is that for SAB 8086 the HOLD pin functions as RQ#'GT# line (if HLDA is held high on reset).

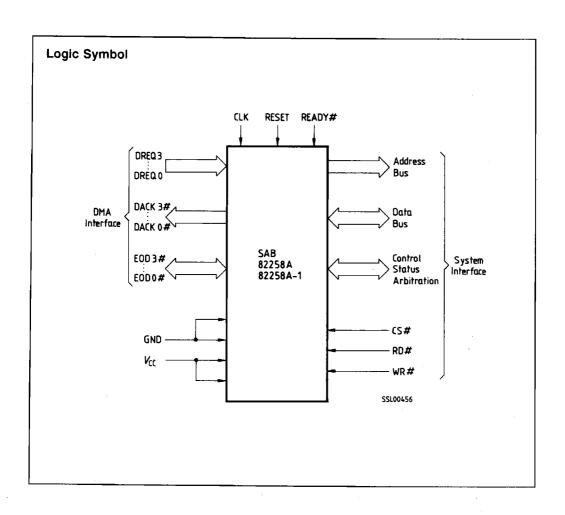

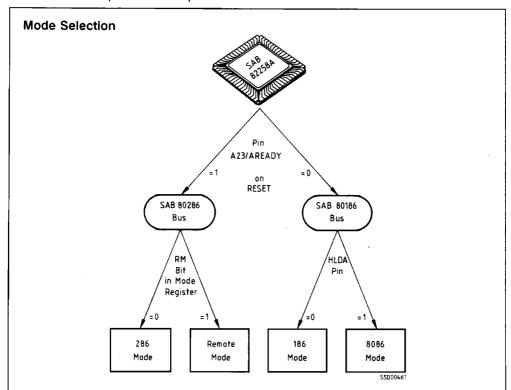

The SAB 82258A can also be operated in remote or standalone mode, in which case it is not coupled directly to a processor. In remote mode, the SAB 82258A can be operated as sole bus master in a multimaster environment. The SAB 82258A is programmed to a specific mode of operation by applying defined logic levels to certain pins during reset and by setting the status of several control bits (see figure below).

Note:

Pin 57 (A21/DT/R# of the SAB 82258A) must be high during reset in order to enable proper operation. This is provided if pin A21 is connected to the SAB 80286's address bus. An internal pullup resistor supports applications where pin 57 is left open.

Pin 57 (A21 or DT/R#) must be high during Reset to enter the desired operating mode. An internal pullup pulls this pin high, if nothing is driving it.

## Pin Configuration

## **Pin Definitions and Functions**

Some pins of the SAB 82258A serve for different purposes according to the different modes of bus operation. The table below summarizes the pinouts of the SAB 82258A in the various modes. A detailed description of the general pin functions as well as the mode-specific pin functions is given in the following sections.

| Pin | 286    | Mode                    | Remo   | te Mode                 | 186/8086 Mode      |                         |  |

|-----|--------|-------------------------|--------|-------------------------|--------------------|-------------------------|--|

|     | Symbol | Input (I)<br>Output (O) | Symbol | Input (I)<br>Output (O) | Symbol             | Input (I)<br>Output (O) |  |

| 16  | HOLD   | 0                       | HOLD   | 0                       | HOLD or<br>RQ#/GT# | O (186)<br>EO (8086)    |  |

| 17  | HLDA   | ı                       | HLDA   | 1                       | HLDA               | 1                       |  |

| 1   | BHE#   | 1/0                     | BHE#   | I/O                     | BHE#               | I/O                     |  |

| 14  | MIO#   | 0                       | BREL   | 0                       | S2#                | 0                       |  |

| 11  | S1#    | I/O                     | S1#    | 0                       | S1#                | 10                      |  |

| 13  | S0#    | I/O                     | S0#    | 0                       | S0#                | I.O                     |  |

| 8   | CS#    | 1                       | CS#    | 1                       | CS#                | 1                       |  |

| 2   | RD#    | 1                       | RD#    | ı                       | RD#                | 10                      |  |

| 3   | WR#    | 1                       | WR#    | 1                       | WR#                | 1.0                     |  |

| 10  | READY# | 1                       | READY# | I                       | SREADY             | 1                       |  |

| 59  | A23    | 0                       | A23    | 0                       | AREADY             | 1                       |  |

| 58  | A22    | 0                       | A22    | 0                       | ALE                | 0                       |  |

| 57  | A21    | 0                       | A21    | 0                       | DT R#              | 0                       |  |

| 56  | A20    | 0                       | A20    | 0                       | DEN#               | 0                       |  |

| 55  | A19    | 0                       | A19    | 0                       | A19 S6             | 0                       |  |

| 54  | A18    | 0                       | A18    | 0                       | A18 S5             | 0                       |  |

| 53  | A17    | 0                       | A17    | 0                       | A17 S4             | 0                       |  |

| 52  | A16    | 0                       | A16    | 0                       | A16 S3             | 0                       |  |

| 51  | A15    | 0                       | A15    | 0                       | A15                | 0                       |  |

| 50  | A14    | 0                       | A14    | 0                       | A14                | 0                       |  |

| 49  | A13    | 0                       | A13    | 0                       | A13                | 0                       |  |

| 48  | A12    | 0                       | A12    | 0                       | A12                | 0                       |  |

| 47  | A11    | 0                       | A11    | 0                       | A11                | 0                       |  |

| 46  | A10    | .0                      | A10    | 0                       | A10                | 0                       |  |

| 45  | A9     | 0                       | A9     | 0                       | A9                 | 0                       |  |

| 44  | A8     | 0                       | A8     | 0                       | A8                 | 0                       |  |

| 42  | A7     | I.O                     | A7     | 10                      | <b>A</b> 7         | 1.0                     |  |

| 41  | A6     | I/O                     | A6     | 10                      | A6                 | 10                      |  |

| 40  | A5     | I/O                     | A5     | 10                      | A5                 | 1.0                     |  |

# Pin Definitions and Functions (cont'd)

| Pin   | 286             | Mode                    | Remo            | te Mode                 | 186/8086 Mode   |                         |  |

|-------|-----------------|-------------------------|-----------------|-------------------------|-----------------|-------------------------|--|

|       | Symbol          | Input (I)<br>Output (O) | Symbol          | Input (I)<br>Output (O) | Symbol          | Input (I)<br>Output (O) |  |

| 39    | A4              | 1:0                     | A4              | 1/0                     | A4              | 10                      |  |

| 38    | A3              | 1.0                     | A3              | 10                      | A3              | 10                      |  |

| 37    | A2              | I.O                     | A2              | 10                      | A2 I            | 10                      |  |

| 36    | A1              | I/O                     | A1              | 1/0                     | A1              | ΙO                      |  |

| 35    | A0              | I/O                     | A0              | I/O                     | AO              | I/O                     |  |

| 18    | D15             | I/O                     | D15             | 1/0                     | AD15            | 1/0                     |  |

| 20    | D14             | I/O                     | D14             | 1/0                     | AD14            | I/O                     |  |

| 22    | D13             | 1/0                     | D13             | 1/0                     | AD13            | 1/0                     |  |

| 24    | D12 .           | 1/0                     | D12             | 1/0                     | AD12            | I/O                     |  |

| 27    | D11             | I/O                     | D11             | 1/0                     | AD11            | 1/0                     |  |

| 29    | D10             | 1/0                     | D10             | I/O                     | AD10            | 1/0                     |  |

| .31   | D9              | I/O                     | D9              | I/O                     | AD9             | I/O                     |  |

| 33    | D8              | I/O                     | D8              | 1/0                     | AD8             | 1/0                     |  |

| 19    | D7              | 1/0                     | D7              | I/O                     | AD7             | I/O                     |  |

| 21    | D6              | 1/0                     | D6              | 1/0                     | AD6             | 1/0                     |  |

| 23    | D5              | I/O                     | D5              | 1/0                     | AD5             | I/O                     |  |

| 25    | D4              | 1/0                     | D4              | I/O                     | AD4             | I/O                     |  |

| 28    | D3              | 1/0                     | D3              | I/O                     | AD3             | I/O                     |  |

| 30    | D2              | I/O                     | D2              | 1/0                     | AD2             | I/O                     |  |

| 32    | D1              | 1/0                     | D1              | I/O                     | AD1             | 1/0                     |  |

| 34    | D0              | I/O                     | D0              | 1/0                     | AD0 I/O         |                         |  |

| 7     | DREQ0           | 1                       | DREQ0           | 1                       | DREQ0           | 1                       |  |

| 6     | DREQ1           | 1                       | DREQ1           | Ti .                    | DREQ1           | I                       |  |

| 5     | DREQ2           | 1                       | DREQ2           | 1                       | DREQ2           | 1                       |  |

| 4     | DREQ3           | 1                       | DREQ3           | 1                       | DREQ3           | i i                     |  |

| 61    | DACK0#          | 0                       | DACK0#          | 0                       | DACK0#          | 0                       |  |

| 62    | DACK1#          | 0                       | DACK1#          | 0                       | DACK1#          | 0                       |  |

| 63    | DACK2#          | 0                       | DACK2#          | 0                       | DACK2#          | 0                       |  |

| 64    | DACK3#          | 0                       | DACK3#          | 0                       | DACK3#          | 0                       |  |

| 65    | EOD0#           | 1/0                     | EOD0#           | 1/0                     | EOD0#           | 1/0                     |  |

| 66    | EOD1#           | 1/0                     | EOD1#           | 1/0                     | EOD1#           | 1/0                     |  |

| 67    | EOD2#           | 1/0                     | EOD2#           | I/O                     | EOD2#           | I/O                     |  |

| 68    | EOD3#           | 1/0                     | EOD3#           | 1/0                     | EOD3#           | I/O                     |  |

| 15    | RESET           | 1                       | RESET           | 1                       | RESET           | 1                       |  |

| 12    | CLK             | i i                     | CLK             | 1                       | CLK             | 1                       |  |

| 9,43  | GND             | _                       | GND             | _                       | GND             | _                       |  |

| 26,60 | V <sub>CC</sub> | _                       | V <sub>CC</sub> | 1-                      | V <sub>CC</sub> | _                       |  |

# Pin Definitions for All Operating Modes

| Symbol          | Pin | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                |    |                                                  |  |

|-----------------|-----|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--------------------------------------------------|--|

| ВНЕ#            | 1   | 1/0                     | BUS HIGH ENABLE This active low input indicates transfer of data of the upper byte of the data bus, D15 to D8. Eigh bit oriented devices assigned to the upper byte the data bus would normally use BHE# to condition chip select functions. BHE# floats to tristate off when the SAB 82258A does not own the bus BHE# and A0 encodings |    |                                                  |  |

|                 |     |                         | BHE#                                                                                                                                                                                                                                                                                                                                    | A0 | Function                                         |  |

|                 |     |                         | 0                                                                                                                                                                                                                                                                                                                                       | 0  | Word transfer (D15-D8)                           |  |

|                 |     |                         | 0                                                                                                                                                                                                                                                                                                                                       | 1  | Byte transfer on upper half of data bus (D15-D8) |  |

|                 |     |                         | 1                                                                                                                                                                                                                                                                                                                                       | 0  | Byte transfer on lower half of data bus (D7-D0)  |  |

|                 |     |                         | 1                                                                                                                                                                                                                                                                                                                                       | 1  | Odd-addressed byte on 8-bit bus (D7-D0)          |  |

| RD#             | 2   | I                       | READ This active low input in conjunction with chip select enables reading the SAB 82258A register which is addressed by the address lines A7 to A0. This signal can be asynchronous to the SAB 82258A clock.                                                                                                                           |    |                                                  |  |

| WR#             | 3   | 1                       | WRITE This active low input in conjunction with chip select enables writing into the SAB 82258A registers which is addressed by the address lines A7 to A0. This signal can be asynchronous to the SAB 82258A clock.                                                                                                                    |    |                                                  |  |

| DREQ0-<br>DREQ3 | 4-7 | 1                       | DMA REQUEST (0 TO 3) These active high inputs are used for synchronized DMA transfers. DREQ3 has the meaning of I/O request (IOREQ) if channel 3 is a multiplexer channel. These signals can be asynchronous to the SAB 82258A clock.                                                                                                   |    |                                                  |  |

# Pin Definitions for All Operating Modes (cont'd)

| Symbol   | Pin    | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|--------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS#      | 8      | 1                       | CHIP SELECT This active low input enables the access of a processor to SAB 82258A registers. This access is additionally controlled either by bus status signals or by the read or write command signals. Chip select can be asynchronous to the SAB 82258A clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

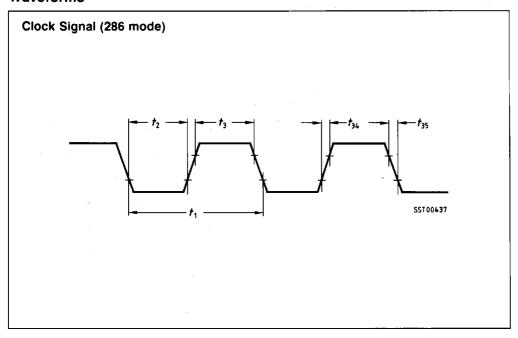

| CLK      | 12     |                         | CLOCK This input provides the fundamental timing. In 286 mode and remote mode it must be two times the system clock. It can be directly connected to the SAB 82284 CLK output. It is divided by two to generate the SAB 82258A internal clock. The onchip divide-by-two circuitry can be synchronized to the external clock generator by a low-to-high transition on the RESET input, or by the first high-to-low transition on the status inputs SO# or S1# after reset. In 186/8086 mode no internal prescaling is done.                                                                                                                                                                                                              |

| S0#, S1# | 11, 13 | I/O                     | BUS STATUS LINES (0, 1) These signals control the support circuits. The beginning of a bus cycle is indicated by S1# or S0# or both going active. The termination of a bus cycle is indicated by all status signals going inactive in 186 mode or bus ready signal (READY#) going active in 286 mode. The type of bus cycle is indicated by S0#, S1# and S2# (in 186 mode) or M/IO# (in 286 mode). S2# and M/IO# have the same meaning but in 186 mode the S2# signal can be active only when at least one of S1# or S0# is active, whereas in 286 mode the M/IO# signal is valid with the address on the address lines. The SAB 82258A can generate the following bus cycles by activating the status signals (and M/IO# in 286 mode): |

# Pin Definitions for All Operating Modes (cont'd)

| Symbol              | Pin    | Input (I)<br>Output (O) | Function                          |                                   |                                  |                                                                                                                                                      |  |

|---------------------|--------|-------------------------|-----------------------------------|-----------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| S0#,S1#<br>(cont'd) | 11, 13 | 10                      | M IO#<br>or S2#                   | S1#                               | S0#                              | Cycle Type                                                                                                                                           |  |

|                     |        |                         | 0                                 | 0                                 | 0                                | Read I O-vector (for multiplexer channel)                                                                                                            |  |

|                     |        |                         | 0                                 | 0                                 | 1                                | Read from I.O space                                                                                                                                  |  |

|                     |        |                         | 0                                 | 1                                 | 0                                | Write into I/O space                                                                                                                                 |  |

|                     |        |                         | 0                                 | 1                                 | 1                                | No bus cycle, does not occur in 186 mode                                                                                                             |  |

|                     |        |                         | 1                                 | 0                                 | 0                                | Does not occur                                                                                                                                       |  |

|                     |        |                         | 1                                 | 0                                 | 1                                | Read from memory space                                                                                                                               |  |

|                     |        |                         | 1                                 | 1                                 | 0                                | Write into memory space                                                                                                                              |  |

|                     |        |                         | 1                                 | .1                                | 1                                | No bus cycle                                                                                                                                         |  |

|                     |        |                         | local bus<br>detection<br>SAB 822 | s the<br>n of s<br>258A.<br>nd CS | status<br>ynchi<br>The<br>5# sig | 258A is not the master of the s signals are used as inputs for ronous accesses to the following table shows the bus mals and their interpretation by |  |

|                     |        |                         | CS#                               | S1#                               | S0#                              | Description                                                                                                                                          |  |

|                     |        |                         | 1                                 | Х                                 | X                                | SAB 82258A is not selected (no action)                                                                                                               |  |

|                     |        |                         | 0                                 | 0                                 | 0                                | No SAB 82258A access (no action)                                                                                                                     |  |

|                     |        |                         | 0                                 | 0                                 | 1                                | Read from an<br>SAB 82258A register                                                                                                                  |  |

|                     |        |                         | 0                                 | 1                                 | 0                                | Write into an SAB 82258A register                                                                                                                    |  |

|                     |        |                         | 0                                 | 1                                 | -1                               | No bus cycle <sup>1)</sup>                                                                                                                           |  |

SAB 82258A is selected but no synchronous access is activated. In this case the SAB 82258A monitors RD# and WR# signals for detection of an asynchronous access.

# Pin Definitions for All Operating Modes (cont'd)

| Symbol                  | Pin    | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------|--------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET                   | 15     | l                       | SYSTEM RESET An activation of the reset signal forces the SAB 82258A to the initial state. The reset signal must be synchronous to CLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DACK0#-<br>DACK3#       | 61-64  | 0                       | DMA ACKNOWLEDGE (0 TO 3) These active low inputs acknowledge the requests on the related DREQn signals. They are activated when the requested transfer(s) is (are) performed. If the channel 3 is a multiplexer channel the signal DACK3# has the meaning of I/O acknowledge (IOACK#).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| EOD0#-<br>EOD3#         | 65-68  | 10                      | END OF DMA (0 TO 3)  These lines are implemented as open drain output drivers with a high impedance pullup resistor and thus can be used as bidirectional lines.  As outputs the lines are activated for two system clock cycles at the end of the DMA transfer of the corresponding channel (if enabled) or they are activated under program control (EOD output or interrupt output).  If the lines are held internally high but forced to low by external circuitry, they act as "End of DMA" inputs. The current transfer is aborted and the SAB 82258A continues with the next command. Additionally, a special function is possible with the EOD2# pin: this pin can also be used as common interrupt signal for all 4 channels. In this mode this line is not an open drain output but a pushpull output (output only). The other EOD# pins may be used as EOD# outputs inputs as described above. |

| $\overline{V_{\rm CC}}$ | 26, 60 |                         | POWER SUPPLY (+5 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GND                     | 9, 43  | †                       | GROUND (0 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### Pin Definitions for 286 Mode and Remote Mode

In 286 mode the SAB 82258A bus signals and bus timings are the same as for the SAB 80286 processor. Additional features of the SAB 82258A require a slight change in pin definitions. The processor can access internal registers of the SAB 82258A. Therefore the bus signals must support these accesses. This means that some of the bus control signals must be bidirectional and some additional bus control signals are necessary. All additional pins and their functions are listed below.

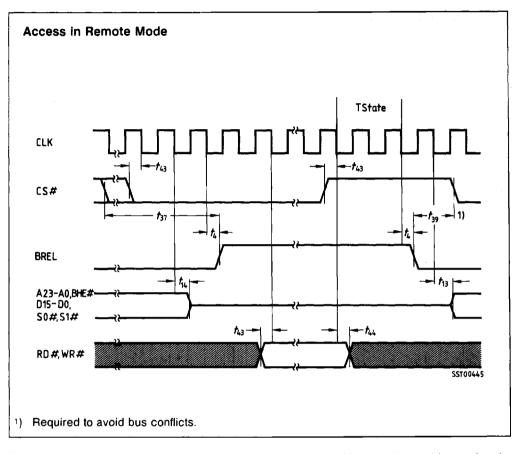

In **remote mode** most of the bus signals are the same as in 286 mode. Pin 14 (M/IO#) serves as BREL output. The HOLD/HLDA arbitration in remote mode is used only for system bus accesses, the resident bus is accessed directly.

The CS# input additionally requests access to the local bus of the SAB 82258A. These accesses are enabled through the BREL output after the SAB 82258A has released the bus.

#### Pin Configuration in 286 Mode and Remote Mode PC Board View - As viewed Component Pad View - As viewed from underside of component from the component side of when mounted on the board the pc board (Example: C-CC-68) (Example:PL-CC-68) D 8 A 17 508 D 1 D9 A 19 509 D 2 A 20 Þ02 D 10 A 21 DD 10 D 3 A 22 **2**03 D 11 A 23 DD 11 82258A 82258A $V_{CC}$ $v_{cc}$ þγα D 4 BACK 0.2 DACKO#F DO 4 D 12 DACK 1# DACK1#E DD 12 D5 DACK 2# DACK2#1 hn s D 13 DACK 3# DACK3#1 **D**D 13 006 0014 007 06 EOD 0# FOD 0#1 D 14 EOD 1# EOD 1#0 EOD 2# FOD 2#1 18 HO 15 FOD 3#H #(BREL) RESET HOLD HLDA

# Pin Definitions for 286 Mode and Remote Mode (cont'd)

| Symbol | Pin                    | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                  |

|--------|------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| READY# | 10                     | 1                       | BUS READY This active low input terminates a bus cycle. Bus cycles are extended without limit until terminated by READY# low. READY# is a synchronous input requiring setup and hold times relative to the system clock to be met for correct operation.                                                  |

| M/IO#  | 14<br>(286 mode)       | 0                       | Memory / I/O SELECT In 286 mode, pin 14 is used to distinguish between memory and I/O space addresses.                                                                                                                                                                                                    |

| BREL   | 14<br>(remote<br>mode) | 0                       | BUS RELEASE In remote mode pin 14 is used to indicate when the SAB 82258A has released the control of the local bus.                                                                                                                                                                                      |

| HOLD   | 16                     | 0                       | BUS HOLD REQUEST  This active high output indicates a request for control of the local bus (286 mode) or the system bus (remote mode). When the SAB 82258A relinquishes the bus it drops the HOLD output. HOLD is connected to the bus arbiter in remote mode.                                            |

| HLDA   | 17                     |                         | BUS HOLD ACKNOWLEDGE This active high input indicates that the SAB 82258A can acquire the control of the bus. When it goes low SAB 82258A must relinquish the bus at the end of its current cycle. HLDA can be asynchronous to the SAB 82258A clock. HLDA is connected to the bus arbiter in remote mode. |

| D0-D15 | 18-25, 27-34           | I/O                     | DATA BUS (0 TO 15) This is the bidirectional 16-bit data bus. For use with an 8-bit bus, only the lower 8 data lines D7-D0 are relevant.                                                                                                                                                                  |

| A0-A7  | 35-42                  | I/O                     | ADDRESS BUS (0 TO 7) The lower 8 address lines for DMA transfers. They are also used to input the register address when the processor accesses an SAB 82258A register.                                                                                                                                    |

| A8-A23 | 44-59                  | 0                       | ADDRESS BUS (8 TO 23) Higher address outputs.                                                                                                                                                                                                                                                             |

## Pin Definitions for 186 Mode and 8086 Mode

In 186 mode and 8086 mode the SAB 82258A multiplexes the address with data and additional status lines.

Pins A0 to A15 retain their original function while pins A20 to A23 serve for different purposes (not used for address in 186 8086 mode).

The RD# and WR# lines are additionally used as outputs in 186 8086 mode to support minimum mode systems.

Note that the HLDA input can be used to force the SAB 82258A off the bus in 8086 mode, even though the arbitration is done via the RQ# GT# line!

#### Pin Configuration in 186 Mode and 8086 Mode Component Pad View - As viewed PC Board View - As viewed from underside of component from the component side of when mounted on the board the pc board (Example: C-CC-68) (Example: PL-CC-68) AD 0 34 A 16/S3 A 16 / S3 C 52 AD8 A 17/54 A17/54E B DAC AD 8 AD 9 AD 2 AD 10 AD 3 AD 11 Vcc AD 4 AD 12 AD 12 AD 12 AD 12 AD 12 AD 15 AD 15 AD 16 AD 17 AD 18 A A 18/55 4 18/SS F A 19/56 A19/56 F DFN# DEN# C DT/R# AD 10 ALE ALF AREADY AREADY [ DAD 11 82258A 8225 A DACK 0# HAD 4 DACK1#C D A D 12 AD 5 AD 13 DACK 2# DACK 3# DACK3#D D A D 13 AD 6 AD 14 AD 7 FOD 6# EOD 1# EOD 1#0 D A D 14 EOD 2# EOD 2#0 DAD 7 68 EOD 3# 18 FIAD 15 EOD 3#1 WKR# COWKR# COWKR# COWKR# COWKR# COWKR 10 COWKR 10 COWKR COW 10LD(RQ#/61# SSP00465

# Pin Definitions for 186 Mode and 8086 Mode (cont'd)

| Symbol          | Pin            | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                      |

|-----------------|----------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ALE             | 58             | 0                       | ADDRESS LATCH ENABLE This active high output provides a strobe signal to separate the address information on the multiplexed AD lines.                                                                                                        |

| DEN#            | 56             | 0                       | DATA ENABLE This active low output enables the data transceivers.                                                                                                                                                                             |

| DT/R#           | 57             | 0                       | DATA TRANSMIT/RECEIVE This signal controls the direction of the data transceivers. When low, data is transferred to the SAB 82258A, when high, the ADMA places data onto the data bus.                                                        |

| S2#             | 14             | 0                       | STATUS LINE 2<br>Signal as for SAB 186/8086/88 processors<br>(see also S1#, S0# description in 286 mode).                                                                                                                                     |

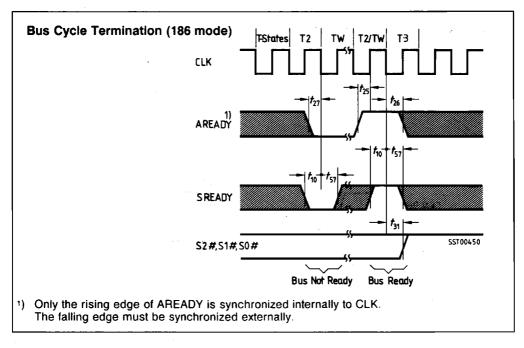

| AREADY          | 59             |                         | ASYNCHRONOUS READY The rising edge of this signal is internally synchronized, the falling edge must be synchronous to CLK. During reset this signal must be low to enter 186 mode.                                                            |

| SREADY          | 10             |                         | SYNCHRONOUS READY This signal must be synchronized externally. The use of this pin permits a relaxed system-timing specification by eliminating the clock phase which is required for resolving the signal level when using the AREADY input. |

| AD0-AD15        | 18-25<br>27-34 | 1/0                     | ADDRESS/DATA BUS (0 to 15) Lower address and data information is multiplexed on pin AD0 to AD15.                                                                                                                                              |

| A0-A7<br>A8-A15 | 35-42<br>44-51 | I/O<br>O                | ADDRESS BUS (0 to 15) Additionally the demultiplexed address information is available on address pin A0 to A15.                                                                                                                               |

# Pin Definitions for 186 Mode and 8086 Mode (cont'd)

| Symbol            | Pin               | Input (I)<br>Output (O) | Function                                                                                                                                                                                                                                                                                                                         |

|-------------------|-------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A16/S3-<br>A19/S6 | 52–55             | 0                       | ADDRESS BUS (16 TO 19)/ STATUS LINES (3 TO 6) The higher address bits are multiplexed with additional status information.                                                                                                                                                                                                        |

| HLDA              | 17                |                         | BUS HOLD ACKNOWLEDGE This active high input indicates that the SAB 82258A can acquire the control of the bus. When it goes low the SAB 82258A must relinquish the bus at the end of its current bus cycle. HLDA can be asynchronous to the SAB 82258A clock. In 8086 mode, HLDA can be used to force the SAB 82258A off the bus. |

| HOLD              | 16<br>(186 mode)  | 0                       | BUS HOLD REQUEST  This active high output indicates a request for control of the bus. When the SAB 82258A relinquishes the bus, it drops the HOLD output.                                                                                                                                                                        |

| RQ#/<br>GT#       | 16<br>(8086 mode) | 1/0                     | REQUEST/GRANT In 8086 mode the HOLD output acts as RQ#/GT# line. The RQ#/GT# protocol implements a one-line communication dialog required to arbitrate the use of the system bus normally done via HOLD/HLDA. The RQ#/GT# signal is active low and has an internal pullup resistor.                                              |

## **Functional Description**

#### General

The SAB 82258A is an advanced general-purpose DMA controller especially designed for efficient highspeed data transfers on an SAB 80286 bus as well as on an SAB 80186/188 or SAB 8086/88 bus.

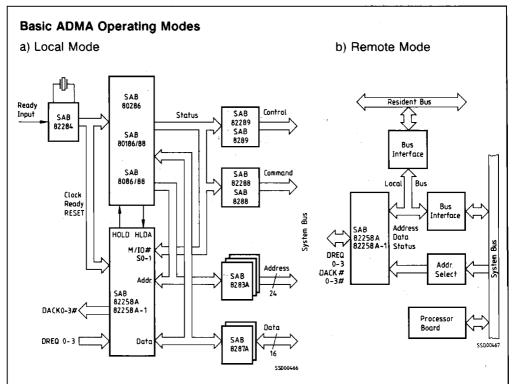

It supports two basic operating modes:

- local mode (tightly coupled to a processor) and

- remote mode (loosely coupled to a processor).

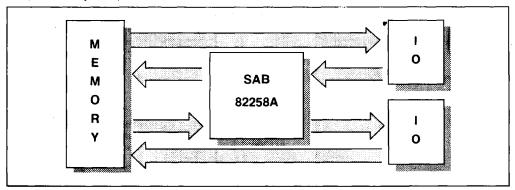

In the first case the SAB 82258A is directly coupled to the CPU and uses the same system support/control devices as the CPU (see figure below). This mode is possible with the above-mentioned processors.

As a second basic operating mode remote (standalone) mode is supported (see figure below). Here the SAB 82258A has its own sets of bus interface circuits and thus can utilize its own local bus. This allows the DMA controller to work in parallel with the main CPU and therefore overall system performance can be increased. Besides, this mode is very useful for the design of modular systems and allows connecting the SAB 82258A to any other processor via the system bus independent of the processor's local bus.

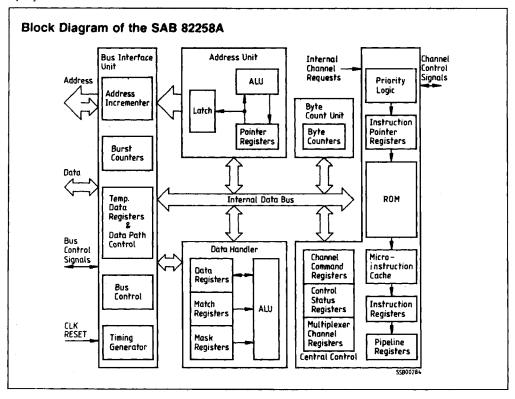

The SAB 82258A has four independent DMA channels that can transfer up to 10 Mbytes/s in single cycle mode (2 clocks/transfer). In 2-cycle transfer mode the maximum rate is 5 Mbytes/s. Switching between channels induces no time penalty. Thus the overall maximum transfer rate of 10 Mbytes s is also valid for multiple channel operation.

This fast operation is possible because of the pipelined architecture of the SAB 82258A which allows the different functional units to work in parallel. The maximum transfer rate can be doubled to 20 Mbytes s (in a 10 MHz system), if the ADMA executes 32-bit fly-by transfers.

The ADMA supports two address spaces, memory space and I O space, each with a maximum address range of 16 Mbytes. In addition, the maximum block length (byte count) is also 16 Mbytes to support applications where large blocks of data have to be transferred (e.g. graphics).

As source or as destination, four parameters can be selected independently:

- address space (memory or I/O)

- logical bus width (same as physical bus width or 8 bits on a 16-bit physical bus)

and

- transfer direction (increasing, decreasing, fixed pointer or constant value).

If the physical bus width of source or destination differs from the logical bus width, an automatic byte word assembly (word byte disassembly) takes place. The same is true, if the logical bus widths of source and destination are not identical.

Transfers between different address spaces can be performed within one or two cycles, transfers within one address space can be performed only in two cycles.

The transfers can be executed free running or externally synchronized via DREQ where source or destination synchronization is possible.

In summary, this very symmetrical operation of the SAB 82258A gives the user a great amount of design flexibility.

#### Adaptive Bus Interface

As shown in the figure on page 4, the SAB 82258A bus interface has two basic timing modes: the 286 mode and the 186 mode. In 286 mode the SAB 82258A is directly coupled to an SAB 80286, in 186 mode to an SAB 80186 or SAB 80188. For each of these two modes a slightly different variation exists:

- For the 286 mode the variation is the remote mode, where the ADMA operates as a bus master on the system bus without being directly coupled to a processor. In this mode the SAB 82258A can utilize its own local bus and the communication with the main processor is done via the system bus. To enable access to ADMA registers by the main processor, the SAB 82258A must release its local bus. This "local bus arbitration" in remote mode is done via the CS# and BREL lines.

- For the 186 mode the variation is the 8086 mode, where the SAB 82258A supports

the RQ#/GT# protocol and thus can be directly coupled to an SAB 8086 or SAB 8088.

## **Memory-Based Communication**

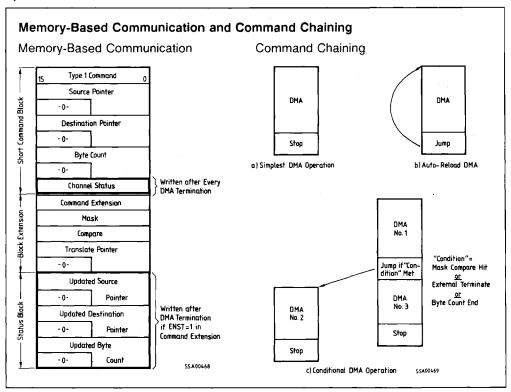

The normal communication between the ADMA and the processor is memory-based. This means that all necessary data for a transfer is contained in a command block in memory accessible for CPU and SAB 82258A (see figure below). To start the transfer the CPU loads one of the command pointer registers of the SAB 82258A with the address of the command block and then issues a "start channel command". Getting the command the SAB 82258A loads the entire command block from memory into its on-chip channel registers and executes it. On completing the operation, channel status information is written back by the SAB 82258A into the channel status word contained in the command block in memory.

If desired, the actual contents of the channel registers, i.e. source pointer, destination pointer and byte count it transferred to the channel status block. The channel status block immediately follows the command block in memory (see figure below).

#### Command Chaining

Command blocks for any channel can be chained for sequential execution (see figure). When the SAB 82258A has completed the execution of a command, it automatically increments the command pointer and starts to fetch and execute the next command block until a stop command is found. As a result a chain of command blocks can be executed by the ADMA without any CPU intervention. Due to conditional and unconditional STOP and JUMP commands, quite complex sequences of DMA can be executed by the SAB 82258A.

#### **Data Chaining**

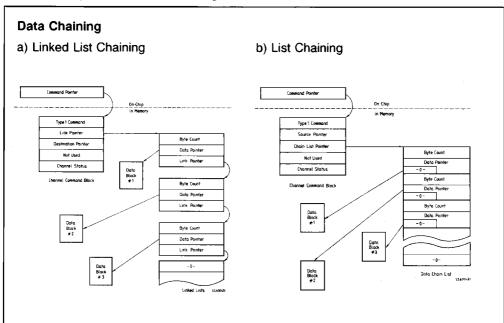

Data chaining allows an automatic, dynamic linking of data blocks scattered in memory. There are two types: list and linked-list data chaining.

If for a DMA the source blocks are to be dynamically linked during DMA, it is called source chaining and the effect is that of gathering data blocks and sending them out effectively as one block.

If one source block is dynamically broken up into multiple destination blocks, it is called destination chaining. This results in scattering of a block.

This dynamic linking and unlinking of data blocks makes the logical sequencing of data independent of its physical sequencing in memory.

In the case of linked list chaining (see figure a) each data block has a descriptor containing information on position of the data block in memory, length of the data block and a pointer to the next descriptor.

During data transfer the data block 1 is sent out first, then 2 and so on till a "0" is encountered in the byte count field.

The second type of data chaining is list chaining (see figure b).

Unlike linked list chaining, here the data block descriptors are continuous in a block and thus determine the sequence of data blocks. The flexibility lost in terms of predefined sequence is gained in terms of linking time.

## "On-The-Fly" Operations

A normal DMA controller blindly transfers data from source to destination without looking at the data. In case of the ADMA on-the-fly operations are executed during the DMA transfer and allow inspection and or operation on the transferred data. There are three possible on-the-fly operations:

- mask/compare

- translate and

- verify

During a mask compare operation each byte word transferred is compared to a given pattern. One or more bits can be masked and thus do not contribute to the result of the compare operation. The result can be used by subsequent conditional stop or jump operations.

For translate operation the byte (no word possible) that is fetched from source is added to a translate pointer to build the effective source pointer. The byte pointed to by this pointer is then fetched and sent out to the destination. Of course, a mask compare operation is possible on the byte sent out.

The verify operation is a type of block compare operation to compare each byte/word of data read from a peripheral with the one in a data block in the memory. There are three options:

- Verify with no termination on mismatch (2-cycle transfer only)

- 2. Verify with termination on mismatch (2-cycle transfer only)

- Verify and save (single cycle transfer only).

Here an actual transfer with compare takes place.

The transfer is not stopped on mismatch.

Note:

Verify and save operation and mask compare operation can be used during 32-bit fly-by transfer, but can check a maximum of 16 bits, not a complete double word.

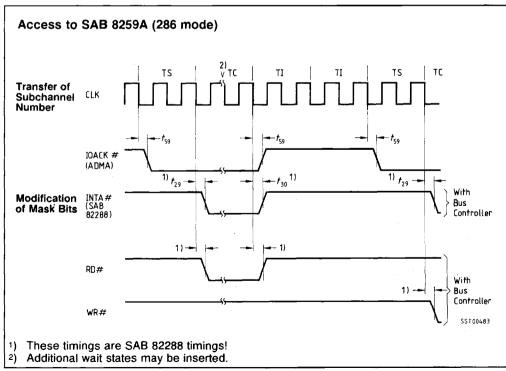

## Multiplexer Channel

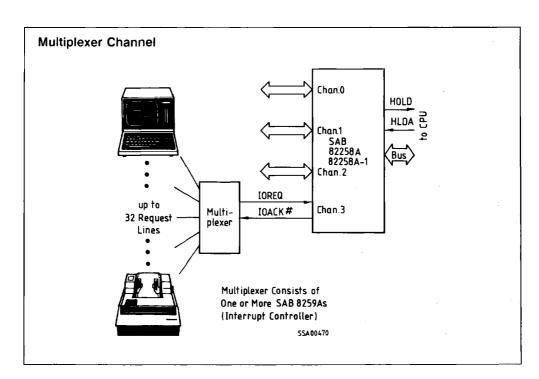

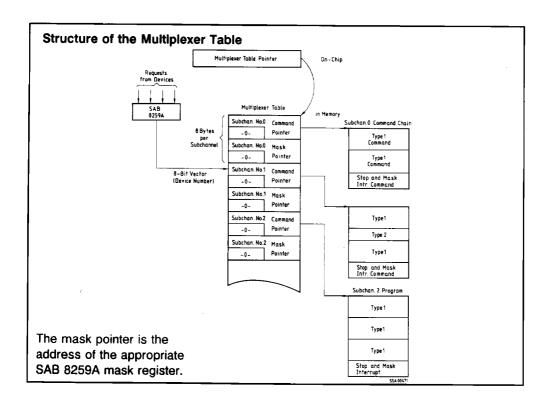

When programmed to multiplexer mode, channel 3 (supported by a multiplexer logic) can be used to service up to 32 subchannel request lines (see figures below). Thus it is ideally suited to service a large number of comparatively slow equipment like CRT terminals, line printers, serial links, etc. Since multiple subchannels are processed with the resource of one DMA channel, the overhead of subchannel switching, of course, decreases the total effective throughput on the multiplexer channel.

To allow efficient control even of the subchannels, a separate command pointer for each subchannel is provided within the multiplexer table. Thus an individual subchannel program (command chain) can be used for each subchannel.

Different transfer modes are provided for subchannels:

### Byte/word multiplex:

One byte or word is transferred per request. Updating the pointers is done within the actual command block.

#### Single transfer:

Similar to byte-word multiplex, but with execution of command chaining after each transfer.

## Block multiplex:

I/O request initiates execution of a complete command block, i.e. the complete data block specified is transferred. This allows maximum transfer rates (2-cycle transfers) also for subchannels.

A type 2 command in a subchannel program can issue an interrupt, whereby the multiplexer channel interrupt vector register (MIVR) provides the corresponding subchannel number for the CPU.

A subchannel program is terminated by a stop and mask command which automatically masks the corresponding request line within the SAB 8259A thus blocking this subchannel until it is enabled again by the CPU.

### 32-Bit Fly-by Transfers

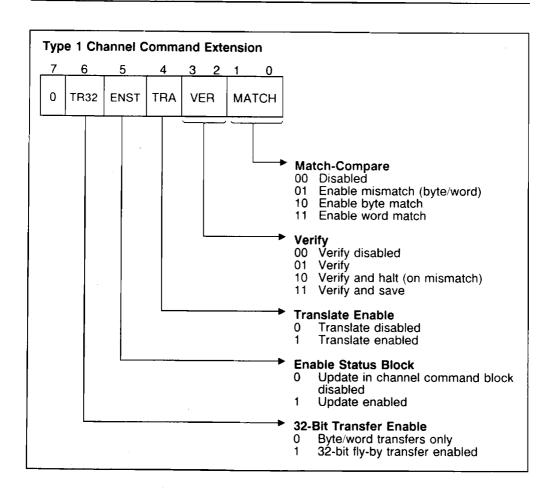

The 32-bit transfer enable bit TR32 (bit 6 of the channel command register extension CCRX) allows the address pointers and byte counters to be modified not only by 1 or 2, but also by 4 in order to count 32-bit double words. Therefore, the SAB 82258A can control 32-bit transfers in single cycle mode. In this mode, data flows past the DMA controller rather than through it. All features that use the data assembly registers (two-cycle mode, compare, verify, etc.), should be avoided, because the 16-bit data port can access only one half of a 32-bit data bus.

Addresses and byte counts must be aligned to double-word boundaries (i.e. multiples of 4) in order to ensure proper operation. Also the effective transfer width (logical and physical bus width) must be programmed to 16 bits. As the external control signals do not allow to distinguish 32-bit fly-by transfers from 16-bit transfers, the transfer mode of a channel must be predefined.

Note:

If the SAB 82258A is to operate in a system with a true 32-bit address bus, the upper address byte (A31 to A24) must be provided by an external page register, as the ADMA's address bus is still 24 bits wide.

## 4

## Operating the SAB 82258A

#### Reset

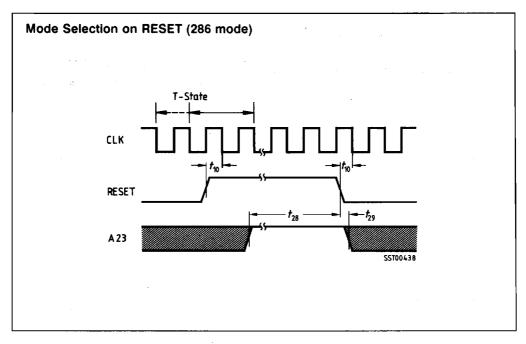

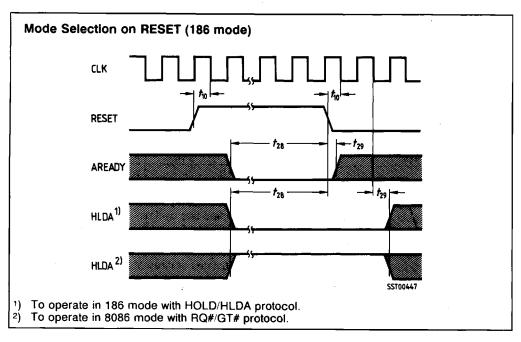

When activating the reset input, the SAB 82258A is forced into its initial state. All channels and bus activities are stopped, tristate lines are tristated and the others enter the inactive state. While the reset input is active, pin 57 must be held high and lines A23 AREADY and HLDA must be forced to the appropriate levels to select the desired bus interface mode (see figures on page 4, 49 and 62).

After deactivating reset the inactive state is maintained, in addition the state of the SAB 82258A registers is as follows:

- general mode register, general burst register, general delay register, general status register and the four channel status registers are set to zero,

- the vector-not-valid bit of the multiplexer interrupt vector register is set to 1,

- all other registers and bits are undefined.

Note: The general mode register (GMR) should be loaded first to select the mode of operation before any other activity is started on the ADMA.

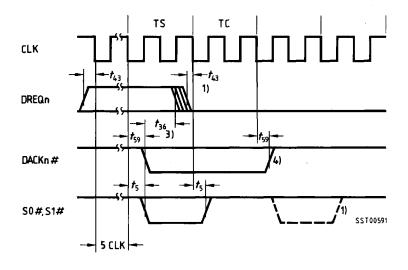

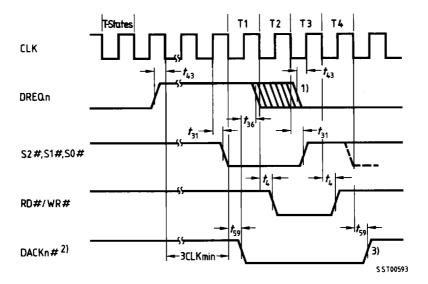

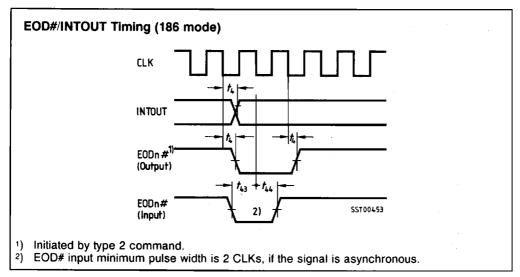

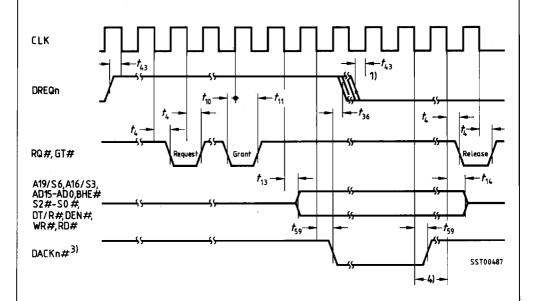

#### **DMA** Interface

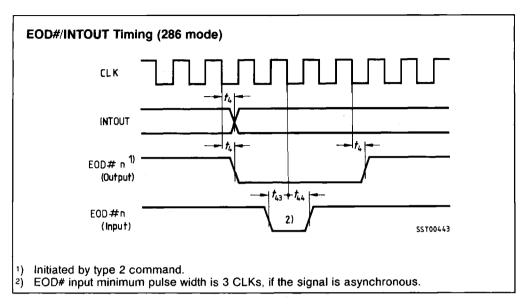

The DMA interface consists of three lines:

- DREQ DMA request

- DACK# DMA acknowledge and

- EOD# End of DMA

The first two lines work as request and acknowledge lines to control synchronized DMA transfers as known from conventional DMA controllers.

A special feature of the SAB 82258A are the bidirectional EOD# lines. Firstly they can be used as inputs to receive an asynchronous external terminate signal to terminate a running DMA.

Secondly, as an output, they can be used to send out a pulse which interrupts the CPU and/or signals to the peripheral a specific status (e.g. transfer aborted, or end of a block, or send/receive next block ...).

The EOD# output signal can be generated synchronously to a transfer (during the last transfer) or asynchronously to the transfers by a specific command.

In addition the EOD# output of channel 2 can be used as a collective interrupt output for all DMA channels while the other three retain their normal function.

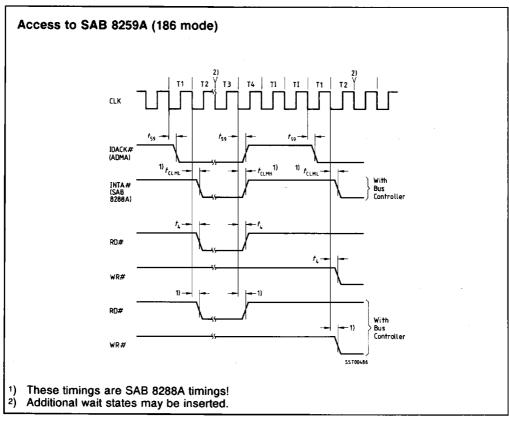

#### Slave Interface

The slave interface is used to access the SAB 82258A internal registers. Although nearly all of the communication between CPU and ADMA is done via memory-based data blocks, some direct accesses to ADMA registers are necessary.

For example during the initialization phase the general mode register must be written, or to start a channel the command pointer register and the general command register must be loaded. Also during the debugging phase it is of great benefit to have access to all of the SAB 82258A internal registers.

The slave interface is enabled by the CS# input and consists of the following lines:

- S0#, S1# status lines (inputs)

- RD#, WR# control lines (inputs)

- A0-A7 register address (inputs)

- D0-D15 data lines (inputs outputs) or

- AD0-AD15 data lines (inputs/outputs) for synchronous access in 186 mode

Note that all of these lines are outputs, if the SAB 82258A is an active bus master.

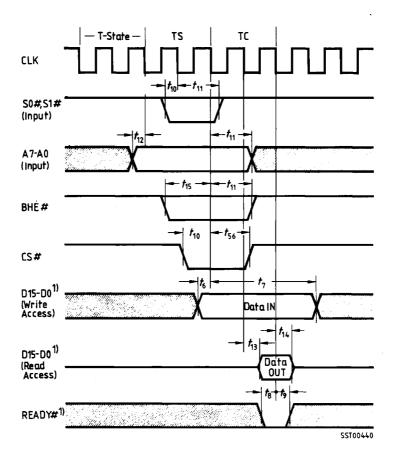

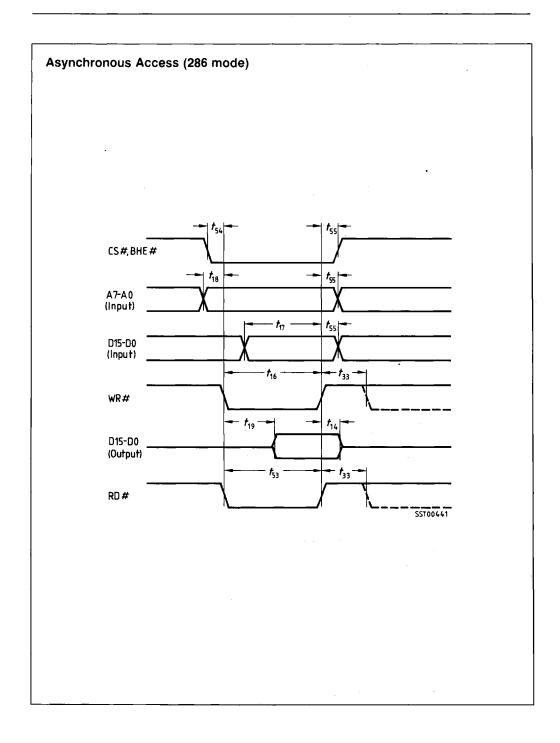

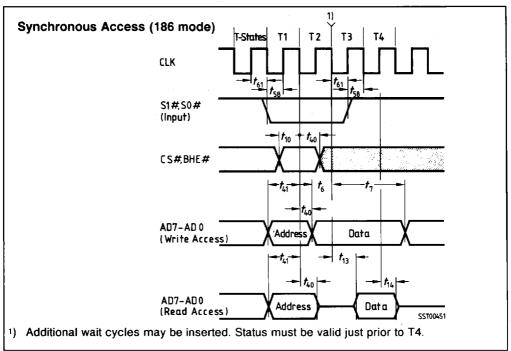

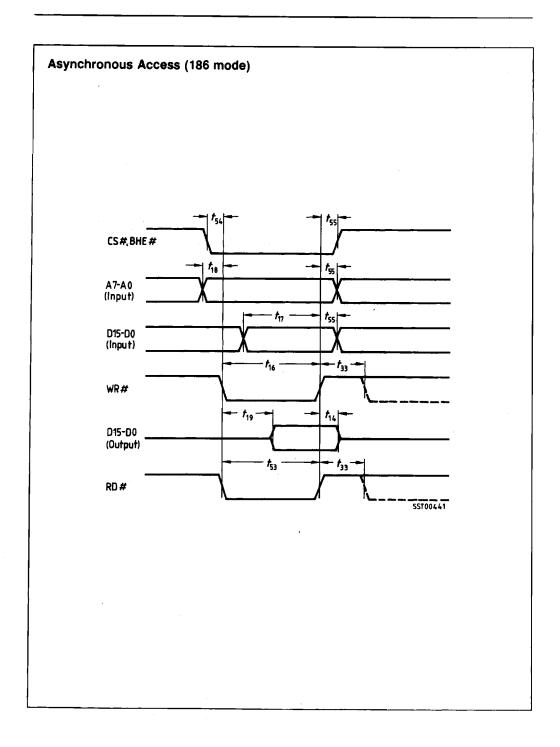

In 186 mode and 286 mode two types of accesses are possible:

- Synchronous access by means of the status lines. Processor and SAB 82258A are directly coupled and must use the same clock.

- Asynchronous access by using the control lines RD# and WR# (processor and ADMA may have different clocks).

In all modes except the synchronous access in 186 mode the register address must be supplied on address pins A0 to A7. Using synchronous access in 186 mode the address information is expected at address/data lines AD0 to AD7.

In remote mode only the asynchronous access is possible because the SAB 82258A first has to release its local bus to enable the register access. On receiving an access request (activation of CS# input) the SAB 82258A releases its local bus as soon as possible and signals this by activating the BREL line. Now the CPU can accomplish its access.

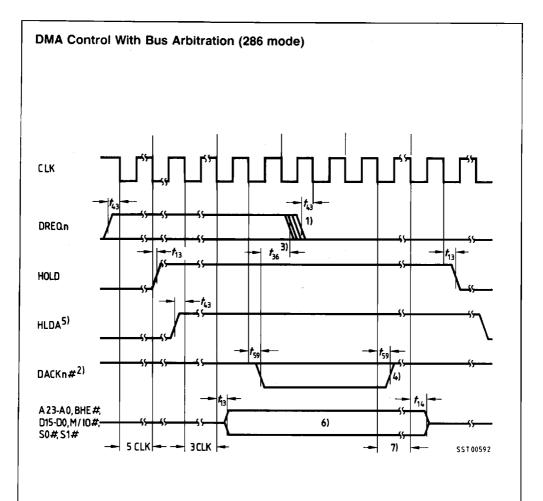

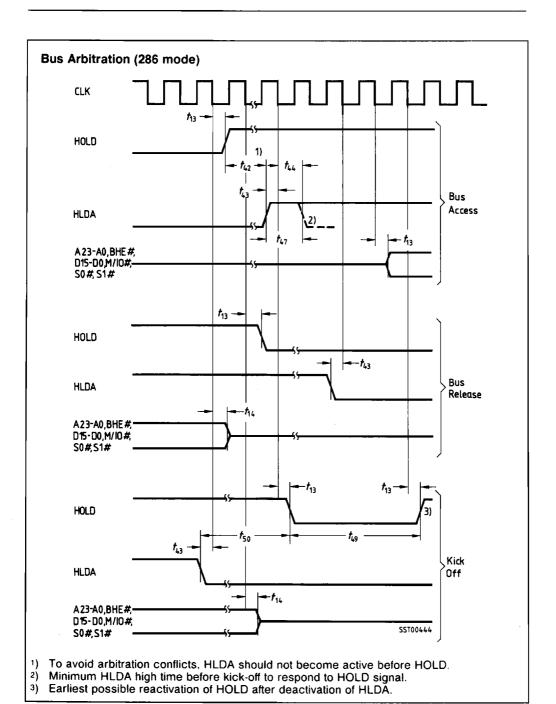

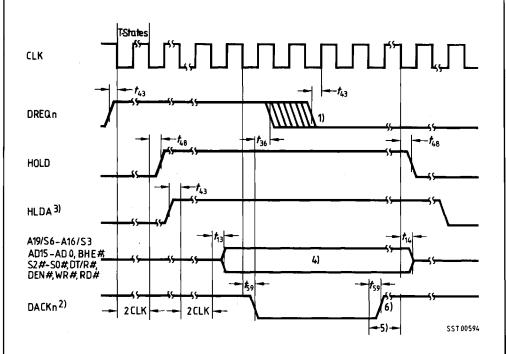

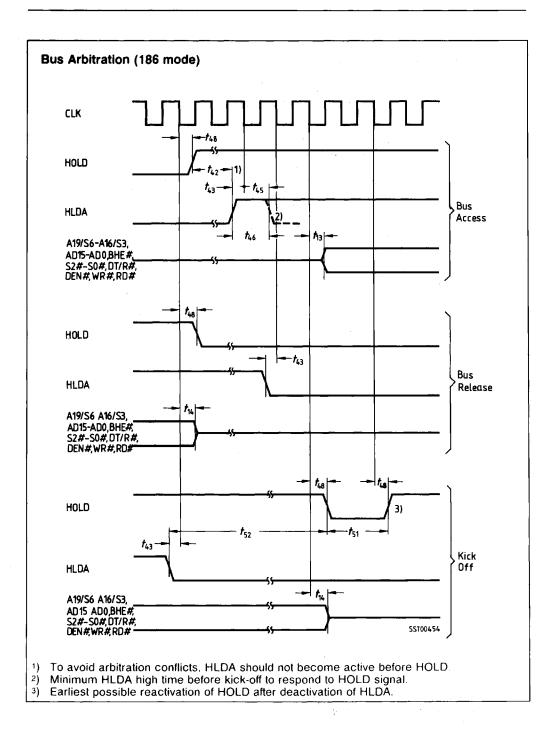

#### **Bus Arbitration**

To arbitrate access to the bus between the ADMA and the processor, the signals HOLD and HLDA serve for communication. Normally the ADMA competes for the bus via HOLD, the processor grants access to the bus via HLDA. The HLDA signal can also be deactivated in order to force the ADMA off the bus for a certain reason (kick off). After reactivation of HLDA, the ADMA will again get control of the bus.

In 8086 mode this communication is done by pulses via a single RQ# GT# line which uses the HOLD pin. In this case normally the HLDA input has no function. Nevertheless, even in 8086 mode the HLDA input can be used for kick-off. This provides some kind of additional bus arbitration.

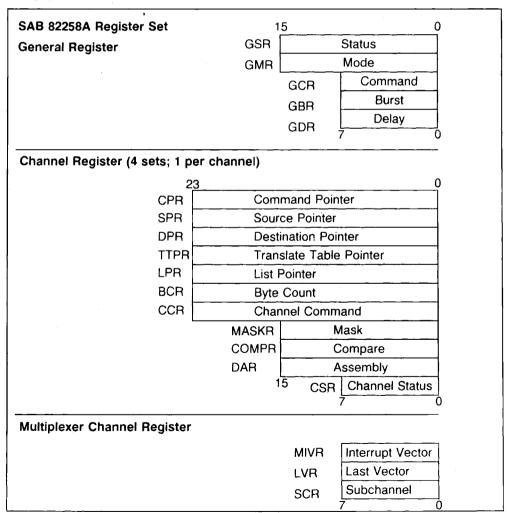

### Register Set

The following figure shows the user visible registers of the SAB 82258A. A set of 5 registers, called the general registers, is used for all of the 4 channels. The mode register is being written to first after reset and it describes the SAB 82258A environment – bus widths, priorities, etc.

The general command register (GCR) is used to start and stop the DMA transfer on different channels. The general status register (GSR) shows the status of all of the 4 channels; if the channel is running, if interrupt is pending, etc. General burst register (GBR) and general delay register (GDR) are used to specify the bus load which is permissible for the SAB 82258A.

There is a set of channel registers for each of the 4 channels. Most channel registers serve as cache registers and need to be accessed only for debugging. During normal operation they are loaded automatically by the SAB 82258A (see next paragraph). The layout of register addresses shown in the figure on the next page. All register addresses are even. Locations not designated in that figure are reserved and should not be used.

| Reg | Register Address Arrangement |         |         |                |               |  |  |

|-----|------------------------------|---------|---------|----------------|---------------|--|--|

|     |                              |         | Add     | ress Bits 7, 6 |               |  |  |

|     | Address Bits<br>0-5          | 00      | 01      | 10             | 11            |  |  |

|     | 0                            | GCR     |         |                |               |  |  |

|     | 2                            | SCR     |         |                |               |  |  |

|     | 4                            | GSR     |         |                |               |  |  |

|     | 6                            |         | ·       |                |               |  |  |

|     | . 8                          | GMR     |         |                |               |  |  |

|     | A                            | GBR     |         |                |               |  |  |

|     | С                            | GDR     |         |                |               |  |  |

|     | E                            |         |         |                |               |  |  |

|     | 10                           | CSR 0   | CSR 1   | CSR 2          | CSR 3         |  |  |

|     | 12                           | DAR 0   | DAR 1   | DAR 2          | DAR 3         |  |  |

|     | 14                           | MASKR 0 | MASKR 1 | MASKR 2        | MASKR 3       |  |  |

|     | 16                           | COMPR 0 | COMPR 1 | COMPR 2        | COMPR 3       |  |  |

|     | 18                           |         |         |                | MIVR          |  |  |

|     | 1A                           |         |         |                | LVR           |  |  |

|     | 1C                           |         |         |                |               |  |  |

|     | 1E                           |         |         |                |               |  |  |

|     | 20                           | CPR L0  | CPR L1  | CPR L2         | CPR L3        |  |  |

|     | 22                           | CPR H0  | CPR H1  | CPR H2         | CPR H3        |  |  |

|     | 24                           | SPR L0  | SPR L1  | SPR L2         | SPR L3        |  |  |

|     | 26                           | SPR H0  | SPR H1  | SPR H2         | SPR H3        |  |  |

|     | 28                           | DPR L0  | DPR L1  | DPR L2         | DPR L3        |  |  |

|     | 2A                           | DPR H0  | DPR H1  | DPR H2         | DPR H3        |  |  |

|     | 2C                           | TTPR L0 | TTPR L1 | TTPR L2        | TTPR L3       |  |  |

| _   | 2E                           | TTPR H0 | TTPR H1 | TTPR H2        | TTPR H3       |  |  |

|     | 30                           | LPR L0  | LPR L1  | LPR L2         | LPR L3/MTPR L |  |  |

|     | 32                           | LPR H0  | LPR H1  | LPR H2         | LPR H3/MTPR H |  |  |

|     | 34                           |         |         |                |               |  |  |

|     | 36                           |         |         |                |               |  |  |

|     | 38                           | BCR L0  | BCR L1  | BCR L2         | BCR L3        |  |  |

|     | 3A                           | BCR H0  | BCR H1  | BCR H2         | BCR H3        |  |  |

|     | 3C                           | CCR L0  | CCR L1  | CCR L2         | CCR L3        |  |  |

| -   | 3E                           | CCR H0  | CCR H1  | CCR H2         | CCR H3        |  |  |

|     |                              |         | ,       |                |               |  |  |

# Register Address Arrangement (cont'd)

| GCR   | = Ge  | neral Command Register | MIVR        | = | Multiplexer Interrupt Vector Register |

|-------|-------|------------------------|-------------|---|---------------------------------------|

| SCR   | = Sul | ochannel Register      | LVR         | = | Last Vector Register                  |

| GSR   | = Ge  | neral Status Register  | CPR         | = | Command Pointer Register              |

| GMR   | = Ge  | neral Mode Register    | SPR         | = | Source Pointer Register               |

| GBR   | = Ge  | neral Burst Register   | DPR         | = | Destination Pointer Register          |

| GDR   | = Ge  | neral Delay Register   | TTPR        | = | Translate Table Pointer Register      |

| CSR   | = Ch  | annel Status Register  | LPR         | = | List Pointer Register                 |

| DAR   | = Da  | ta Assembly Register   | <b>MTPR</b> | = | Multiplexer Table Pointer Register    |

| MASKR | = Ma  | sk Register            | BCR         | = | Byte Count Register                   |

| COMPR | = Co  | mpare Register         | CCR         | = | Channel Command Register              |

|       |       |                        |             |   |                                       |

## **Register Description**

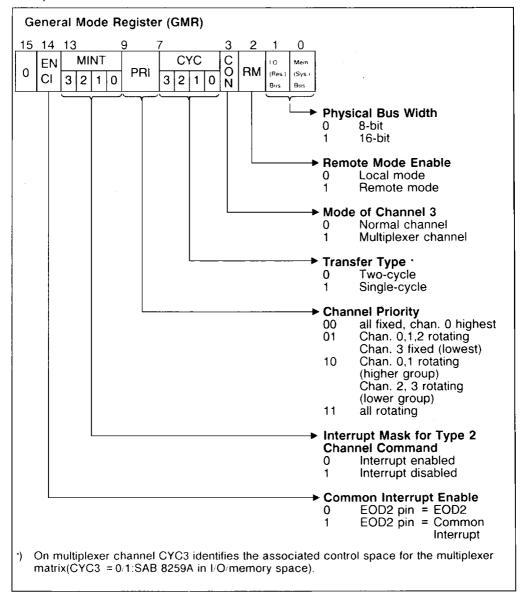

#### **General Mode Register**

In the general mode register GMR (figure below) the system wide parameters are specified. This register should be programmed first after reset, with an 8-bit bus program low byte first.

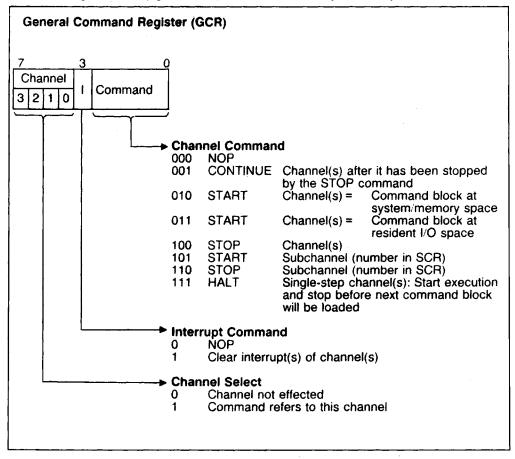

Individual channels are started and stopped by a command written to the general command register GCR (figure below). The GCR is directly loaded by the CPU.

### General Burst and Delay Register

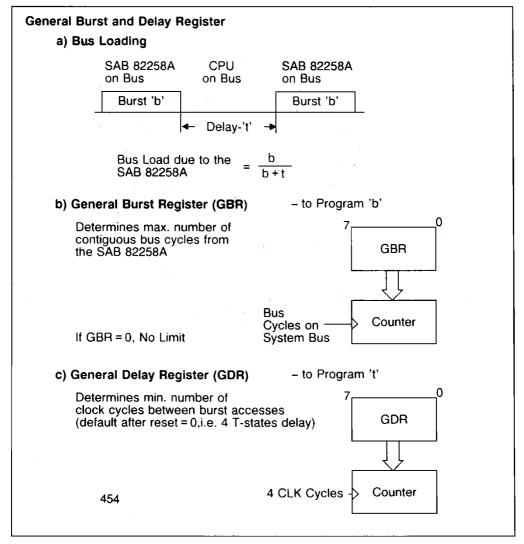

It is possible to restrict the bus load generated by the SAB 82258A on the CPU bus by programming the burst and the delay register. The bus load is defined by the formula given in figure a) below. The factor b (burst) is programmed in the general burst register GBR, t (delay time) in the general delay register GDR (see figures b and c). Since the SAB 82258A can also execute locked bus cycles, the maximum burst length consists of b+3 (8-bit bus) or b+2 (16-bit bus) bus cycles. GBR and GDR must be directly loaded by the CPU. Loading GBR with 0 leads to no bus load limitations for the SAB 82258A (default after reset).

### **General Status Register**

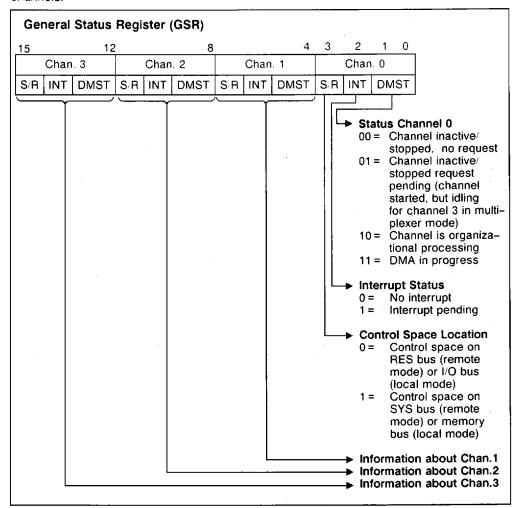

The general status register GSR (figure below) shows the current status of all the channels.

#### **Channel Commands**

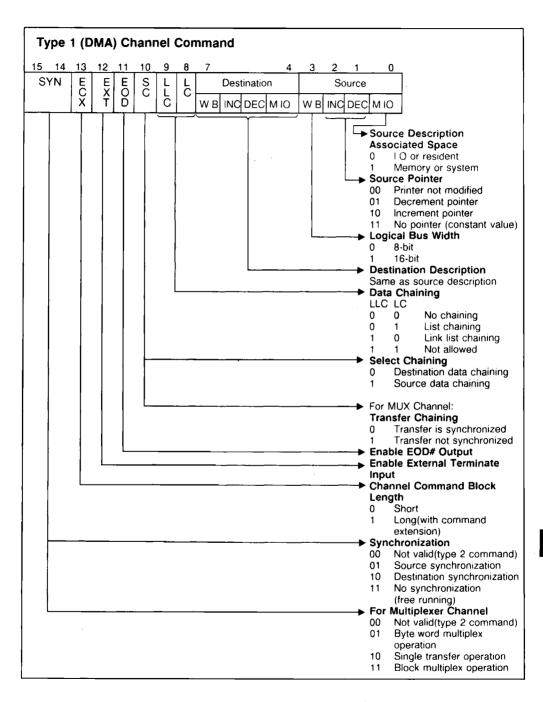

The channel commands are contained in the channel command block. Up to 22 bits are used to specify the command. There are two types of channel commands:

- Type 1: for data movement

- Type 2: for command chaining control

The command block for a type 1 command is in general 26 bytes long (see figure ...Memory based Communication").

For certain type 1 transfers which, for example, do not use on-the-fly match, translate or verify feature, the command is only 16 bits long and only a short command block is necessary (see figure "Memory based Communication").

The type 1 command fields (see figures below) contain information on:

- a. Bus width of source and destination

- b. If source and/or destination address should be incremented or decremented or kept constant during the transfer

- If source/destination is in memory or I/O space (local mode) or in system or resident space (remote mode)

- d. If data chaining (list or linked-list) is to be performed

- e. If the data transfer is synchronized (source or destination)

- f. If an on-the-fly match operation and/or translate operation has to be performed

- q. If a verify operation has to be performed

- h. If 32-bit fly-by transfers are to be executed.

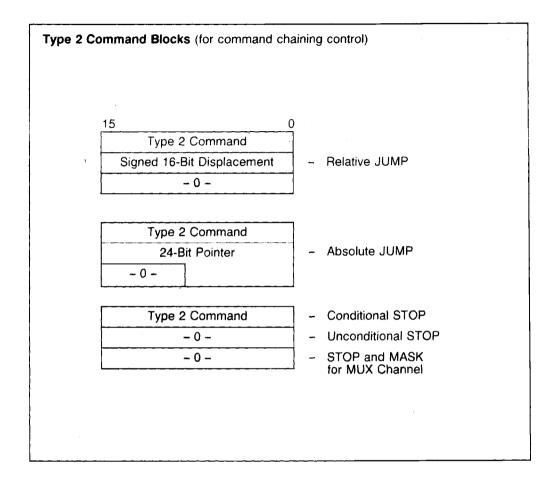

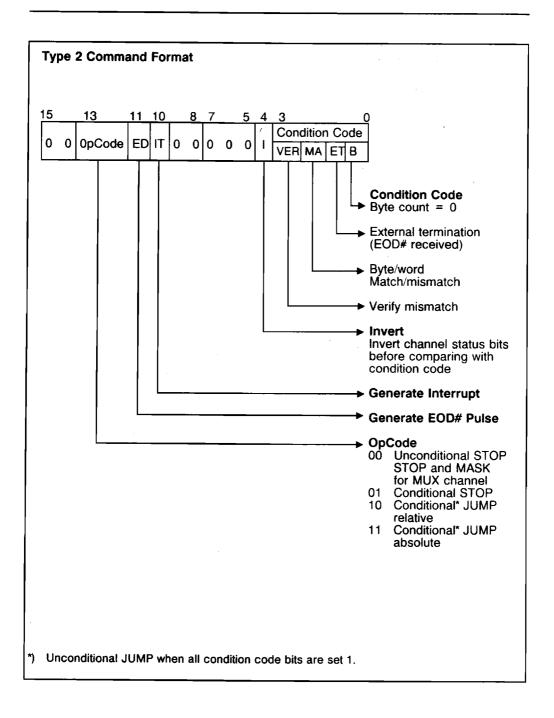

Type 2 command blocks are 6 bytes long (see figure "Type 2 Command Block") of which the first 2 bytes form the command and the rest is either a relative displacement or an absolute address for the JUMP operation. There are two basic type 2 commands (see figure "Type 2 Command Block"):

- a. JUMP conditional and non-conditional

- b. STOP conditional and non-conditional

The conditional case tests for either of the 4 condition bits which are altered at the termination of any DMA operation:

- Termination due to byte count end

- Termination due to mask-compare

- Termination due to external terminate

- Verify operation resulting in mismatch.

It is thus possible to JUMP or STOP further execution of commands based on any of these conditions and optionally generate an EOD# or interrupt signal.

The combination of type 1 and 2 commands gives the SAB 82258A a high degree of "programmability". It can thus execute quite complex algorithms with a fairly low demand for CPU service.

#### **Channel Status Register**

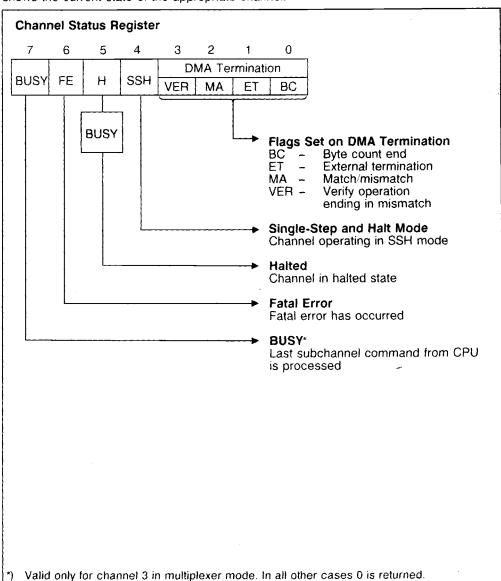

For each channel there is a channel status register (see figure below). This register shows the current state of the appropriate channel.

## Multiplexer Channel Register

These registers are valid only for channel 3 if programmed as multiplexer channel.

#### Multiplexer Table Pointer Register (MTPR)

This 24-bit register is used to reference the multiplexer table in memory (see figure "Structure of the Multiplexer Table"). It must be loaded by the CPU. Physically the list pointer register is used, since data chaining is not allowed for multiplexer channel.

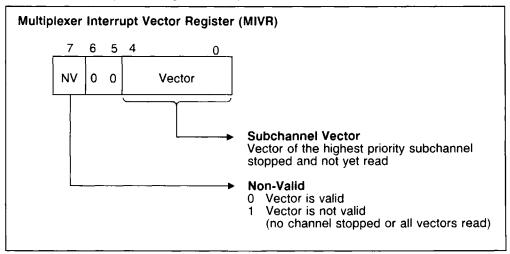

### Multiplexer Interrupt Vector Register (MIVR)

This 8-bit register is read by the CPU to determine which subchannels are stopped. The vectors of the stopped subchannels are output on subsequent read operations in the order of their priority (0 has highest priority).

## Last Vector Register (LVR)

The 8-bit register holds the last vector read by the SAB 82258A (from SAB 8259A). In case of a stop caused by a fatal error on channel 3, LVR determines the failing subchannel.

#### Subchannel Register (SCR)

The 8-bit register must be loaded by the CPU with the desired subchannel number before a subchannel command is written into GCR.

#### **Timings**

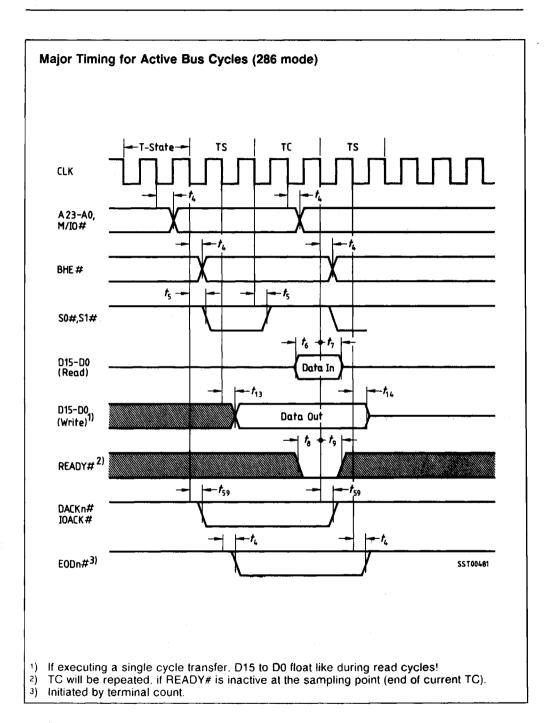

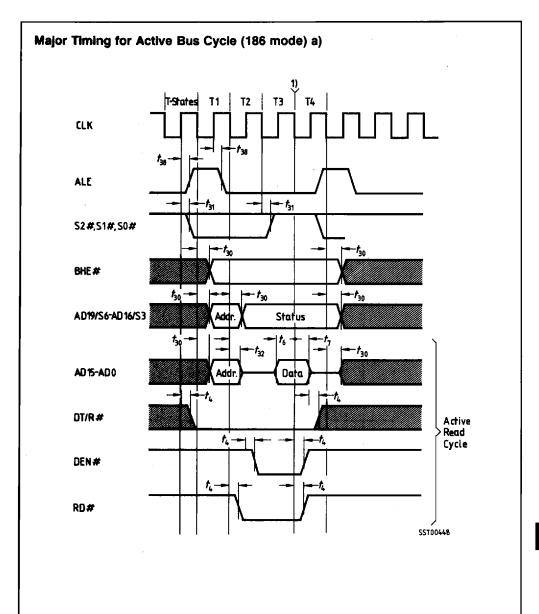

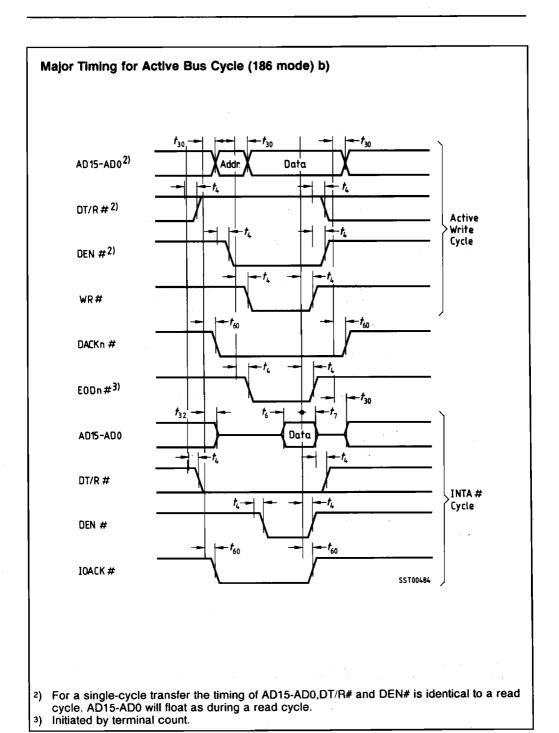

The bus timings in 286 and remote mode are identical to that for the SAB 80286, in 186 and 8086 mode the timings are identical to that for the SAB 80186. For exact timings see timing diagrams of AC Characteristics.

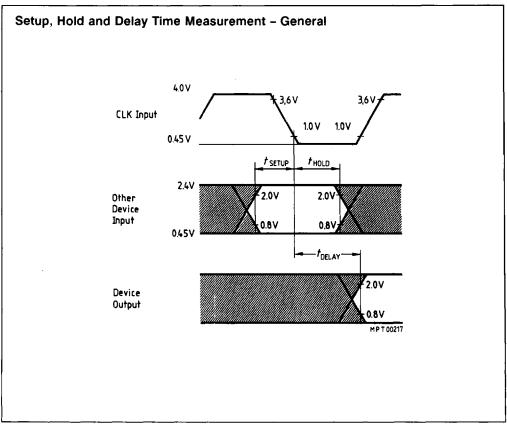

Asynchronous control inputs are specified with setup and hold times which are only important to determine whether the SAB 82258A responds to the signal in the current cycle or the next cycle.

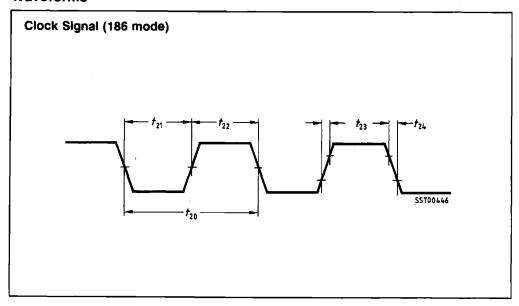

The following pages hold two sections of AC characteristics and waveforms. The first section refers to 286 mode and remote mode, the second one to 186 mode and 8086 mode.

## **Absolute Maximum Ratings**

Temperature under bias Storage temperature Voltage on any pin with respect to ground Power dissipation 0 to 70°C -65 to + 150°C -0.5 to + 7 V 3.6 W

Note:

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC Characteristics 19

$T_{\rm C}$  = 0 to 100°C;  $V_{\rm CC}$  = +5 V ± 10%

| Parameter                         | Symbol                 | Limit values |                       | Unit | Test                                                    |

|-----------------------------------|------------------------|--------------|-----------------------|------|---------------------------------------------------------|

|                                   |                        | min.         | max.                  |      | conditions                                              |

| Input low voltage<br>(except CLK) | VIL                    | -0.5         | +0.8                  | V    | -                                                       |

| Input high voltage (except CLK)   | <b>V</b> <sub>IH</sub> | 2.0          | V <sub>CC</sub> + 0.5 | V    | _                                                       |

| Output low voltage                | VOL                    |              | 0.45                  | V    | $I_{OL} = 3.0 \text{ mA}$                               |

| Output high voltage               | V <sub>OH</sub>        | 2.4          | _                     | ٧    | I <sub>OH</sub> = -400 μA                               |

| Power supply current              | I <sub>CC</sub>        | _            | 550                   | mΑ   | $T_{\rm C} = 0^{\circ} \rm C$ , (turn on)               |

|                                   |                        | -            | 385                   | mA   | $T_{\rm C}$ = 100°C (steady                             |

|                                   |                        |              |                       |      | operation)                                              |

|                                   |                        | ļ            |                       |      | all outputs open                                        |

| Input leakage current             | $I_{\Box 1}$           |              |                       |      |                                                         |

| S0#, S1#, S2#, BHE#, RD#,         |                        | -            | -200                  | μА   | $0 \text{ V} \leq V_{iN} \leq V_{CC}$                   |

| WR#, M/IO#                        |                        |              |                       |      |                                                         |

| HOLD(RQ#/GT# mode), EOD#          |                        | _            | -1.5                  | mA   | $0 \text{ V} \leq V_{\text{IN}} \leq V_{\text{CC}}$     |

| A23 (AREADY),A21 2)               |                        | -            | -1.5                  | mA   | $0 \text{ V} \leq V_{\text{IN}} \leq V_{\text{CC}}$     |

| other pins                        |                        | -            | ± 10                  | μΑ   | $0 \text{ V} \leq V_{\text{IN}} \leq V_{\text{CC}}$     |

| Output leakage current            | $I_{LO}$               | -            | ± 10                  | μΑ   | $0.45 \text{ V} \leq V_{\text{OUT}} \leq V_{\text{CC}}$ |