# FailSafe™ PacketClock™ Global Communications Clock Generator

#### **Features**

- Fully integrated phase-locked loop (PLL)

- FailSafe<sup>™</sup> output

- · PLL driven by a crystal oscillator that is phase-aligned with external reference

- Two 6.312-MHz outputs from 8-kHz input

- · Low-jitter, high-accuracy outputs

- 3.3V ± 5% operation

- 16-lead TSSOP

#### **Benefits**

- · Integrated high-performance PLL tailored for telecommunications frequency synthesis eliminates the need for external loop filter components

- · When reference is off, DCXO maintains clock outputs and SAFE pin indicates FailSafe conditions

- DCXO maintains continuous operation should the input reference clock fail

- · Glitch-free transition simplifies system design

- Works with commonly available, low-cost 18.432-MHz crystal

- · Zero-ppm error for all output frequencies

- · Compatible across industry standard design platforms

- Industry standard package with 6.4 x 5.0 mm<sup>2</sup> footprint and a height profile of just 1.1 mm

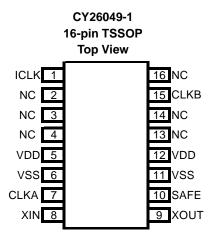

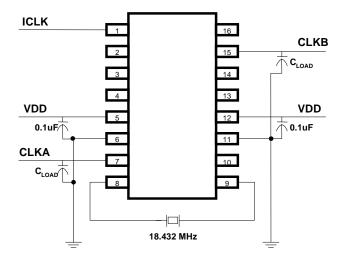

## **Pin Configuration**

#### **Pin Description**

| Pin Number | Pin Name | Pin Description                                                        |

|------------|----------|------------------------------------------------------------------------|

| 1          | ICLK     | Reference Input Clock: 8kHz.                                           |

| 2          | NC       | No Connect.                                                            |

| 3          | NC       | No Connect.                                                            |

| 4          | NC       | No Connect.                                                            |

| 5          | VDD      | Voltage Supply: 3.3V.                                                  |

| 6          | VSS      | Ground.                                                                |

| 7          | CLKA     | Clock Output: 6.312 MHz.                                               |

| 8          | XIN      | Pullable Crystal Input: 18.432 MHz.                                    |

| 9          | XOUT     | Pullable Crystal Output: 18.432 MHz.                                   |

| 10         | SAFE     | High = reference ICLK within range, Low = reference ICLK out of range. |

| 11         | VSS      | Ground.                                                                |

| 12         | VDD      | Voltage Supply: 3.3V.                                                  |

| 13         | NC       | No Connect.                                                            |

| 14         | NC       | No Connect.                                                            |

| 15         | CLKB     | Clock Output: 6.312 MHz.                                               |

| 16         | NC       | No Connect.                                                            |

#### **Selector Guide**

| Part Number | Input Frequency Range                                          | Outputs | Output Frequencies |

|-------------|----------------------------------------------------------------|---------|--------------------|

| CY26049ZC-1 | Reference Input Clock: 8 kHz                                   | 2       | 6.312 MHz          |

|             | Crystal: 18.432-MHz pullable Crystal per Cypress Specification |         |                    |

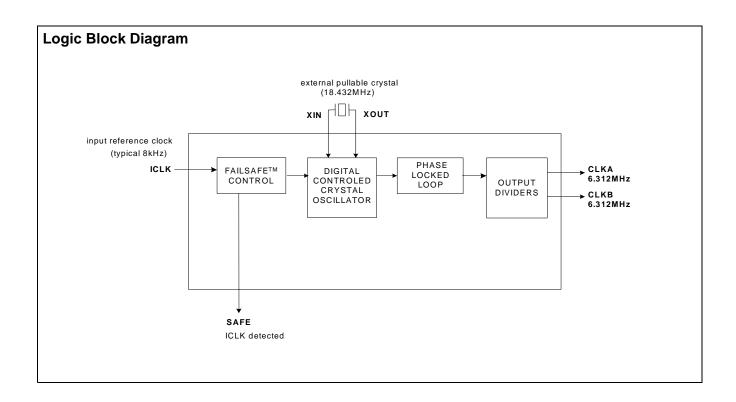

#### **Description**

CY26049-1 is a FailSafe frequency synthesizer with a reference clock input and two 6.312-MHz outputs. The device provides an optimum solution for applications where continuous operation is required in the event of a primary clock failure. The continuous, glitch-free operation is achieved by using a DCXO, which serves as a primary clock source. The FailSafe control circuit synchronizes the DCXO oscillator with the reference as long as the reference is within the pull range of the crystal.

In the event of a reference clock failure the DCXO maintains the last frequency of the reference clock. The unique feature of the CY26049-1 is that the DCXO is in fact the primary clocking source. When the reference clock is restored, the DCXO automatically resynchronizes to the reference. The status of the reference clock input, as detected by the CY26049-1, is reported by the SAFE pin.

## **ADVANCE INFORMATION**

CY26049-1

#### **Absolute Maximum Conditions**

| Supply Voltage (V <sub>DD</sub> )0.5 to +7.0V                                                        |

|------------------------------------------------------------------------------------------------------|

| DC Input Voltage0.5V to V <sub>DD</sub> +0.5                                                         |

| Storage Temperature (Non-condensing)55°C to +125°C                                                   |

| Junction Temperature40°C to +125°C <b>Recommended Pullable Crystal Specifications</b> <sup>[1]</sup> |

| Data Retention @ Tj=125°C                                             | .> 10 years |

|-----------------------------------------------------------------------|-------------|

| Package Power Dissipation                                             | 350 mW      |

| ESD (Human Body Model) MIL-STD-883                                    | 2000V       |

| (Above which the useful life may be impaired. For lines, not tested.) | user guide- |

| Parameter                      | Description                                              | Comments                                                                    | Min. | Тур.   | Max. | Unit |

|--------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------|------|--------|------|------|

| F <sub>NOM</sub>               | Nominal crystal frequency                                | Parallel resonance, fundamental mode, AT cut                                | -    | 18.432 | -    | MHz  |

| C <sub>LNOM</sub>              | Nominal load capacitance                                 |                                                                             | -    | 14     | -    | pF   |

| R <sub>1</sub>                 | Equivalent series resistance (ESR)                       | Fundamental mode                                                            | -    | -      | 25   | Ω    |

| R <sub>3</sub> /R <sub>1</sub> | Ratio of third overtone mode ESR to fundamental mode ESR | Ratio used because typical $R_1$ values are much less than the maximum spec | 3    | -      | 1    |      |

| DL                             | Crystal drive level                                      | No external series resistor assumed                                         | _    | 0.5    | 2    | mW   |

| F <sub>3SEPHI</sub>            | Third overtone separation from 3*F <sub>NOM</sub>        | High side                                                                   | 400  | _      | _    | ppm  |

| F <sub>3SEPLO</sub>            | Third overtone separation from 3*F <sub>NOM</sub>        | Low side                                                                    | ı    | -      | -200 | ppm  |

| $C_0$                          | Crystal shunt capacitance                                |                                                                             | ı    | -      | 7    | pF   |

| C <sub>0</sub> /C <sub>1</sub> | Ratio of shunt to motional capacitance                   |                                                                             | 180  | _      | 250  |      |

| C <sub>1</sub>                 | Crystal motional capacitance                             |                                                                             | 14.4 | 18     | 21.6 | fF   |

## **Recommended Operating Conditions**

| Parameter         | Description                                                                                                | Min. | Тур. | Max. | Unit |

|-------------------|------------------------------------------------------------------------------------------------------------|------|------|------|------|

| $V_{DD}$          | Operating Voltage                                                                                          | 3.15 | 3.3  | 3.45 | V    |

| T <sub>AC</sub>   | Ambient Temperature (Commercial Temperature)                                                               | 0    | _    | 70   | ° C  |

| C <sub>LOAD</sub> | Max Output Load Capacitance                                                                                | _    | _    | 15   | pF   |

| t <sub>pu</sub>   | Power-up time for all V <sub>DD</sub> s to reach minimum specified voltage (power ramps must be monotonic) | 0.05 | _    | 500  | ms   |

## DC Electrical Specifications (Commercial Temp: 0° to 70°C)

| Parameter       | Description         | Test Conditions                                    | Min. | Тур. | Max. | Unit     |

|-----------------|---------------------|----------------------------------------------------|------|------|------|----------|

| I <sub>OH</sub> | Output High Current | $V_{OH} = V_{DD} - 0.5$ , $V_{DD} = 3.3V$ (source) | 12   | 24   | _    | mA       |

| I <sub>OL</sub> | Output Low Current  | $V_{OL} = 0.5, V_{DD} = 3.3V \text{ (sink)}$       | 12   | 24   | _    | mA       |

| V <sub>IH</sub> | Input High Voltage  | CMOS Levels                                        | 0.7  | _    | _    | $V_{DD}$ |

| V <sub>IL</sub> | Input High Voltage  | CMOS Levels                                        | _    | _    | 0.3  | $V_{DD}$ |

| I <sub>IH</sub> | Input High Current  | $V_{IH} = V_{DD}$                                  | _    | 5    | 10   | μΑ       |

| I <sub>IL</sub> | Input Low Current   | V <sub>IL</sub> = 0V                               | _    | 5    | 10   | μΑ       |

| C <sub>IN</sub> | Input Capacitance   |                                                    | _    | _    | 7    | pF       |

| I <sub>DD</sub> | Supply Current      | $C_{LOAD} = 15 \text{ pF}, V_{DD} = 3.45 \text{V}$ | -    | _    | 30   | mA       |

## **AC Electrical Specifications** (Commercial Temp: 0° to 70° C)

| Parameter           | Description                        | Test Conditions                                                 | Min. | Тур. | Max. | Unit |

|---------------------|------------------------------------|-----------------------------------------------------------------|------|------|------|------|

| f <sub>ICLK-E</sub> | Frequency, Input Clock             | Input Clock Frequency, External Mode                            | -    | 8.00 | _    | kHz  |

| LR                  | FailSafe Lock Range <sup>[2]</sup> | Range of reference ICLK for Safe = High                         | -250 | _    | +250 | ppm  |

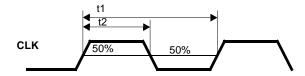

| $DC = t_2/t_1$      | Output Duty Cycle                  | Duty Cycle defined in Figure 1, measured at 50% of $V_{\rm DD}$ | 45   | 50   | 55   | %    |

| T <sub>PJIT1</sub>  | Clock Jitter; output > 5 MHz       | Period Jitter, Peak to Peak, 10,000 periods                     | _    | _    | 250  | ps   |

|                     |                                    | RMS Period Jitter, RMS                                          | -    | _    | 50   | ps   |

| t <sub>6</sub>      | PLL Lock Time                      | Time for PLL to lock within ± 150 ppm of target frequency       | _    | _    | 3    | ms   |

#### Notes:

Ecliptek ECX-5761-18.432M meets these specifications.

Dependent on crystals chosen and crystal specs.

## **AC Electrical Specifications** (Commercial Temp: 0° to 70° C) (continued)

| Parameter            | Description               | Test Conditions                                                                                         | Min. | Тур. | Max. | Unit |

|----------------------|---------------------------|---------------------------------------------------------------------------------------------------------|------|------|------|------|

| t <sub>fs_lock</sub> | Failsafe Lock Time        | Time for PLL to lock to ICLK (outputs phase aligned with ICLK and Safe = High)                          | -    | -    | 7    | S    |

| f <sub>error</sub>   | Frequency Synthesis Error | Actual mean frequency error vs. target                                                                  | _    | 0    | _    | ppm  |

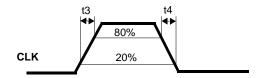

| ER                   | Rising Edge Rate          | Output Clock Edge Rate, Measured from 20% to 80% of $V_{DD}$ , $C_{LOAD}$ = 15pF. See <i>Figure 2</i> . | 0.8  | 1.4  | 2    | V/ns |

| EF                   | Falling Edge Rate         | Output Clock Edge Rate, Measured from 20% to 80% of $V_{DD}$ , $C_{LOAD}$ = 15pF. See <i>Figure</i> 2.  | 0.8  | 1.4  | 2    | V/ns |

## **Voltage and Timing Definitions**

Figure 1. Duty Cycle Definition; DC = t2/t1

Figure 2. Rise and Fall Time Definitions: ER =  $0.6 \times VDD / t3$ , EF =  $0.6 \times VDD / t4$

#### **Test Circuit**

## **Ordering Information**

| Ordering Code | Package Type                | Operating Temperature Range |

|---------------|-----------------------------|-----------------------------|

| CY26049ZC-1   | 16-lead TSSOP               | Commercial 0 to 70°C        |

| CY26049ZC-1T  | 16-lead TSSOP—Tape and Reel | Commercial 0 to 70°C        |

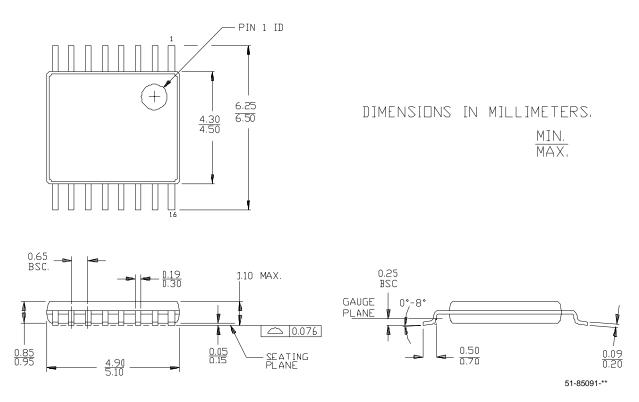

## **Package Drawing and Dimensions**

## 16-lead Thin Shrunk Small Outline Package (4.40 MM Body) Z16

FailSafe and PacketClock are trademarks of Cypress Semiconductor. All product and company names mentioned in this document are the trademarks of their respective holders.

# ADVANCE INFORMATION

CY26049-1

## **Document History Page**

| REV. | ECN No. | Issue<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                     |

|------|---------|---------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **   | 120007  | 11/01/02      | CKN                | New Data Sheet                                                                                                                                                                                                                                                                                            |

| *A   | 128089  | 09/11/03      | IJA                | Changed title to FailSafe™ PacketClock™ Global Communications Clock Generator from FailSafe Communications Clock Generator Changed some wording of Features in Features and Benefits column Changed a few definitions in Pin Description table Replaced Recommended Pullable Crystal Specifications table |