# NSSD

# (NAND Flash-based Solid State Disk)

Module Type Product Data sheet Version 1.1 Sep 2006

INFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS, AND IS SUBJECT TO CHANGE WITHOUT NOTICE.

NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE,

TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOLOGY. ALL INFORMATION IN THIS DOCUMENT IS PROVIDED

ON AS "AS IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND.

1. For updates or additional information about Samsung products, contact your nearest Samsung office.

2. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where Product failure could result in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply.

\* Samsung Electronics reserves the right to change products or specification without notice.

## **Document Title**

## SAMSUNG NAND Flash-based Solid State Disk

## **Revision History**

| <u>Revision No</u> | History                                                                                                                                                                                                                                                                               | Draft Date  | <u>Remark</u> |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------|

| 0.5                | Initial issue                                                                                                                                                                                                                                                                         | May.09.2006 | Preliminary   |

| 1.0                | Physical dimension was added(Slim 4/8/16GB)<br>GND PAD was added on Slim 32GB<br>Supporting SECURITY FEATURE Set<br>Supporting SMART FEATURE Set<br>Supporting HOST PROTECTED AREA FEATURE Set<br>Identify Device Data was updated<br>Software/Hardware Reset State Diagram was added | Aug.18.2006 | Final         |

| 1.1                | Misprint was modified(page 56)<br>( In graph, R/B -> BSY)<br>Product line-up was added(page 65)<br>(A-die based Small 8/16GB)<br>(Shared PCB based Slim 4/8/16/32GB)                                                                                                                  | Sep.27.2006 | Final         |

The attached data sheets are prepared and approved by SAMSUNG Electronics. And SAMSUNG Electronics has the right to change all the specifications in data sheets. SAMSUNG Electronics will evaluate and reply to any dear customer's requests and questions on the parameters of this device. If dear customer has any questions, please call or fax to Memory Product Planning Team, or contact the SAMSUNG branch office near your office

## **TABLE OF CONTENTS**

| 1. General Description                                  | 6  |

|---------------------------------------------------------|----|

| 2. Physical Specifications                              | 7  |

| 2.1 Small Type Physical Dimensions(16GB)                | 7  |

| 2.2 Slim Type Physical Dimensions(4/8/16GB)             | 9  |

| 2.3 Slim Type Physical Dimensions(32GB)                 | 11 |

| 3. Product Specifications                               | 13 |

| 3.1 System Interface and Configuration                  | 13 |

| 3.2 System Performance                                  | 13 |

| 3.3 System Power Consumption                            | 13 |

| 3.4 System Reliability                                  | 13 |

| 3.5 Environmental Specifications                        | 13 |

| 4. Electrical Specifications                            | 14 |

| 4.1 ZIF Connector Dimensions                            | 14 |

| 4.2 Pin Assignment                                      | 14 |

| 4.3 Signal Descriptions                                 | 15 |

| 4.4 DC Characteristics                                  | 16 |

| 4.4.1 Absolute Maximum Ratings                          | 16 |

| 4.4.2 Recommended Operating Conditions                  | 16 |

| 4.4.3 Electrical Characteristics                        | 16 |

| 4.5 AC Characteristics                                  | 17 |

| 4.5.1 Register Transfers                                | 17 |

| 4.5.2 PIO Data Transfers                                | 19 |

| 4.5.3 Multiword DMA Data Transfer                       | 21 |

| 4.5.3.1 Initiating a Multiword DMA data burst           | 22 |

| 4.5.3.2 Sustaining a Multiword DMA data burst           | 23 |

| 4.5.3.3 Device terminating a Multiword DMA data burst   | 24 |

| 4.5.3.4 Host terminating a Multiword DMA data burst     | 25 |

| 4.5.4 Ultra DMA Data Transfer                           | 26 |

| 4.5.4.1 Initiating an Ultra DMA data-in burst           | 27 |

| 4.5.4.2 Sustained Ultra DMA data-in burst               | 28 |

| 4.5.4.3 Host pausing an Ultra DMA data-in burst         | 29 |

| 4.5.4.4 Device terminating an Ultra DMA data-in burst   | 30 |

| 4.5.4.5 Host terminating an Ultra DMA data-in burst     | 31 |

| 4.5.4.6 Initiating an Ultra DMA data-out burst          | 32 |

| 4.5.4.7 Sustained Ultra DMA data-out burst              | 33 |

| 4.5.4.8 Device pausing an Ultra DMA data-out burst      | 34 |

| 4.5.4.9 Host terminating an Ultra DMA data-out burst    | 35 |

| 4.5.4.10 Device terminating an Ultra DMA data-out burst | 36 |

| 5. ATA Registers                                        | 37 |

| 5.1 I/O Register Descriptions                           | 37 |

| 5.2 Alternate Status Register                           | 37 |

| 5.2.1 Address                                           | 37 |

| 5.2.2 Direction                                         | 37 |

| 5.2.3 Access Restrictions                               | 37 |

| 5.2.4. Effect                                           | 37 |

| 5.2.5 Functional Description                            | 37 |

| 5.3 Command Register                                    | 38 |

| 5.3.1 Address                                           | 38 |

| 5.3.2 Direction                                         | 38 |

| 5.3.3 Access Restrictions                               | 38 |

| 5.3.4 Effect                                            | 38 |

| 5.3.5 Functional description                            | 38 |

| 5.3.6 Field/bit description                             | 38 |

| 5.4 Cylinder High Register                              | 39 |

| 5.4.1 Address                                           | 39 |

| 5.4.2 Direction                                         | 39 |

| 5.4.3 Access Restrictions                               | 39 |

| 5.4.4 Effect                                            | 39 |

| 5.4.5 Functional description  | 39 |

|-------------------------------|----|

| 5.5 Cylinder Low Register     | 40 |

| 5.5.1 Address                 | 40 |

| 5.5.2 Direction               | 40 |

| 5.5.3 Access Restrictions     | 40 |

| 5.5.4 Effect                  | 40 |

| 5.5.5 Functional description  | 40 |

|                               |    |

| 5.6 Data Port                 | 40 |

| 5.6.1 Address                 | 40 |

| 5.6.2 Direction               | 40 |

| 5.6.3 Access Restrictions     | 41 |

| 5.6.4 Effect                  | 41 |

| 5.6.5 Functional description  | 41 |

| 5.6.6 Field/bit description   | 41 |

| 5.7 Data Register             | 42 |

| 5.7.1 Address                 | 42 |

| 5.7.2 Direction               | 42 |

| 5.7.3 Access Restrictions     | 42 |

| 5.7.4 Effect                  | 42 |

| 5.7.5 Functional description  | 42 |

| •                             |    |

| 5.7.6 Field/bit description   | 42 |

| 5.8 Device Control Register   | 43 |

| 5.8.1 Address                 | 43 |

| 5.8.2 Direction               | 43 |

| 5.8.3 Access Restrictions     | 43 |

| 5.8.4 Effect                  | 43 |

| 5.8.5 Functional description  | 43 |

| 5.8.6 Field/bit description   | 43 |

| 5.9 Device/Head Register      | 44 |

| 5.9.1 Address                 | 44 |

| 5.9.2 Direction               | 44 |

| 5.9.3 Access Restrictions     | 44 |

| 5.9.4 Effect                  | 44 |

|                               |    |

| 5.9.5 Functional description  | 44 |

| 5.9.6 Field/bit description   | 44 |

| 5.10 Error Register           | 45 |

| 5.10.1 Address                | 45 |

| 5.10.2 Direction              | 45 |

| 5.10.3 Access Restrictions    | 45 |

| 5.10.4 Effect                 | 45 |

| 5.10.5 Functional description | 45 |

| 5.10.6 Field/bit description  | 45 |

| 5.11 Features Register        | 46 |

| 5.11.1 Address                | 46 |

| 5.11.2 Direction              | 40 |

|                               | 46 |

| 5.11.3 Access Restrictions    |    |

| 5.11.4 Effect                 | 46 |

| 5.11.5 Functional description | 46 |

| 5.12 Sector Count Register    | 47 |

| 5.12.1 Address                | 47 |

| 5.12.2 Direction              | 47 |

| 5.12.3 Access Restrictions    | 47 |

| 5.12.4 Effect                 | 47 |

| 5.12.5 Functional description | 47 |

| 5.13 Sector Number Register   | 48 |

| 5.13.1 Address                | 48 |

| 5.13.2 Direction              | 48 |

| 5.13.3 Access Restrictions    | 48 |

| 5.13.4 Effect                 | 48 |

|                               |    |

| 5.13.5 Functional description | 48 |

| 5.14 Status Register          | 49 |

## TABLE OF CONTENTS

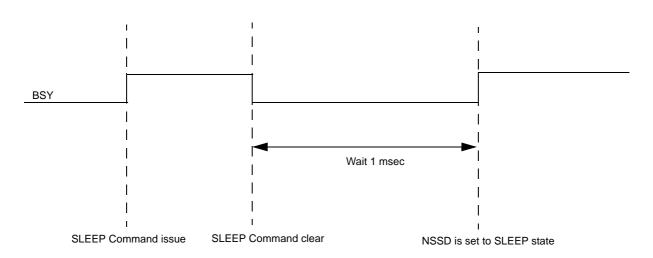

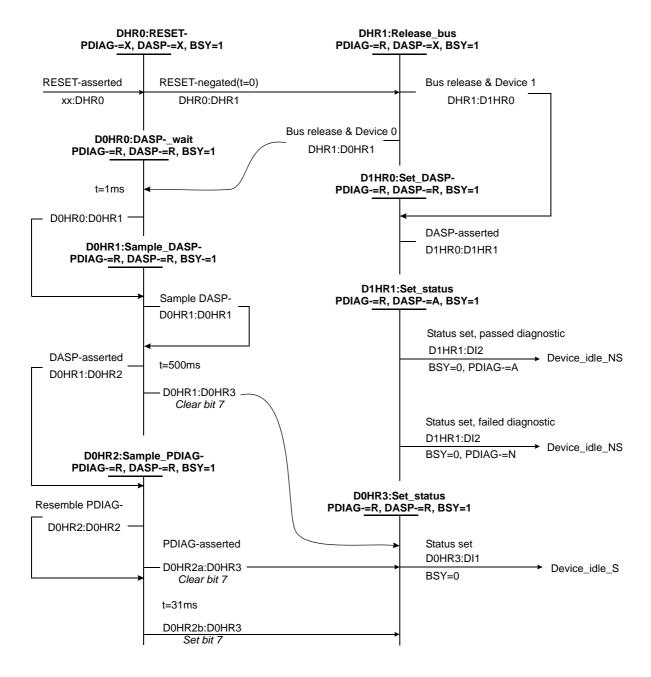

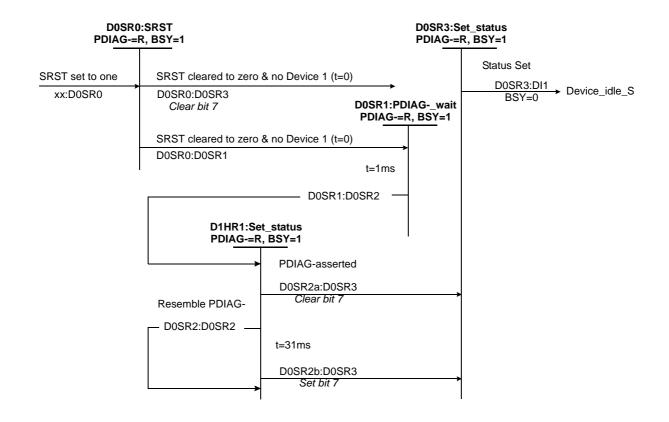

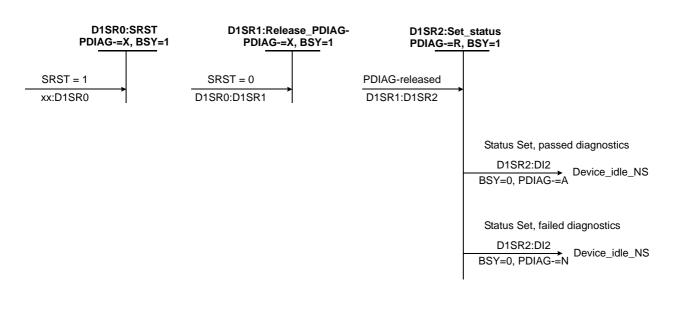

| <ul> <li>6.2.3 Security mode operation from power-on</li> <li>6.2.4 Password lost</li> <li>6.3 SMART Feature Set</li> <li>6.3.1 Sub Command Set</li> <li>6.3.2 SMART Data Structure(READ DATA(Doh))</li> <li>6.3.3 Threshold Sector Size</li> <li>6.4 R/B Status in SLEEP command</li> <li>6.5 SET FEATURES</li> <li>6.5.1 SET FEATURES Register Value</li> <li>6.6 SET MAX</li> <li>6.6.1 SET MAX FEATURES Register Value</li> <li>6.7 Identify Device Data</li> <li>6.8 Hardware Reset State Diagram</li> <li>6.9 Software Reset State Diagram</li> </ul> 7. Ordering Information | 54<br>55<br>55<br>55<br>56<br>56<br>56<br>57<br>57<br>58<br>58<br>59<br>61<br>62 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 6.2.4 Password lost<br>6.3 SMART Feature Set<br>6.3.1 Sub Command Set<br>6.3.2 SMART Data Structure(READ DATA(Doh))<br>6.3.3 Threshold Sector Size<br>6.4 R/B Status in SLEEP command<br>6.5 SET FEATURES<br>6.5.1 SET FEATURES Register Value<br>6.6 SET MAX<br>6.6.1 SET MAX FEATURES Register Value<br>6.7 Identify Device Data<br>6.8 Hardware Reset State Diagram                                                                                                                                                                                                              | 54<br>55<br>55<br>56<br>56<br>56<br>57<br>57<br>57<br>58<br>58<br>58<br>59<br>61 |

| <ul> <li>6.2.4 Password lost</li> <li>6.3 SMART Feature Set <ul> <li>6.3.1 Sub Command Set</li> <li>6.3.2 SMART Data Structure(READ DATA(Doh))</li> <li>6.3.3 Threshold Sector Size</li> </ul> </li> <li>6.4 R/B Status in SLEEP command</li> <li>6.5 SET FEATURES <ul> <li>6.5.1 SET FEATURES Register Value</li> </ul> </li> <li>6.6 SET MAX <ul> <li>6.6.1 SET MAX FEATURES Register Value</li> </ul> </li> <li>6.7 Identify Device Data</li> </ul>                                                                                                                              | 54<br>55<br>55<br>56<br>56<br>56<br>57<br>57<br>57<br>58<br>58<br>58<br>59<br>61 |

| 6.2.4 Password lost<br>6.3 SMART Feature Set<br>6.3.1 Sub Command Set<br>6.3.2 SMART Data Structure(READ DATA(Doh))<br>6.3.3 Threshold Sector Size<br>6.4 R/B Status in SLEEP command<br>6.5 SET FEATURES<br>6.5.1 SET FEATURES Register Value<br>6.6 SET MAX<br>6.6.1 SET MAX FEATURES Register Value                                                                                                                                                                                                                                                                              | 54<br>55<br>55<br>56<br>56<br>56<br>57<br>57<br>57<br>58<br>58                   |

| <ul> <li>6.2.4 Password lost</li> <li>6.3 SMART Feature Set</li> <li>6.3.1 Sub Command Set</li> <li>6.3.2 SMART Data Structure(READ DATA(Doh))</li> <li>6.3.3 Threshold Sector Size</li> <li>6.4 R/B Status in SLEEP command</li> <li>6.5 SET FEATURES</li> <li>6.5.1 SET FEATURES Register Value</li> <li>6.6 SET MAX</li> </ul>                                                                                                                                                                                                                                                   | 54<br>55<br>55<br>56<br>56<br>56<br>57<br>57<br>57                               |

| 6.2.4 Password lost<br>6.3 SMART Feature Set<br>6.3.1 Sub Command Set<br>6.3.2 SMART Data Structure(READ DATA(Doh))<br>6.3.3 Threshold Sector Size<br>6.4 R/B Status in SLEEP command<br>6.5 SET FEATURES<br>6.5.1 SET FEATURES Register Value                                                                                                                                                                                                                                                                                                                                      | 54<br>55<br>55<br>55<br>56<br>56<br>57<br>57                                     |

| 6.2.4 Password lost<br>6.3 SMART Feature Set<br>6.3.1 Sub Command Set<br>6.3.2 SMART Data Structure(READ DATA(Doh))<br>6.3.3 Threshold Sector Size<br>6.4 R/B Status in SLEEP command<br>6.5 SET FEATURES                                                                                                                                                                                                                                                                                                                                                                           | 54<br>55<br>55<br>55<br>56<br>56<br>56<br>57                                     |

| <ul> <li>6.2.4 Password lost</li> <li>6.3 SMART Feature Set</li> <li>6.3.1 Sub Command Set</li> <li>6.3.2 SMART Data Structure(READ DATA(Doh))</li> <li>6.3.3 Threshold Sector Size</li> <li>6.4 R/B Status in SLEEP command</li> </ul>                                                                                                                                                                                                                                                                                                                                             | 54<br>55<br>55<br>55<br>56<br>56                                                 |

| 6.2.4 Password lost<br>6.3 SMART Feature Set<br>6.3.1 Sub Command Set<br>6.3.2 SMART Data Structure(READ DATA(Doh))<br>6.3.3 Threshold Sector Size                                                                                                                                                                                                                                                                                                                                                                                                                                  | 54<br>55<br>55<br>55<br>55<br>56                                                 |

| 6.2.4 Password lost<br>6.3 SMART Feature Set<br>6.3.1 Sub Command Set<br>6.3.2 SMART Data Structure(READ DATA(Doh))                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 54<br>55<br>55<br>55                                                             |

| 6.2.4 Password lost<br>6.3 SMART Feature Set<br>6.3.1 Sub Command Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 54<br>55<br>55                                                                   |

| 6.2.4 Password lost<br>6.3 SMART Feature Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 54<br>55                                                                         |

| 6.2.4 Password lost                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 54                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                                                                                |

| 6.2.3 Security mode operation from power-on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 54                                                                               |

| 6.2.2 Initial setting of the user password                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 54                                                                               |

| 6.2.1 Security mode default setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 54                                                                               |

| 6.2 Security Feature Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 54                                                                               |

| 6.1 Supporting ATA Command Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 53<br>53                                                                         |

| 6 Command Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 50                                                                               |

| 5.14.6.6 ERR(Error)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 52                                                                               |

| 5.14.6.5 Obsolete bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 51                                                                               |

| 5.14.6.4 DRQ(Data request)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 51                                                                               |

| 5.14.6.3 Command dependent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 51                                                                               |

| 5.14.6.2 DRDY(Device ready)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51                                                                               |

| 5.14.6.1 BSY(Busy)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 50                                                                               |

| 5.14.6 Field/bit description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 49                                                                               |

| 5.14.5 Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 49                                                                               |

| 5.14.4 Effect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 49                                                                               |

| 5.14.3 Access Restrictions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 49                                                                               |

| 5.14.2 Direction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 49                                                                               |

| 5.14.1 Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 49                                                                               |

## **TABLE OF CONTENTS**

## **1. General Description**

The NSSD(Nand Flash-based Solid State Disk) of Samsung Electronics is fully consist of semiconductor device and using NAND Flash Memory which has a high reliability and a high technology for a storage media.

As the NSSD doesn't have a moving parts such as platter(disk) and head media, it gives a good solution in a sub. note PC and Tablet PC for a storage device with a high performance and a power consumption and a small form factor.

Also it gives rugged features in industrial PC with an extreme environment and an increased MTBF.

For an easy adoption, the NSSD has a same host interface with HDD and has a same physical dimension.

#### •Density

- 8GB,16GB,32GB NSSD are available

#### •Form Factor

- Small Type (56 x 48 x 3.8mm) : 8/16GB

- Slim Type (53.60 x 70.60 x 3.00mm) :32GB

- (53.60 x 70.60 x 2.50mm) : 4/8/16GB

#### Host interface

- PIO Mode 0 to 4.

- Multiword DMA

- Up to ATA5 UDMA Mode4 (66MHz)

#### •Performance

- Host Interface : Max 66MB/s

- Sustained Data Read : Max 56MB/s

- Sustained Data Write : Max 32MB/s

#### •Power consumption

- Active : Typical 200mA

- Idle : Typical 20mA

- Standby : Typical 20mA

#### •Temperature

- Operating : -25'C ~ 85'C

#### Shock

- Operating : 1500G, duration 0.5ms, Half Sine Wave

- Vibration : 20G Peak, 10~2000Hz,(12Cycle/Axis)x3 Axis

#### •MTBF

- 1,000,000 Hours

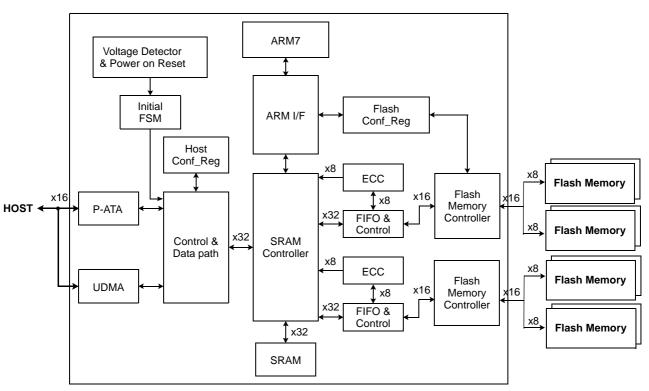

### NSSD Functional Block Diagram

## 2. Physical Specifications

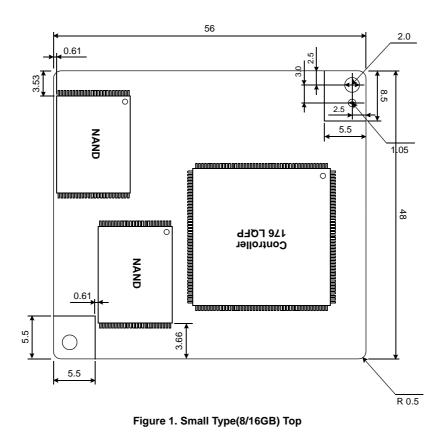

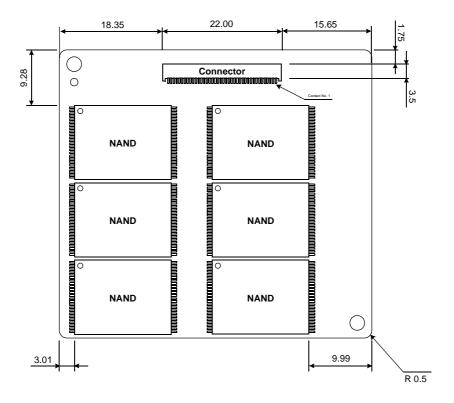

## 2.1 Small Type Physical Dimensions (8/16GB)

Figure 3. Small Type(8/16GB) Side

8

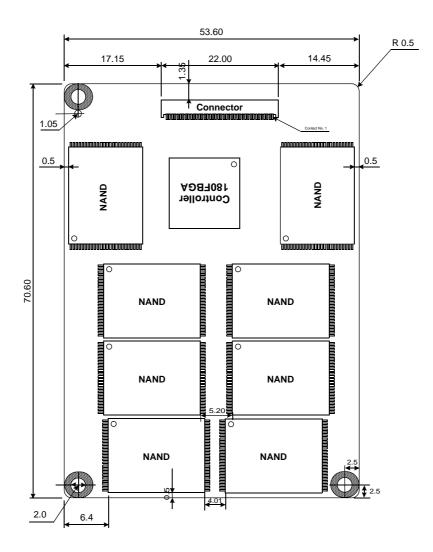

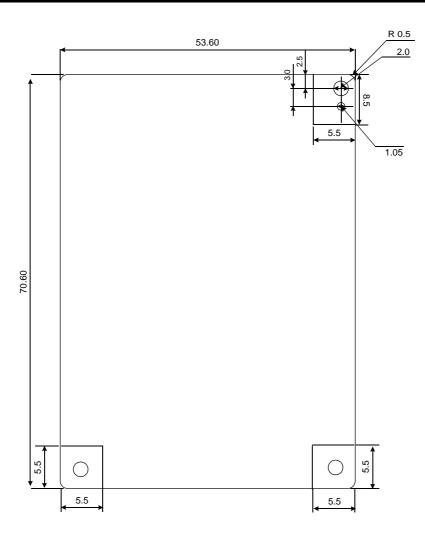

## 2.2 Slim Type Physical Dimensions (4/8/16GB)

Figure 4. Slim Type(4/8/16GB) Top

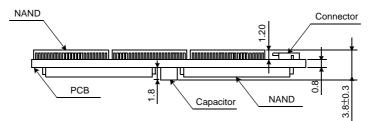

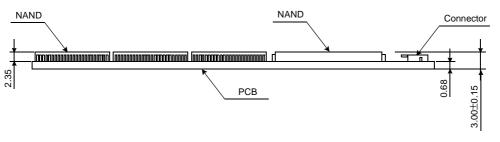

Figure 6. Slim Type(4/8/16GB) Side

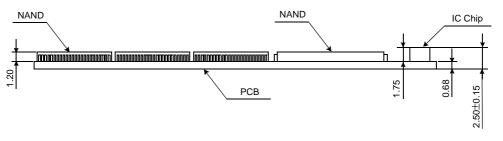

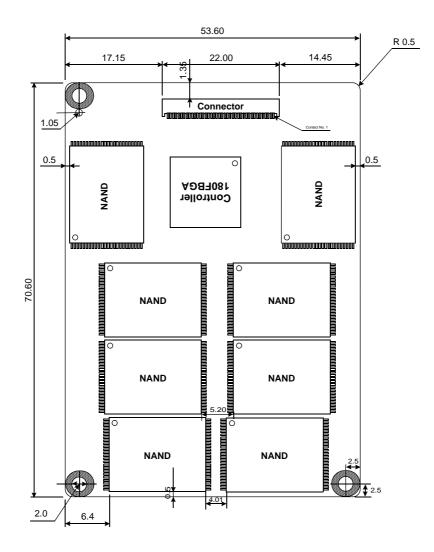

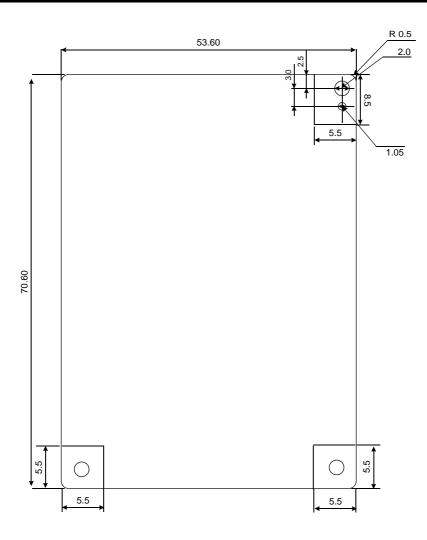

## 2.3 Slim Type Physical Dimensions (32GB)

Figure 7. Slim Type(32GB) Top

Figure 9. Slim Type(32GB) Side

## 3. Product Specifications

### 3.1 System Interface and Configuration

• PIO 0~4 mode,

• Up to ATA5 and UDMA mode4(Ultra DMA66)

• Fully compatible with ATA5 Specification

### 3.2 System Performance

(Sandra 2005, 32GB)

| Read / Write            | Performance(MB/s) |

|-------------------------|-------------------|

| Random Read Sector      | Max 56            |

| Random Write Sector     | Max 13            |

| Sequential Read Sector  | Max 56            |

| Sequential Write Sector | Max 32            |

### 3.3 System Power Consumption

(32GB)

| Current | Typical(mA) |

|---------|-------------|

| Active  | 200         |

| Idle    | 20          |

| Standby | 20          |

### 3.4 System Reliability

| MTBF 1,000,000 Hours |      |                 |

|----------------------|------|-----------------|

|                      | MTBF | 1.000.000 Hours |

## **3.5 Environmental Specifications**

| Features    | Operating Non-Operating                         |  |  |

|-------------|-------------------------------------------------|--|--|

| Temperature | -25'C ~ 85'C -40'C ~ 85'C                       |  |  |

| Humidity    | 0'C to 55'C / 90~98% RH, 10cycles               |  |  |

| Vibration   | 20G Peak, 10 ~ 2000Hz, (12cycle / Axis) x3 Axis |  |  |

| Shock       | 1500G, duration 0.5ms, Half Sine Wave           |  |  |

## 4. Electrical Specification

**4.1 ZIF Connector Dimensions**

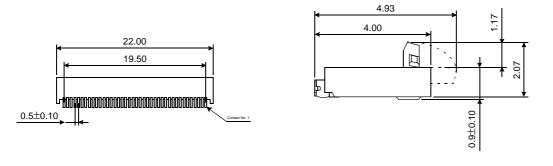

#### Figure 7. Connector Top

Figure 8. Connector Side

\*ZIF: Zero Insertion Force

## 4.2 Pin Assignment

| Pin No | Signals  | Pin No | Signals  |

|--------|----------|--------|----------|

| 1      | Reserved | 21     | GROUND   |

| 2      | Reserved | 22     | DMARQ    |

| 3      | RESET    | 23     | GROUND   |

| 4      | GROUND   | 24     | DIOW     |

| 5      | DD7      | 25     | DIOR     |

| 6      | DD8      | 26     | GROUND   |

| 7      | DD6      | 27     | IORDY    |

| 8      | DD9      | 28     | GROUND   |

| 9      | DD5      | 29     | DMACK    |

| 10     | DD10     | 30     | INTRQ    |

| 11     | DD4      | 31     | DA1      |

| 12     | DD11     | 32     | PDIAG    |

| 13     | DD3      | 33     | DA0      |

| 14     | DD12     | 34     | DA2      |

| 15     | DD2      | 35     | CS0      |

| 16     | DD13     | 36     | CS1      |

| 17     | DD1      | 37     | DASP     |

| 18     | DD14     | 38     | 3.3V     |

| 19     | DD0      | 39     | 3.3V     |

| 20     | DD15     | 40     | Reserved |

## 4.3 Signal Descriptions

"I" of I/O type represents an input signal from the device and "O" represents an output signal from the device.

| Signal name  | Pin NO   | Туре | Description                                                                                                                                                                                                                                                                                                                |

|--------------|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET        | 3        | I    | This is a reset signal output from the host system and to be used for inter-<br>face logic circuit.                                                                                                                                                                                                                        |

| DD0 - DD15   | 5-20     | I/O  | This is a 16bit bi-directional data bus. The lover 8 bits are used for register acess other that data register.                                                                                                                                                                                                            |

| DIOW         | 24       |      | This rising edge of this Write Strobe signal clocks data from the host data bus into a register on the device.                                                                                                                                                                                                             |

| STOP*        | 24       | I    | Assertion of this signal by the host during an Ultra DMA burst signals the termination of the Ultra DMA burst.                                                                                                                                                                                                             |

| DIOR         |          |      | Activating this Read Strobe signal enables data from a register on the device to be clocked onto the host data bus. The rising edge of this signal latches data at the host.                                                                                                                                               |

| HDMARDY*     | 25       | I    | This signal is a flow control signal for Ultra DMA Read. Host asserts this signal, and indicates that the host is ready to receive Ultra DMA read data.                                                                                                                                                                    |

| HSTROBE*     |          |      | This signal is Write data strobe signal from the host for an Ultra DMA Write.<br>Both the rising and falling edge latch the data from DD(15:0) into the<br>device.                                                                                                                                                         |

| IORDY        |          |      | This signal is used to temporarily stop the host register access(read or write) when the device is not ready to respond to a data transfer request.                                                                                                                                                                        |

| DDMARDY*     | 27       | 0    | This signal is flow control signal for Ultra DMA Write. Device asserts this signal, and indicates that the device is ready to receive Ultra DMA Write data.                                                                                                                                                                |

| DSTROBE*     |          |      | This signal is the data in strobe signal from the device for an Ultra DMA Read. Both the rising and falling edge latch the data from DD(15:0) into the host.                                                                                                                                                               |

| INTRQ        | 30       | 0    | This is an interrupt signal for the host system. This signal is asserted by a selected device when the nIEN bit in the Device Control Register is "0". In other cases, this signal should be a high impedance state.                                                                                                       |

| DA0-2        | 31,33,34 | l    | This is a register address signal from the host system.                                                                                                                                                                                                                                                                    |

| PDIAG:CBLID* | 32       | I/O  | The host shall wait until the power on or hardware reset sequence is com-<br>plete for all devices on the cable;                                                                                                                                                                                                           |

| CS0          | 35       | I    | This device chip selection signal is used to select the Control Block Registers from the host system.                                                                                                                                                                                                                      |

| CS1          | 36       | I    | This device chip selection signal is used to select the Command Block Registers from the host system.                                                                                                                                                                                                                      |

| DASP         | 37       | I/O  | This signal indicates that a device is active when the power is turned on.<br>Upon receipt of a command from the host, the device asserts this signal. At<br>command completion, the device de-asserts this signal.                                                                                                        |

| DMARQ        | 22       | 0    | The device shall assert this signal, used for DMA data transfers between host and device, when it is ready to transfer data.                                                                                                                                                                                               |

| DMACK        | 29       | I    | The host in response to DMARQ to either acknowledge that data has been accepted, or that data is available shall use this signal.                                                                                                                                                                                          |

| DEVADR       | 40       | I    | The device is configured as either Device 0(Master) or Device 1(Slave) depending upon the signal level of 40 pin DEVADR signal.<br>- When used as Device 1(Master), DEVADR is open<br>- When used as Device 1(Slave), the host shall have pull-up resistor. Rec-<br>ommended pull-up register is 10K ohm based on +3.3Vcc. |

### 4.4 DC Characteristics

### 4.4.1 Absolute Maximum Ratings

| Characteristics      | Symbol                            | Rating      | Unit |

|----------------------|-----------------------------------|-------------|------|

| DC Supply Voltage    | V <sub>DD</sub>                   | -0.3 to 4.6 | V    |

| Input/Output Voltage | V <sub>IN</sub> /V <sub>OUT</sub> | 3.8         | V    |

| DC Input Current     | I <sub>IN</sub>                   | +/- 200     | mA   |

| Storage Temperature  | T <sub>STG</sub>                  | -40 to 85   | °C   |

### 4.4.2 Recommended Operating Conditions

| Characteristics       | Symbol                            | Rating     | Unit |

|-----------------------|-----------------------------------|------------|------|

| DC Supply Voltage     | V <sub>DD</sub>                   | 3.0 to 3.6 | V    |

| Input/Output Voltage  | V <sub>IN</sub> /V <sub>OUT</sub> | 3.0 to 3.6 | V    |

| Operating Temperature | T <sub>OPR</sub>                  | -25 to 85  | °C   |

## 4.4.3 Electrical Characteristics - Normal I/O

### Vdd = 3.0 to 3.6(V), Ta = 25(°C), Vext = 5V $\pm$ 0.25V

| Characteristics                  | Symbol          | Min                                              | Тур                              | Max        | Unit |           |          |

|----------------------------------|-----------------|--------------------------------------------------|----------------------------------|------------|------|-----------|----------|

| Input High Current               | I <sub>IH</sub> | V <sub>IN</sub> = V <sub>DD</sub><br>Pull - Down | Normal<br>Down                   | -10<br>10  | -    | 10<br>60  | uA<br>uA |

| Input Low Current                | I <sub>IL</sub> | V <sub>IN</sub> = V <sub>SS</sub><br>Pull - Up   | Normal<br>Up                     | -10<br>-60 | -    | 10<br>-10 | uA<br>uA |

| Input High Voltage               | V <sub>IH</sub> | CM                                               | 2.0                              | -          | -    | V         |          |

| Input Low Voltage                | V <sub>IL</sub> | CM                                               | -                                | -          | 0.8  | V         |          |

| Output High Voltage              | V <sub>OH</sub> | 6mA Buffer,                                      | 2.4                              | -          | -    | V         |          |

| Output Low Voltage               | V <sub>OL</sub> | 6mA Buffer                                       | -                                | -          | 0.4  | V         |          |

| Tri-state Output Leakage Current | I <sub>OZ</sub> | V <sub>OUT</sub> = V                             | <sub>DD</sub> or V <sub>SS</sub> | -10        | -    | 10        | uA       |

#### NOTE:

\* Schmitt Trigger test condition :  $V_{DD}$  = 3.0 to 3.6(V), Ta = 25(°C)

#### Characteristic:

These DC parameters guarantee the I/O cell characteristic at the static state only, not at the dynamic state.

### 4.5 AC Characteristics

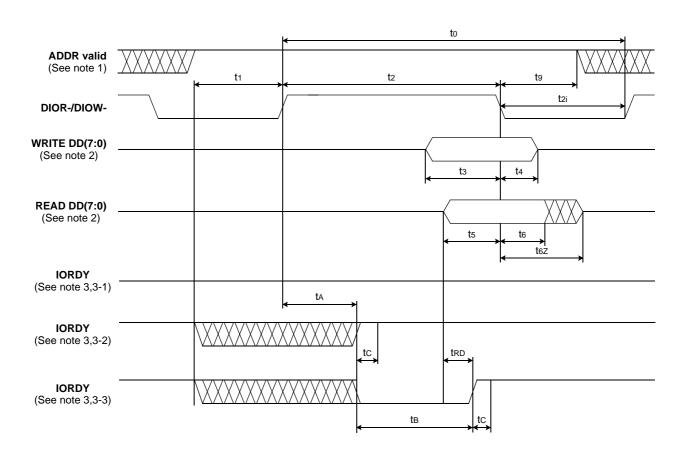

#### 4.5.1 Register Transfers

Figure 1 defines the relationships between the interface signals for register transfers. Peripherals reporting support for PIO mode 3 or 4 shall power-up in a PIO mode 0,1, or 2.

For PIO modes 3 and above, the minimum value of  $t_0$  is specified by word 68 in the IDENTIFY DEVICE parameter list. Table 1 defines the minimum value that shall be placed in word 68.

Both hosts and devices shall support IORDY when PIO mode 3 or 4 are the currently selected mode of operation.

#### NOTE:

- 1. Device address consists of signals CS0-, CS1- and DA(2:0)

- 2. Data consists of DD(7:0)

- The negation of IORDY by the device is used to extend the register transfer cycle. The determination of whether the cycle is to be extended is made by the host after t<sub>A</sub> from the assertion of DIOR- or DIOW-. The assertion and negation of IORDY are described in the following three cases:

3-1. Device never negates IORDY, devices keeps IORDY released: no wait is generated.

- 3-2. Device negates IORDY before  $t_A$ , but causes IORDY to be asserted before  $t_A$ .

- IORDY is released prior to negation and may be asserted for no more than 5ns before release: no wait generated.

- 3-3. Device negates IORDY before t<sub>A</sub>. IORDY is released prior to negation and may be asserted for no more than 5ns before release: wait generated. The cycle completes after IORDY is reasserted. For cycles where a wait is generated and DIOR- is asserted, the device shall place read data on DD(7:0) for t<sub>RD</sub> before asserting IORDY.

- 4. DMACK- shall remain negated during a register transfer.

|                 | Register transfer timing parameters                                   |     | Mode Ons | Mode 1ns | Mode 2ns | Mode 3ns | Mode 4ns | Note  |

|-----------------|-----------------------------------------------------------------------|-----|----------|----------|----------|----------|----------|-------|

| t <sub>0</sub>  | Cycle time                                                            | min | 600      | 383      | 330      | 180      | 120      | 1,4,5 |

| t <sub>1</sub>  | Address valid to DIOR-/DIOW- setup                                    | min | 70       | 50       | 30       | 30       | 25       |       |

| t <sub>2</sub>  | DIOR-/DIOW- pulse width 8bit                                          | min | 290      | 290      | 290      | 80       | 70       | 1     |

| t <sub>2i</sub> | DIOR-/DIOW- recovery time                                             | min | -        | -        | -        | 70       | 25       | 1     |

| t <sub>3</sub>  | DIOW- data setup                                                      | min | 60       | 45       | 30       | 30       | 20       |       |

| t <sub>4</sub>  | DIOW- data hold                                                       | min | 30       | 20       | 15       | 10       | 10       |       |

| t <sub>5</sub>  | DIOR- data setup                                                      | min | 50       | 35       | 20       | 20       | 20       |       |

| t <sub>6</sub>  | DIOR- data hold                                                       | min | 5        | 5        | 5        | 5        | 5        |       |

| t <sub>6Z</sub> | DIOR- data tristate                                                   | max | 30       | 30       | 30       | 30       | 30       | 2     |

| t <sub>9</sub>  | DIOR-/DIOW- to address valid hold                                     | min | 20       | 15       | 10       | 10       | 10       |       |

| t <sub>RD</sub> | Read Data Valid to IORDY active (if IORDY initially low after $t_A$ ) | min | 0        | 0        | 0        | 0        | 0        |       |

| t <sub>A</sub>  | IORDY setup time                                                      |     | 35       | 35       | 35       | 35       | 35       | 3     |

| t <sub>B</sub>  | IORDY pulse width                                                     | max | 1250     | 1250     | 1250     | 1250     | 1250     |       |

| t <sub>C</sub>  | IORDY assertion to release                                            | max | 5        | 5        | 5        | 5        | 5        |       |

#### Table 1 - Register transfer to/from device

NOTE:

1. t<sub>0</sub> is the minimum total cycle time, t<sub>2</sub> is the minimum DIOR-/DIOW- assertion time, and A host implementation shall lengthen t<sub>2</sub> and/or t<sub>2i</sub> to ensure that t<sub>0</sub> is equal to or greater than the value reported in the devices INDENTIFY DEVICE data. A device implementation shall support any legal host implementation.

2. This parameter specifies the time from the negation edge of DIOR- to the time that the data bus is released by the device.

3. The delay from the activation of DIOR- or DIOW- until the state of IORDY is first sampled. If IORDY is inactive then the host shall wait until IORDY negated at the t<sub>A</sub> after the activation of DIOR- or DIOW-, then t<sub>5</sub> shall be met and t<sub>RD</sub> is not applicable. If the device is driving IORDY negated at the time t<sub>A</sub> after the activation of DIOR- or DIOW-, then t<sub>RD</sub> shall be met and t<sub>5</sub> is not applicable.

4. ATA/ATAPI standards prior to ATA/ATAPI-5 inadvertently specified an incorrect value for mode2 time to by utilizing the 16-bit PIO value.

5. Mode shall be selected no faster than the highest mode supported by the slowest device.

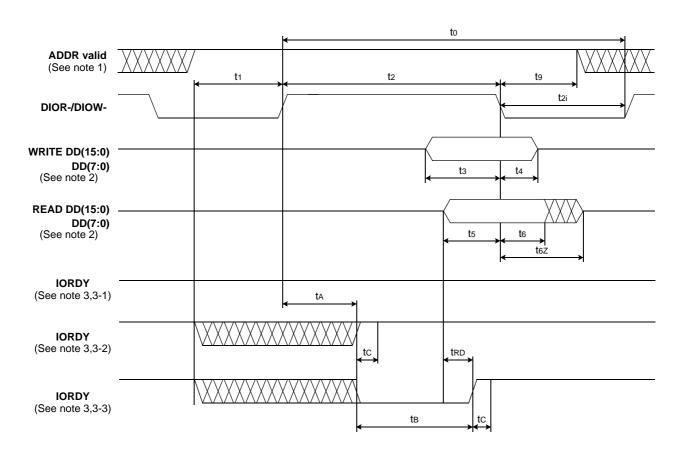

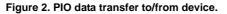

#### 4.5.2 PIO Data Transfers

Figure 2 defines the relationships between the interface signals for PIO data transfers. Peripherals reporting support for PIO mode 3 or 4 shall power-up in a PIO mode 0,1, or 2.

For PIO modes 3 and above, the minimum value of  $t_0$  is specified by word 68 in the IDENTIFY DEVICE parameter list. Table 2 defines the minimum value that shall be placed in word 68.

IORDY shall be supported when PIO mode 3 or 4 are the current mode of operation.

#### NOTE:

- 1. Device address consists of signals CS0-, CS1- and DA(2:0)

- 2. Data consists of DD(15:0) for all devices except devices implementing the CFA feature set when 8-bit transfers is enabled. In that case, data consists of DD(7:0)

The negation of IORDY by the device is used to extend the PIO cycle. The determination of whether the cycle is to be extended is made by the host after t<sub>A</sub> from the assertion of DIOR- or DIOW-. The assertion and negation of IORDY are described in the following three cases: 3-1. Device never negates IORDY, devices keeps IORDY released: no wait is generated.

3-2. Device negates IORDY before  $t_A$ , but causes IORDY to be asserted before  $t_A$ .

IORDY is released prior to negation and may be asserted for no more than 5ns before release: no wait generated.

- 3-3. Device negates IORDY before t<sub>A</sub>. IORDY is released prior to negation and may be asserted for no more than 5ns before release: wait generated. The cycle completes after IORDY is reasserted. For cycles where a wait is generated and DIOR- is asserted, the device shall place read data on DD(7:0) for t<sub>RD</sub> before asserting IORDY.

- 4. DMACK- shall be negated during a PIO data transfer.

|                 | PIO timing parameters                                                 |     | Mode Ons | Mode 1ns | Mode 2ns | Mode 3ns | Mode 4ns | Note |

|-----------------|-----------------------------------------------------------------------|-----|----------|----------|----------|----------|----------|------|

| t <sub>0</sub>  | Cycle time                                                            | min | 600      | 383      | 240      | 180      | 120      | 1,4  |

| t <sub>1</sub>  | Address valid to DIOR-/DIOW- setup                                    | min | 70       | 50       | 30       | 30       | 25       |      |

| t <sub>2</sub>  | DIOR-/DIOW-                                                           | min | 165      | 125      | 100      | 80       | 70       | 1    |

| t <sub>2i</sub> | DIOR-/DIOW- recovery time                                             | min | -        | -        | -        | 70       | 25       | 1    |

| t <sub>3</sub>  | DIOW- data setup                                                      | min | 60       | 45       | 30       | 30       | 20       |      |

| t <sub>4</sub>  | DIOW- data hold                                                       | min | 30       | 20       | 15       | 10       | 10       |      |

| t <sub>5</sub>  | DIOR- data setup                                                      | min | 50       | 35       | 20       | 20       | 20       |      |

| t <sub>6</sub>  | DIOR- data hold                                                       | min | 5        | 5        | 5        | 5        | 5        |      |

| t <sub>6Z</sub> | DIOR- data tristate                                                   | max | 30       | 30       | 30       | 30       | 30       | 2    |

| t <sub>9</sub>  | DIOR-/DIOW- to address valid hold                                     | min | 20       | 15       | 10       | 10       | 10       |      |

| t <sub>RD</sub> | Read Data Valid to IORDY active (if IORDY initially low after $t_A$ ) | min | 0        | 0        | 0        | 0        | 0        |      |

| t <sub>A</sub>  | IORDY setup time                                                      |     | 35       | 35       | 35       | 35       | 35       | 3    |

| t <sub>B</sub>  | IORDY pulse width                                                     | max | 1250     | 1250     | 1250     | 1250     | 1250     |      |

| t <sub>C</sub>  | IORDY assertion to release                                            | max | 5        | 5        | 5        | 5        | 5        |      |

#### Table 2 - PIO data transfer to/from device

#### NOTE:

1.  $t_0$  is the minimum total cycle time,  $t_2$  is the minimum DIOR-/DIOW- assertion time, and  $t_{21}$  is the minimum DIOR-/DIOW- negation time. A host implementation shall lengthen  $t_2$  and/or  $t_{2i}$  to ensure that  $t_0$  is equal to or greater than the value reported in the devices IDENTIFY DEVICE data. A device implementation shall support any legal host implementation.

2. This parameter specifies the time from the negation edge of DIOR- to the time that the data bus is released by the device.

3. The delay from the activation of DIOR- or DIOW- until the state of IORDY is first sampled. If IORDY is inactive then the host shall wait until IORDY is active before the PIO cycle is completed. If the device is not driving IORDY negated at the t<sub>A</sub> after the activation of DIOR- or DIOW-, then t<sub>5</sub> shall be met and t<sub>RD</sub> is not applicable. If the device is driving IORDY negated at the time t<sub>A</sub> after the activation of DIOR- or DIOW-, then t<sub>5</sub> shall be met and t<sub>5</sub> is not applicable.

4. Mode may be selected at the highest mode for the device if CS(1:0) and AD(2:0) do not change between read or write cycles or selected at the highest mode supported by the slowest device if CS(1:0) or AD(2:0) do change between read or write cycles.

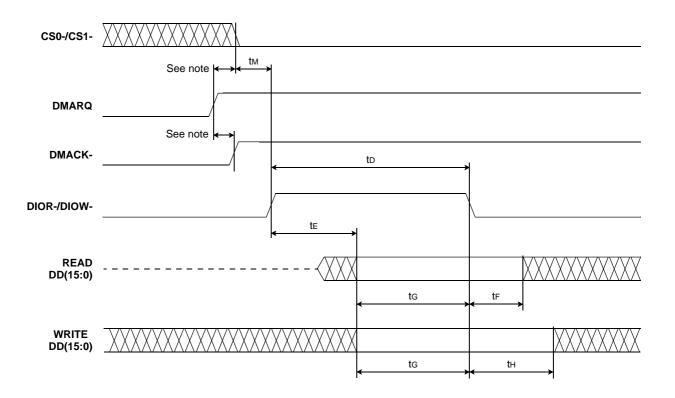

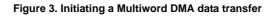

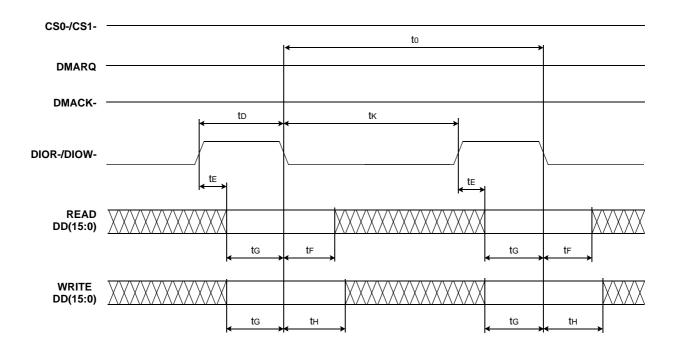

### 4.5.3 Multiword DMA Data Transfers

Figure 3 through Figure 6 define the timing associated with Multiword DMA transfers.

For Multiword DMA modes 1 and above, the minimum value of  $t_0$  is specified by word 65 in the IDENTIFY DEVICE parameter list. Table 3 defines the minimum value that shall be placed in word 65.

Devices shall power-up with mode 0 as the default Multiword DMA mode.

#### Table 3 - Multiword DMA data transfer

|                 | Multiword DMA timing parameters  | Mode Ons | Mode 1ns | Mode 2ns | Note |          |

|-----------------|----------------------------------|----------|----------|----------|------|----------|

| t <sub>0</sub>  | Cycle time                       | min      | 480      | 150      | 120  | see note |

| t <sub>D</sub>  | DIOR-/DIOW- asserted pulse width | min      | 215      | 80       | 70   | see note |

| t <sub>E</sub>  | DIOR- data access                | max      | 150      | 60       | 50   |          |

| t <sub>F</sub>  | DIOR- data hold                  | min      | 5        | 5        | 5    |          |

| t <sub>G</sub>  | DIOR-/DIOW-data setup            | min      | 100      | 30       | 20   |          |

| t <sub>H</sub>  | DIOW- data hold                  | min      | 20       | 15       | 10   |          |

| tl              | DMACK to DIOR-/DIOW- data setup  | min      | 0        | 0        | 0    |          |

| tj              | DIOR-/DIOW- to DMACK hold        | min      | 20       | 5        | 5    |          |

| t <sub>KR</sub> | DIOR- negated pulse width        | min      | 50       | 50       | 25   | see note |

| t <sub>KW</sub> | DIOW- negated pulse width        | min      | 215      | 50       | 25   | see note |

| t <sub>LR</sub> | DIOR- to DMARQ delay             | max      | 120      | 40       | 35   |          |

| t <sub>LW</sub> | DIOW- to DMARQ delay             | max      | 40       | 40       | 35   |          |

| t <sub>M</sub>  | CS(1:0) valid to DIOR-/DIOW-     | min      | 50       | 30       | 25   |          |

| t <sub>N</sub>  | CS(1:0) hold                     | min      | 15       | 10       | 10   |          |

| tz              | DMACK- to read data released     | max      | 20       | 25       | 25   |          |

#### NOTE:

>  $t_0$  is the minimum total cycle time,  $t_D$  is the minimum DIOR-/DIOW- assertion time, and  $t_K$  ( $t_{KR}$  or  $t_{Kw}$ , as appropriate) is the minimum DIOR-/DIOWnegation time. A host shall lengthen  $t_D$  and/or  $t_K$  to ensure that  $t_0$  is equal to the value reported in the devices IDENTIFY DEVICE data.

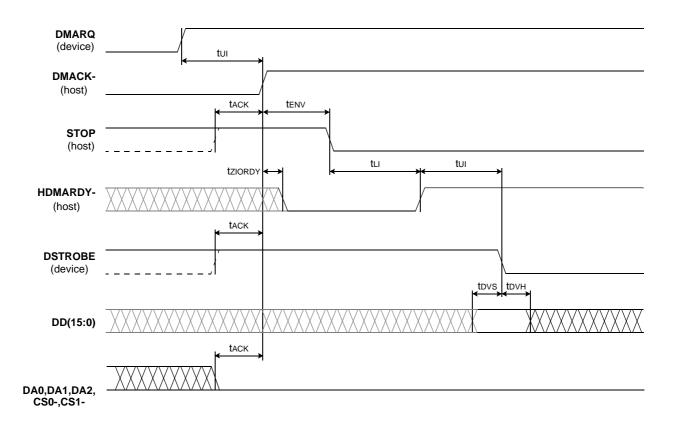

### 4.5.3.1 Initiating a Multiword DMA data burst

The values for the timings for each of the Multiword DMA modes are contained in Table 50.

#### NOTE:

The host shall not assert DMACK- or negate both CS0 and CS1 until the assertion of DMARQ is detected. The maxium time from the assertion of DMARQ to the assertion of DMACK- or the negation of both CS0 and CS1 is not defined.

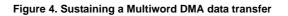

### 4.5.3.2 Sustaining a Multiword DMA data burst

The values for the timings for each of the Multiword DMA modes are contained in Table 50.

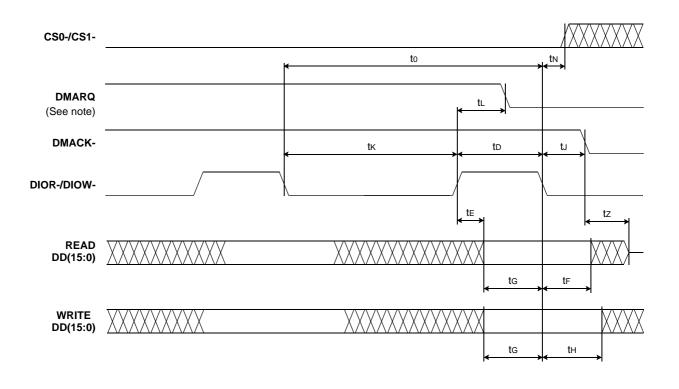

### 4.5.3.3 Device terminating a Multiword DMA data burst

The values for the timings for each of the Multiword DMA modes are contained in Table 50.

#### Figure 5. Device terminating a Multiword DMA data transfer

NOTE:

To terminate the data burst, the Host shall negate DMARQ within the tL of the assertion of the current DIOR- or DIOW- pulse. The last data word for the burst shall then be transferred by the negation of the current DIOR- or DIOW- pulse. If all data for the command has not been transferred, the Host shall reassert DMARQ again at any later time to resume the DMA operation.

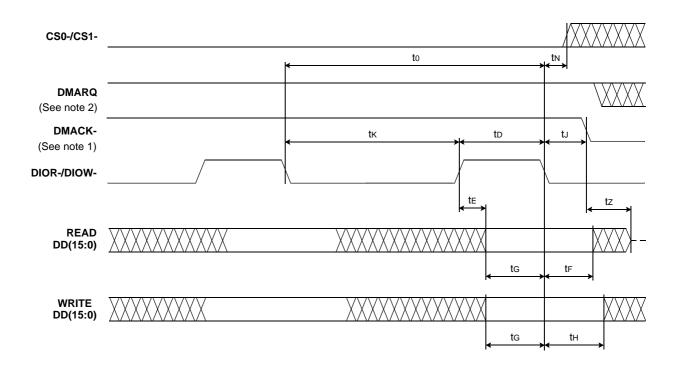

### 4.5.3.4 Host terminating a Multiword DMA data burst

The values for the timings for each of the Multiword DMA modes are contained in Table 50.

#### Figure 6. Host terminating a Multiword DMA data transfer

#### NOTE:

1. To terminate the transmission of a data burst, the host shall negate DMACK- within the specified time after a DIOR- or DIOW- pulse. No further DIOR- or DIOW- pulses shall be asserted for this burst.

2. If the device is able to continue the transfer of data, the Host may leave DMARQ asserted and wait for the host to reassert DMACK- or may negate DMARQ at any time after detecting that DMACK- has been negated.

### 4.5.4 Ultra DMA data burst

Figure 7 through Figure 16 define the timings associated with all phases of Ultra DMA bursts. Table 4 contains the values for the timings for each of the Ultra DMA modes.

#### Table 4 - Ultra DMA data burst timing requirements

| Nama                 | Мо  | de O | Мо  | de 1 | Мо  | de 2 | Мо  | de 3 | Mo  | de 4 | Comment                                                                                                                                                    |

|----------------------|-----|------|-----|------|-----|------|-----|------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                 | min | max  | (See Notes 1 and 2)                                                                                                                                        |

| t <sub>2CYCTYP</sub> | 240 |      | 160 |      | 120 |      | 90  |      | 60  |      | Typical sustained average two cycle time                                                                                                                   |

| t <sub>CYC</sub>     | 112 |      | 73  |      | 54  |      | 39  |      | 25  |      | Cycle time allowing for asymmetry and clock varia-<br>tions (from STROBE edge to STROBE edge)                                                              |

| t <sub>2CYC</sub>    | 230 |      | 154 |      | 115 |      | 86  |      | 57  |      | Two cycle time allowing for clock variations (from ris-<br>ing edge to next rising edge or from falling edge to<br>next falling edge of STROBE)            |

| t <sub>DS</sub>      | 15  |      | 10  |      | 7   |      | 7   |      | 5   |      | Data setup time at recipient                                                                                                                               |

| t <sub>DH</sub>      | 5   |      | 5   |      | 5   |      | 5   |      | 5   |      | Data hold time at recipient                                                                                                                                |

| t <sub>DVS</sub>     | 70  |      | 48  |      | 30  |      | 20  |      | 6   |      | Data valid setup time at sender (from data valid until STROBE edge) (See Note 4)                                                                           |

| t <sub>DVH</sub>     | 6   |      | 6   |      | 6   |      | 6   |      | 6   |      | Data valid hold time at sender (from STROBE edge until data may become invalid) (See Note 4)                                                               |

| t <sub>FS</sub>      | 0   | 230  | 0   | 200  | 0   | 170  | 0   | 130  | 0   | 120  | First STROBE time (for device to first negate<br>DSTROBE from STOP during a data in burst)                                                                 |

| t <sub>LI</sub>      | 0   | 150  | 0   | 150  | 0   | 150  | 0   | 100  | 0   | 100  | Limited interlock time (See Note 3)                                                                                                                        |

| t <sub>MLI</sub>     | 20  |      | 20  |      | 20  |      | 20  |      | 20  |      | Interlock time with minimum(See Note 3)                                                                                                                    |

| t <sub>UI</sub>      | 0   |      | 0   |      | 0   |      | 0   |      | 0   |      | Unlimited interlock time (See Note 3)                                                                                                                      |

| t <sub>AZ</sub>      |     | 10   |     | 10   |     | 10   |     | 10   |     | 10   | Maximum time allowed for output drivers to release (from asserted or negated)                                                                              |

| t <sub>ZAH</sub>     | 20  |      | 20  |      | 20  |      | 20  |      | 20  |      | Minimum delay time required for output                                                                                                                     |

| t <sub>ZAD</sub>     | 0   |      | 0   |      | 0   |      | 0   |      | 0   |      | Drivers to assert or negate (from released)                                                                                                                |

| t <sub>ENV</sub>     | 20  | 70   | 20  | 70   | 20  | 70   | 20  | 55   | 20  | 55   | Envelope time (from DMACK- to STOP and<br>HDMARDY- during data in burst initiation and from<br>DMACK to STOP during data out burst initiation)             |

| t <sub>SR</sub>      |     | 50   |     | 30   |     | 20   |     | NA   |     | NA   | STROBE-to-DMARDY- time (if DMARDY- is negated<br>before this long after STROBE edge, the recipient<br>shall receive no more than one additional data word) |

| t <sub>RFS</sub>     |     | 75   |     | 70   |     | 60   |     | 60   |     | 60   | Ready-to-final-STROBE time (no STROBE edges<br>shall be sent this long after negation of DMARDY-)                                                          |

| t <sub>RP</sub>      | 160 |      | 125 |      | 100 |      | 100 |      | 100 |      | Minimum time to assert STOP or negate DMARQ                                                                                                                |

| t <sub>IORDYZ</sub>  |     | 20   |     | 20   |     | 20   |     | 20   |     | 20   | Maximum time before releasing IORDY                                                                                                                        |

| t <sub>ZIORDY</sub>  | 0   |      | 0   |      | 0   |      | 0   |      | 0   |      | Minimum time before driving STROBE (See Note 5)                                                                                                            |

| t <sub>ACK</sub>     | 20  |      | 20  |      | 20  |      | 20  |      | 20  |      | Setup and hold times for DMACK- (before assertion or negation)                                                                                             |

| t <sub>SS</sub>      | 50  |      | 50  |      | 50  |      | 50  |      | 50  |      | Time from STROBE edge to negation of DMARQ or<br>assertion of STOP (when sender terminates a burst)                                                        |

#### NOTE:

1. Timing parameters shall be measured at the connector of the sender or receiver to which the parameter applies. For example, the sender shall stop generating STROBE edges t<sub>RFS</sub> after the negation of DMARDY-. Both STROBE and DMARDY- timing measurements are taken at the connector of the sender.

2. All timing measurement switching points(low to high and high to low) shall be taken at 1.5V.

3.  $t_{UI}$ ,  $t_{MLI}$ , and  $t_{LI}$  indicate sender-to-recipient or recipient-to-sender interlocks, i.e., either sender or recipient is waiting for the other to respond with a signal before proceeding.  $t_{UI}$  is an inlimited interlock that has no maximum time value.  $t_{MLI}$  is a limited time-out that has a defined minimum.  $t_{LI}$  is a limited time-out that has a defined maximum.

4. The test load for  $t_{DVS}$  and  $t_{DVH}$  shall be a lumped capacitor load with no cable or receivers. Timing for  $t_{DVS}$  and  $t_{DVH}$  shall be met for all capacitive loads from 15 to 40 pf where all signals have the same capacitive load value.

5. t<sub>ZIORDY</sub> may be greater than t<sub>ENV</sub> since the device has a pull up on IORDY- giving it a known state when released.

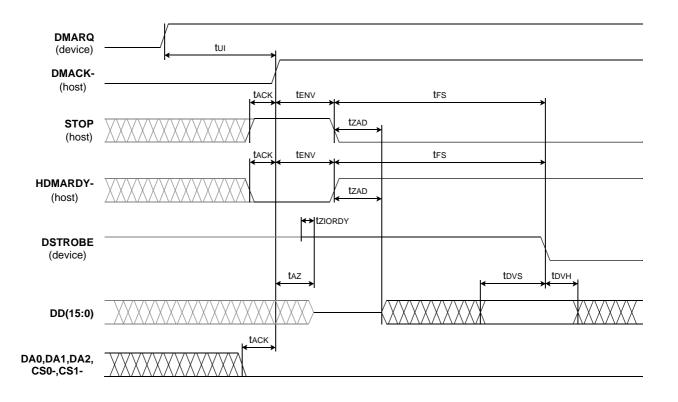

### 4.5.4.1 Initiating an Ultra DMA data-in burst

The values for the timings for each of the Ultra DMA modes are contained in 4.4.4

#### Figure 7. Initiating an Ultra DMA data-in burst

#### NOTE:

1. The definitions for the DIOW-:STOP, DIOR-:HDMARDY-:HSTROBE and IORDY:DDMARDY-:DSTROBE signal lines are not in effect until DMARQ and DMACK are asserted.

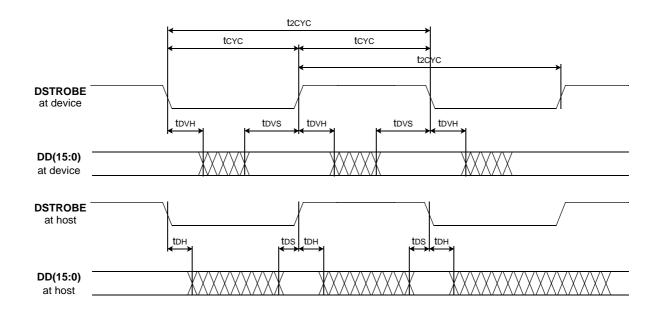

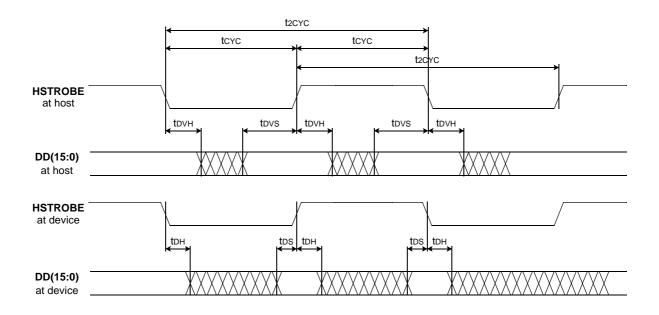

### 4.5.4.2 Sustained Ultra DMA data-in burst

The values for the timings for each of the Ultra DMA modes are contained in 4.4.4

Figure 8. Sustained Ultra DMA data-in burst

#### NOTE:

1. DD(15:0) and DSTROBE signals are shown at both the host and the device to emphasize that cable setting time as well as cable propagation delay shall not allow the data signals to be considered stable at the host until some time after they are driven by the device.

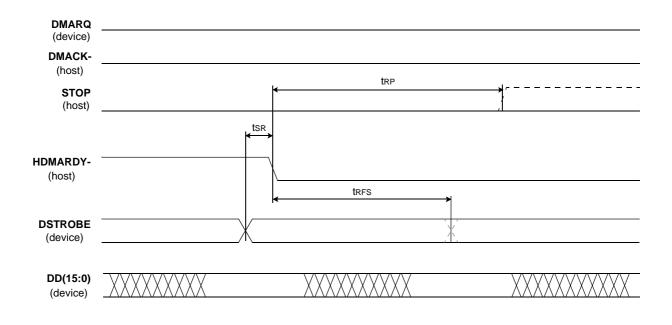

### 4.5.4.3 Host pausing an Ultra DMA data-in burst

The values for the timings for each of the Ultra DMA modes are contained in 4.4.4

#### Figure 9. Host pausing an Ultra DMA data-in burst

#### NOTE:

- The host mat assert STOP to request termination of the ultra DMA burst no sooner than tRP after HDMARDY- is negated.

If the t<sub>SR</sub> timing is not satisfied, the host may receive zero, one, or two more data words from the Host.

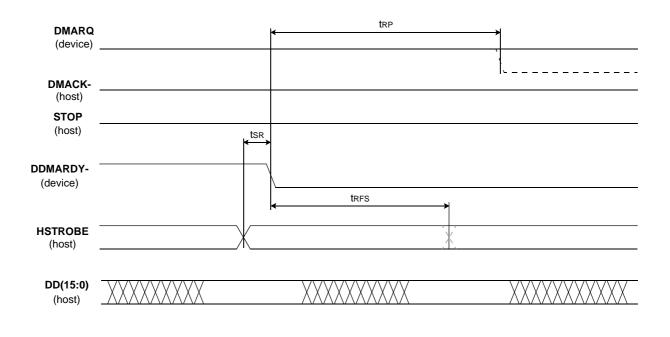

### 4.5.4.4 Device terminating an Ultra DMA data-in burst

The values for the timings for each of the Ultra DMA modes are contained in 4.4.4

#### Figure 10. Device terminating an Ultra DMA data-in burst

NOTE:

1. The definitions for the DIOW-:STOP, DIOR-:HDMARDY-:HSTROBE and IORDY:DDMARDY-:DSTROBE signal lines are no longer in effect after DMARQ and DMACK are negated.

### 4.5.4.5 Host terminating an Ultra DMA data-in burst

The values for the timings for each of the Ultra DMA modes are contained in 4.4.4

Figure 11. Host terminating an Ultra DMA data-in burst

#### NOTE:

1. The definitions for the DIOW-:STOP, DIOR-:HDMARDY-:HSTROBE and IORDY:DDMARDY-:DSTROBE signal lines are no longer in effect after DMARQ and DMACK are negated.

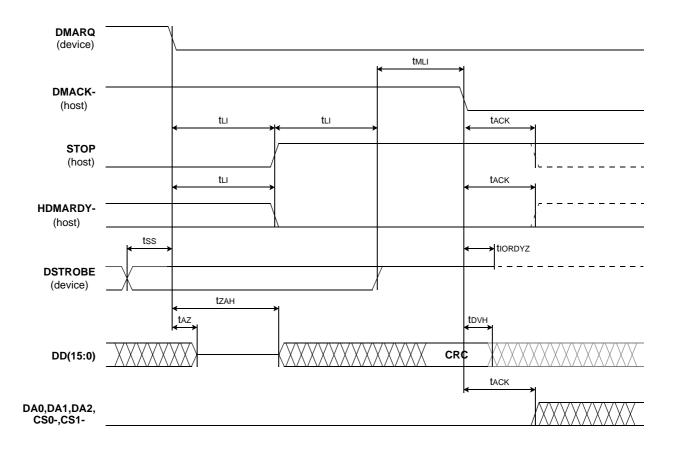

### 4.5.4.6 Initiating an Ultra DMA data-out burst

The values for the timings for each of the Ultra DMA modes are contained in 4.4.4

#### Figure 12. Initiating an Ultra DMA data-out burst

NOTE:

1. The definitions for the DIOW-:STOP,IORDY:DDMARDY-:DSTROBE and DIOR-:HDMARDY-:HSTROBE signal lines are no longer in effect after DMARQ and DMACK are negated.

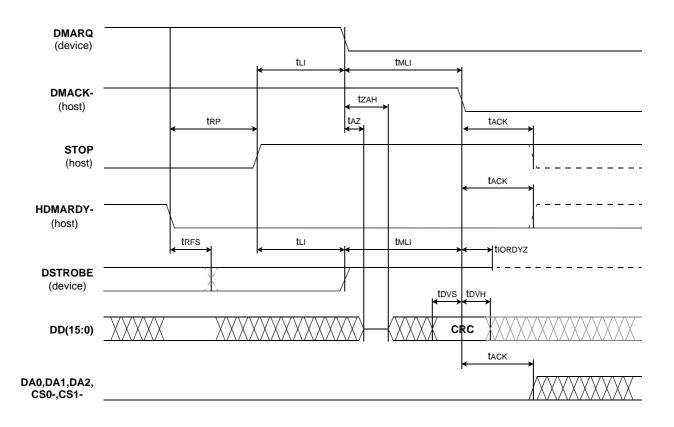

### 4.5.4.7 Sustained Ultra DMA data-out burst

The values for the timings for each of the Ultra DMA modes are contained in 4.4.4

Figure 13. Sustained Ultra DMA data-out burst

#### NOTE:

1. DD(15:0) and HSTROBE signals are shown at both the host and the device to emphasize that cable setting time as well as cable propagation delay shall not allow the data signals to be considered stable at the device until some time after they are driven by the host.

### 4.5.4.8 Device pausing an Ultra DMA data-out burst

The values for the timings for each of the Ultra DMA modes are contained in 4.4.4

#### Figure 14. Device pausing an Ultra DMA data-out burst

#### NOTE:

The device may negate DMARQ to request termination of the Ultra DMA burst no sooner that t<sub>RP</sub> after DDMARDY- is negated.

If the t<sub>SR</sub> timing is not satisfied, the device may receive zero,one,or two more data words from the host.

Sep. 27. 2006

### 4.5.4.9 Host terminating an Ultra DMA data-out burst

The values for the timings for each of the Ultra DMA modes are contained in 4.4.4

#### Figure 15. Host terminating an Ultra DMA data-out burst

NOTE:

1. The definitions for the DIOW-:STOP,IORDY:DDMARDY-:DSTROBE and DIOR-:HDMARDY-:HSTROBE signal lines are no longer in effect after DMARQ and DMACK are negated.

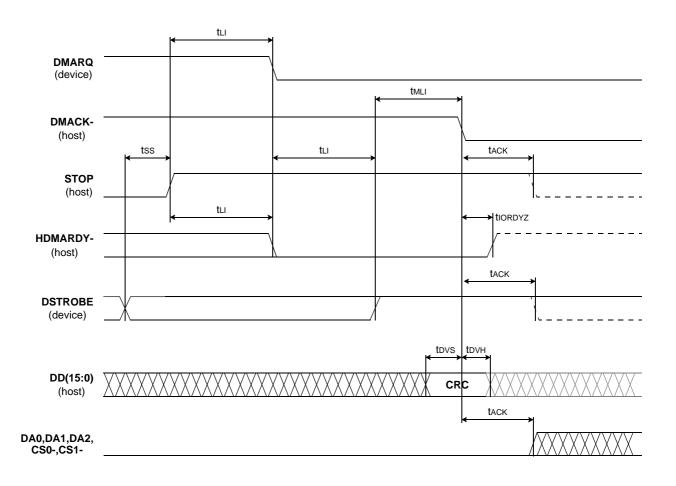

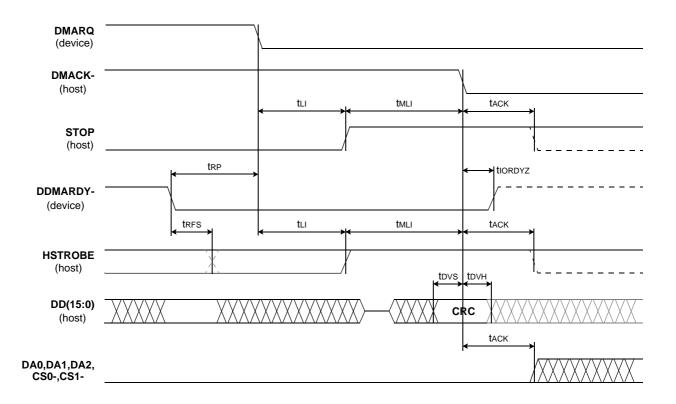

### 4.5.4.10 Device terminating an Ultra DMA data-out burst

The values for the timings for each of the Ultra DMA modes are contained in 4.4.4

#### Figure 16. Device terminating an Ultra DMA data-out burst

NOTE:

1. The definitions for the DIOW-:STOP,IORDY:DDMARDY-:DSTROBE and DIOR-:HDMARDY-:HSTROBE signal lines are no longer in effect after DMARQ and DMACK are negated.

### 5. ATA Registers

### 5.1 I/O Register Descriptions

Communication to or from the device is through registers addressed by the signals from the host(CS0-,CS1-, DA(2:0), DIOR-, and DIOW), CS0- and CS1- both asserted or negated is an invalid (not used) address except when both are negated during a DMA data transfer. When CS0- and CS1- are both asserted or both negated and a DMA transfer is not in progress, the device shall hold DD (15:0) in the released state and ignore transitions on DIOR- and DIOW-. When CS0- is negated and CS1- is asserted only DA (2:0) with a value of 6th is valid. During invalid combinations of assertion and negation of CS0-, CS1-, DA0, DA1, and DA2, a device shall keep DD(15:0) in the high impedance state and ignore transitions on DIOR- and DIOW-. Valid register addresses are described in the clauses defining the registers.

Address - the CS and DA address of the register.

Direction - indicates if the register is read/write, read only, or write only from the host.

Access restrictions - indicates when the register may be accessed.

Effect - indicates the effect of accessing the register.

Functional description - describes the function of the register.

Field/bit description - describes the content of the register.

### 5.2 Alternate Status Register

### 5.2.1 Address

| CS1 | CS0 | DA2                  | DA1 | DA0 |

|-----|-----|----------------------|-----|-----|

| A   | Ν   | А                    | А   | Ν   |

|     |     | A=asserted, N=negate | d   |     |

### 5.2.2 Direction

This register is read only. If this address is written to by the host, the Device Control register is written.

### **5.2.3 Access Restrictions**

When the BSY bit is set to one, the other bits in this register shall not be used. The entire contents of this register are not valid while the device is in Sleep mode.

### 5.2.4. Effect

Reading this register shall not clear a pending interrupt.

### **5.2.5 Functional Description**

This register contains the same information as the Status register in the command block.

### 5.3 Command Register

### 5.3.1 Address

| CS1 | CS0 | DA2                  | DA1 | DA0 |

|-----|-----|----------------------|-----|-----|

| Ν   | А   | А                    | А   | Ν   |

|     |     | A=asserted, N=negate | d   |     |

### 5.3.2 Direction

This register is write only. If this address is read by the host, the Status register is read.

### **5.3.3 Access Restrictions**

For all commands, this register shall only be written when BSY and DRQ are both cleared to zero and DMACK- is not asserted. If written when BSY or DRQ is set to one, the results of writing the Command register are indeterminate.

### 5.3.4 Effect

Command prcessing begins when this register is writte. The content of the Command Blcok registers become parameters of the command when this register is written. Writing this register clears any pending interrupt condition.

### 5.3.5 Functional description

This register contains the command code being sent to the device. Command execution begins immediately after this register is written.

### 5.3.6 Field/bit description

| 7 | 6 | 5 | 4     | 3        | 2 | 1 | 0 |